【计组】实验五 J型指令设计实验

目录

一、实验目的

二、实验环境

三、实验原理

四、实验任务

代码

一、实验目的

1. 理解MIPS处理器指令格式及功能。

2. 掌握lw, sw, beq, bne, lui, j, jal指令格式与功能。

3. 掌握ModelSim和ISE\Vivado工具软件。

4. 掌握基本的测试代码编写和FPGA开发板使用方法。

二、实验环境

1. 装有ModelSim和ISE\Vivado的计算机。

2. Sword\Basys3\EGo1实验系统。

三、实验原理

MIPS 32位处理器的指令格式分为R型、I型和J型。R型为寄存器型,即两个源操作数和目的操作数都是寄存器性。I型为操作数含有立即数。而J型特指转移类型指令,如图1所示。

如图2所示,本次实验将实现实验挑选剩余部分MIPS处理器指令进行实现。主要是部分R型和J型指令。指令的格式如图2所示,指令的功能参考资料1(李亚民. 计算机原理与设计:Verilog HDL版)。

如图3所示为按照单指令周期设计MIPS处理器内部结构。所有控制信号及字段均标注出来。另外,每条指令周期都包含2个clk,即PC模块用1个clk,Regfile和DataMem模块用1个clk,也可以说是由2个时钟构成的指令流水线。为了便于今后的扩展,将MIPS处理器进行了分阶段设计,这样结构更清晰,也有利于流水线的设计。随着后续指令的不断添加,处理器内部结构设计也会进行相应的调整,但时序部分应保持不变。

四、实验任务

1. 用Verilog HDL设计32位MIPS处理指令实现,参照图3的MIPS内部结构示意图,先编写基本实现代码,即能实现j和jal指令的取指令和执行指令,在Modelsim上仿真测试。

2. 参照图2,将设计的MIPS处理器改造为分阶段实现方案,注意每条指令周期平均只包含1个时钟周期。

3.编写指令存储测试文件,在Modelsim上调试通过。

代码

`define RstEnable 1'b1

`define RstDisable 1'b0

`define RomEnable 1'b1

`define RomDisable 1'b0

`define Zero 0

`define Valid 1'b1

`define Invalid 1'b0

//I

`define Inst_ori 6'b001101

`define Inst_addi 6'b001000

`define Inst_andi 6'b001100

`define Inst_xori 6'b001110

`define Inst_lui 6'b001111

`define Inst_subi 6'b001001

//R

`define Inst_r 6'b000000

`define Inst_add 6'b100000

`define Inst_sub 6'b100010

`define Inst_and 6'b100100

`define Inst_or 6'b100101

`define Inst_xor 6'b100110

`define Inst_sll 6'b000000

`define Inst_srl 6'b000010

`define Inst_sra 6'b000011

//J

`define Inst_j 6'b000010

`define Inst_jal 6'b000011

`define Inst_jr 6'b001000`define Inst_beq 6'b000100

`define Inst_bne 6'b000101`define Nop 6'b000000

`define Or 6'b000001

`define Add 6'b000010

`define And 6'b000011

`define Xor 6'b000100

`define Lui 6'b000101

`define Sub 6'b000110

`define Sll 6'b000111

`define Srl 6'b001000

`define Sra 6'b001001

`define J 6'b001010

`define Jal 6'b001011

`define Beq 6'b001100

`define Bne 6'b001101

`define Jr 6'b001110`include "define.v"

module EX(input wire rst,input wire [5:0] op, input wire [31:0] regaData,input wire [31:0] regbData,input wire regcWrite_i,input wire [4:0]regcAddr_i,output reg [31:0] regcData,output wire regcWrite,output wire [4:0] regcAddr

); always@(*)if(rst == `RstEnable)regcData = `Zero;elsebegincase(op)`Or:regcData = regaData | regbData;`Add:regcData = regaData + regbData;`And:regcData = regaData & regbData;`Xor:regcData = regaData ^ regbData;`Lui:regcData = regaData;/*`Lui:regcData = regaData | regbData;*/`Sub:regcData = regaData - regbData;`Sll:regcData = regbData << regaData;`Srl:regcData = regbData >> regaData;`Sra:regcData = ($signed(regbData)) >>> regaData;`J:regcData = `Zero;`Jr:regcData = `Zero;`Jal:regcData = regbData;`Beq:regcData = `Zero;`Bne:regcData = `Zero;default:regcData = `Zero;endcaseendassign regcWrite = regcWrite_i;assign regcAddr = regcAddr_i;

endmodule`include "define.v";

module ID (input wire rst, input wire [31:0] pc, //Jinput wire [31:0] inst,input wire [31:0] regaData_i,input wire [31:0] regbData_i,output reg [5:0] op, output reg [31:0] regaData,output reg [31:0] regbData,output reg regaRead,output reg regbRead,output reg regcWrite,output reg [4:0] regaAddr,output reg [4:0] regbAddr, output reg [4:0] regcAddr,output reg [31:0] jAddr, //Joutput reg jCe//J);wire [5:0] inst_op = inst[31:26]; reg [31:0] imm;//Rwire[5:0] func = inst[5:0]; //Jwire [31:0] npc = pc + 4;always@(*)if(rst == `RstEnable)beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;jCe = `Invalid;//JjAddr = `Zero;//Jendelse beginjCe = `Invalid;//JjAddr = `Zero;//Jcase(inst_op)`Inst_ori:beginop = `Or; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_andi:beginop = `And; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_xori:beginop = `Xor; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_addi:beginop = `Add; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_subi:beginop = `Sub; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_lui:beginop = `Lui; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = inst[20:16];imm = {inst[15:0],16'h0};end`Inst_r:case(func)`Inst_add:beginop = `Add; regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_or:beginop = `Or;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sub:beginop = `Sub;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_and:beginop = `And;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_xor:beginop = `Xor;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sll:beginop = `Sll;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_srl:beginop = `Srl;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_sra:beginop = `Sra;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_jr:beginop = `Jr;regaRead = `Valid;//rsregbRead = `Invalid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = `Zero;jAddr = regaData;jCe = `Valid;imm = `Zero;enddefault:beginregaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase//J`Inst_j:beginop = `J;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = `Zero;end `Inst_jal:beginop = `Jal;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = 5'b11111;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = npc;end//J `Inst_beq:beginop = `Beq;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData==regbData)?`Valid:`Invalid; /* if(regaData==regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bne:beginop = `Bne;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData!=regbData)?`Valid:`Invalid; /* if(regaData!=regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end default:beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase endalways@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaRead == `Valid)regaData = regaData_i;else regaData = imm;always@(*)if(rst == `RstEnable)regbData = `Zero; else if(regbRead == `Valid)regbData = regbData_i;elseregbData = imm; endmodule

`include "define.v"

module IF(input wire clk,input wire rst,input wire [31:0] jAddr,//Jinput wire jCe,//Joutput reg ce,

output reg [31:0] pc

);always@(*)if(rst == `RstEnable)ce = `RomDisable;elsece = `RomEnable;

/* always@(posedge clk)if(ce == `RomDisable)pc = `Zero;elsepc = pc + 4;

*/always@(posedge clk)if(ce == `RomDisable)pc = `Zero;else if(jCe == `Valid)//Jpc = jAddr;elsepc = pc + 4;

endmodule

`include "define.v"

module MIPS(input wire clk,input wire rst,input wire [31:0] instruction,output wire romCe,output wire [31:0] instAddr

);wire [31:0] regaData_regFile, regbData_regFile;wire [31:0] regaData_id, regbData_id; wire [31:0] regcData_ex;wire [5:0] op; wire regaRead, regbRead;wire [4:0] regaAddr, regbAddr;wire regcWrite_id, regcWrite_ex;wire [4:0] regcAddr_id, regcAddr_ex;//Jwire [31:0] jAddr;wire jCe;IF if0(.clk(clk),.rst(rst),.jAddr(jAddr),//J.jCe(jCe),//J.ce(romCe), .pc(instAddr));ID id0(.pc(instAddr),//J.jAddr(jAddr),//J.jCe(jCe),//J.rst(rst), .inst(instruction),.regaData_i(regaData_regFile),.regbData_i(regbData_regFile),.op(op),.regaData(regaData_id),.regbData(regbData_id),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regcWrite(regcWrite_id),.regcAddr(regcAddr_id));EX ex0(.rst(rst),.op(op), .regaData(regaData_id),.regbData(regbData_id),.regcWrite_i(regcWrite_id),.regcAddr_i(regcAddr_id),.regcData(regcData_ex),.regcWrite(regcWrite_ex),.regcAddr(regcAddr_ex)); RegFile regfile0(.clk(clk),.rst(rst),.we(regcWrite_ex),.waddr(regcAddr_ex),.wdata(regcData_ex),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regaData(regaData_regFile),.regbData(regbData_regFile));

endmodule`include "define.v"

module RegFile(input wire clk,input wire rst,input wire we,input wire [4:0] waddr,input wire [31:0] wdata,input wire regaRead,input wire regbRead,input wire [4:0] regaAddr,input wire [4:0] regbAddr,output reg [31:0] regaData,output reg [31:0] regbData

);reg [31:0] reg32 [31 : 0]; always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaAddr == `Zero)regaData = `Zero;elseregaData = reg32[regaAddr];always@(*)if(rst == `RstEnable) regbData = `Zero;else if(regbAddr == `Zero)regbData = `Zero;elseregbData = reg32[regbAddr];always@(posedge clk)if(rst != `RstEnable)if((we == `Valid) && (waddr != `Zero))reg32[waddr] = wdata;else ;

endmodulemodule SoC(input wire clk,input wire rst

);wire [31:0] instAddr;wire [31:0] instruction;wire romCe; MIPS mips0(.clk(clk),.rst(rst),.instruction(instruction),.instAddr(instAddr),.romCe(romCe)); InstMem instrom0(.ce(romCe),.addr(instAddr),.data(instruction));

endmodule`include "define.v"

module soc_tb;reg clk;reg rst;initialbeginclk = 0;rst = `RstEnable;#100rst = `RstDisable;#10000 $stop; endalways #10 clk = ~ clk;SoC soc0(.clk(clk), .rst(rst));

endmodule相关文章:

【计组】实验五 J型指令设计实验

目录 一、实验目的 二、实验环境 三、实验原理 四、实验任务 代码 一、实验目的 1. 理解MIPS处理器指令格式及功能。 2. 掌握lw, sw, beq, bne, lui, j, jal指令格式与功能。 3. 掌握ModelSim和ISE\Vivado工具软件。 4. 掌握基本的测试代码编写和FPGA开发板使用方法。 …...

Redis03 - 高可用

Redis高可用 文章目录 Redis高可用一:主从复制 & 读写分离1:主从复制的作用2:主从复制原理2.1:全量复制2.2:增量复制(环形缓冲区) 3:主从复制实际演示3.1:基本流程准…...

SAP HCM自定义开发程序调用odata api 如何ping外网

网络:我们知道SAP系统一般是部署在内网,Successfactors是云系统,部署在公有云上面,那肯定是公网,那内网和外网数据传递就需要网络做相关的设置,今天遇到的问题是网络说已经把SAP系统映射到公网,…...

SAP HCM PFCG读取结构化权限参数

权限:HCM的权限分两套,一套是PFCG的普通权限,一套是结构化权限是根据组织ID限制访问权限的,今天我们讨论的话题如何把这两类的权限组合起来 场景:例如下载有个薪酬管理人员,他复制A和B部门,但是…...

Ubuntu 20.04配置网络

1,检查自己网络是否配通。 网络配置成功显示的网络图标 不成功的网络图标 如果看不见网络图标,可以使用ping命令。连接一下百度网。 ping www.baidu.com ping失败的样子 ping成功的样子 2,接下来进入正题,我们开始配置网络。 这…...

【hive】记一次hiveserver内存溢出排查,线程池未正确关闭导致

一、使用 MemoryAnalyzer软件打开hprof文件 很大有30G,win内存24GB,不用担心可以打开,ma软件能够生成索引文件,逐块分析内存,如下图。 大约需要4小时。 overview中开不到具体信息。 二、使用Leak Suspects功能继续…...

Windows编程:下载与安装 Visual Studio 2019

本节前言 在写作本节的时候,本来呢,我正在写的专栏,是 MFC 专栏。而 VS2010 和 VS2019,正是 MFC 学习与开发中,可以使用的两款软件。然而呢,如果你去学习 Windows API 知识的话,那么࿰…...

Unity3D实现Shader开发之径向模糊(实现镜头中间不模糊,四周模糊的效果)

系列文章目录 unity工具 文章目录 系列文章目录👉前言👉一、效果图👉二、实现步骤与原理详解👉三、实现方法👉壁纸分享👉总结👉前言 径向模糊(Radial Blur)是一种常见的图像特效,在 Unity 开发中常用于模拟聚焦、运动模糊等效果,让图像产生从中心向四周或从…...

iOS 自动翻滚广告条(榜单条)实现方案

引言 在直播场景中,榜单信息、活动公告或者广告推广通常需要以醒目的方式展示,但由于屏幕空间有限,一次只能显示一条内容。为了让用户能够持续关注这些信息,我们可以实现一个自动翻滚的广告条(或榜单条)&a…...

计算机视觉-拟合

一、拟合 拟合的作用主要是给物体有一个更好的描述 根据任务选择对应的方法(最小二乘,全最小二乘,鲁棒最小二乘,RANSAC) 边缘提取只能告诉边,但是给不出来数学描述(应该告诉这个点线是谁的&a…...

【JVM详解一】类加载过程与内存区域划分

一、简介 1.1 概述 JVM是Java Virtual Machine(Java虚拟机)的缩写,是通过在实际的计算机上仿真模拟各种计算机功能来实现的。由一套字节码指令集、一组寄存器、一个栈、一个垃圾回收堆和一个存储方法域等组成。JVM屏蔽了与操作系统平台相关…...

Unity项目接入xLua的一种流程

1. 导入xlua 首先导入xlua,这个不用多说 2. 编写C#和Lua交互脚本 基础版本,即xlua自带的版本 using System.Collections; using System.Collections.Generic; using UnityEngine; using XLua; using System; using System.IO;[Serializable] public…...

Deepseek 接入Word处理对话框(隐藏密钥)

硅基流动邀请码:1zNe93Cp 邀请链接:网页链接 亲测deepseek接入word,自由调用对话,看截图有兴趣的复用代码(当然也可以自己向deepseek提问,帮助你完成接入,但是提问逻辑不一样给出的答案是千差万…...

Office/WPS接入DS等多个AI工具,开启办公新模式!

在现代职场中,Office办公套件已成为工作和学习的必备工具,其功能强大但复杂,熟练掌握需要系统的学习。为了简化操作,使每个人都能轻松使用各种功能,市场上涌现出各类办公插件。这些插件不仅提升了用户体验,…...

ximalaya(三) playUriList值解密--webpack

本文主要介绍解密音频播放url参数。 本文仅代表个人理解,如有其他建议可在评论区沟通。 声明 仅仅记录一下自己的学习方法,不作为其他参考、更不作为商业用途。如有侵犯请联系本人删除 目标地址:aHR0cHM6Ly93d3cueGltYWxheWEuY29tL3NvdW5k…...

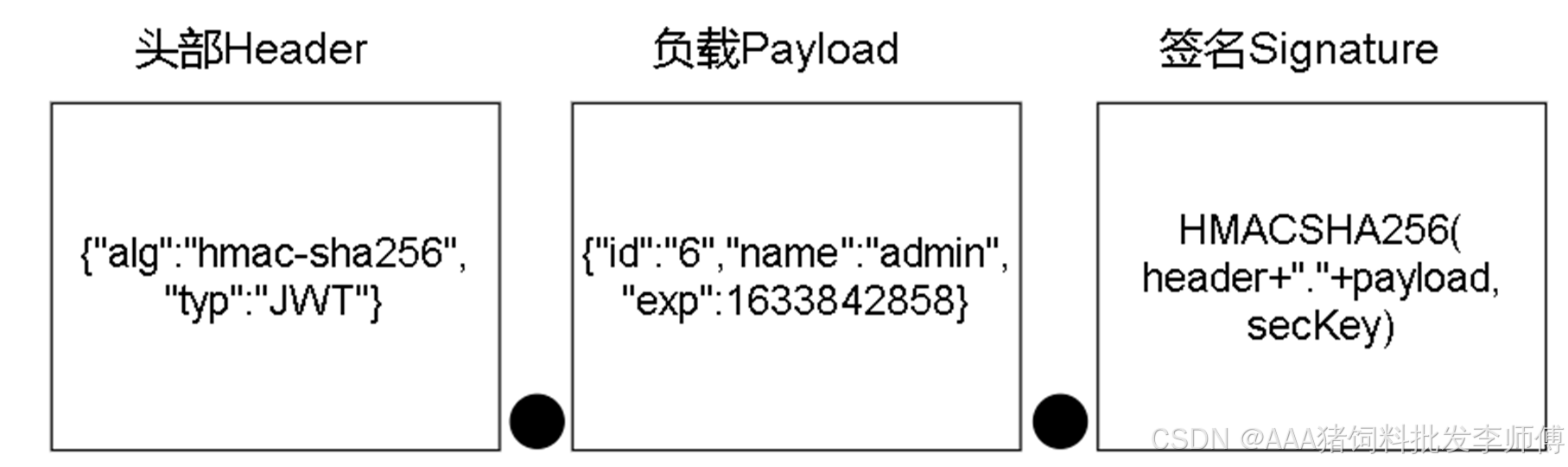

ASP.NET Core JWT

目录 Session的缺点 JWT(Json Web Token) 优点: 登录流程 JWT的基本使用 生成JWT 解码JWT 用JwtSecurityTokenHandler对JWT解码 注意 Session的缺点 对于分布式集群环境,Session数据保存在服务器内存中就不合适了&#…...

原生redis实现分布式锁

用 原生 Redis(Jedis、Lettuce) 实现分布式锁,可以参考 Redisson 的原理,但需要自己处理锁的自动续期、故障恢复等细节。核心思路是使用 Redis 的 SET NX EX 或 SET PX NX 命令来实现互斥锁,并利用 Lua 脚本 保障原子性…...

光伏-报告显示,假期内,硅料端签单顺序发货相对稳定。若3月份下游存提产,则不排除硅料价格有上调预期。

据TrendForce集邦咨询报告显示,假期内,硅料端按照前期签单顺序发货,相对稳定。若3月份下游存提产,则不排除硅料价格有上调预期。 002306中科云网 旅游 | 公司为提供复合菜系特色餐饮的连锁企业,形成了以粤菜ÿ…...

【信息系统项目管理师-案例真题】2017上半年案例分析答案和详解

更多内容请见: 备考信息系统项目管理师-专栏介绍和目录 文章目录 试题一【问题1】8 分【问题2】4 分【问题3】8 分【问题4】5 分试题二【问题1】10 分【问题2】8 分【问题3】6 分【问题4】5 分试题三【问题1】5 分【问题2】7 分【问题3】6 分【问题4】3 分试题一 阅读下列说明…...

滴水逆向_程序实现弹窗修改OEP

作业: 几个很重要的注意事项。 1 我们模拟的是内核如何将一个文件硬盘中拉伸到内存中,但是我们做的仅仅是 模拟拉伸过程。也就是说其中的属性字段是无差别的拷贝的。 但是加载exe的时候 ,imagebase 是随机分配的。 我们打开内存中的exe&…...

快速上手——.net封装使用DeekSeek-V3 模型

📢欢迎点赞 :👍 收藏 ⭐留言 📝 如有错误敬请指正,赐人玫瑰,手留余香!📢本文作者:由webmote 原创📢作者格言:新的征程,用爱发电,去丈量人心,是否能达到人机合一?开工大吉 新的一年就这么水灵灵的开始了,在这里,祝各位读者新春快乐,万事如意! 新年伊…...

ReactNative进阶(五十九):存量 react-native 项目适配 HarmonyOS NEXT

文章目录 一、前言二、ohos_react_native2.1 Fabric2.2 TurboModule2.2.1 ArkTSTurboModule2.2.2 cxxTurboModule: 三、拓展阅读 一、前言 2024年10月22日19:00,华为在深圳举办“原生鸿蒙之夜暨华为全场景新品发布会”,主题为“星河璀璨&…...

1-2 面向对象编程方法

1.0 面向对象编程思维 在面向对象风格中,结构体被看做数据(data),而操作数据的函数称作方法(method)。目前函数 和数据是分离的,函数并不直接操作数据,我们需要拿到函数返回的结果&a…...

k8s中部署nginx的pod

在当今数字化的浪潮中,容器编排技术成为了构建和管理应用程序的核心力量。Kubernetes(简称 k8s)作为容器编排领域的佼佼者,凭借其强大的自动化部署、扩展和管理能力,深受开发者和运维人员的青睐。而 Nginx 作为一款高性…...

CSS 组合选择符详解与实战示例

在 Web 开发过程中,CSS 用于定义页面元素的样式,而选择器则帮助我们精确定位需要添加样式的元素。今天我们主要来讲解 CSS 中的组合选择符,它们能够根据 DOM 结构中元素之间的关系来选中目标元素,从而写出结构清晰、易于维护的 CS…...

html为<td>添加标注文本

样式说明: /*为td添加相对定位点*/ .td_text {position: relative; }/*为p添加绝对坐标(相对于父元素中的定位点)*/ .td_text p {position: absolute;top: 80%;font-size: 8px; }参考资料:...

apachePoi中XSSFClientAnchor图片坐标简述;填充多张图片

概述 业务中经常会遇到在单元格内填充图片的需求,而且要求指定图片在单元格内的位置。 一般都是用的apache的poi,设置图片坐标。 HSSFClientAnchor(int dx1, int dy1, int dx2, int dy2, short col1, int row1, short col2, int row2)dx1 dy1 起始单元…...

无界构建微前端?NO!NO!NO!多系统融合思路!

文章目录 微前端理解1、微前端概念2、微前端特性3、微前端方案a、iframeb、qiankun --> 使用比较复杂 --> 自己写对vite的插件c、micro-app --> 京东开发 --> 对vite支持更拉跨d、EMP 方案--> 必须使用 webpack5 --> 很多人感觉不是微前端 --> 去中心化方…...

数据留痕的方法

在项目中,数据变更时,经常需要记录上次的数据,以便查看对比,专业术语叫做数据留痕。数据变更留痕(即记录数据的变更历史)是一个常见的需求,例如在审计、追踪数据变化或满足合规性要求的场景中。…...

Glustefs 服务端配置流程

Glustefs 服务端配置流程 (一)环境搭建 名称ip硬件设备文件虚拟机 gluster1192.168.101.12G新磁盘/dev/sdb虚拟机 gluster2192.168.101.22G新磁盘/dev/sdb虚拟机 gluster3192.168.101.32G新磁盘/dev/sdb (二)磁盘格式化&#x…...