【Basys3】外设-灯和数码管

灯

约束文件

set_property PACKAGE_PIN W5 [get_ports CLK]

set_property PACKAGE_PIN U18 [get_ports rst]

set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property PACKAGE_PIN U19 [get_ports {led[2]}]

set_property PACKAGE_PIN V19 [get_ports {led[3]}]

set_property PACKAGE_PIN W18 [get_ports {led[4]}]

set_property PACKAGE_PIN U15 [get_ports {led[5]}]

set_property PACKAGE_PIN U14 [get_ports {led[6]}]

set_property PACKAGE_PIN V14 [get_ports {led[7]}]

set_property PACKAGE_PIN V13 [get_ports {led[8]}]

set_property PACKAGE_PIN V3 [get_ports {led[9]}]

set_property PACKAGE_PIN W3 [get_ports {led[10]}]

set_property PACKAGE_PIN U3 [get_ports {led[11]}]

set_property PACKAGE_PIN P3 [get_ports {led[12]}]

set_property PACKAGE_PIN N3 [get_ports {led[13]}]

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property PACKAGE_PIN L1 [get_ports {led[15]}]

set_property PACKAGE_PIN V16 [get_ports {sel[1]}]

set_property PACKAGE_PIN V17 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property IOSTANDARD LVCMOS33 [get_ports rst]CLK、rst、sel都是自定义的端口名,可做相应修改

数码管

约束文件

set_property PACKAGE_PIN W5 [get_ports CLK]

set_property PACKAGE_PIN V17 [get_ports SW_in]

set_property IOSTANDARD LVCMOS33 [get_ports SW_in]

set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN W4 [get_ports {display_out[10]}]

set_property PACKAGE_PIN V4 [get_ports {display_out[9]}]

set_property PACKAGE_PIN U4 [get_ports {display_out[8]}]

set_property PACKAGE_PIN U2 [get_ports {display_out[7]}]

set_property PACKAGE_PIN W7 [get_ports {display_out[6]}]

set_property PACKAGE_PIN W6 [get_ports {display_out[5]}]

set_property PACKAGE_PIN U8 [get_ports {display_out[4]}]

set_property PACKAGE_PIN V8 [get_ports {display_out[3]}]

set_property PACKAGE_PIN U5 [get_ports {display_out[2]}]

set_property PACKAGE_PIN V5 [get_ports {display_out[1]}]

set_property PACKAGE_PIN U7 [get_ports {display_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {display_out[10]}]像CLK、SW_in、display_out这些,可通过自己定义的端口进行相应的修改

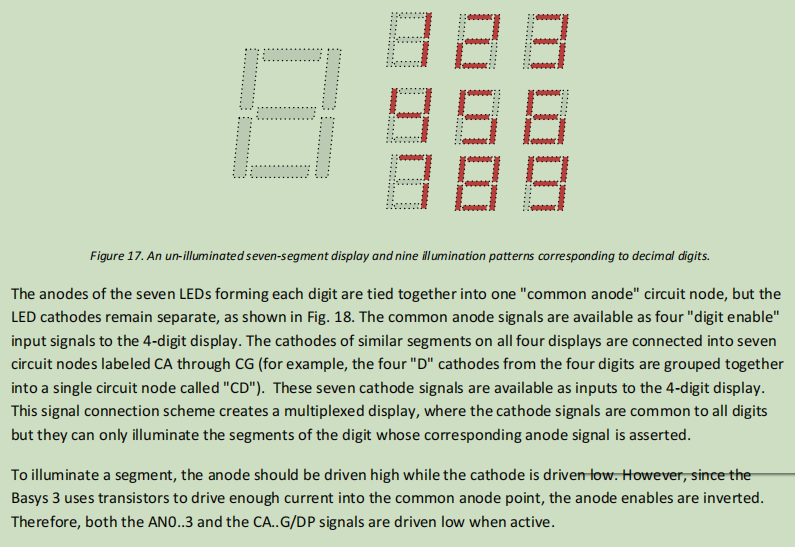

数码管是共阳极的,阳极通过晶体管驱动,所以当需要点亮某个段时,阳极应该被拉低(因为晶体管是反向驱动的)。另外,显示控制器需要以一定的刷新率循环点亮四个数码管,每个数码管依次显示一段时间,利用人眼的视觉暂留效应让四个数码管看起来同时亮起。刷新率一般在1kHz到60Hz之间,每个数码管的点亮时间大约是刷新周期的四分之一,比如16ms的周期,每个数码管点亮4ms。

Basys 3板上的七段数码管是共阳极的,每个数码管的七个段(加上小数点)的阴极是分开的,而阳极是共用的。每个段的LED通过330欧姆的电阻连接到FPGA的I/O引脚,当对应的引脚输出高电平时,LED会点亮。但是根据前面的描述,由于驱动电路中的反向晶体管,实际有效的信号可能是低电平激活。

如何通过分时复用来控制四个数码管。例如,当AN0(第一个数码管的阳极)有效时,设置相应的阴极信号来显示特定的数字,然后依次切换到AN1、AN2、AN3,每个阳极的有效时间相同,循环往复。

总结

数码管为共阳极结构,阳极通过反向晶体管驱动,因此阳极有效信号为低电平。

显示控制采用分时复用技术,每个数码管依次点亮,刷新率需高于人眼感知阈值(如1kHz到60Hz)。

每个数码管点亮时间为刷新周期的四分之一(如16ms总周期,每个数码管点亮4ms)。

Basys 3板的七段数码管为四位数码管,共阳极设计,阴极分段控制。

段选信号(阴极)需设置为低电平以点亮对应段,阳极通过FPGA引脚输出低电平激活(因驱动电路反向)。

具体时序示例说明:通过循环切换阳极(AN0-AN3)并同步设置阴极信号,实现多位数显示。

刷新周期建议为1ms-16ms,每个数码管点亮时间为刷新周期的四分之一(如4ms)。

dispaly.v

显示1234和4321

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2015/12/02 22:02:29

// Design Name:

// Module Name: display

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module display(input CLK,input SW_in,output reg[10:0] display_out);reg [19:0]count=0;reg [2:0] sel=0;parameter T1MS=50000;always@(posedge CLK)beginif(SW_in==0)begincase(sel)0:display_out<=11'b0111_1001111;1:display_out<=11'b1011_0010010;2:display_out<=11'b1101_0000110;3:display_out<=11'b1110_1001100;default:display_out<=11'b1111_1111111;endcaseendelsebegincase(sel)0:display_out<=11'b1110_1001111;1:display_out<=11'b1101_0010010;2:display_out<=11'b1011_0000110;3:display_out<=11'b0111_1001100;default:display_out<=11'b1111_1111111;endcaseendendalways@(posedge CLK)begincount<=count+1;if(count==T1MS)begincount<=0;sel<=sel+1;if(sel==4)sel<=0;endend

endmodule模块有三个端口:CLK(时钟输入),SW_in(开关输入),display_out(11位的输出寄存器)。display_out可能对应四个数码管的阳极选择(4位)和七段的阴极控制(7位),总共11位。例如,假设前4位是四个数码管的阳极使能,后7位是阴极控制(CA到CG)。

在第一个always块中,当SW_in为0时,根据sel的值(0到3),设置不同的display_out。例如,当sel=0时,display_out是11'b0111_1001111。这里前四位是0111,可能表示选择第一个数码管(因为AN0是低电平有效,而0111中的第一位是0),后面七位是1001111,对应七段显示的数字。类似地,其他sel值对应不同的数码管和显示内容。当SW_in为1时,display_out的阳极选择位相反,可能是数码管的顺序被反转。

第二个always块用于生成sel信号,即选择当前要点亮的数码管。计数器count在每次时钟上升沿递增,当达到T1MS(50000)时,sel加1,循环在0到3之间。这样,每个数码管的显示时间由count的溢出频率决定。例如,如果时钟频率是50MHz,那么每个计数周期是20ns,T1MS=50000对应1ms的计数溢出。因此,每个数码管的点亮时间是1ms,四个数码管的总刷新周期是4ms,对应250Hz的刷新率,这在人眼可接受的范围内,不会有明显的闪烁。

模块功能

通过分时复用控制四位数码管,循环点亮每一位并显示特定内容,具体逻辑如下:

信号定义:

display_out[10:0]:11位输出信号,前4位控制阳极(AN0-AN3),后7位控制阴极(CA-CG)。

sel[2:0]:数码管选择信号(0-3),用于切换当前点亮的数码管。

count:计数器,用于控制刷新频率。

T1MS=50000:假设时钟为50MHz时,计数至50000对应1ms(20ns * 50000 = 1ms)。显示逻辑(第一个always块):

SW_in=0时:

sel=0:选中第一个数码管(display_out=0111_1001111),即AN0低电平,阴极显示“1”(对应1001111)。

sel=1:选中第二个数码管(display_out=1011_0010010),即AN1低电平,阴极显示“2”(对应0010010)。类似逻辑依次控制第3、4位数码管。

SW_in=1时:

阳极选择顺序反转,例如

sel=0对应AN3(display_out=1110_1001111),实现数码管点亮顺序的逆向切换。刷新逻辑(第二个always块):

计数器

count累加,每1ms(达到T1MS)切换一次sel,循环范围为0-3。每个数码管点亮时间为1ms,总刷新周期为4ms(对应250Hz刷新率),满足无闪烁要求。

关键设计细节

阳极控制:前4位为

AN3-AN0(高位在前),例如0111表示AN0有效(低电平),其余无效(高电平)。阴极编码:后7位为七段码(CA-CG),例如

1001111对应段码“1”(CA=1, CB=0, CC=0, CD=1, CE=1, CF=1, CG=1)。刷新机制:通过快速循环切换阳极和同步更新阴极,利用视觉暂留效应实现四位数码管“同时”显示。

流水灯

`timescale 1ns / 1ps

module led_display(input CLK, // 系统时钟(假设50MHz)input RST, // 复位信号output reg [15:0] LED, // 16位流水灯输出output reg [3:0] AN, // 数码管位选(AN0-AN3,低电平有效)output reg [6:0] SEG // 七段码输出(CA-CG,低电平有效)

);// 分时复用控制参数

reg [19:0] cnt_refresh = 0; // 刷新计数器(1ms刷新周期)

reg [1:0] sel = 0; // 数码管选择信号

reg [15:0] shift_reg = 16'h0001; // 流水灯移位寄存器(初始值1)// 七段译码表(0-F,共阴极编码,需根据实际硬件调整)

function [6:0] seg_decoder;input [3:0] data;begincase(data)4'h0: seg_decoder = 7'b0000001; // 04'h1: seg_decoder = 7'b1001111; // 14'h2: seg_decoder = 7'b0010010; // 24'h3: seg_decoder = 7'b0000110; // 34'h4: seg_decoder = 7'b1001100; // 44'h5: seg_decoder = 7'b0100100; // 54'h6: seg_decoder = 7'b0100000; // 64'h7: seg_decoder = 7'b0001111; // 74'h8: seg_decoder = 7'b0000000; // 84'h9: seg_decoder = 7'b0000100; // 9default: seg_decoder = 7'b1111111; // 灭endcaseend

endfunction// 流水灯移位逻辑(每秒移位一次)

reg [25:0] cnt_shift = 0;

always @(posedge CLK) beginif (RST) beginshift_reg <= 16'h0001; // 复位时初始化为1end else begincnt_shift <= cnt_shift + 1;if (cnt_shift == 50_000_000) begin // 1秒移位一次(50MHz时钟)shift_reg <= {shift_reg[14:0], shift_reg[15]}; // 循环左移cnt_shift <= 0;endendLED <= shift_reg; // 输出流水灯状态

end// 数码管动态扫描逻辑

always @(posedge CLK) begincnt_refresh <= cnt_refresh + 1;if (cnt_refresh == 50_000) begin // 1ms刷新周期(50MHz时钟)cnt_refresh <= 0;sel <= sel + 1; // 切换数码管end

end// 数码管数据选择与七段译码

always @(*) begincase(sel)2'b00: beginAN = 4'b1110; // 选中第1位数码管(AN0低电平)SEG = seg_decoder(shift_reg[3:0]); // 显示低4位流水灯状态end2'b01: beginAN = 4'b1101; // 选中第2位数码管(AN1低电平)SEG = seg_decoder(shift_reg[7:4]); // 显示次低4位end2'b10: beginAN = 4'b1011; // 选中第3位数码管(AN2低电平)SEG = seg_decoder(shift_reg[11:8]); // 显示次高4位end2'b11: beginAN = 4'b0111; // 选中第4位数码管(AN3低电平)SEG = seg_decoder(shift_reg[15:12]); // 显示高4位enddefault: beginAN = 4'b1111; // 默认关闭所有数码管SEG = 7'b1111111;endendcase

endendmodule选中某一个数码管

module SoC(input wire clk0, input wire rst,/*IO interface*/input wire [1:0] sel,output reg[10:0] displayout,//output wire[15:0] led

);

wire[6:0] out1;

wire[6:0] out2;

wire[6:0] out3;

wire[6:0] out4;

shumaguan U1(out1,led[3:0]);

shumaguan U2(out2,led[7:4]);

shumaguan U3(out3,led[11:8]);

shumaguan U4(out4,led[15:12]);

always@(*)beginif(led[3:0]>0) displayout={4'b1110,out1};else if(led[7:4]>0) displayout={4'b1101,out2};else if(led[11:8]>0) displayout={4'b1011,out3};else if(led[15:12]>0) displayout={4'b0111,out4};endwire clk;clk_div clk_div0(.clk(clk0),.rst(rst),.Clk_CPU(clk));//........xdc

set_property PACKAGE_PIN W5 [get_ports clk0]

set_property PACKAGE_PIN W16 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports clk0]

set_property PACKAGE_PIN W4 [get_ports {displayout[10]}]

set_property PACKAGE_PIN V4 [get_ports {displayout[9]}]

set_property PACKAGE_PIN U4 [get_ports {displayout[8]}]

set_property PACKAGE_PIN U2 [get_ports {displayout[7]}]

set_property PACKAGE_PIN W7 [get_ports {displayout[6]}]

set_property PACKAGE_PIN W6 [get_ports {displayout[5]}]

set_property PACKAGE_PIN U8 [get_ports {displayout[4]}]

set_property PACKAGE_PIN V8 [get_ports {displayout[3]}]

set_property PACKAGE_PIN U5 [get_ports {displayout[2]}]

set_property PACKAGE_PIN V5 [get_ports {displayout[1]}]

set_property PACKAGE_PIN U7 [get_ports {displayout[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {displayout[10]}]set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property PACKAGE_PIN E19 [get_ports {led[1]}]

set_property PACKAGE_PIN U19 [get_ports {led[2]}]

set_property PACKAGE_PIN V19 [get_ports {led[3]}]

set_property PACKAGE_PIN W18 [get_ports {led[4]}]

set_property PACKAGE_PIN U15 [get_ports {led[5]}]

set_property PACKAGE_PIN U14 [get_ports {led[6]}]

set_property PACKAGE_PIN V14 [get_ports {led[7]}]

set_property PACKAGE_PIN V13 [get_ports {led[8]}]

set_property PACKAGE_PIN V3 [get_ports {led[9]}]

set_property PACKAGE_PIN W3 [get_ports {led[10]}]

set_property PACKAGE_PIN U3 [get_ports {led[11]}]

set_property PACKAGE_PIN P3 [get_ports {led[12]}]

set_property PACKAGE_PIN N3 [get_ports {led[13]}]

set_property PACKAGE_PIN P1 [get_ports {led[14]}]

set_property PACKAGE_PIN L1 [get_ports {led[15]}]

set_property PACKAGE_PIN V16 [get_ports {sel[1]}]

set_property PACKAGE_PIN V17 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

shumaguan.v

module shumaguan(out,in);input[3:0] in;output reg[6:0] out;

always@(*)case(in)4'h0:out=7'b0000001;4'h1:out=7'b1001111;4'h2:out=7'b0010010;4'h3:out=7'b0000110;4'h4:out=7'b1001100;4'h5:out=7'b0100100;4'h6:out=7'b0100000;4'h7:out=7'b0001111;4'h8:out=7'b0000000;4'h9:out=7'b0000100;4'ha:out=7'b0001000;4'hb:out=7'b1100000;4'hc:out=7'b0110001;4'hd:out=7'b1000010;4'he:out=7'b0110000;4'hf:out=7'b0111000;default: out=7'b0000001;endcase

endmodule

分时复用

module SoC(input wire clk0, input wire rst,/*IO interface*/input wire [1:0] sel,output reg [10:0] displayout, // 前4位控制AN,后7位控制段码output wire [15:0] led

);wire [6:0] out1, out2, out3, out4;reg [19:0] cnt_refresh = 0; // 刷新计数器(假设50MHz时钟)reg [1:0] sel_scan = 0; // 数码管动态扫描选择信号// 七段译码模块实例化shumaguan U1(out1, led[3:0]);shumaguan U2(out2, led[7:4]);shumaguan U3(out3, led[11:8]);shumaguan U4(out4, led[15:12]);// 分时复用控制逻辑always @(posedge clk0) beginif (rst) begincnt_refresh <= 0;sel_scan <= 0;end else begincnt_refresh <= cnt_refresh + 1;if (cnt_refresh == 50_000) begin // 1ms刷新周期(50MHz时钟)cnt_refresh <= 0;sel_scan <= sel_scan + 1;endendend// 数码管动态扫描输出always @(*) begincase (sel_scan)2'b00: displayout = {4'b1110, out1}; // 选中第1位数码管(AN0低电平)2'b01: displayout = {4'b1101, out2}; // 选中第2位数码管(AN1低电平)2'b10: displayout = {4'b1011, out3}; // 选中第3位数码管(AN2低电平)2'b11: displayout = {4'b0111, out4}; // 选中第4位数码管(AN3低电平)default: displayout = 11'b1111_1111111; // 默认关闭endcaseend// 其余原有代码保持不变(时钟分频、MIPS、内存等)wire clk;clk_div clk_div0(.clk(clk0),.rst(rst),.Clk_CPU(clk));// ...(其他模块实例化代码)

endmodule相关文章:

【Basys3】外设-灯和数码管

灯 约束文件 set_property PACKAGE_PIN W5 [get_ports CLK] set_property PACKAGE_PIN U18 [get_ports rst] set_property PACKAGE_PIN U16 [get_ports {led[0]}] set_property PACKAGE_PIN E19 [get_ports {led[1]}] set_property PACKAGE_PIN U19 [get_ports {led[2]}] set…...

axios文件下载使用后端传递的名称

java后端通过HttpServletResponse 返回文件流 在Content-Disposition中插入文件名 一定要设置Access-Control-Expose-Headers,代表跨域该Content-Disposition返回Header可读,如果没有,前端是取不到Content-Disposition的,可以在统…...

从零开始搭建Anaconda环境

Anaconda是一个流行的Python数据科学平台,包含conda包管理器、Python解释器和大量预装的数据科学工具包。以下是详细的安装和配置步骤: 1. 下载Anaconda 访问Anaconda官方网站 根据你的操作系统(Windows/macOS/Linux)选择相应版本 推荐下载Python 3.x版…...

TDengine 中的命名与边界

简介 本章主要介绍命名的合法字符集和限制规则,这对于正确使用 TDengine,减小报错很重要,这些规则在 SQL 语句中都生效,在使用过程中要注意,避免不必要的错误。 名称命名规则 合法字符:英文字符、数字和…...

软件架构设计中的软件过程模型初识

软件架构设计中的软件过程模型是指导软件开发过程的框架,它们定义了软件开发的不同阶段、活动、任务和角色。结合具体的使用场景,可以更好地理解这些模型如何在实际项目中应用。以下将详细介绍几种常见的软件过程模型,并结合典型场景进行讲解…...

基于ssm的课程辅助教学平台(全套)

互联网发展至今,无论是其理论还是技术都已经成熟,而且它广泛参与在社会中的方方面面。它让信息都可以通过网络传播,搭配信息管理工具可以很好地为人们提供服务。针对《离散结构》课程教学信息管理混乱,出错率高,信息安…...

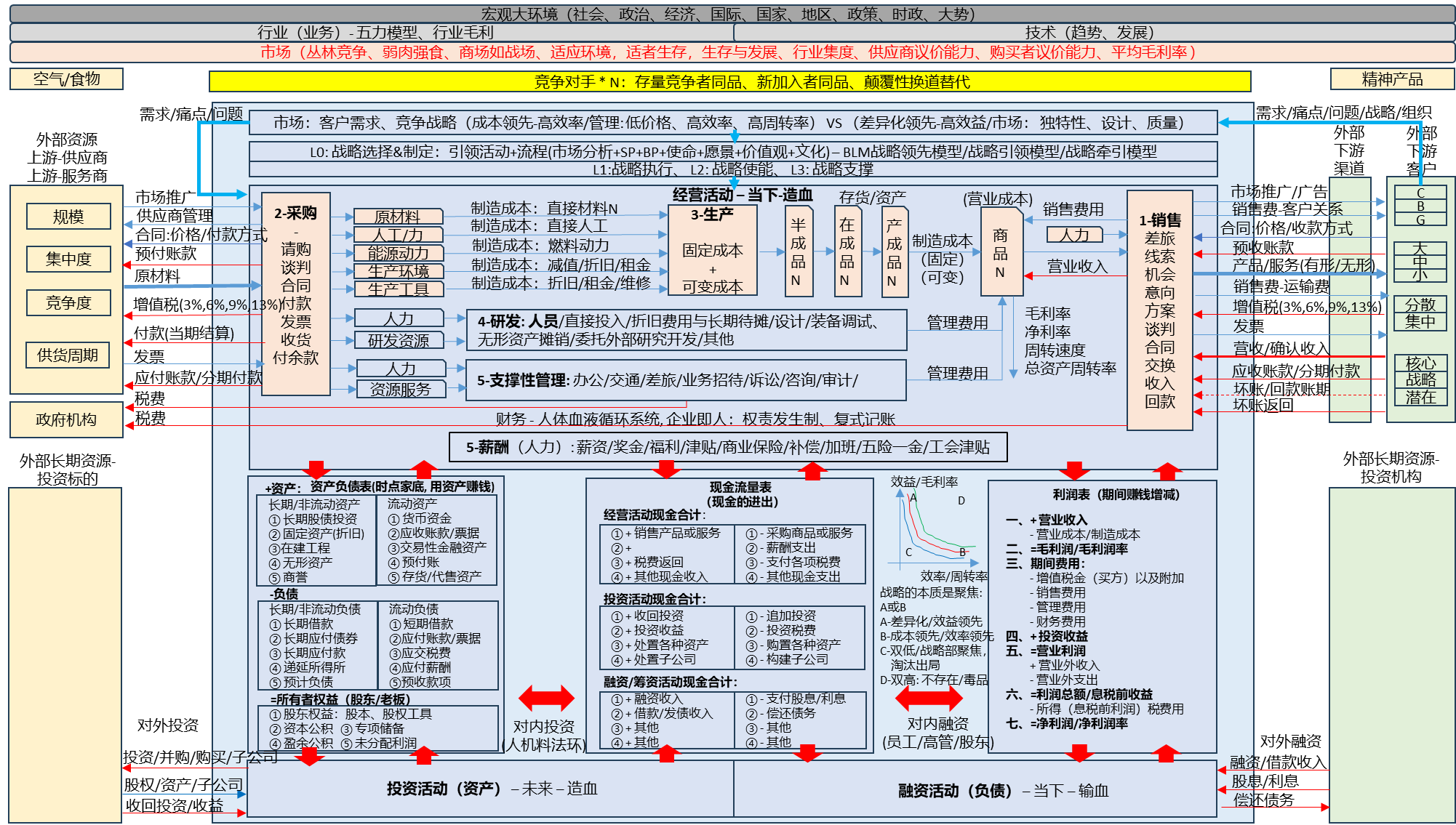

[创业之路-344]:战略的本质是选择、聚焦, 是成本/效率/低毛利优先,还是差易化/效益/高毛利优先?无论是成本优先,还是差易化战略,产品聚焦是前提。

前言: 一、战略的本质是选择、聚焦 关于战略的本质,触及了商业竞争的核心矛盾:选择成本优先(效率/低毛利)还是差异化(效益/高毛利),本质上是对企业战略方向的终极拷问。 1、战略选…...

洛谷题单1-P5705 【深基2.例7】数字反转-python-流程图重构

题目描述 输入一个不小于 100 100 100 且小于 1000 1000 1000,同时包括小数点后一位的一个浮点数,例如 123.4 123.4 123.4 ,要求把这个数字翻转过来,变成 4.321 4.321 4.321 并输出。 输入格式 一行一个浮点数 输出格式 …...

Typora 小乌龟 git 上传到gitee仓库教程

首先进行资源分享 通过网盘分享的文件:TortoiseGit-LanguagePack-2.17.0.0-64bit-zh_CN.msi等4个文件 链接: https://pan.baidu.com/s/1NC8CKLifCEH_YixDU3HG_Q?pwdqacu 提取码: qacu --来自百度网盘超级会员v3的分享 首先将软件进行解压 看自己电脑的版本进行…...

【新人系列】Golang 入门(八):defer 详解 - 上

✍ 个人博客:https://blog.csdn.net/Newin2020?typeblog 📝 专栏地址:https://blog.csdn.net/newin2020/category_12898955.html 📣 专栏定位:为 0 基础刚入门 Golang 的小伙伴提供详细的讲解,也欢迎大佬们…...

知识图谱之知识抽取:从数据海洋中 “捞金”

目录 知识抽取:开启知识宝库的钥匙 知识抽取的对象:实体、关系与属性 知识抽取的方法:各显神通的 “淘金术” 基于规则的方法 机器学习方法 深度学习方法 知识抽取面临的挑战:荆棘丛中的探索 数据的多样性和复杂性 语义理…...

RAG - 五大文档切分策略深度解析

文章目录 切分策略1. 固定大小分割(Fixed-Size Chunking)2. 滑动窗口分割(Sliding Window Chunking)3. 自然语言单元分割(Sentence/Paragraph Segmentation)4. 语义感知分割(Semantic-Aware Seg…...

keil中文注释出现乱码怎么解决

keil中文注释出现乱码怎么解决 在keil–edit–configuration中encoding改为chinese-GB2312...

论文阅读笔记——ReconDreamer

ReconDreamer 论文 在 DriveDreamer4D 的基础上,通过渐进式数据更新,解决大范围机动(多车道连续变道、紧急避障)的问题。同时 DriveDreamer4D生成轨迹后直接渲染,而 ReconDreamer 会实时通过 DriveRestorer 检测渲染结…...

鸿蒙harmonyOS:笔记 正则表达式

从给出的文本中,按照既定的相关规则,匹配出符合的数据,其中的规则就是正则表达式,使用正则表达式,可以使得我们用简洁的代码就能实现一定复杂的逻辑,比如判断一个邮箱账号是否符合正常的邮箱账号࿰…...

计算机网络——传输层(TCP)

传输层 在计算机网络中,传输层是将数据向上向下传输的一个重要的层面,其中传输层中有两个协议,TCP,UDP 这两个协议。 TCP 话不多说,我们直接来看协议报头。 源/目的端口号:表示数据从哪个进程来࿰…...

英伟达与通用汽车深化合作,澳特证券am broker助力科技投资

在近期的GTC大会上,英伟达CEO黄仁勋宣布英伟达将与通用汽车深化合作,共同推进AI技术在自动驾驶和智能工厂的应用。此次合作标志着自动驾驶汽车时代的加速到来,同时也展示了英伟达在AI技术领域的最新进展。 合作内容包括:…...

Visual Studio 2022静态库与动态库创建及使用完全指南

在C开发中,库(Library)是代码复用的重要方式。本教程将详细介绍如何在Visual Studio 2022中创建和使用静态库(.lib)和动态库(.dll),每种库类型都会有完整的创建步骤和实际示例。 第…...

C++中常见符合RAII思想的设计有哪些

文章目录 **一、标准库中的 RAII 类**1. **智能指针**2. **文件操作类**3. **锁管理类**4. **容器类**5. **线程管理** **二、自定义 RAII 类的常见场景**1. **数据库连接**2. **图形资源管理(如 OpenGL 纹理)**3. **网络套接字**4. **事务处理**5. **临…...

CUDA Memory Fence 函数的功能与硬件实现细节

CUDA Memory Fence 函数的功能与硬件实现细节 Memory Fence 的基本功能 CUDA中的memory fence函数用于控制内存操作的可见性顺序,确保在fence之前的内存操作对特定范围内的线程可见。主要功能包括: 排序内存操作:确保fence之前的内存操作在…...

CSS学习笔记5——渐变属性+盒子模型阶段案例

目录 通俗易懂的解释 渐变的类型 1、线性渐变 渐变过程 2、径向渐变 如何理解CSS的径向渐变,以及其渐变属性 通俗易懂的解释 渐变属性 1. 形状(Shape) 2. 大小(Size) 3. 颜色停靠点(Color Sto…...

[Java微服务架构]4_服务通信之客户端负载均衡

欢迎来到啾啾的博客🐱,一个致力于构建完善的Java程序员知识体系的博客📚,记录学习的点滴,分享工作的思考、实用的技巧,偶尔分享一些杂谈💬。 欢迎评论交流,感谢您的阅读😄…...

基于SpringBoot实现的高校实验室管理平台功能四

一、前言介绍: 1.1 项目摘要 随着信息技术的飞速发展,高校实验室的管理逐渐趋向于信息化、智能化。传统的实验室管理方式存在效率低下、资源浪费等问题,因此,利用现代技术手段对实验室进行高效管理显得尤为重要。 高校实验室作为…...

神经网络与深度学习的发展)

吴恩达深度学习复盘(1)神经网络与深度学习的发展

一、神经网络的起源与生物学动机 灵感来源 神经网络的最初动机源于对生物大脑的模仿。20 世纪 50 年代,科学家试图通过软件模拟神经元的工作机制(如树突接收信号、轴突传递信号),构建类似人类大脑的信息处理系统。 生物神经元的简…...

用Python实现资本资产定价模型(CAPM)

使用 Python 计算资本资产定价模型(CAPM)并获取贝塔系数(β)。 步骤 1:导入必要的库 import pandas as pd import yfinance as yf import statsmodels.api as sm import matplotlib.pyplot as plt 步骤 2࿱…...

Linux进程管理之子进程的创建(fork函数)、子进程与线程的区别、fork函数的简单使用例子、子进程的典型应用场景、父进程等待子进程结束后自己再结束

收尾 进程终止:子进程通过exit()或_exit()终止,父进程通过wait()或waitpid()等待子进程终止,并获取其退出状态。?其实可以考虑在另一篇博文中来写 fork函数讲解 fork函数概述 fork() 是 Linux 中用于创建新进程的系统调用。当…...

妙用《甄嬛传》中的选妃来记忆概率论中的乘法公式

强烈推荐最近在看的不错的B站概率论课程 《概率统计》正课,零废话,超精讲!【孔祥仁】 《概率统计》正课,零废话,超精讲!【孔祥仁】_哔哩哔哩_bilibili 其中概率论中的乘法公式,老师用了《甄嬛传…...

虚幻基础:UI

文章目录 控件蓝图可以装载其他控件蓝图可以安装其他蓝图接口 填充:相对于父组件填充水平框尺寸—填充—0.5:改变填充的尺寸填充—0.5:改变与父组件的距离 锚点:相对于父组件的控件坐标系原点,屏幕比例改变时ÿ…...

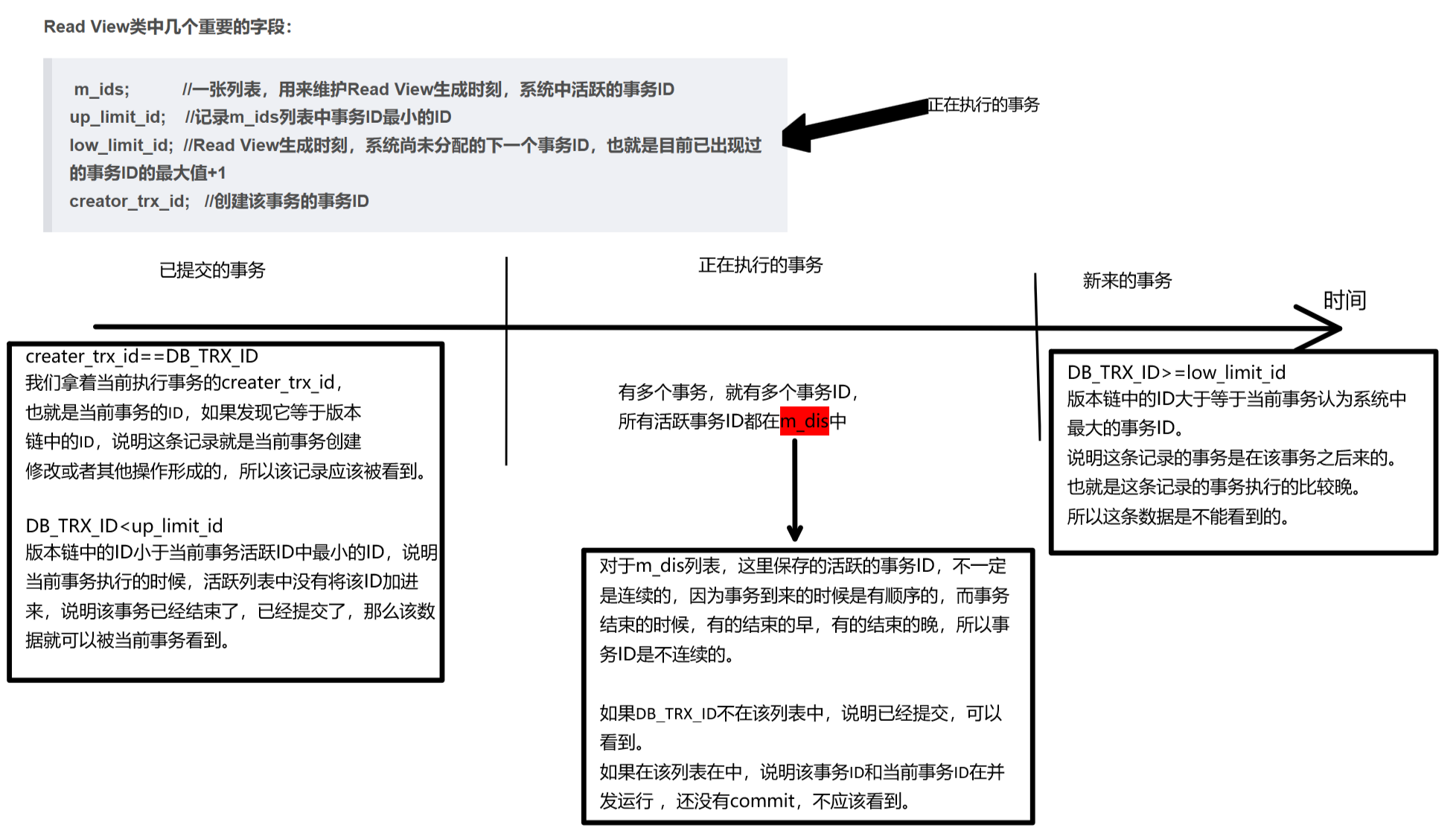

【MySQL篇】事务管理,事务的特性及深入理解隔离级别

目录 一,什么是事务 二,事务的版本支持 三,事务的提交方式 四,事务常见操作方式 五,隔离级别 1,理解隔离性 2,查看与设置隔离级别 3,读未提交(read uncommitted&a…...

项目实战-角色列表

抄上一次写过的代码: import React, { useState, useEffect } from "react"; import axios from axios; import { Button, Table, Modal } from antd; import { BarsOutlined, DeleteOutlined, ExclamationCircleOutlined } from ant-design/icons;const…...