Quartus II的IP核调用及仿真测试

目录

- 第一章 什么是IP核?

- 第二章 什么是LPM?

- 第一节 设置LPM_COUNTER模块参数

- 第二节 仿真

- 第三章 什么是PLL?

- 第一节 设置ALTPLL(嵌入式锁相环)模块参数

- 第二节 仿真

- 第四章 什么是RAM?

- 第一节 RAM_1PORT的调用

- 第二节 配置RAM_1PORT

- 第三节 RAM_2PORT的调用

- 第四节 配置RAM_2PORT

- 第五章 什么是FIFO?

- 第一节 FIFO模块参数配置

- 第二节 配置FIFO

- 参考文献

第一章 什么是IP核?

IP核就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品——掩膜。[1]

第二章 什么是LPM?

LPM即参数化模块库(Library of Parameterized Modules),是Altera 公司FPGA/CPLD设计软件Quartus II自带的一些宏功能模块,如:锁相环(PLLs), LVDS,数字信号处理(DSP) 模块等。这些功能是对Altera器件的优化,设计者在用这些模块时,不耗用器件的逻辑资源(Logic Cell)。[2]

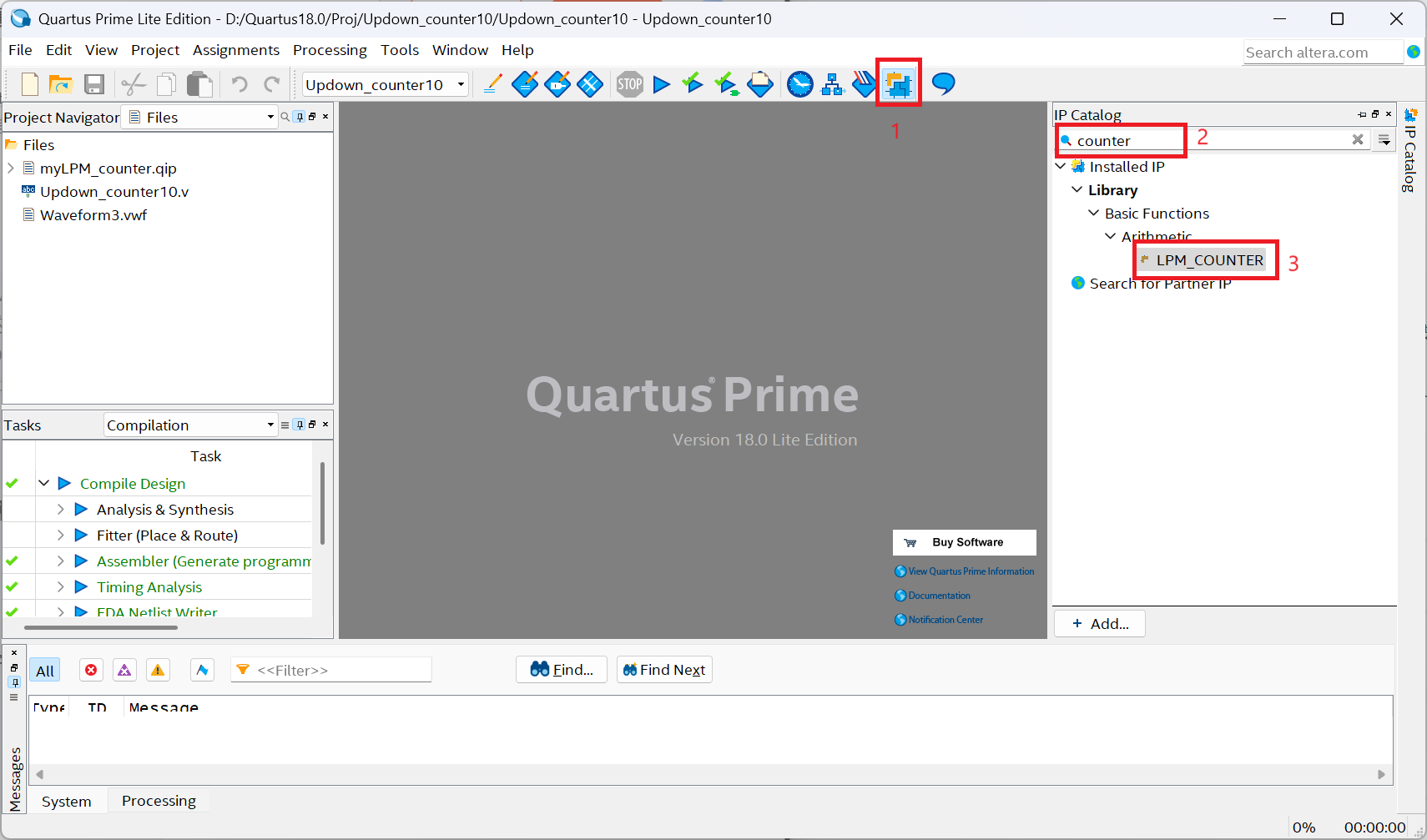

第一节 设置LPM_COUNTER模块参数

-

新建项目,点击

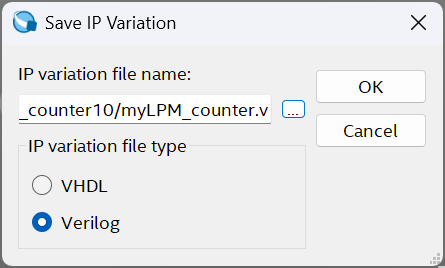

IP Catalog,在搜索框内输入counter,点击LPM_COUNTER,然后将其保存为myLPM_counter.v,点击Ok开始配置

-

基础设置

-

设置输入并点击NEXT。

-

多次点击NEXT,出现如下界面后选择需要文件,点击Finish完成配置,在弹出界面点击Yes

第二节 仿真

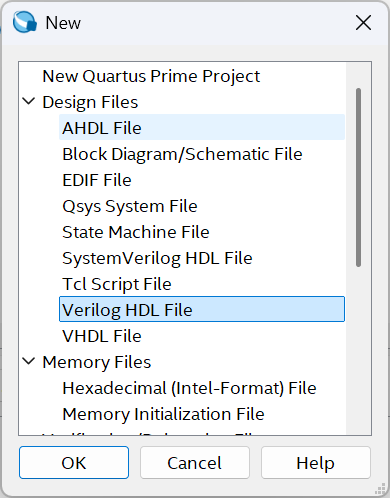

- 新建Verilog HDL File,然后写入代码,生成需要的模型,将其保存为

Updown_counter10.v

module Updown_counter10 (aclr,cp_en,cp,updown,co,q);input aclr;input cp_en;input cp;input updown;output co;output [3:0] q;myLPM_counter myLPM_counter_inst(.aclr(aclr),.clk_en(cp_en),.clock(cp),.updown(updown),.cout(co),.q (q));

endmodule

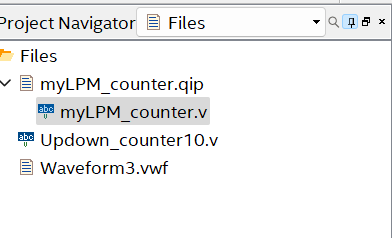

文件目录如下

- 设置LPM_COUNTER,修改

myLPM_counter.qip文件下的myLPM_counter.v,使其符合期望

`timescale 1 ps / 1 ps

module myLPM_counter (aclr,clk_en,clock,sclr,updown,cout,q);input aclr;input clk_en;input clock;input sclr;input updown;output cout;output [3:0] q;wire sub_wire0;wire [3:0] sub_wire1;wire cout = sub_wire0;wire [3:0] q = sub_wire1[3:0];lpm_counter LPM_COUNTER_component (.clk_en (clk_en),.clock (clock),

// .sclr (sclr),.updown (updown),.cout (sub_wire0),.q (sub_wire1),.aclr (1'b0),.aload (1'b0),.aset (1'b0),.cin (1'b1),.cnt_en (1'b1),.data ({4{1'b0}}),.eq (),.sclr(1'b0),.sload (1'b0),.sset (1'b0));defparamLPM_COUNTER_component.lpm_direction = "UNUSED",LPM_COUNTER_component.lpm_modulus = 10,LPM_COUNTER_component.lpm_port_updown = "PORT_USED",LPM_COUNTER_component.lpm_type = "LPM_COUNTER",LPM_COUNTER_component.lpm_width = 4;

endmodule

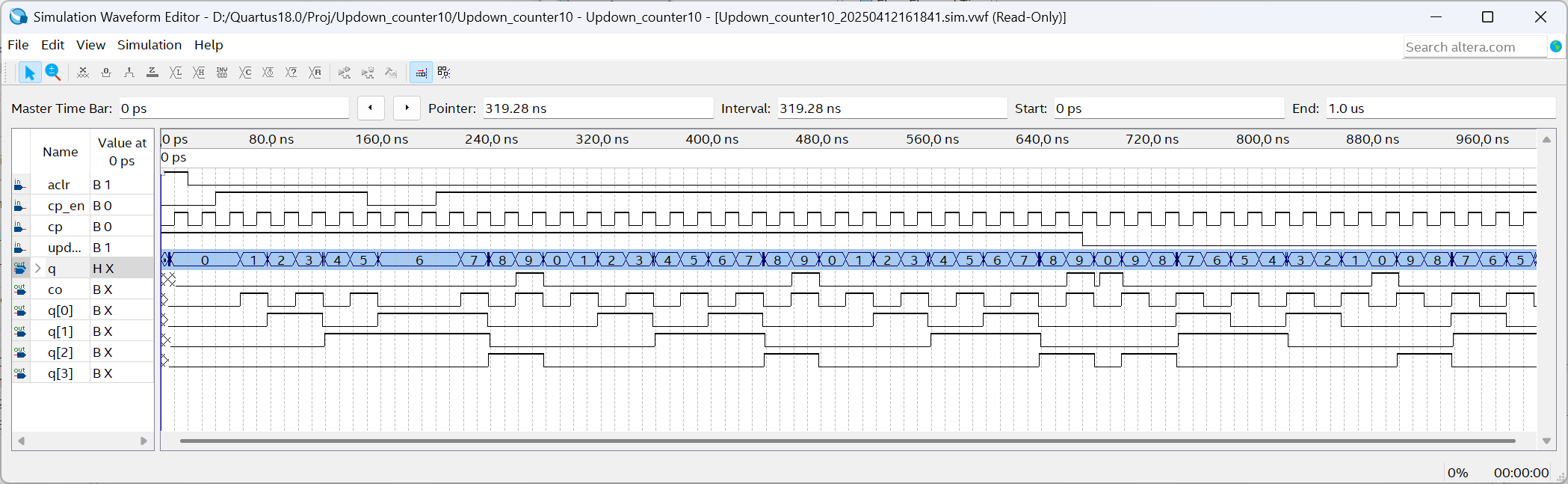

- 开始完整编译,编译通过后,新建

University Program VWF进行仿真

- 仿真

观察仿真结果发现,结果与预期相同

第三章 什么是PLL?

PLL即锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。根据自动控制原理,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。[3]

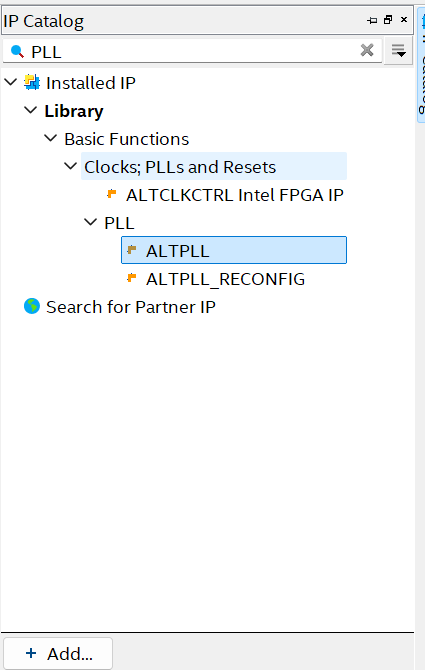

第一节 设置ALTPLL(嵌入式锁相环)模块参数

-

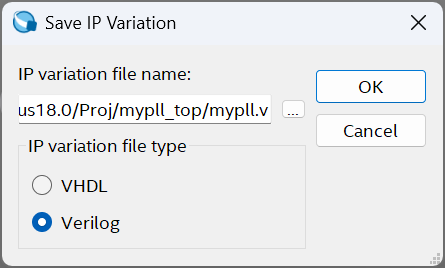

选择ALTPLL,与第二章第一节相同的处理方法,在IP Catalog中搜索

PLL,选择ALTPLL在点击左下角的Add按钮将其保存为mypll.v文件并开始配置

-

根据选择的芯片设置合适的晶振,ep4ce115f29c7的晶振为50MHZ,使用时钟频率选择50MHZ,模式为正常

-

以下配置默认即可

-

设置时钟

c0:设置100MHZ,将时钟倍频,占空比设置50%

c1:25MHZ,选择分频,且相位偏移90°,占空比50%

c2:5MHZ,占空比为25%

c3:先分频再倍频,75MHZ,占空比50%

目前只选择4个时钟,第5个时钟不启用 -

多次点击next,直到出现此界面,勾选

mypll_inst.v文件和mypll_bb.v文件

第二节 仿真

- 新建

Verilog HDL File,写入下面的模型代码,保存为test_IP.v

module test_IP(input clk , // 时钟信号input rst_n , // 上电复位低有效output c0 ,output c1 ,output c2 ,output c3 ,output locked

);// PLL

mypll mypll_inst (.areset ( ~rst_n ), // IP复位高有效.inclk0 ( clk ), // 输入时钟.c0 ( c0 ), // 输出时钟.c1 ( c1 ), // 输出时钟.c2 ( c2 ), // 输出时钟.c3 ( c3 ), // 输出时钟.locked ( locked ) // 时钟输出锁--锁定不稳定时钟输出

);endmodule以及测试代码test_tb.v

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;wire c0 ;wire c1 ;wire c2 ;wire c3 ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.c0 (c0 ),.c1 (c1 ),.c2 (c2 ),.c3 (c3 ),.locked (locked )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位#200;rst_n = 1'b1;#20000;$stop;

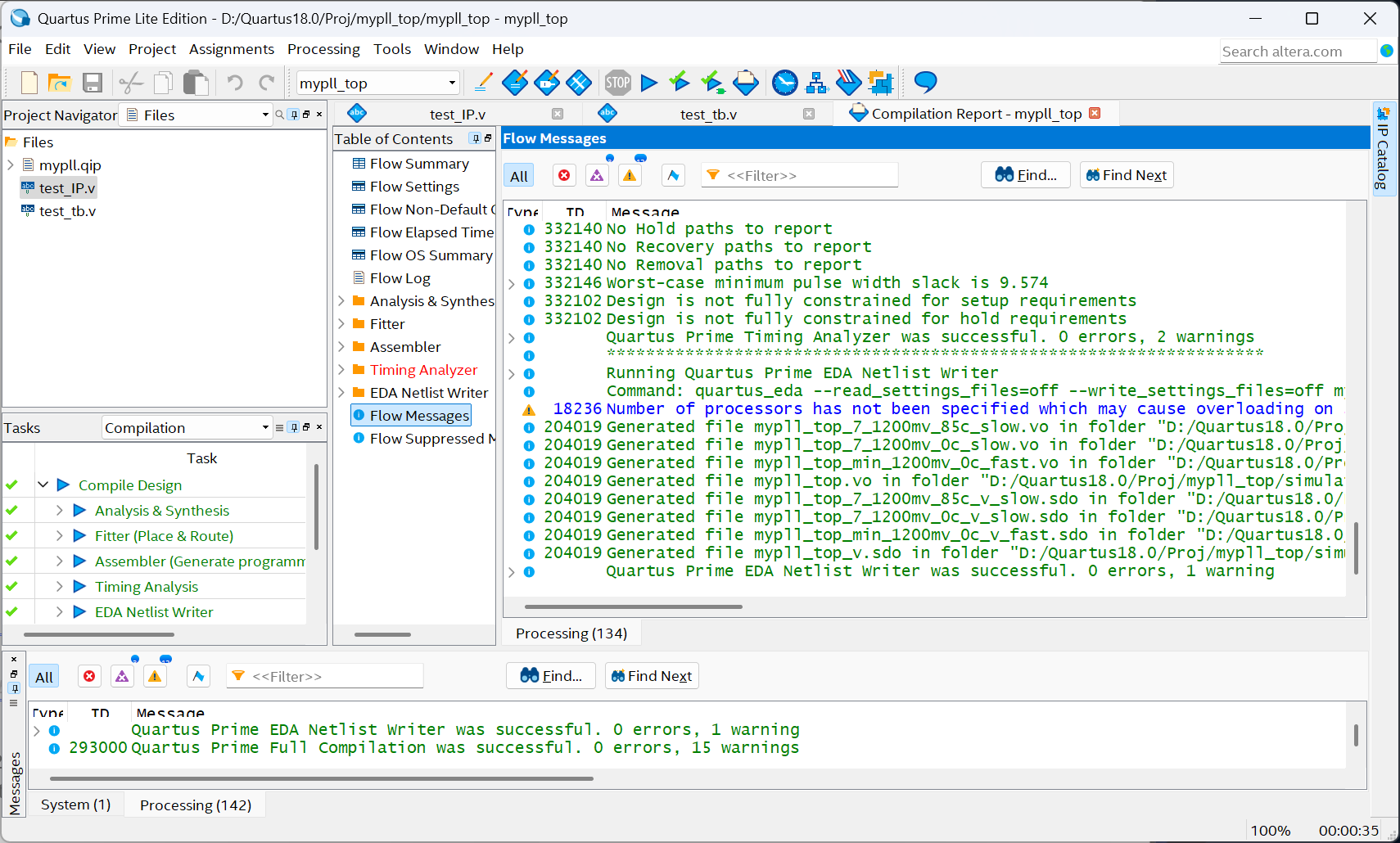

endendmodule- 进行完整编译,编译通过后开始仿真

- 仿真

观察仿真结果发现与预期相同

第四章 什么是RAM?

RAM即随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。[4]

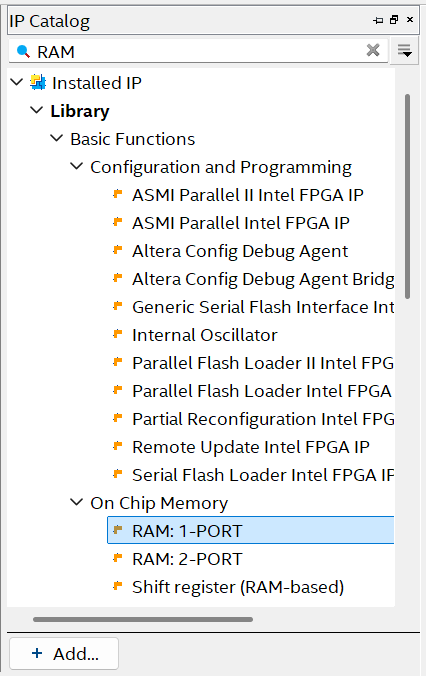

第一节 RAM_1PORT的调用

-

搜索

RAM选择RAM_1PORT并添加保存为RAM_1PORT.v

-

设置位宽和数据深度

-

多次点击NEXT直到出现此界面,并勾选

RAM_1PORT_inst.v和RAM_1PORT_bb.v

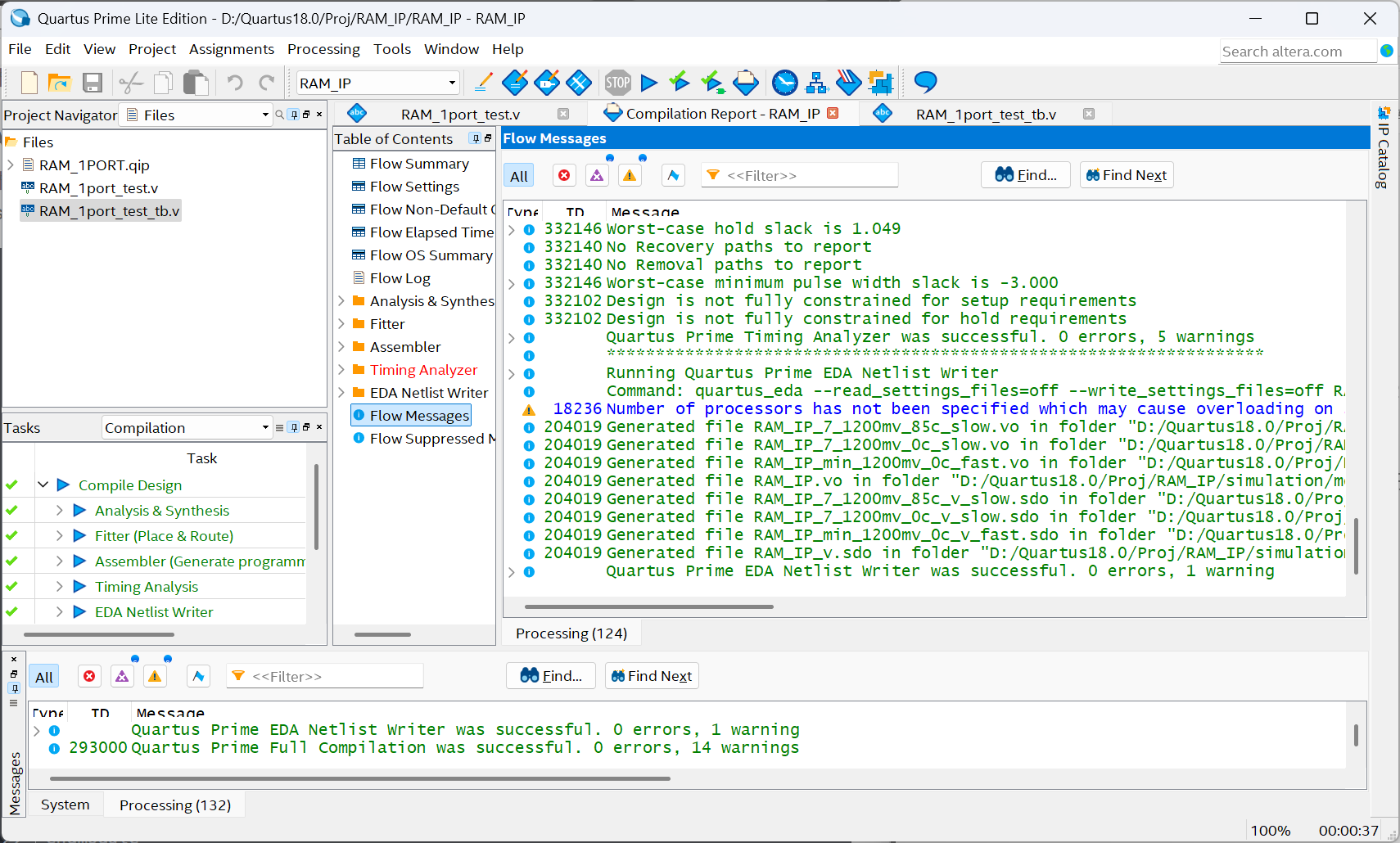

第二节 配置RAM_1PORT

- 新建Verilog HDL File,写入模型的代码

module RAM_1port_test(input clk ,//时钟信号input rst_n ,//上电复位低有效input rden ,input wren ,input [7:0] address ,input [7:0] data ,output [7:0] q

);//RAM_1portRAM_1PORT RAM_1PORT_inst (.aclr ( ~rst_n ),.address ( address ),.clock ( clk ),.data ( data ),.rden ( rden ),.wren ( wren ),.q ( q ));

endmodule以及测试的代码

`timescale 1ns/1ps

module RAM_1port_test_tb();reg clk ;reg rst_n ;reg rden ;reg wren ;reg [7:0] address ;reg [7:0] data ;wire [7:0] q ;//例化要仿真的文件

RAM_1port_test u_RAM_1port_test(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.rden (rden ),.wren (wren ),.address (address ),.data (data ),.q (q )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位

//RAM_1PORTwren = 1'b0;//复位有效,赋初值rden = 1'b0;data = 0;address = 0;#200;rst_n = 1'b1;#200;//wren 50Mfor(i=0;i<256;i=i+1)beginwren = 1'b1;//高电平有效address = i;data = i+1;#20;endwren = 1'b0;//写完拉低#100;//rden 100Mfor(j=0;j<256;j=j+1)beginrden = 1'b1;address = j;#20;endrden = 1'b0;//读完拉低#200;$stop;

endendmodule- 完全编译

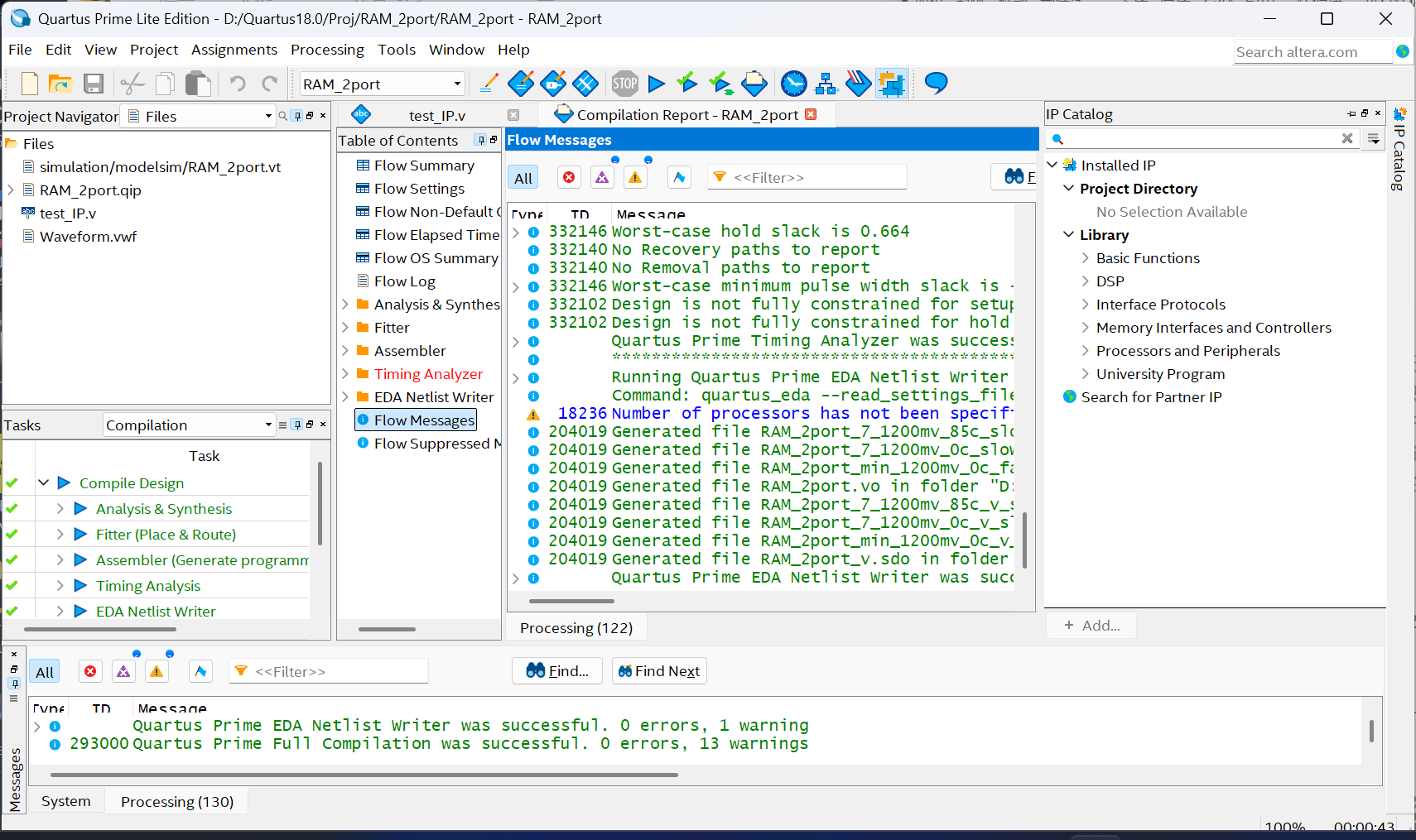

第三节 RAM_2PORT的调用

- 同样,找到RAM_2PORT并添加,保存为

RAM_2port.v

- 配置读写模块

- 配置数据深度为1024

- 选择读写时钟分开

- 读出数据设置为q,同样选择复位清零

- 多次点击next直到出现此界面,选择

RAM_2port_inst.v及RAM_2port_bb.v

第四节 配置RAM_2PORT

- 同样编译模型代码和测试代码

test_IP.v

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input [7:0] data ,input [7:0] rdaddress ,input rden ,input [7:0] wraddress ,input wrclock ,input wren ,output [7:0] q);// //RAM_2portRAM_2port RAM_2port_inst (.data ( data ),.rd_aclr ( ~rst_n ),.rdaddress ( rdaddress ),.rdclock ( clk ),.rden ( rden ),.wraddress ( wraddress ),.wrclock ( wrclock ),.wren ( wren ),.q ( q ));endmodule测试代码test_tb.v

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;reg [7:0] data ;reg [7:0] rdaddress ;reg rden ;reg [7:0] wraddress ;reg wrclock ;reg wren ;wire [7:0] q ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.data (data ),.rdaddress (rdaddress ),.rden (rden ),.wraddress (wraddress ),.wrclock (clk ),.wren (wren ),.q (q )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位wren = 1'b0;//复位有效,赋初值rden = 1'b0;rdaddress = 0;wraddress = 0;data = 0;#200;rst_n = 1'b1;#200;//wren 50Mfor(i=0;i<256;i=i+1)beginwren = 1'b1;//高电平有效wraddress = i;data = i+1;#20;endwren = 1'b0;//写完拉低#100;//rden 100Mfor(j=0;j<256;j=j+1)beginrden = 1'b1;rdaddress = j;#20;endrden = 1'b0;//读完拉低#200;$stop;

endendmodule- 完整编译通过

第五章 什么是FIFO?

FIFO( First Input First Output)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采集、高速数据处理、高速数据传输以及多机处理系统中得到越来越广泛的应用。[5]

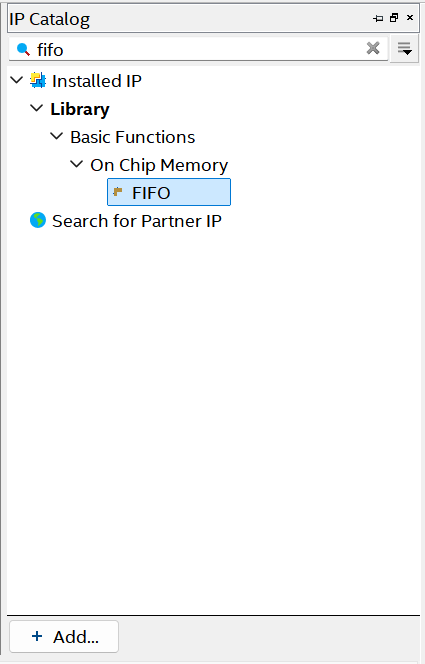

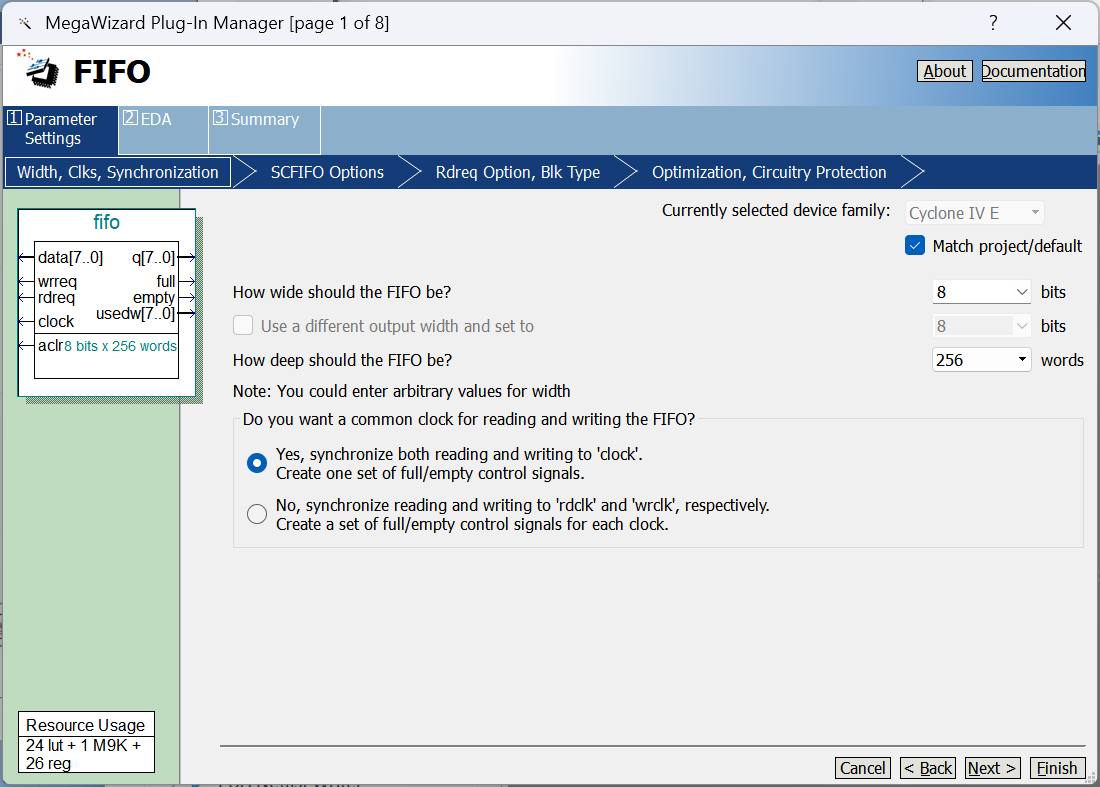

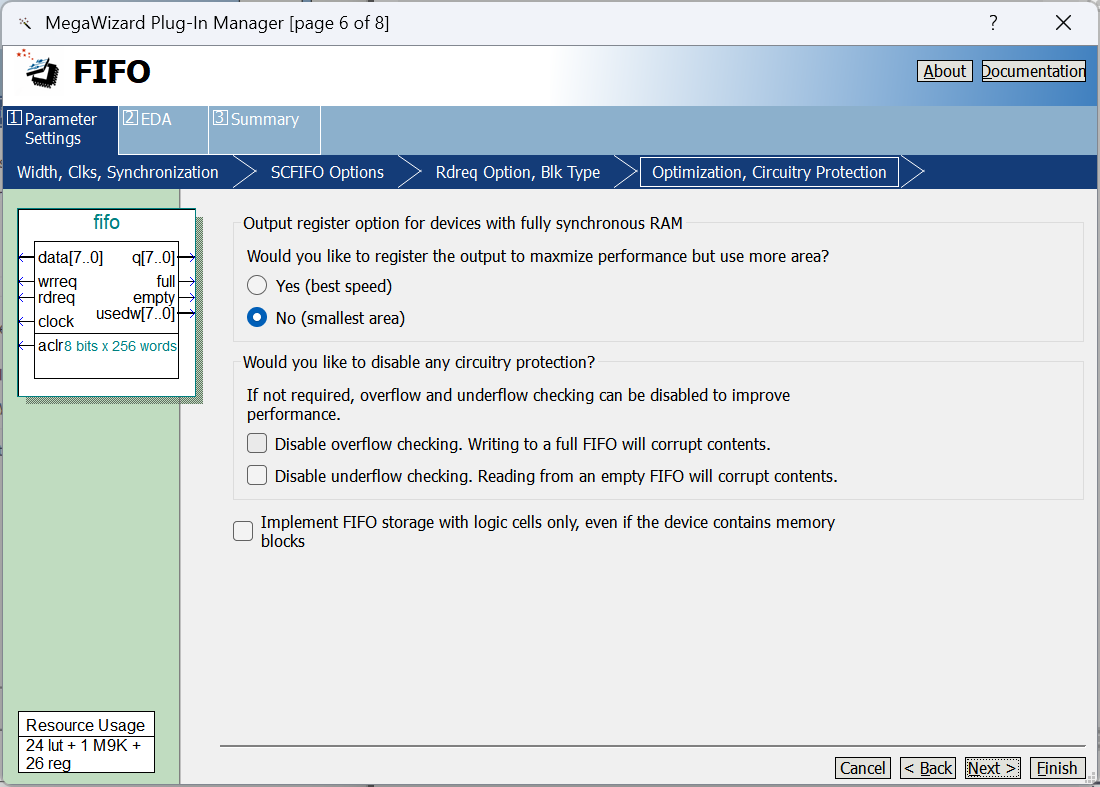

第一节 FIFO模块参数配置

1.在IP Catelog搜索FIFO,选择FIFO并添加,保存为fifo.v

- 选择读写使用同一个时钟

- 配置SCFIFO

- 默认即可,点击next

- 默认即可

- 勾选

fifo_inst.v和fifo_bb.v

第二节 配置FIFO

- 与前面相同,新建Verilog HDL File,写入如下代码并保存

模型代码:

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input [7:0] data ,input rdreq ,input wrreq ,output empty ,output full ,output [7:0] q ,output [7:0] usedw );// //FIFOfifo fifo_inst (.aclr ( ~rst_n ),.clock ( clk ),.data ( data ),.rdreq ( rdreq ),.wrreq ( wrreq ),.empty ( empty ),.full ( full ),.q ( q ),.usedw ( usedw ));

endmodule测试代码:

`timescale 1ns/1ps

module test_tb();reg clk ;reg rst_n ;reg wrreq ;reg rdreq ;reg [7:0] data ;wire [7:0] q ;wire empty ;wire full ;wire usedw ;//例化要仿真的文件

test_IP u_test_IP(.clk (clk ),//时钟信号.rst_n (rst_n ),//上电复位低有效.data (data ),.rdreq (rdreq ),.wrreq (wrreq ),.empty (empty ), .full (full ), .q (q ), .usedw (usedw )

);always #10 clk = ~clk;//产生50M仿真时钟integer i = 0,j = 0;//用于产生地址,写入数据initial beginclk = 1'b1;rst_n = 1'b1;#200.1;rst_n = 1'b0;//主动产生上电复位rdreq = 1'b0;wrreq = 1'b0;data = 0;#200;rst_n = 1'b1;#200;//wrreq 50Mfor(i=0;i<256;i=i+1)beginwrreq = 1'b1;//高电平有效data = {$random};#20;endwrreq = 1'b0;//写完拉低#100;//rdreq 100Mfor(j=0;j<256;j=j+1)beginrdreq = 1'b1;#20;endrdreq = 1'b0;#200;$stop;

endendmodule- 全部编译通过

参考文献

[1] 潘松·EDA技术与Verilog HDL·北京:清华大学出版社,2010

[2] LPM(FPGA参数化模块库) -百度百科

[3] 锁相环(无线电术语)-百度百科

[4] 杨颂华,冯毛官,孙万蓉,初秀琴,胡力山编著·数字电子技术基础:西安电子科技大学出版社,2016.07

[5] FIFO存储器 -百度百科

[6] Quartus基本IP核调用及仿真

[7] 罗杰.Verilog HDL 与FPGA数字系统设计 第二版[M].机械工业出版社:北京,2022:198-210.

相关文章:

Quartus II的IP核调用及仿真测试

目录 第一章 什么是IP核?第二章 什么是LPM?第一节 设置LPM_COUNTER模块参数第二节 仿真 第三章 什么是PLL?第一节 设置ALTPLL(嵌入式锁相环)模块参数第二节 仿真 第四章 什么是RAM?第一节 RAM_1PORT的调用第…...

JDK(Java Development Kit)从发布至今所有主要版本 的详细差异、新增特性及关键更新的总结,按时间顺序排列

以下是 JDK(Java Development Kit)从发布至今所有主要版本 的详细差异、新增特性及关键更新的总结,按时间顺序排列: 1. JDK 1.0 (1996) 发布年份:1996年1月23日关键特性: Java首次正式发布。核心语言特性…...

Vue 3 和 Vue 2 的区别及优点

Vue.js 是一个流行的 JavaScript 框架,广泛用于构建用户界面和单页应用。自 Vue 3 发布以来,很多开发者开始探索 Vue 3 相较于 Vue 2 的新特性和优势。Vue 3 引入了许多改进,优化了性能、增强了功能、提升了开发体验。本文将详细介绍 Vue 2 和…...

Linux 入门五:Makefile—— 从手动编译到工程自动化的蜕变

一、概述:Makefile—— 工程编译的 “智能指挥官” 1. 为什么需要 Makefile? 手动编译的痛点:当工程包含数十个源文件时,每次修改都需重复输入冗长的编译命令(如gcc file1.c file2.c -o app),…...

通过websocket给服务端发送订单催单提醒消息

controller层 GetMapping("/reminder/{id}")public Result Remainder(PathVariable("id") Long id){orderService.remainder(id);return Result.success();} 实现类 Overridepublic void remainder(Long id) {Orders ordersDB orderMapper.getById(id);…...

【NumPy科学计算:高性能数组操作核心指南】

目录 前言:技术背景与价值当前技术痛点解决方案概述目标读者说明 一、技术原理剖析核心概念图解关键技术模块技术选型对比 二、实战演示环境配置要求核心代码实现运行结果验证 三、性能对比测试方法论量化数据对比结果分析 四、最佳实践推荐方案 ✅常见错误 ❌调试技…...

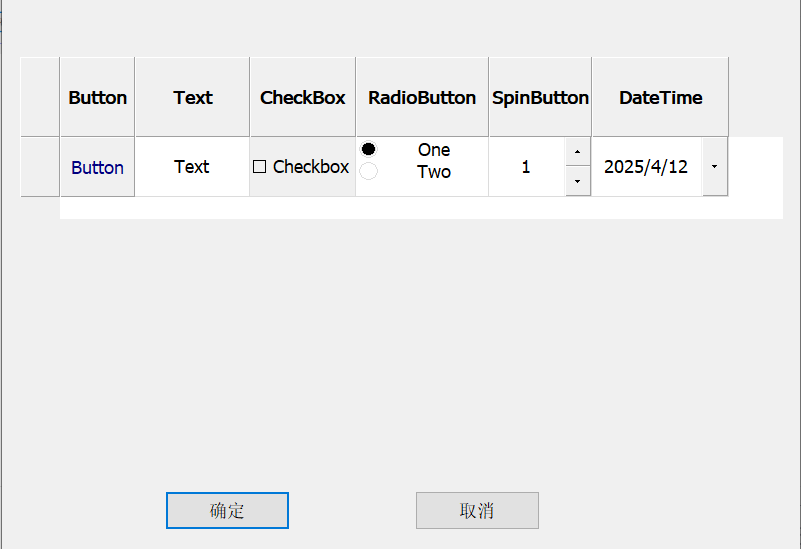

c++ 表格控件 UltimateGrid 控件实例

控件区域: 使用效果: 代码如下: void MyUGCtrl::OnSetup() { m_nButtonIndex AddCellType(&m_button); SetNumberCols(6); AppendRow(); CUGCell cell; int rows, cols; int row 0; // 头部 int nHeaderRow -1; …...

从单机版到超级APP:MCP如何解锁AI的超能力

MCP:AI界的“万能充电宝”——让AI从此告别“语言不通”的尴尬! 开篇:AI咖啡馆的尴尬日常 想象一下这样的场景: 一位AI助手在咖啡馆里手忙脚乱——它想帮用户点杯咖啡,但需要先写代码调用天气API(“今天下…...

【算法】 欧拉函数与欧拉降幂 python

欧拉函数 欧拉函数 ϕ ( n ) \phi(n) ϕ(n) 表示小于等于 n 的正整数中与 n 互质的数的个数。即: ϕ ( n ) ∣ { k ∈ Z ∣ 1 ≤ k ≤ n , gcd ( k , n ) 1 } ∣ \phi(n) \left| \{ k \in \mathbb{Z}^ \mid 1 \leq k \leq n, \gcd(k, n) 1 \} \right| ϕ(n)…...

【Python] pip制作离线包

制作离线安装包是一种非常实用的方法,尤其是在网络环境受限或需要在多台机器上部署相同环境时。以下是详细的步骤,帮助您创建一个包含所有依赖项的离线安装包,并在后续环境中复用。 步骤 1:准备工具和环境 确保您有一台可以访问互…...

什么是回表?哪些数据库存在回表?

目录 一、什么是回表1. 回表的核心流程2. 示例说明3. 回表的性能问题4. 总结 二、哪些数据库会有回表1. MySQL(InnoDB)2. Oracle3. 其他数据库(如 SQL Server、PostgreSQL)4. 总结 三、非聚集索引与聚集索引的区别及产生原因1. 聚…...

linux 内存踩踏导致的空指针问题分析纪要

1,查看日志信息打印 我们看到日志发现发包的skb模块有NULL pointer情况,我们看代码分析skb指针不可能出现是空指针,这个时候我们怀疑可能是出现了踩内存导致的空指针情况,所以我们首先需要找到系统PANIC的条件,也就是…...

使用 VcXsrv 在 Windows 10 上运行 Ubuntu 图形界面

VcXsrv 是一款用于 Windows 的开源 X 服务器,它允许在 Windows 系统上显示 Linux 的图形应用程序。当在 Windows 10 上安装并正确配置 VcXsrv 后,通过设置 WSL2 中的DISPLAY环境变量,使其指向运行 VcXsrv 的 Windows 主机的 IP 地址ÿ…...

LSTM-SVM长短期记忆神经网络结合支持向量机组合模型多特征分类预测/故障诊断,适合新手小白研究学习(Matlab完整源码和数据)

LSTM-SVM长短期记忆神经网络结合支持向量机组合模型多特征分类预测/故障诊断,适合新手小白研究学习(Matlab完整源码和数据) 目录 LSTM-SVM长短期记忆神经网络结合支持向量机组合模型多特征分类预测/故障诊断,适合新手小白研究学习…...

Autoware源码总结

Autoware源码网站 项目简介 教程 Autoware的整体架构如下图,主要包括传感器sensing、高精地图map data、车辆接口vehicle interface、感知perception(动态障碍物检测detection、跟踪tracking、预测prediction;交通信号灯检测detection、分类c…...

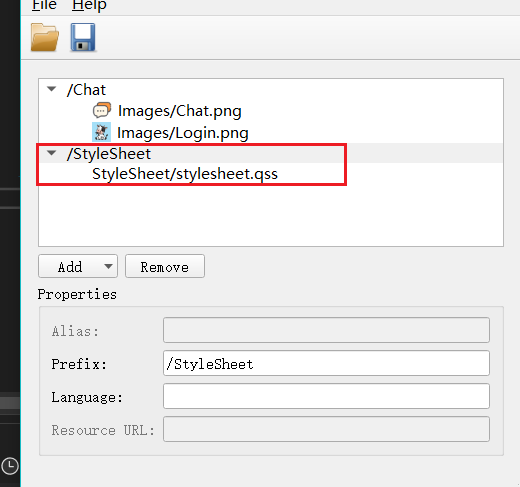

QT聊天项目DAY01

1.新建初始项目 2.修改UI格式 运行效果 3.创建登录界面 设计登录界面UI 设计布局 调整布局间距 往水平布局中拖入标签和文本输入框 更换控件名称并固定高度 添加窗口部件 往现有的资源文件中导入图片 添加水平布局 4.设置登陆界面为主窗口的核心组件 #pragma once#include &l…...

【NumPy科学计算引擎:从基础操作到高性能实践】

目录 前言:技术背景与价值当前技术痛点解决方案概述目标读者说明 一、技术原理剖析关键技术模块说明技术选型对比 二、实战演示环境配置核心代码实现运行结果验证 三、性能对比测试方法论量化数据对比结果分析 四、最佳实践推荐方案 ✅常见错误 ❌调试技巧 五、应用…...

MySQL InnoDB 索引与B+树面试题20道

1. B树和B+树的区别是什么? 数据存储位置: B树:所有节点(包括内部节点和叶子节点)均存储数据。 B+树:仅叶子节点存储数据,内部节点仅存储键值(索引)。 叶子节点结构: B+树:叶子节点通过双向链表连接,支持高效的范围查询。 查询稳定性: B+树:所有查询必须走到叶子…...

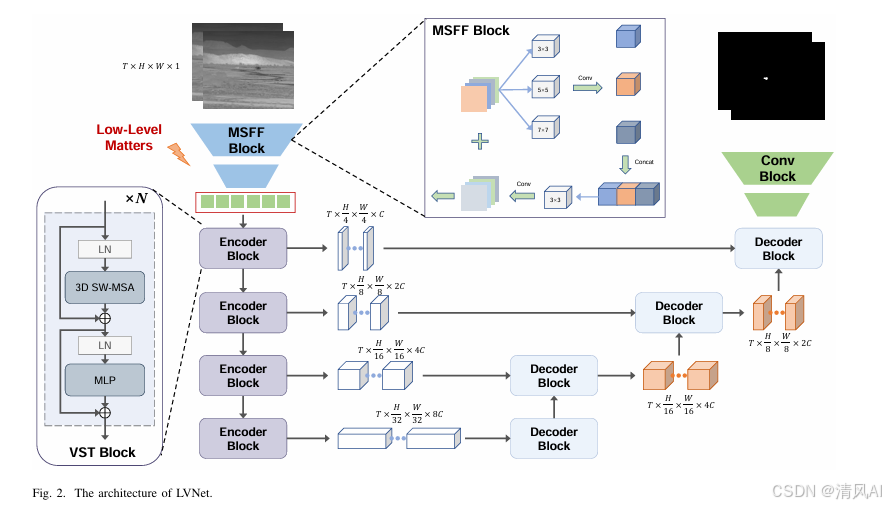

论文精度:基于LVNet的高效混合架构:多帧红外小目标检测新突破

论文地址:https://arxiv.org/pdf/2503.02220 目录 一、论文背景与结构 1.1 研究背景 1.2 论文结构 二、核心创新点解读 2.1 三大创新突破 2.2 创新结构原理 2.2.1 多尺度CNN前端 2.2.2 视频Transformer设计 三、代码复现指南 3.1 环境配置 3.2 数据集准备 3.3 训…...

ORM查询的补充

一,ORM查询的补充: 1,连接查询: 反向查询: 先介绍一下什么是正向查询,比如我们之前的数据表之间建立的一对多的关系,我们通过文章找到相应的作者是属于正向查询的(由多到一)&…...

【C语言-全局变量】

【C语言-全局变量】 1.能局部就局部,别啥都往全局塞2.尽量用结构体对零散变量封装3.函数传参4.静态变量模块化5 单例模式, 限制全局实例数量6. 配置化全局参数——集中管理可调参数7. 事件驱动架构:消息队列通信策略选择建议 参考https://mp.weixin.qq.c…...

mysql 商城商品属性开发的动态解决方案

终极方案:动态属性解决方案 推荐使用 JSON 字段 虚拟列索引 的组合方案 结合灵活存储与查询优化,平衡扩展性与性能 完整实现步骤 步骤 1:创建基础表结构 CREATE TABLE products (id INT PRIMARY KEY AUTO_INCREMENT,name VARCHAR(100) NO…...

python利用open-cv和SSIM和特征值比较两个图片的相似性

以下是关于 **SSIM(结构相似性指数)** 和 **特征匹配** 的详细解释及实际示例,帮助理解它们的区别和应用场景: --- ### **1. SSIM(结构相似性指数)** #### **含义**: - **SSIM** 是一种衡量两…...

蔚来汽车智能座舱接入通义大模型,并使用通义灵码全面提效

为加速AI应用在企业市场落地,4月9日,阿里云在北京召开AI势能大会。阿里云智能集团资深副总裁、公共云事业部总裁刘伟光发表主题演讲,大模型的社会价值正在企业市场释放,阿里云将坚定投入,打造全栈领先的技术࿰…...

QT 老版本下载地址被禁 如何下载

前提: 想用老版本的QT 5.12 系列,但是QT官方已经封禁了国内IP 访问,5.15之前的版本,而且5.14.2是最后一个离线exe版本 ; Index of /official_releases/qt 基本不可用;全部改为在线安装; 收集了一下地址&am…...

VMWare Workstation Pro17.6最新版虚拟机详细安装教程(附安装包教程)

目录 前言 一、VMWare虚拟机下载 二、VMWare虚拟机安装 三、运行虚拟机 前言 VMware 是全球领先的虚拟化技术与云计算解决方案提供商,通过软件模拟计算机硬件环境,允许用户在一台物理设备上运行多个独立的虚拟操作系统或应用。其核心技术可提升硬件…...

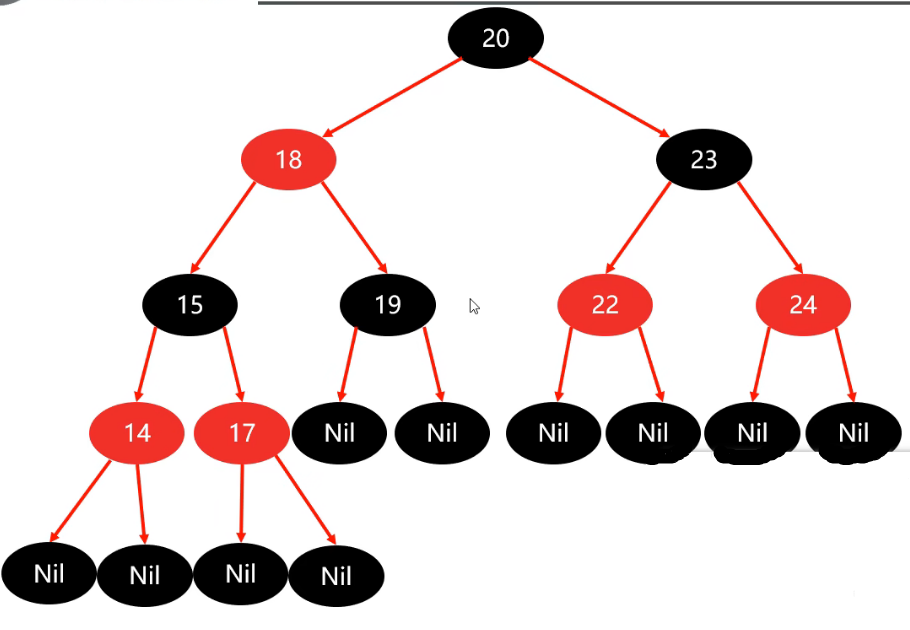

【数据结构】红黑树超详解 ---一篇通关红黑树原理(含源码解析+动态构建红黑树)

一.什么是红黑树 红黑树是一种自平衡的二叉查找树,是计算机科学中用到的一种数据结构。1972年出现,最初被称为平衡二叉B树。1978年更名为“红黑树”。是一种特殊的二叉查找树,红黑树的每一个节点上都有存储表示节点的颜色。每一个节点可以是…...

uni-app初学

文章目录 1. pages.json 页面路由2. 图标3. 全局 CSS4. 首页4.1 整体框架4.2 完整代码4.3 轮播图 swiper4.3.1 image 4.4 公告4.4.1 uni-icons 4.5 分类 uni-row、uni-col4.6 商品列表 uni-row、uni-col 小程序开发网址: 注册小程序账号 微信开发者工具下载 uniapp …...

PHP多维数组

在 PHP 中,多维数组是数组的数组,允许你存储和处理更复杂的数据结构。多维数组可以有任意数量的维度,但通常我们最常用的是二维数组(数组中的数组)。 首先来介绍一下一维数组, <?php//一维数组 $strAr…...

数学建模:针对汽车行驶工况构建思路的延伸应用

前言: 汽车行驶工况构建的思简单理解为将采集的大量数据进行“去除干扰、数据处理,缩减至1800S的数据”,并可达到等效替换的目的,可以使在试验室快速复现;相应的解决思路、办法可应用在 “通过能量流采集设备大量采集…...