【HDLBits刷题】Verilog Language——1.Basics

目录

一、题目与题解

1.Simple wire(简单导线)

2.Four wires(4线)

3.Inverter(逆变器(非门))

4.AND gate (与门)

5. NOR gate (或非门)

6. XNOR gate(异或非(同或)门)

7.Declaring wires(声明导线)

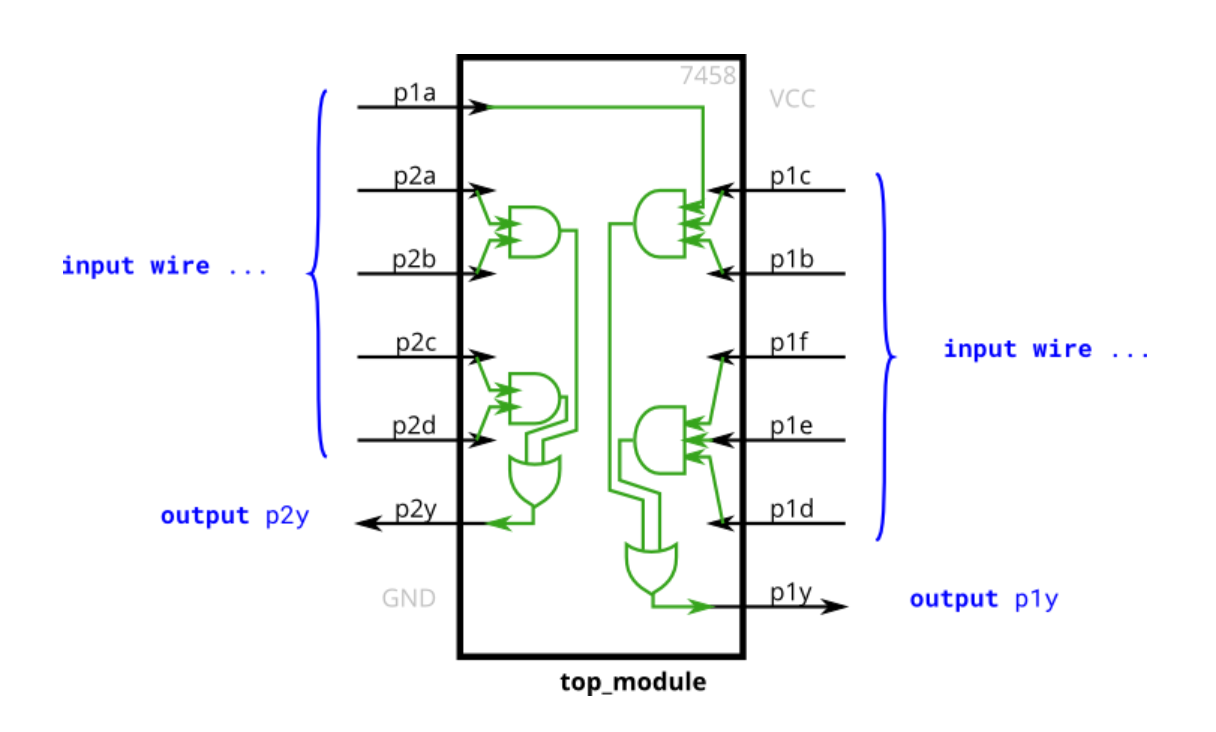

8.7458 chip( 7458芯片)

二、杂谈

1.新的数据类型:wire

2.串联运算符:{}

3.逻辑运算符

4.同或的表示方法

一、题目与题解

1.Simple wire(简单导线)

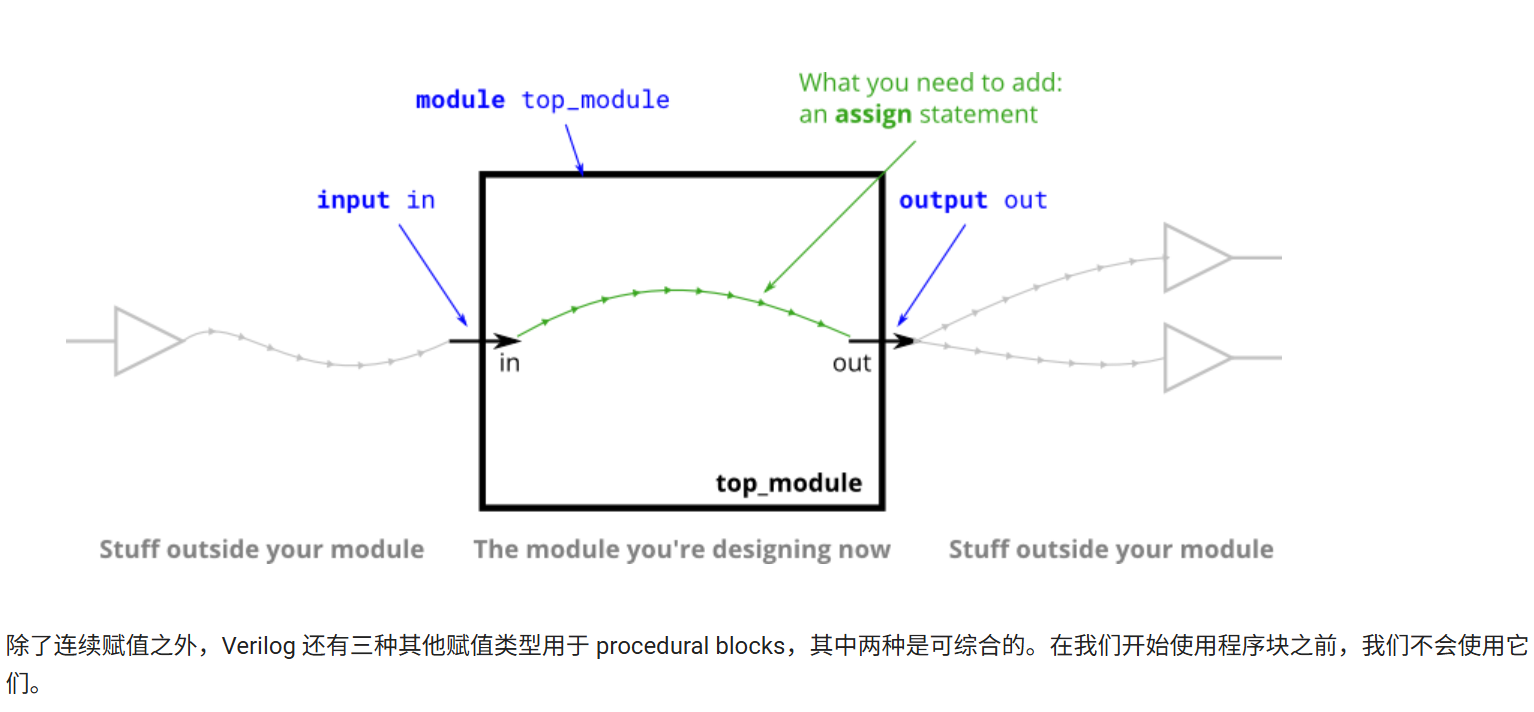

创建一个具有一个 input 和一个 output 的模块,其行为类似于一条线。

与物理电线不同,Verilog 中的电线(和其他信号)是定向的 。这意味着信息仅沿一个方向流动,从 (通常一个) 源流向接收器 (源通常也称为驱动器 ,将值驱动到线路上) 。在 Verilog 的 “continuous assignment” (

assign left_side = right_side;) 中,右侧的信号值被驱动到左侧的导线上。赋值是 “continuous” 的,因为即使右侧的值发生变化,赋值也会一直继续。连续分配不是一次性事件。模块上的端口也有一个方向(通常是输入或输出)。输入端口由模块外部的东西驱动,而输出端口则驱动外部的东西。从模块内部查看时,输入端口是驱动器或源,而输出端口是接收器。

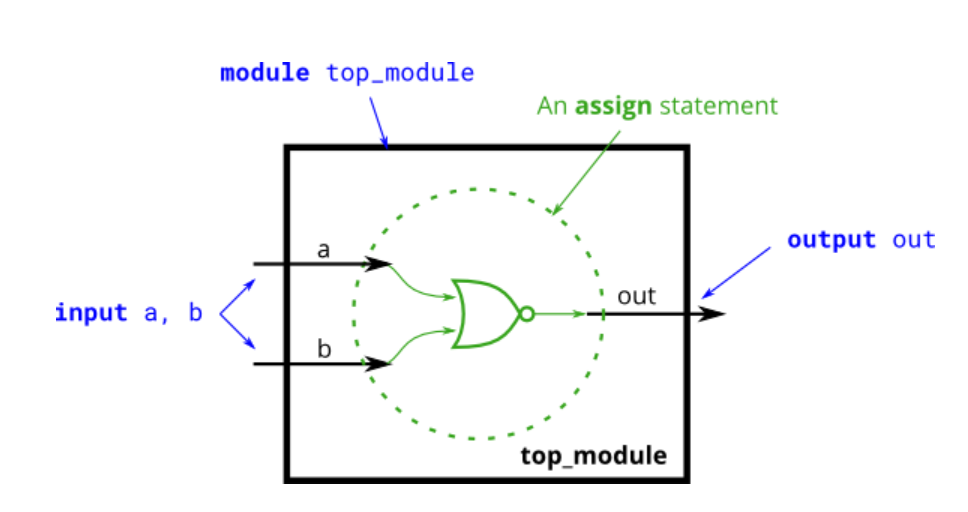

下图说明了电路的每个部分如何对应于Verilog代码的每个位。模块和端口声明创建电路的黑色部分。您的任务是通过添加要连接到 的语句来创建一条线路(绿色)。开箱即用的部件不是您关心的问题,但您应该知道,通过将测试线束的信号连接到顶部_模块的端口,可以测试您的电路。

module top_module( input in, output out );assign out = in;

endmodule2.Four wires(4线)

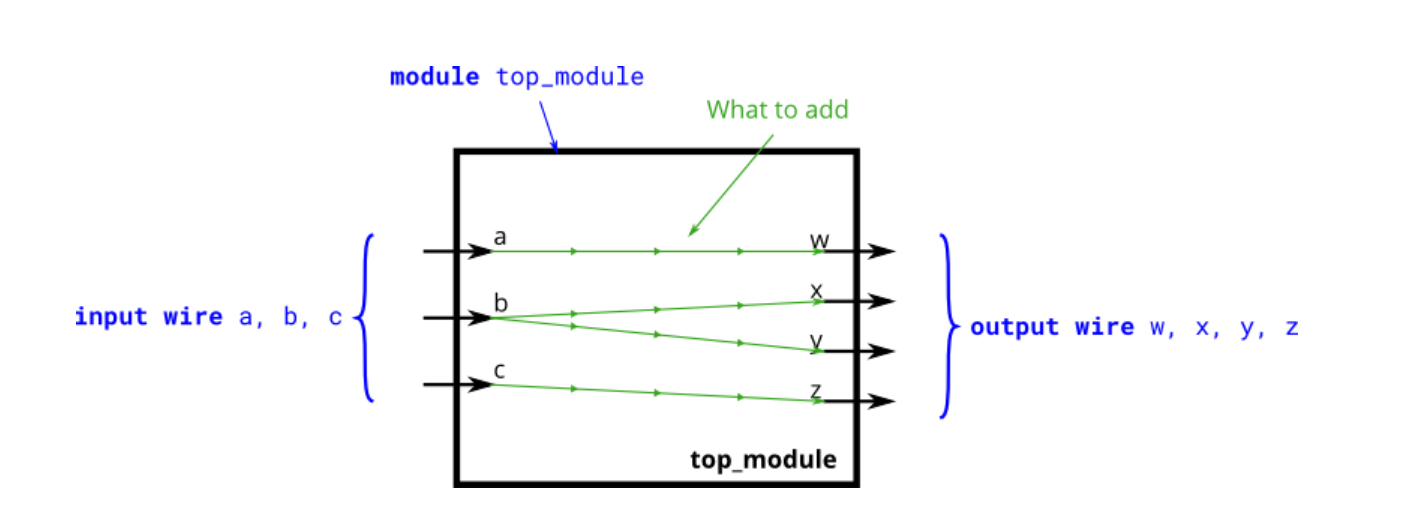

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于进行以下连接的电线:

a -> w b -> x b -> y c -> z下图说明了 circuit 的每个部分如何对应于 Verilog 代码的每个位。从模块外部,有三个输入端口和四个输出端口。

当您有多个 assign 语句时,它们在代码中出现的顺序无关紧要。与编程语言不同, assign 语句(“连续赋值”)描述事物之间的连接 ,而不是将值从一个事物复制到另一个事物的操作 。

现在也许应该澄清一个潜在的混淆来源:这里的绿色箭头代表电线之间的连接,但本身不是电线。该模块本身已经声明了 7 条电线(名为 a、b、c、w、x、y 和 z)。这是因为

input和output声明实际上声明了一个连线,除非另有指定。写入输入线 a与写入 a相同。因此,assign语句不是在创建电线,而是在已经存在的 7 条电线之间创建连接。

module top_module( input a,b,c,output w,x,y,z );assign w = a;assign x = b,y = b;assign z = c;//如果我们确定每个信号的宽度,使用//串联运算符等效且更短://assign {w,x,y,z}={a,b,b,c};

endmodule3.Inverter(逆变器(非门))

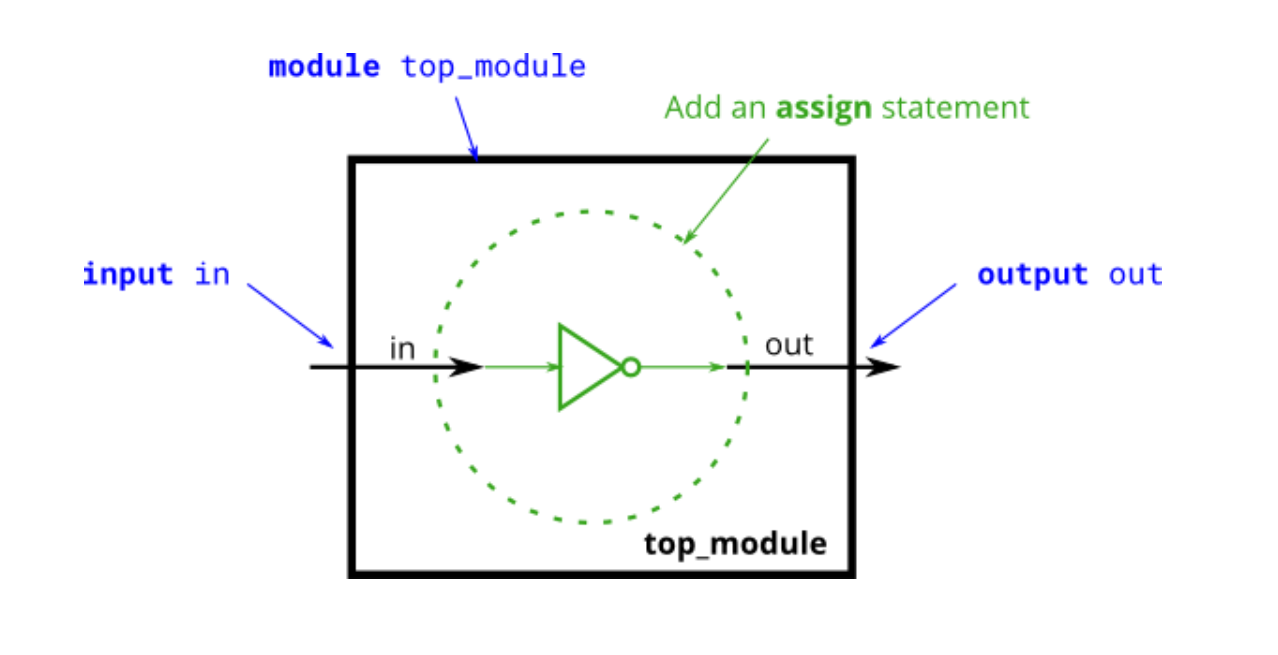

创建一个实现 NOT 门的模块。该电路类似于线,但略有不同。当从电线连接到电线时,我们将实现逆变器(或者"非门")而不是普通电线。使用assign语句。assign语句将持续将in的非转换为out。

module top_module( input in, output out );assign out = ~in;

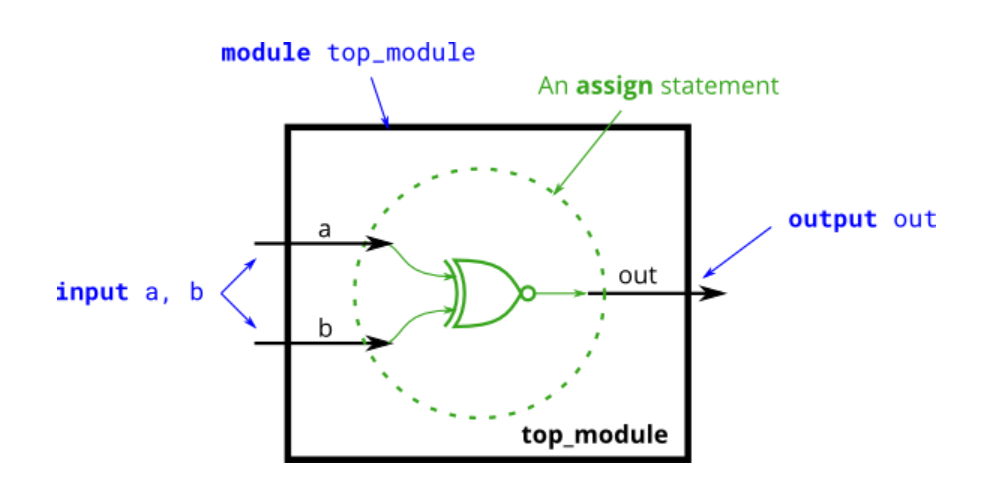

endmodule4.AND gate (与门)

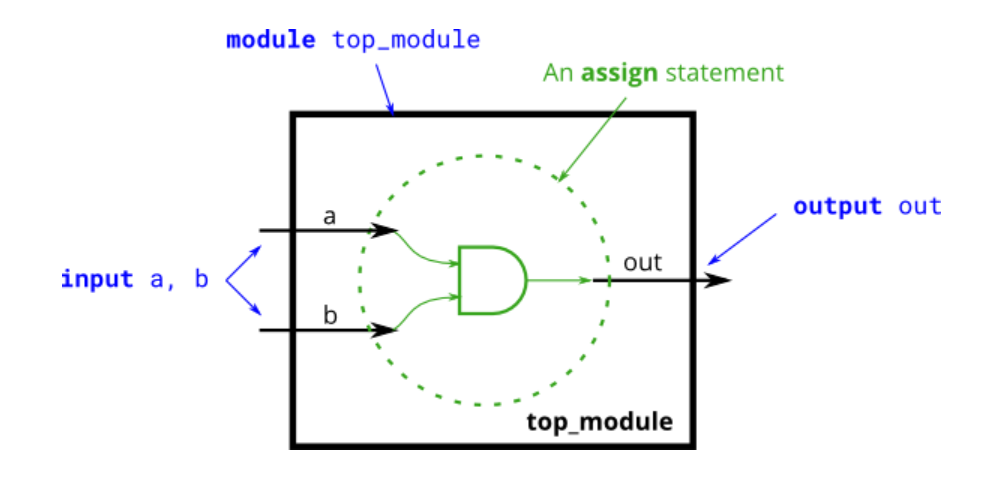

创建实现 AND 门的模块。

该电路现在有三条导线(a、b和out)。导线a和b已经具有由输入端口驱动的值。但wire out目前并不是由任何因素驱动的。写一个assign语句,用a和b的AND信号输出。

请注意,该电路与NOT门非常相似,只是多了一个输入。如果听起来不一样,那是因为我已经开始描述信号是被驱动的(已知值由附加到它的某个东西决定)还是不是被某个东西驱动的。输入线由模块外部的东西驱动。assign语句将把一个逻辑电平驱动到一条线上。正如您所料,一条导线不能有多个驱动器(如果有,其逻辑级别是多少?),没有驱动程序的导线将有一个未定义的值(在合成硬件时通常被视为0)。

module top_module( input a, input b, output out );assign out = a & b;

endmodule5. NOR gate (或非门)

创建一个实现或非门的模块。或非门是输出反转的或门。在Verilog中编写NOR函数时需要两个运算符。

assign语句用一个值驱动一条线(或者更正式地称为“网”)。该值可以是任意复杂的函数,只要它是组合函数(即无内存、无隐藏状态)。assign语句是一种连续赋值,因为每当其任何输入发生变化时,都会“重新计算”输出,就像一个简单的逻辑门一样

module top_module( input a, input b, output out );assign out = ~(a | b);

endmodule6. XNOR gate(异或非(同或)门)

创建一个实现 XNOR 门的模块。

module top_module( input a, input b, output out );//assign out = a ~^ b;a和b相同输出0,不同输出1//assign out = a ^~ b;assign out = ~(a ^ b);

endmodule7.Declaring wires(声明导线)

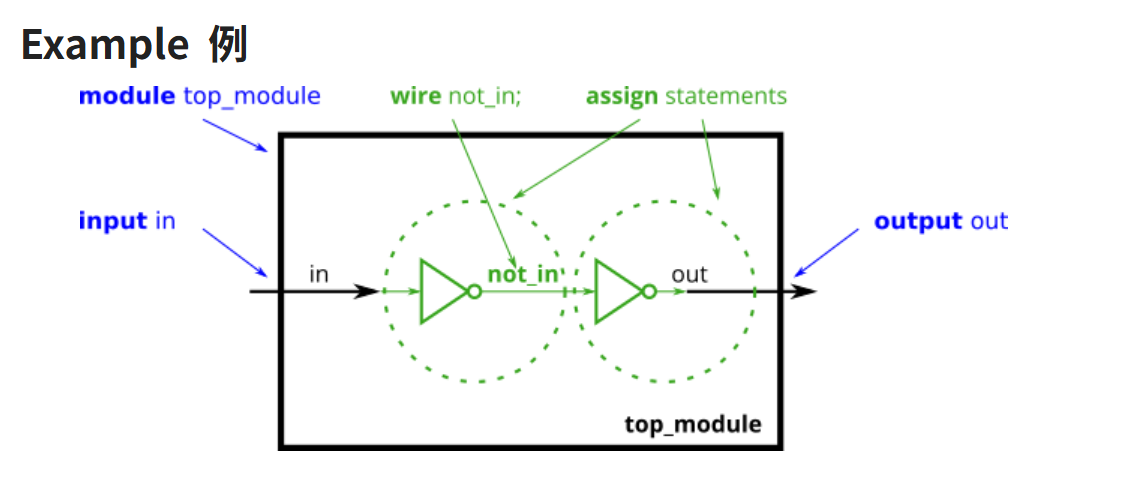

到目前为止,电路已经足够简单,以至于 output 是 inputs 的简单函数。随着电路变得越来越复杂,您将需要电线将内部组件连接在一起。当你需要使用 wire 时,你应该在 module 的主体中声明它,在它第一次使用之前的某个地方。(将来,您将遇到更多类型的信号和变量,它们也以相同的方式声明,但现在,我们将从 type 为 wire 的信号 ) 开始。

module top_module (input in, // Declare an input wire named "in"output out // Declare an output wire named "out" );wire not_in; // Declare a wire named "not_in"assign out = ~not_in; // Assign a value to out (create a NOT gate).assign not_in = ~in; // Assign a value to not_in (create another NOT gate).endmodule // End of module "top_module"在上面的模块中,有三根电线 ( in , out , 和 not_in ),其中两根已经声明为模块的输入和输出端口的一部分(这就是为什么你在前面的练习中不需要声明任何电线的原因)。需要在 module 内部声明 wire not_in 。从模块外部不可见。然后,使用两个 assign 语句创建两个 NOT 门。请注意,您首先创建哪个 NOT 门并不重要:您最终仍然会得到相同的电路。

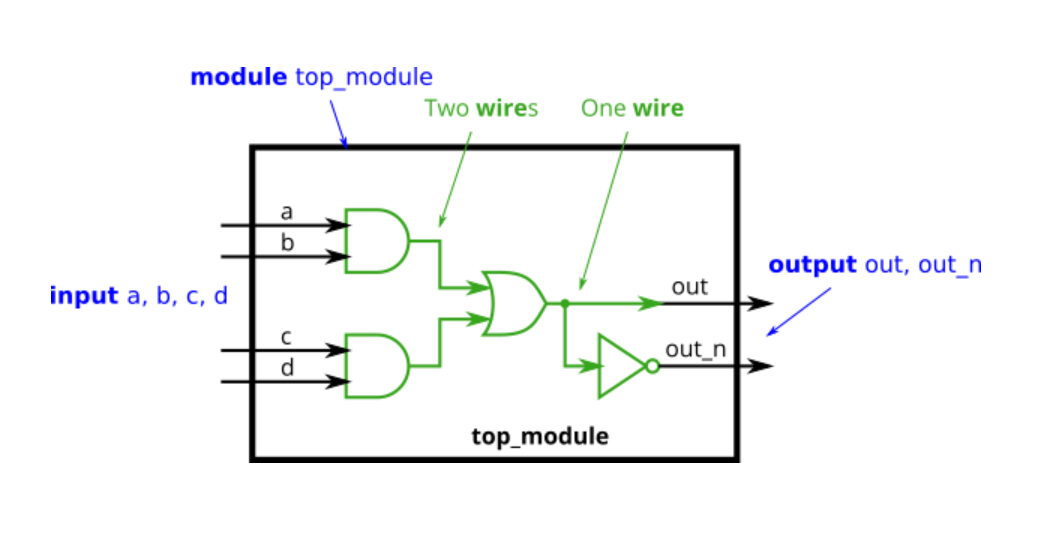

实现以下电路。创建两条中间线(命名您想要的任何名称)以将 AND 和 OR 门连接在一起。请注意,馈送 NOT 门的 wire 实际上是 wire out ,因此您不一定需要在此处声明第三根 wire 。请注意 wires 是如何由一个 source (gate 的 output) 驱动的,但可以馈送多个 inputs。

如果您遵循图中的电路结构,则最终应该有四个 assign 语句,因为有四个信号需要赋值。

module top_module (input a,input b,input c,input d,output out,output out_n );wire w1, w2; // Declare two wires (named w1 and w2)assign w1 = a&b; // First AND gateassign w2 = c&d; // Second AND gateassign out = w1|w2; // OR gate: Feeds both 'out' and the NOT gateassign out_n = ~out; // NOT gateendmodule8.7458 chip( 7458芯片)

7458 是一款具有 4 个 AND 门和 2 个 OR 门的芯片。此问题比 7420 稍微复杂一些。

创建与 7458 芯片具有相同功能的模块。它有 10 个输入和 2 个输出。您可以选择使用

assign语句来驱动每根输出线,也可以选择声明 (four) 线用作中间信号,其中每根内部线都由其中一个 AND 门的输出驱动。如需额外练习,请尝试两种方式。

module top_module ( input p1a, p1b, p1c, p1d, p1e, p1f,output p1y,input p2a, p2b, p2c, p2d,output p2y );//第一种方法assign p2y = (p2a & p2b) | (p2c & p2d);assign p1y = (p1a & p1c & p1b) | (p1f & p1e & p1d);//第二种方法wire a,b,c,d;assign a = p2a & p2b;assign b = p2c & p2d;assign p2y = a | b;assign c = p1a & p1c & p1b;assign d = p1f & p1e & p1d;assign p1y = c | d;

endmodule二、杂谈

1.新的数据类型:wire

2.串联运算符:{}

assign {w, x, y, z} = {a, b, b, c};

可实现一对一的赋值

3.逻辑运算符

&与

|或

~非

^异或

4.同或的表示方法

~ (a ^ b) == (a ^~ b) == (a ~^ b)

相关文章:

【HDLBits刷题】Verilog Language——1.Basics

目录 一、题目与题解 1.Simple wire(简单导线) 2.Four wires(4线) 3.Inverter(逆变器(非门)) 4.AND gate (与门) 5. NOR gate (或非门&am…...

SCDN是什么?

SCDN是安全内容分发网络的简称,它在传统内容分发网络(CDN)的基础上,集成了安全防护能力,旨在同时提升内容传输速度和网络安全性。 SCDN的核心功能有: DDoS防御:识别并抵御大规模分布式拒绝服务…...

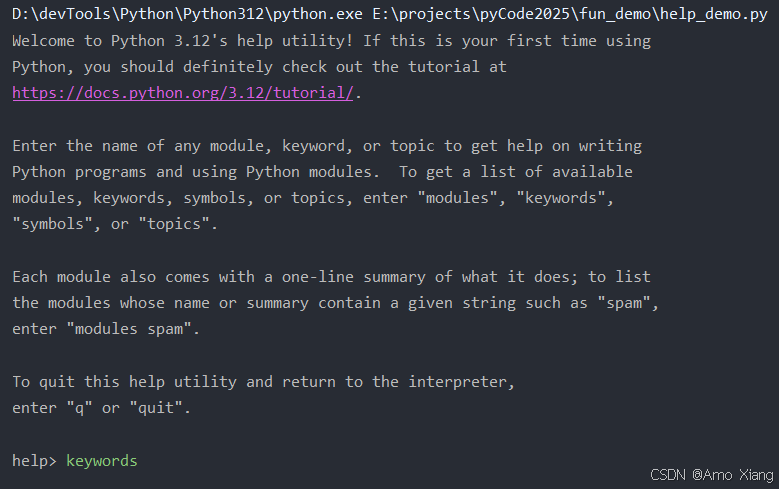

Python 常用内置函数详解(十):help()函数——查看对象的帮助信息

目录 一、语法参考二、示例 一、语法参考 help() 函数的语法格式如下: 参数说明: request:可选参数,要查看其帮助信息的对象,如类、函数、模块、数据类型等;返回值:返回对象的帮助信息。 二…...

【Python系列】Python 中的 HTTP 请求处理

💝💝💝欢迎来到我的博客,很高兴能够在这里和您见面!希望您在这里可以感受到一份轻松愉快的氛围,不仅可以获得有趣的内容和知识,也可以畅所欲言、分享您的想法和见解。 推荐:kwan 的首页,持续学…...

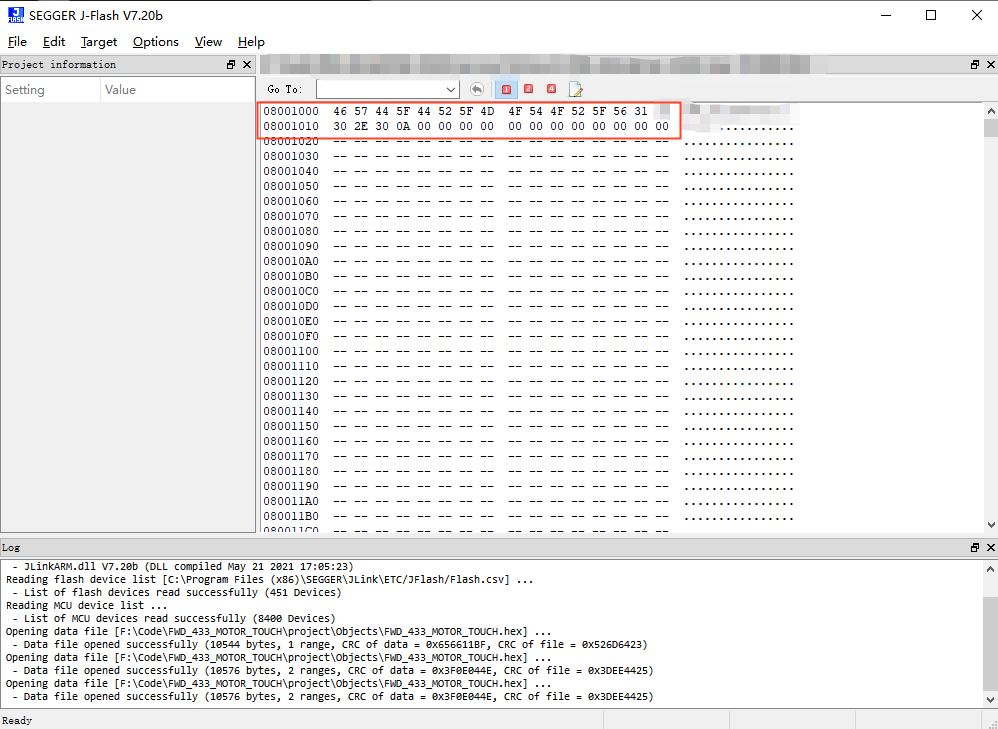

辉芒微离线烧录器“文件格式错误”问题解决

最近在使用辉芒微离线烧录器烧录程序时,提示“文件格式错误”,记录一下解决方法。 一、问题现象 经过多次尝试和排查,发现以下几种情况: 情况一:使用离线烧录器导入固件1(boot程序),…...

buck和boost总结

目录 1. 基本概念与原理 2. 工作模式 3. 典型应用场景 4. Buck-Boost电路:升降压结合 5. 核心区别与选择 1. 基本概念与原理 Buck电路(降压电路) 通过开关器件(如MOSFET)周期性地导通和关断,控制电感充…...

Ansible内置模块之package

原创:厦门微思网络 Ansible内置模块之 package ansible.builtin.package 模块用于管理基于 Linux 系统上的软件包。它是一个通用模块,支持多个包管理器(如 apt、yum、dnf、zypper 等),可以安装、更新和删除软件包。其…...

)

RISC-V AIA SPEC学习(五)

第六章 Interrupts for Virtual Machines(VS Level) 核心内容 1.VS级别外部中断支持: 客户中断文件(Guest Interrupt File):虚拟机的每个vCPU拥有独立的IMSIC中断文件,允许直接接收设备MSI。vstopi CSR:类似stopei,用于虚拟机内部处理最高优先级中…...

【软件设计师:体系结构】15.计算机体系结构概论

计算机体系结构是指计算机系统的功能和属性,是程序员所看到的计算机的属性。它主要研究计算机体系的概念性结构和功能特性,包括指令集、数据类型、存储器寻址技术、I/O机制等。例如,计算机是否具备乘法指令的功能,这是一个体系结构的问题。 一、机内代码及运算 一、数的进…...

CVE-2025-24813:Apache Tomcat RCE 漏洞分析

CVE-2025-24813 是 Apache Tomcat 中的一个严重远程代码执行 (RCE) 漏洞,源于路径等效缺陷,允许攻击者绕过安全约束并远程执行任意代码。 CYFIRMA 的研究发现了一些活跃的漏洞利用,一些 PoC 漏洞在地下论坛上流传。攻击者利用基于 HTTP PUT 的任意文件上传、NTFS 连接漏洞利…...

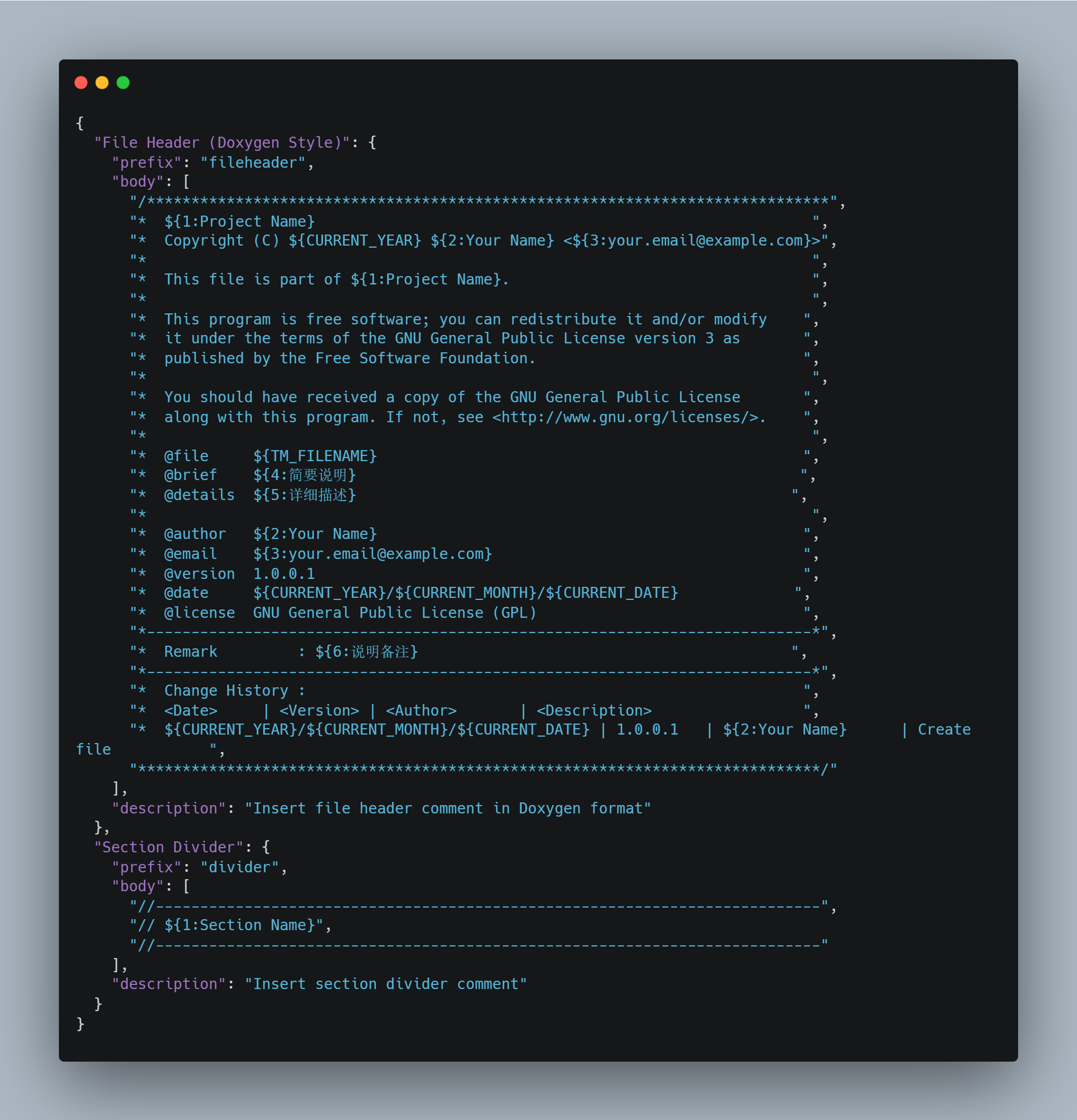

vscode 配置doxygen注释和snippet

vscode 配置doxygen注释和snippet Doxygen的C/C注释原则 基于Doxygen的C/C注释原则 标注总述 1.文件头标注 2. 命名空间标注 3. 类、结构、枚举标注 4. 函数注释原则 5. 变量注释 6. 模块标注 7. 分组标注指令表格 命令字段名语法file文件名file [< name >]brief简介b…...

分析 Docker 磁盘占用

以下是分析 Docker 磁盘占用的详细步骤和工具指南,帮助开发者快速定位和清理冗余数据: 1. 查看 Docker 磁盘使用概览 docker system df 输出说明: TYPE TOTAL ACTIVE SIZE RECLAIMABLE Images 15 …...

HarmonyOS NEXT 免费无广告看电影app:从想法到实现的经验总结

学习一项新技能,最好也是最快的方法就是动手实战。学习鸿蒙也一样,给自己定一个小目标,直接找项目练,这样进步是最快的。最近,我在网上看到360周董的一句话:“想干什么就去干,干得烂总比不干强!…...

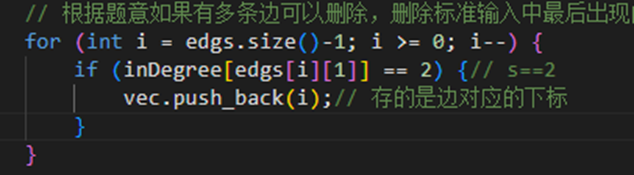

代码随想论图论part06冗余连接

图论part06 冗余连接 代码随想录 冗余边就是已经边已经在并查集里了,从图的角度来说构成了环(冗余连接2要用到这个概念) 代码其他部分为:并查集初始化,查根,判断是否在集合里,加入集合 冗余…...

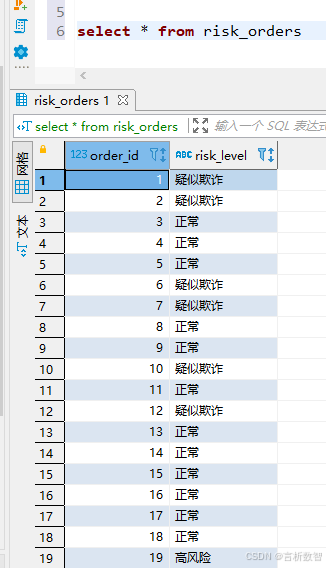

MySQL 数据库操作

目录 一、 MySQL 数据库介绍 二、 MySQL 库操作 1. 系统数据库 2. 数据库操作 三、 MySQL 表操作 1. 表介绍 2. 查看表 3. 创建表 4. 查看表结构 5. 修改表 6. 删除表 四、 MySQL 数据操作 4.1 单表查询 4.2 多表查询 一、 MySQL 数据库介绍 数据库目前标准的指令…...

企业高性能WEB服务器—Nginx

Nginx介绍 Nginx是一款轻量级的网页服务器、反向代理服务器以及电子邮件代理服务器。 具有高并发(特别是静态资源)、占用系统资源少的特性。它不仅是Web服务软件,还具有反向代理负载均衡功能和缓存服务功能 具备如下基本特性 可针对静态资…...

C++跨平台开发实践:深入解析与常见问题处理指南

一、跨平台开发基础架构设计 1.1 跨平台架构的核心原则 分层设计模式: 平台抽象层(PAL):将平台相关代码集中管理 核心逻辑层:完全平台无关的业务代码 平台实现层:针对不同平台的特定实现 代码组织最佳实践: pro…...

Python MNE-Python 脑功能磁共振数据分析

一、什么是Python MNE-Python 脑功能磁共振数据分析 为大脑功能磁共振成像数据分析工具,致力于为神经科学研究提供便捷、高效的数据分析处理工具。MNE-Python提供了处理和分析脑电图(EEG)、…...

DevExpressWinForms-AlertControl-使用教程

文章目录 AlertControl-使用教程一、将 AlertControl 添加到 Form二、编辑 AlertControl 的 HtmlTemplateHTML Template Editor介绍编辑HTML Template 三、使用AlertControl弹出AlertAlert中的按钮事件获取 Alert 标题等信息向Alert传递参数 总结源码 AlertControl-使用教程 一…...

SurfSense开源程序是NotebookLM / Perplexity / Glean的开源替代品,连接到外部来源,如搜索引擎

一、软件介绍 文末提供程序和源码下载 虽然 NotebookLM 和 Perplexity 等工具令人印象深刻,并且对于对任何主题/查询进行研究都非常有效,但 SurfSense 通过与你的个人知识库集成来提升这种能力。它是一个高度可定制的 AI 研究代理,连接到外…...

【PostgreSQL数据分析实战:从数据清洗到可视化全流程】电商数据分析案例-9.4 可视化报告输出

👉 点击关注不迷路 👉 点击关注不迷路 👉 点击关注不迷路 文章大纲 电商数据分析实战:基于PostgreSQL的可视化报告生成全流程9.4 可视化报告输出9.4.1 可视化报告设计框架9.4.1.1 报告目标与受众9.4.1.2 数据准备与指标体系 9.4.2…...

屎上雕花系列-2nd

以下为“屎上雕花”的尝试2nd 使用Deepseek扩容而来,我竟然没有找到明显的错误,太强大了,工作改变生活了 LeCroy 以太网与 SAN 网络测试解决方案 硬件平台一:Xena 以太网流量生成器 Xena 以太网流量生成器是一款高性能的网络测…...

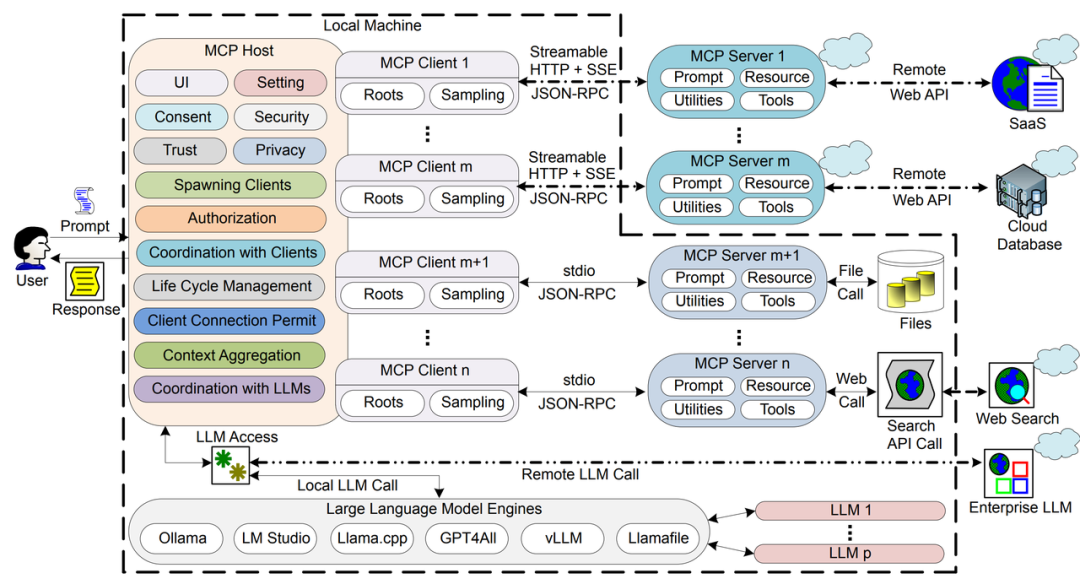

MCP专题| 突破LLM三大瓶颈!模型上下文协议(MCP)如何重塑AI交互体验?

最近引爆了整个AI圈的Model Context Protocol(MCP)到底是什么?你是否也和小编一样一头雾水,不是说好的LLM风潮呢,怎么现在变成通信协议啦?最近小编也是找到一篇神仙综述,带你一遍搞清什么是MCP的…...

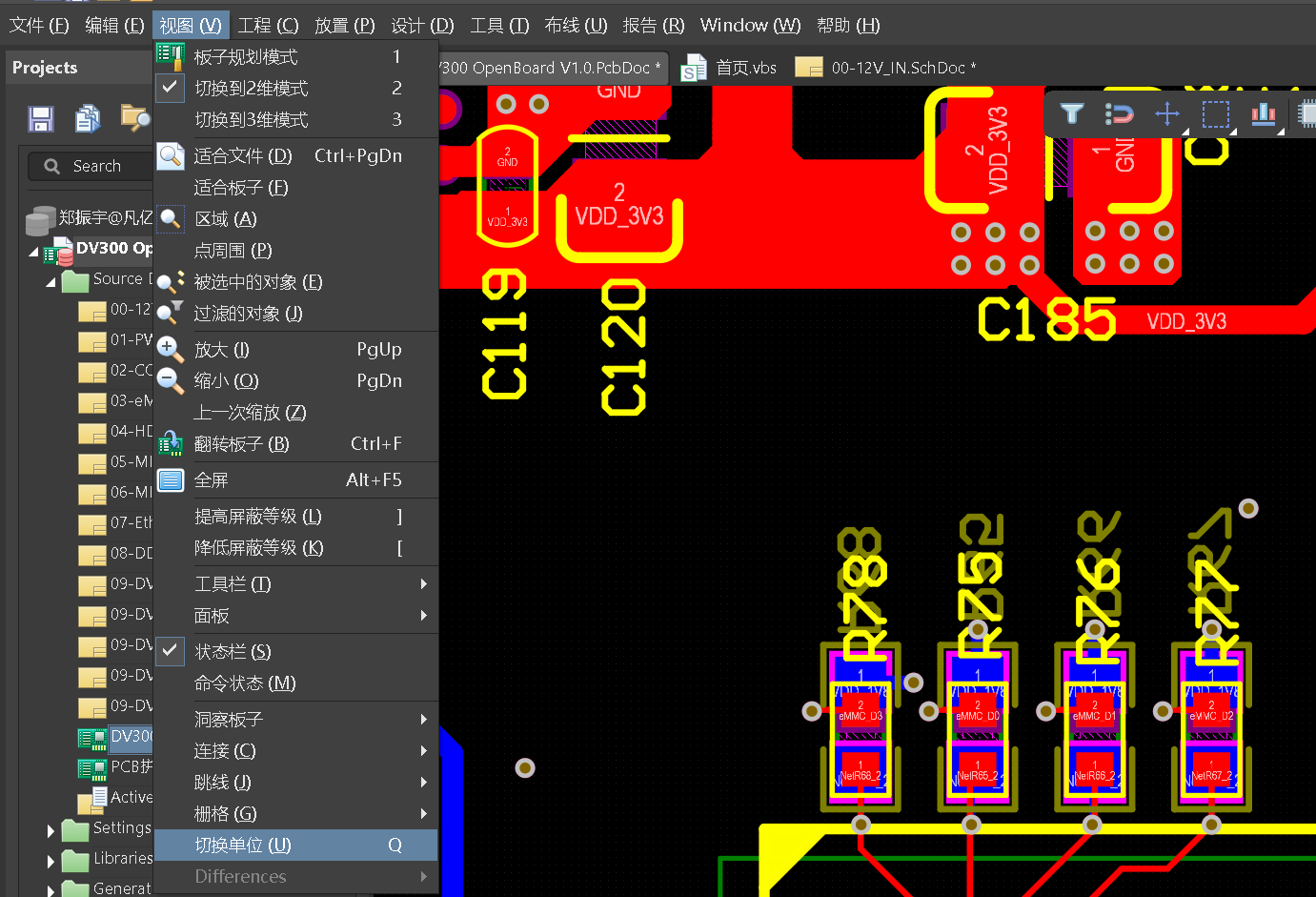

我的AD快捷键方案【留存】

留存我的快捷键方案文件,以便换电脑的时候能够快速导入快捷键。 我的快捷键文件: 通过网盘分享的文件:JB20250509.DXPPrf 链接: https://pan.baidu.com/s/1t6V0GjdGFPNSFydP5Z_tfg?pwde4xs 提取码: e4xs 复制这段内容后打开百度网盘手机Ap…...

uni-app,小程序自定义导航栏实现与最佳实践

文章目录 前言为什么需要自定义导航栏?基本实现方案1. 关闭原生导航栏2. 自定义导航栏组件结构3. 获取状态栏高度4. 样式设置 内容区域适配跨平台适配要点iOS与Android差异处理 常见导航栏效果实现1. 透明导航栏2. 滚动渐变导航栏3. 自定义返回逻辑 解决常见问题1. …...

解决osx-arm64平台上conda默认源没有提供 python=3.7 的官方编译版本的问题

CONDA_SUBDIRosx-64 conda create -n py37_env python3.7 是一个用于创建特定架构环境的命令,主要针对 macOS 系统。下面为你详细解析它的功能和作用: 命令功能解析 这个命令的主要功能是创建一个名为 py37_env 的 Conda 环境,并且指定该环…...

Edwards爱德华STP泵软件用于操作和监控涡轮分子泵

Edwards爱德华STP泵软件用于操作和监控涡轮分子泵...

vue内写websocket实时订阅

首先安装插件reconnecting-websocket 或者不安装也可以,这个插件只是在断连之后可以重新连接 引入插件 import ReconnectingWebSocket from reconnecting-websocket;。 js文件: export const WebSocketClass (url, params, successFn, errorFn, clo…...

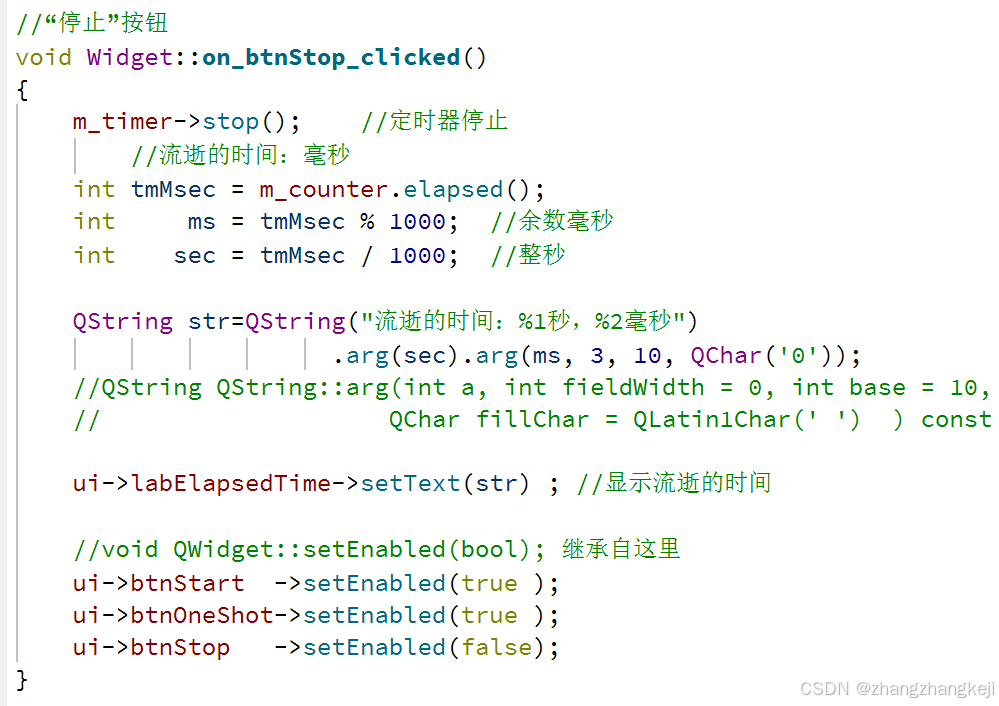

QT6(35)4.8定时器QTimer 与QElapsedTimer:理论,例题的界面搭建,与功能的代码实现。

(112) (113)模仿随书老师给的源代码搭建的, LCD 显示的部分不一样 : (114)以下开始代码完善: 关联定时器的信号与槽函数 : (115)…...

在R语言中如何将列的名字改成别的

在 R 中,更改数据框(data frame)中列的名字可以通过多种方法实现。以下是几种常见的方法: 方法 1:使用 names() 函数 names() 函数可以获取或设置数据框的列名。 示例 假设我们有一个数据框 data: dat…...