Altera系列FPGA实现图像视频采集转HDMI/LCD输出,提供4套Quartus工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- Altera系列FPGA相关方案推荐

- 3、设计思路框架

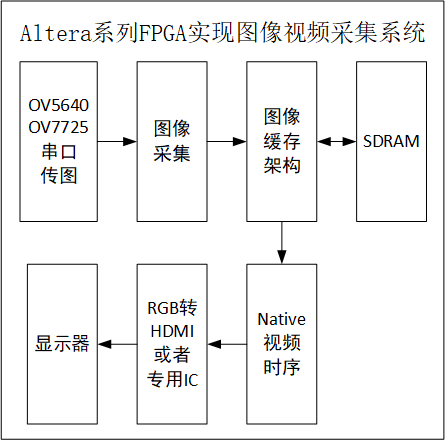

- 工程设计原理框图

- 输入Sensor之-->OV7725摄像头

- 输入Sensor之-->OV5640摄像头

- 输入Sensor之-->串口传图输入

- 图像缓存架构

- HDMI输出架构

- LCD输出架构

- 工程源码架构

- 4、Quartus工程源码1详解:OV7725输入-HDMI输出版本

- 5、Quartus工程源码2详解:OV5640输入-HDMI输出版本

- 6、Quartus工程源码3详解:串口传图输入-LCD输出版本

- 7、Quartus工程源码4详解:串口传图输入-HDMI输出版本

- 8、上板调试验证并演示

- 准备工作

- Altera系列FPGA视频采集效果演示

- 9、福利:工程源码获取

Altera系列FPGA实现图像视频采集转HDMI/LCD输出,提供4套Quartus工程源码和技术支持

1、前言

Altera系列FPGA现状:

Altera系列FPGA目前处于逐步退出市场状态,市场占有率很低、使用便捷性很低、开发生态很不完善,之前还可以凭借价格低廉在低端产品上使用,但如今国产FPGA的崛起让Altera唯一的优势也荡然无存;所以本博主奉劝还在学Altera系列FPGA的同学赶紧悬崖略吗回头是岸,别再浪费宝贵的时间了,未来的FPGA市场,高端市场非Xilinx莫属,中低端市场非国产FPGA莫属;

工程概述

本文使用Altera的Cyclone-IV系列FPGA做基础的图像视频采集系统;视频输入源有多种,一种是传统摄像头,包括OV7725、OV5640和AR0135,另一种是用串口发送图片到FPGA作为输入源;如果你的FPGA开发板没有视频输入接口,或者你的手里没有摄像头时,可以使用FPGA逻辑实现的动态彩条模拟输入视频,代码里通过parametr参数选择视频源,默认不使用动态彩条;FPGA首先对摄像头进行i2c初始化配置,然后采集摄像头视频;然后视频送入图像缓存架构实现视频2帧缓存功能,本设计使用SDRAM作为缓存介质;然后Native视频时序控制图像缓存架构从SDRAM中读取视频,并做Native视频时序同步,输出RGB888视频;然后视频送入RGB转HDMI实现HDMI输出功能;最后视频通过板载HDMI或者LCD输出接口送显示器显示即可;针对市场主流需求,本设计提供4套Quartus工程源码,具体如下:

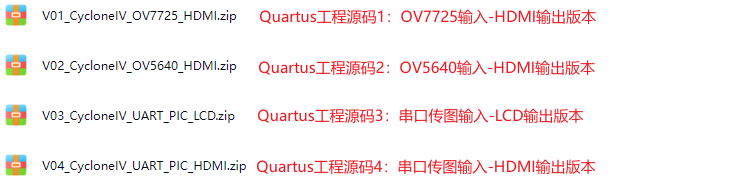

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Cyclone-IV-EP4CE10F17C8;输入视频为OV7725摄像头或者动态彩条,默认使用OV7725;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为640x480@60Hz;然后采集输入视频,将输入的两个时钟传输一个RGB565像素的视频采集为一个时钟传输一个RGB888像素的视频;然后视频送入图像缓存架构实现视频2帧缓存功能,本设计使用SDRAM作为缓存介质;然后Native视频时序控制图像缓存架构从SDRAM中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为640x480@60Hz,然后视频送入RGB转HDMI实现HDMI输出功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用Altera系列FPGA实现图像视频采集系统应用;

工程源码2

开发板FPGA型号为Cyclone-IV-EP4CE10F17C8;输入视频为OV5640摄像头或者动态彩条,默认使用OV5640;FPGA首先使用纯Verilog实现的i2c总线对摄像头进行初始化配置,分辨率配置为1280x720@30Hz;然后采集输入视频,将输入的两个时钟传输一个RGB565像素的视频采集为一个时钟传输一个RGB888像素的视频;然后视频送入图像缓存架构实现视频2帧缓存功能,本设计使用SDRAM作为缓存介质;然后Native视频时序控制图像缓存架构从SDRAM中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为1280x720@60Hz,然后视频送入RGB转HDMI实现HDMI输出功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用Altera系列FPGA实现图像视频采集系统应用;

工程源码3

开发板FPGA型号为Cyclone-IV-EP4CE10F17C8;输入视频为串口发送来的图片,使用串口上位机发送bmp格式图片到FPGA,图片分辨率为800x480,串口波特率设置为1562500;FPGA接收图片数据后送入图像缓存架构实现视频2帧缓存功能,本设计使用SDRAM作为缓存介质;然后Native视频时序控制图像缓存架构从SDRAM中读取视频,并做Native视频时序同步,输出RGB565视频,输出分辨率为800x480@60Hz;最后视频通过板载LCD输出接口送显示器显示即可;该工程适用Altera系列FPGA实现图像视频采集系统应用;

工程源码4

开发板FPGA型号为Cyclone-IV-EP4CE10F17C8;输入视频为串口发送来的图片,使用串口上位机发送bmp格式图片到FPGA,图片分辨率为800x480,串口波特率设置为1562500;FPGA接收图片数据后送入图像缓存架构实现视频2帧缓存功能,本设计使用SDRAM作为缓存介质;然后Native视频时序控制图像缓存架构从SDRAM中读取视频,并做Native视频时序同步,输出RGB888视频,输出分辨率为800x480@60Hz,然后视频送入RGB转HDMI实现HDMI输出功能;最后视频通过板载HDMI输出接口送显示器显示即可;该工程适用Altera系列FPGA实现图像视频采集系统应用;

本博客描述了Altera系列FPGA实现图像视频采集系统的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

Altera系列FPGA相关方案推荐

我专门开设了一个Altera系列FPGA专栏,里面收录了基于Altera系列FPGA的图像处理、UDP网络通信、GT高速接口、PCIE等博客,感兴趣的可以去看看,博客地址:

点击直接前往

3、设计思路框架

工程设计原理框图

工程设计原理框图如下:

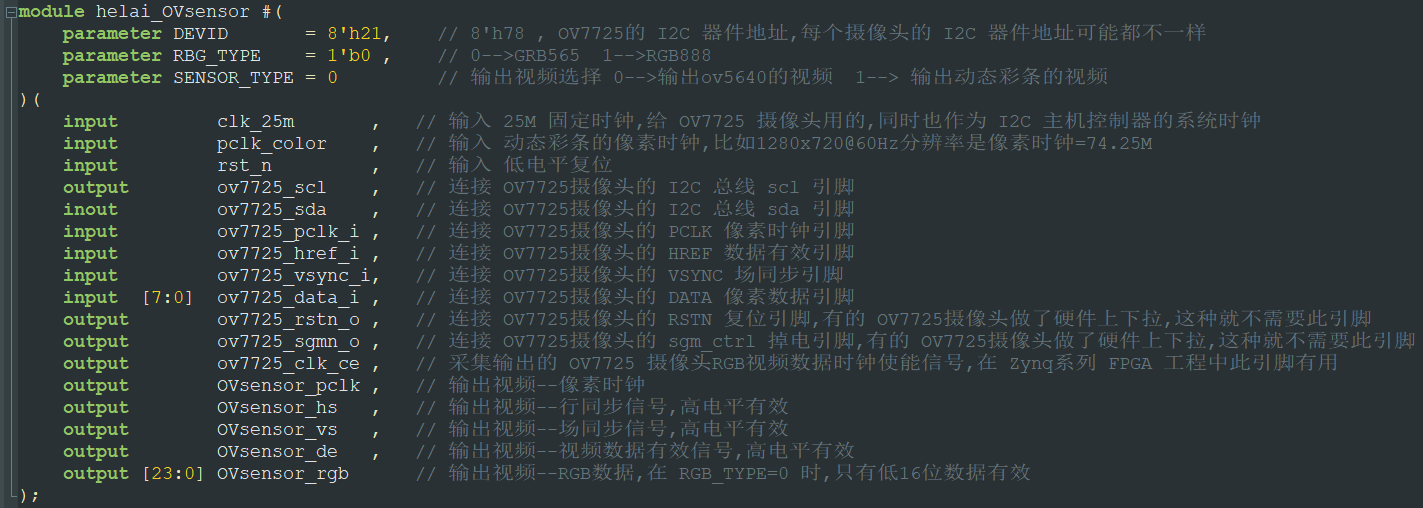

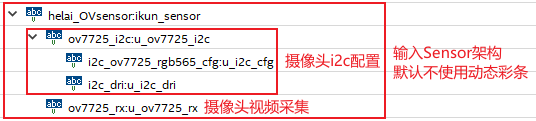

输入Sensor之–>OV7725摄像头

输入Sensor是本工程的输入设备,其一为OV7725摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV7725摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

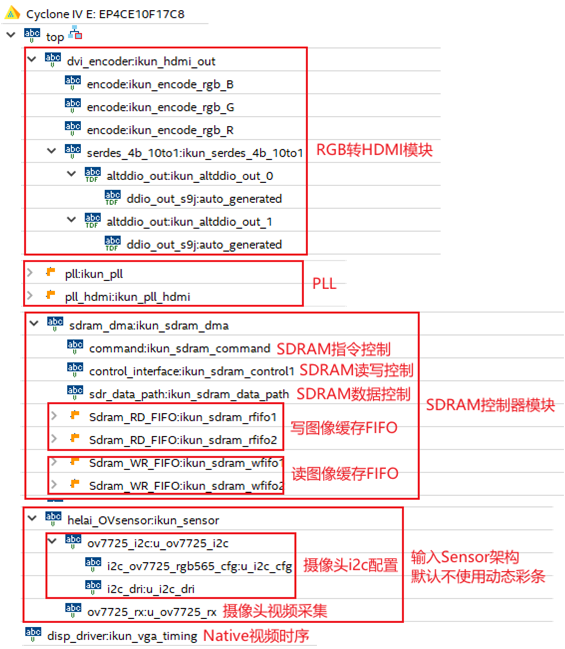

OV7725摄像头需要i2c初始化配置,本设计配置为640x480@60Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV7725摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV7725摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

输入Sensor之–>OV5640摄像头

输入Sensor是本工程的输入设备,其一为OV5640摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV5640摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

OV5640摄像头需要i2c初始化配置,本设计配置为1280x720@30Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV5640摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV5640摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

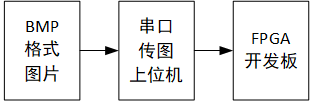

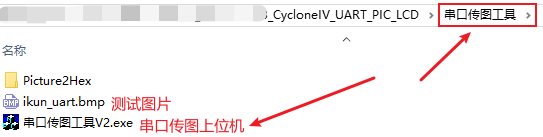

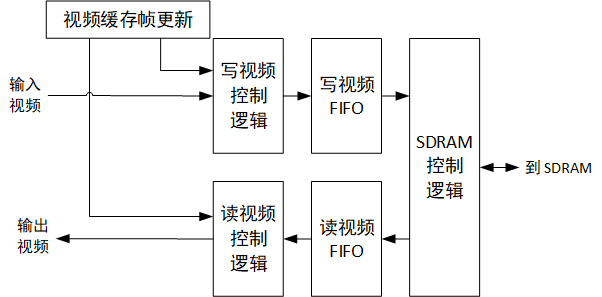

输入Sensor之–>串口传图输入

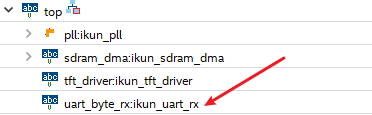

输入Sensor是本工程的输入设备,其三为串口传图作为输入;输入视频为串口发送来的图片,使用串口上位机发送bmp格式图片到FPGA,图片分辨率为800x480,串口波特率设置为1562500;串口传图架构如下:

串口传图模块代码架构如下:

串口传图上位机已放在资料包中,如下:

串口传图上位机使用方法如下:

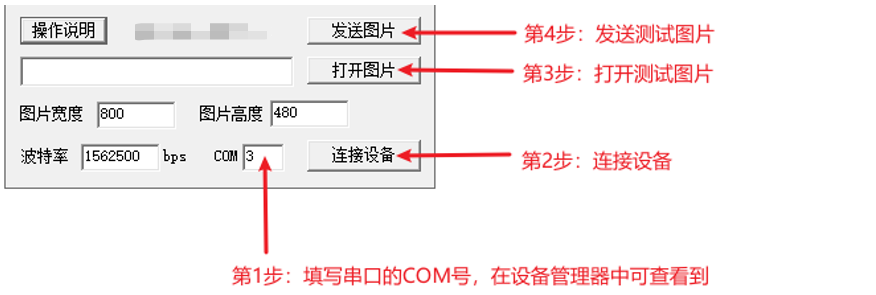

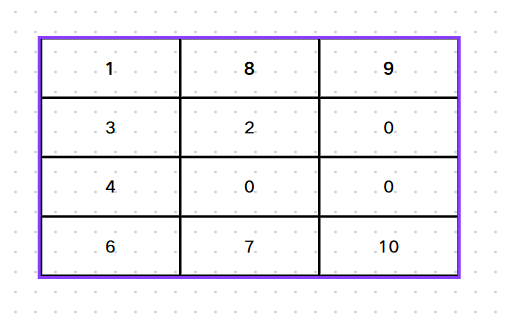

图像缓存架构

图像缓存架构实现的功能是将输入视频缓存到板载SDRAM中再读出送后续模块,目的是实现视频同步输出,实现输入视频到输出视频的跨时钟域问题,更好的呈现显示效果,其中SDRAM控制器用纯verilog代码实现,所以图像缓存架构就是实现用户数据到SDRAM的桥接作用;架构如下:

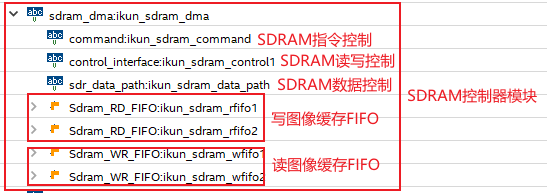

图像缓存架构由视频缓存帧更新模块+写视频控制逻辑+读视频控制逻辑+SDRAM控制器模块组成;SDRAM控制器实现了SDRAM初始化、读写时序控制、读写流程控制等功能,写视频控制逻辑、读视频控制逻辑实际上就是一个视频读写状态机,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;写视频控制逻辑每次写入一次突发传输的视频数据,记作Y,即每次向SDRAM中写入Y个像素,写M×N÷Y次即可完成1帧图像的缓存,读视频与之一样;同时调用两个FIFO实现输入输出视频的跨时钟域处理,使得用户可以忽略SDRAM复杂的控制时序,以简单地像使用FIFO那样操作SDRAM,从而达到读写SDRAM的目的,进而实现视频缓存;本设计图像缓存方式为2帧缓存;图像缓存模块代码架构如下:

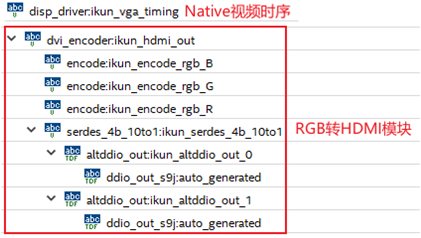

HDMI输出架构

HDMI输出包括Native视频时序和HDMI编码,Native视频时序的作用是产生传统VGA的、RGB的视频流;HDMI编码采用RTL逻辑编码方式;HDMI输出代码架构如下:

LCD输出架构

使用Native视频时序产生LCD输出的时序,本设计使用5寸TFT-CLD屏幕;CLD输出代码架构如下:

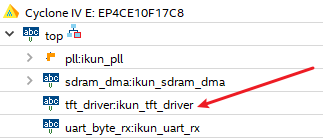

工程源码架构

以工程2为例,工程源码架构如下,其他工程与之类似:

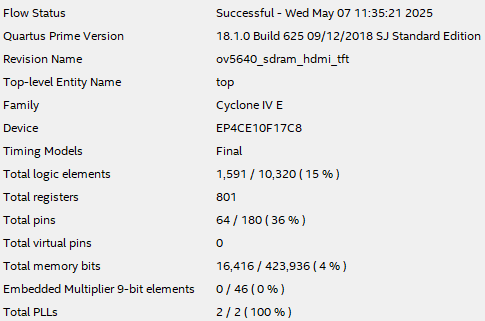

4、Quartus工程源码1详解:OV7725输入-HDMI输出版本

开发板FPGA型号:Altera–Cyclone-IV系列-EP4CE10F17C8;

开发环境:Quartus 18.1;

输入:OV7725摄像头或FPGA内部动态彩条,分辨率640x480@60Hz;

输出:HDMI,RTL逻辑编码,分辨率640x480@60Hz;

图像缓存方案:纯Verilog图像缓存,2帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Altera系列FPGA实现图像视频采集系统的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

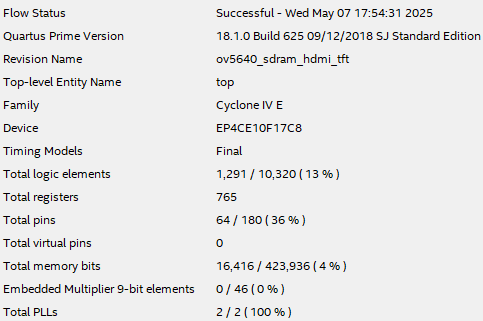

5、Quartus工程源码2详解:OV5640输入-HDMI输出版本

开发板FPGA型号:Altera–Cyclone-IV系列-EP4CE10F17C8;

开发环境:Quartus 18.1;

输入:OV5640摄像头或FPGA内部动态彩条,分辨率1280x720@30Hz;

输出:HDMI,RTL逻辑编码,分辨率1280x720@60Hz;

图像缓存方案:纯Verilog图像缓存,2帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Altera系列FPGA实现图像视频采集系统的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

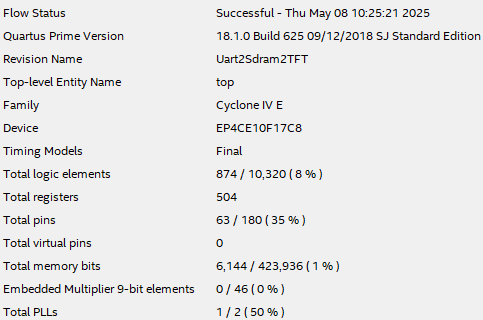

6、Quartus工程源码3详解:串口传图输入-LCD输出版本

开发板FPGA型号:Altera–Cyclone-IV系列-EP4CE10F17C8;

开发环境:Quartus 18.1;

输入:串口传图,图片分辨率800x480;

输出:5寸LCD屏,分辨率800x480@60Hz;

图像缓存方案:纯Verilog图像缓存,2帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Altera系列FPGA实现图像视频采集系统的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

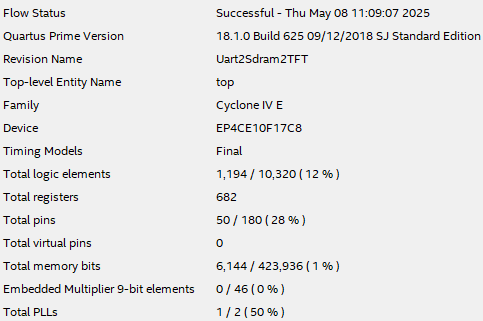

7、Quartus工程源码4详解:串口传图输入-HDMI输出版本

开发板FPGA型号:Altera–Cyclone-IV系列-EP4CE10F17C8;

开发环境:Quartus 18.1;

输入:串口传图,图片分辨率800x480;

输出:HDMI,RTL逻辑编码,分辨率800x480@60Hz;

图像缓存方案:纯Verilog图像缓存,2帧缓存;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Altera系列FPGA实现图像视频采集系统的设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

8、上板调试验证并演示

准备工作

你需要有以下装备才能移植并测试该工程代码:

1:FPGA开发板;

2:OV7725或OV5640摄像头或笔记本电脑,没有则请使用FPGA内部生成的彩条;

3:HDMI传输线;

4:HDMI显示,要求分辨率支持1920x1080;

Altera系列FPGA视频采集效果演示

Altera系列FPGA视频采集效果演示如下:

Altera-图传

9、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Altera系列FPGA实现图像视频采集转HDMI/LCD输出,提供4套Quartus工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目Altera系列FPGA相关方案推荐 3、设计思路框架工程设计原理框图输入Sensor之-->OV7725摄像头输入Sensor之-->OV5640摄像头输入Sensor之-->串口传图输入图像缓…...

互联网大厂Java面试实战:Spring Boot到微服务的技术问答解析

💪🏻 1. Python基础专栏,基础知识一网打尽,9.9元买不了吃亏,买不了上当。 Python从入门到精通 😁 2. 毕业设计专栏,毕业季咱们不慌忙,几百款毕业设计等你选。 ❤️ 3. Python爬虫专栏…...

Leetcode-BFS问题

LeetCode-BFS问题 1.Floodfill问题 1.图像渲染问题 [https://leetcode.cn/problems/flood-fill/description/](https://leetcode.cn/problems/flood-fill/description/) class Solution {public int[][] floodFill(int[][] image, int sr, int sc, int color) {//可以借助另一…...

Web端项目系统访问页面很慢,后台数据返回很快,网络也没问题,是什么导致的呢?

Web端访问缓慢问题诊断指南(测试工程师专项版) ——从浏览器渲染到网络层的全链路排查方案 一、问题定位黄金法则(前端性能四象限) 1. [网络层] 数据返回快 ≠ 资源加载快(检查Content Download时间) 2. [渲染层] DOM复杂度与浏览器重绘(查看FPS指标) 3. [执行层…...

Next.js 知识框架总结

一、核心概念 1. 渲染策略 CSR (Client-Side Rendering): 传统 React 渲染方式 SSR (Server-Side Rendering): 服务端渲染 getServerSideProps SSG (Static Site Generation): 静态生成 getStaticProps getStaticPaths (动态路由) ISR (Incremental Static Regeneration…...

【PostgreSQL数据分析实战:从数据清洗到可视化全流程】8.4 数据故事化呈现(报告结构设计/业务价值提炼)

👉 点击关注不迷路 👉 点击关注不迷路 👉 点击关注不迷路 文章大纲 8.4 数据故事化呈现:从报告结构到业务价值的深度融合一、数据故事化的核心价值体系(一)报告结构设计的黄金框架1. 业务场景锚定ÿ…...

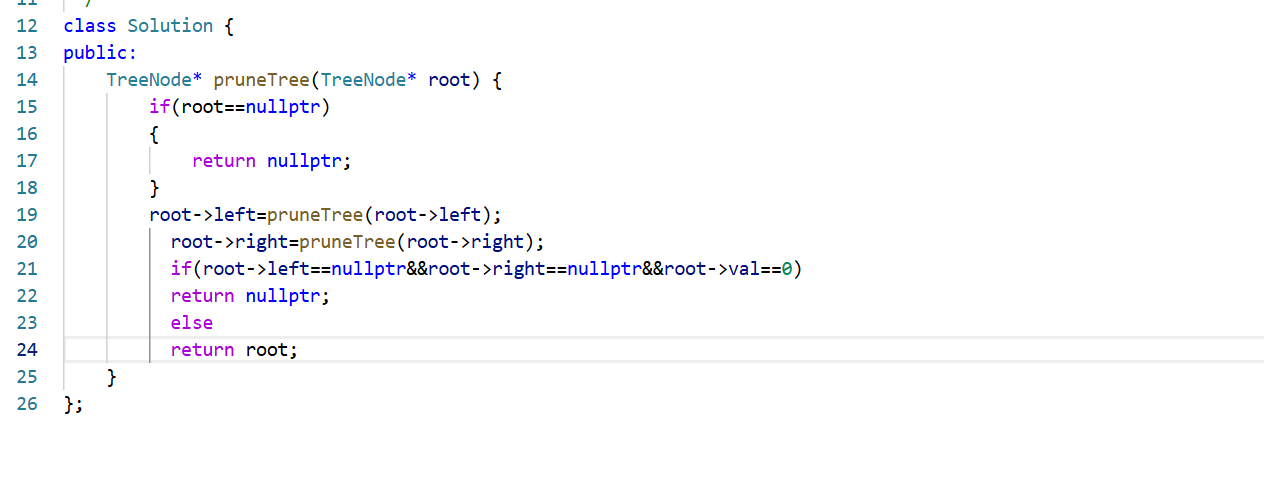

专题二:二叉树的深度搜索(二叉树剪枝)

以leetcode814题为例 题目分析: 也就是当你的子树全为0的时候就可以剪掉 算法原理分析: 首先分析问题,你子树全为0的时候才可以干掉,我们可以设递归到某一层的时候如何处理 然后抽象出三个核心问题 也就是假设我们递归到第2层…...

Hugging Face推出了一款免费AI代理工具,它能像人类一样使用电脑

Hugging Face推出了一款免费AI代理工具,它能像人类一样使用电脑。 这款工具名为Open Computer Agent(开放计算机代理),可模拟真实的电脑操作。 无需安装,在浏览器中即可运行。 以下是一些信息: - Open C…...

Datawhale AI春训营 day

待补充 2025星火杯应用赛入门应用 创空间 魔搭社区 {"default": {"system": "你是星火大模型,一个由科大讯飞研发的人工智能助手。请用简洁、专业、友好的方式回答问题。","description": "默认系统提示词"}…...

Java面试高阶篇:Spring Boot+Quarkus+Redis高并发架构设计与性能优化实战

Java面试高阶篇:Spring BootQuarkusRedis高并发架构设计与性能优化实战 面试官(严肃): Q1: 你项目中如何实现高并发下的缓存优化? 候选人(水货): 我们用了Redis做缓存,…...

生成对抗网络(GAN)深度解析:理论、技术与应用全景

生成对抗网络(Generative Adversarial Networks,GAN)作为深度学习领域的重要突破,通过对抗训练框架实现了强大的生成能力。本文从理论起源、数学建模、网络架构、工程实现到行业应用,系统拆解GAN的核心机制,涵盖基础理…...

CSRF记录

CSRF(Cross-site request forgery)跨站请求伪造:攻击者诱导受害者进入第三方网站,在第三方网站中,向被攻击网站发送跨站请求。利用受害者在被攻击网站已经获取的注册凭证,绕过后台的用户验证,达…...

【ROS2】CMakeLists配置信息通俗解释

文件示例 cmake_minimum_required(VERSION 3.8) project(pkg01_helloworld_cpp)if(CMAKE_COMPILER_IS_GNUCXX OR CMAKE_CXX_COMPILER_ID MATCHES "Clang")add_compile_options(-Wall -Wextra -Wpedantic) endif()# find dependencies find_package(ament_cmake REQU…...

Python集成开发环境之Thonny

前言:今天介绍一款Python的傻瓜IDE(集成开发环境)——Thonny,比较适合初学者进行Python程序的开发和学习,为用户提供了代码编辑、调试、运行等一系列功能。 我应该不止两次提到过这个词了“IDE”(集成开发环境)&#…...

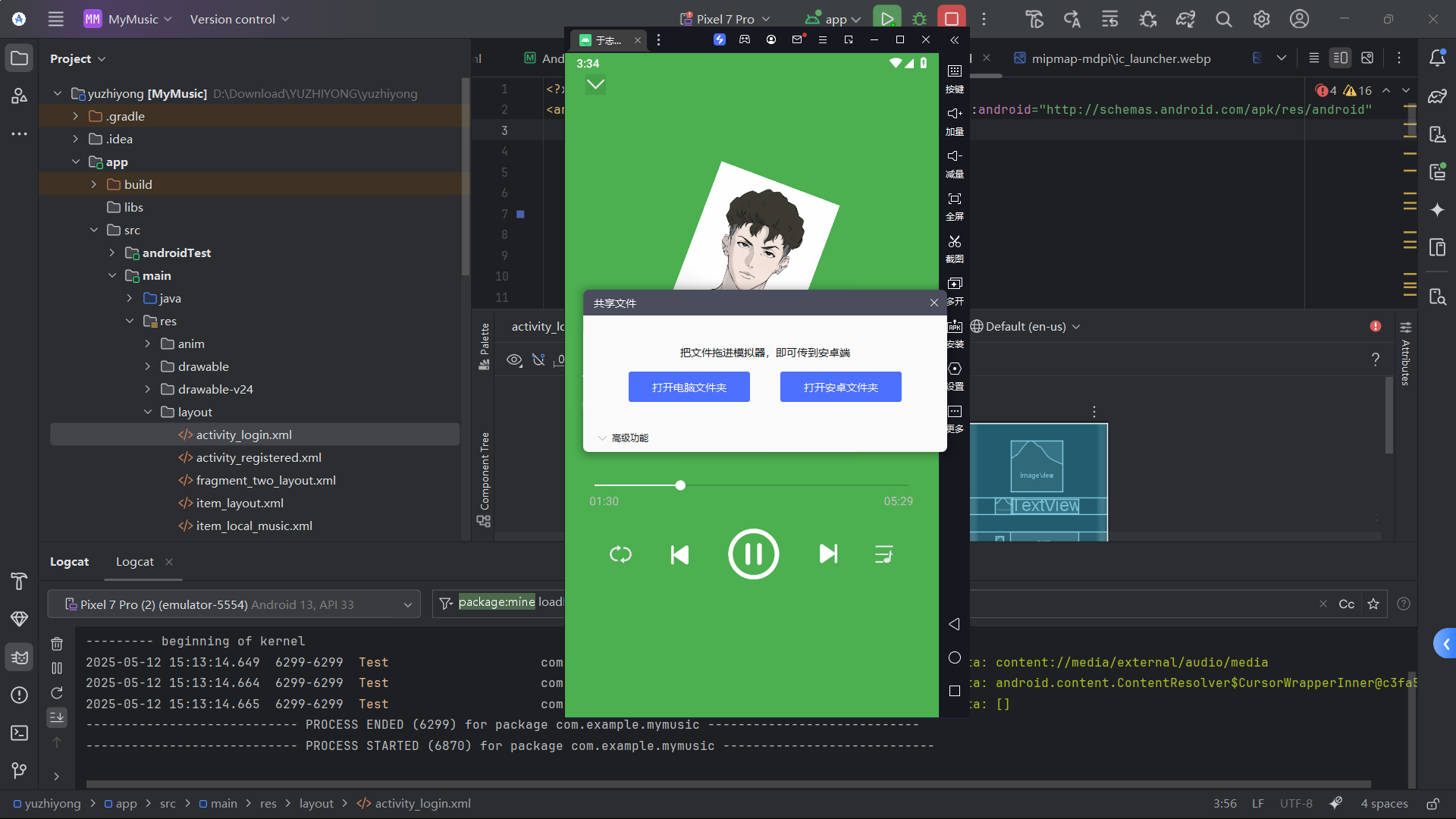

【超详细教程】安卓模拟器如何添加本地文件?音乐/照片/视频一键导入!

作为一名安卓开发者或手游爱好者,安卓模拟器是我们日常工作和娱乐的重要工具。但很多新手在使用过程中常常遇到一个共同问题:**如何将电脑本地的音乐、照片、视频等文件导入到安卓模拟器中?**今天,我将为大家带来一份全网最详细的…...

switch能否作用在byte上,long上,string上

在Java中,switch语句可以用于多种数据类型,但这些类型需要满足特定的条件。以下是switch语句可以作用的数据类型: byte:可以用于switch语句。由于byte可以隐式转换为int,所以可以直接在switch语句中使用。 long&#…...

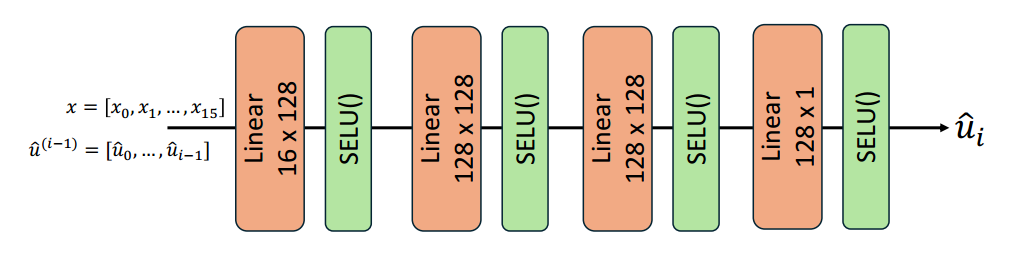

构建DEEPPOLAR ——Architecture for DEEPPOLAR (256,37)

目录 编码器 解码器 编码器 编码器是大小为的内核的集合ℓ 16,每个都由神经网络g建模。编码器内核g负责编码ℓ 输入。g的架构如下: 表1 DEEPOLAR模型训练中使用的超参数(256,37,ℓ16) Table 1. Hyperparameters used in model…...

使用 DMM 测试 TDR

TDR(时域反射计)可能是实验室中上升时间最快的仪器,但您可以使用直流欧姆表测试其准确性。 TDR 测量什么 在所有高速通道中,反射都很糟糕。我们尝试设计一个通道来减少反射,这些反射都会导致符号间干扰 (…...

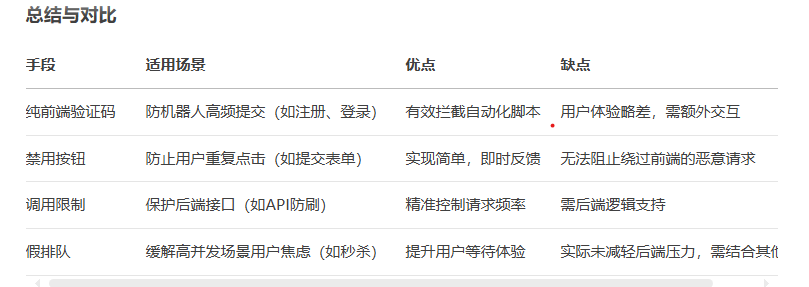

客户端限流主要采用手段:纯前端验证码、禁用按钮、调用限制和假排队

一、纯前端验证码 场景 防止机器人或脚本高频提交,需用户完成验证后才能触发请求。 Vue 前端实现 <template><div><button click"showCaptcha">提交订单</button><div v-if"captchaVisible"><img :src"…...

第一天——贪心算法——分饼干

一、算法介绍 顾名思义,贪心算法或贪心思想采用贪心的策略,保证每次操作都是局部最优的,从而使最后得到的结果是全局最优的。 举一个最简单的例子:小明和小王喜欢吃苹果,小明可以吃五个,小王可以吃三个。…...

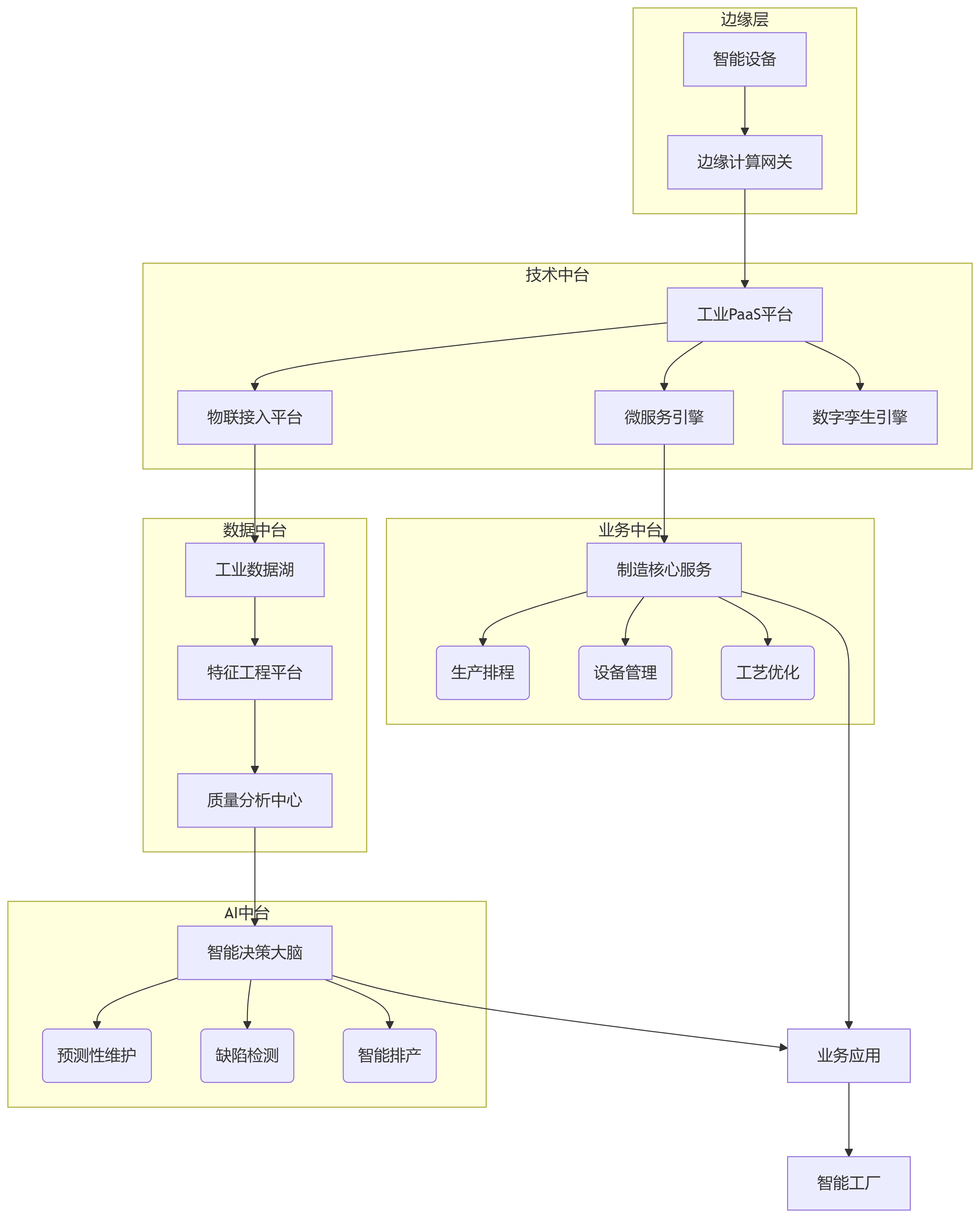

企业数字化中台建设方案(AI/技术中台、数据中台、业务中台)

构建企业数字化中台需要实现业务、数据、AI和技术四大中台的有机协同,形成闭环能力体系。以下是综合建设方案(含技术架构和实施路径): 一、建设背景与目标 1.1 行业痛点 生产设备数据孤岛,实时监控能力不足 传统ERP/…...

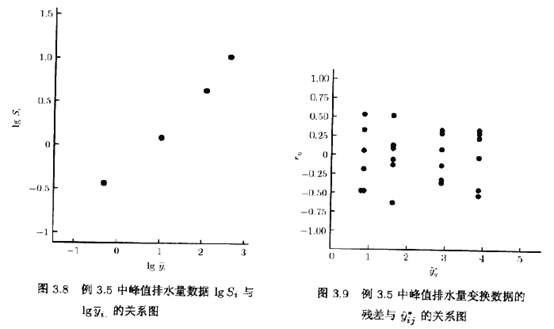

单因子实验方差分析模型的适应性检验

本文是实验设计与分析(第6版,Montgomery著傅珏生译)第3章单因子实验 方差分析第3.4节的python解决方案。本文尽量避免重复书中的理论,着于提供python解决方案,并与原书的运算结果进行对比。您可以从Detail 下载实验设计与分析&…...

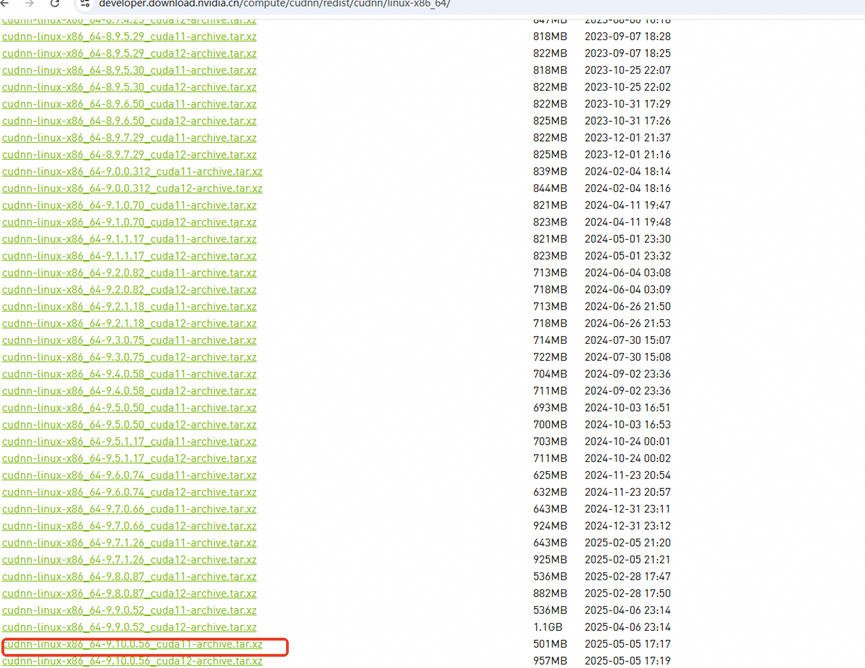

linux CUDA与CUDNN安装教程

目录 1.CUDA安装 1.1.CUDA作用 1.2.CUDA下载 1.3.CUDA安装 1.4.验证 2.CUDNN安装 2.1.CUDNN作用 2.2.下载 2.3.安装 2.4.验证 1.CUDA安装 1.1.CUDA作用 CUDA 是 NVIDIA 提供的并行计算平台和编程模型,允许开发者直接利用 GPU 的并行计算能力ÿ…...

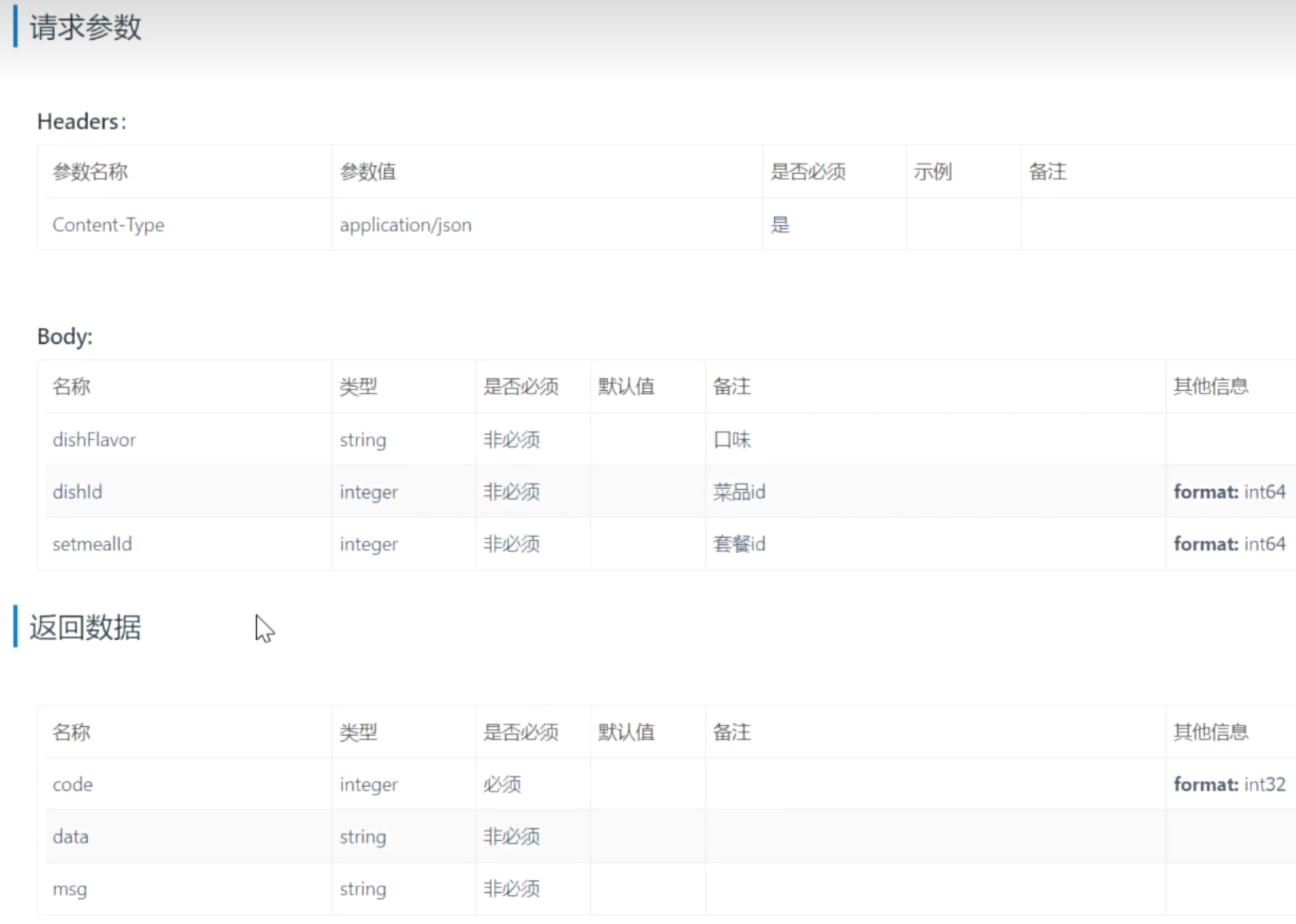

添加购物车-02.代码开发

一.代码开发 购物车属于用户端功能,因此要在user下创建controller代码。 Controller层 package com.sky.controller.user;import com.sky.dto.ShoppingCartDTO; import com.sky.entity.ShoppingCart; import com.sky.result.Result; import com.sky.service.Shopp…...

Unity动画系统使用整理 --- Playable

Playable API 是一个强大的工具,用于更灵活地控制动画、音频、脚本等时间轴内容的播放和混合。它提供了比传统 Animator 更底层、更可控的方式管理时间轴行为,尤其适合复杂动画逻辑或动态内容组合的场景。 优点: 1.Playables API 支…...

Xilinx FPGA PCIe | XDMA IP 核 / 应用 / 测试 / 实践

注:本文为 “Xilinx FPGA 中 PCIe 技术与 XDMA IP 核的应用” 相关文章合辑。 图片清晰度受引文原图所限。 略作重排,未整理去重。 如有内容异常,请看原文。 FPGA(基于 Xilinx)中 PCIe 介绍以及 IP 核 XDMA 的使用 N…...

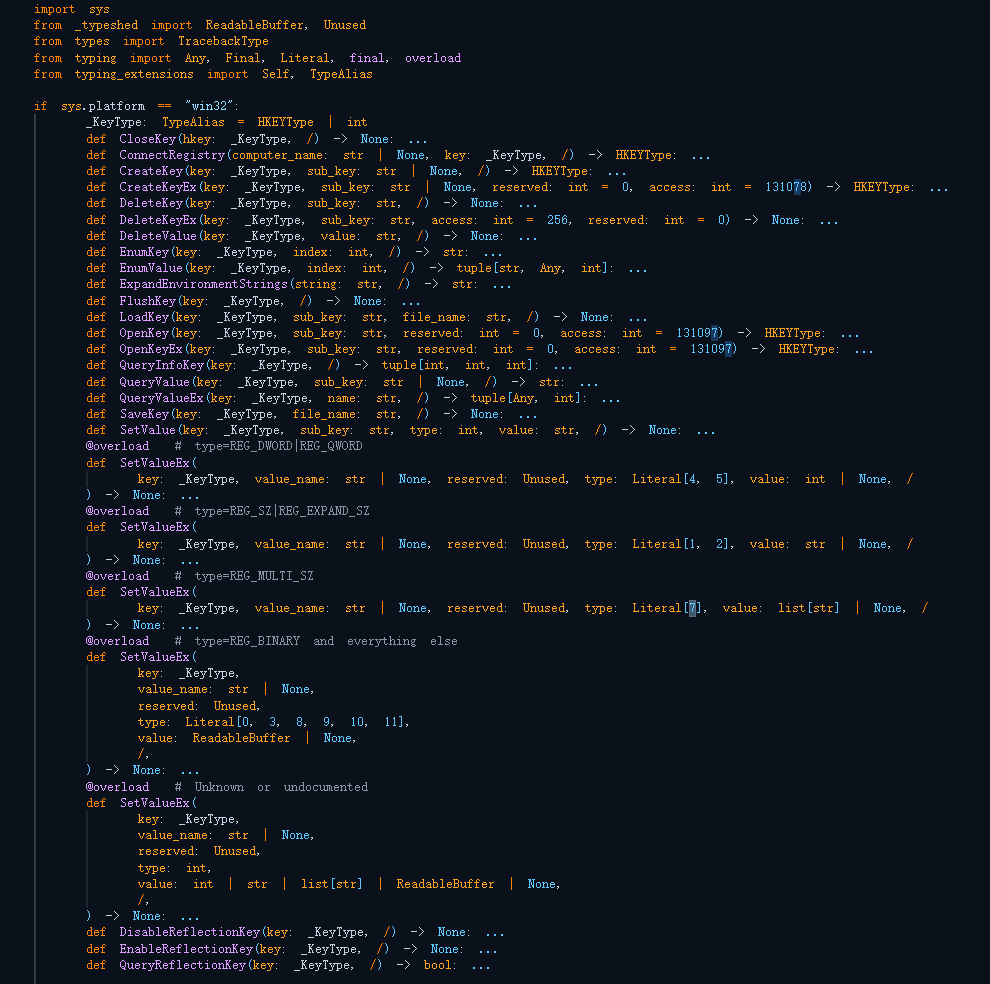

winreg查询Windows注册表的一些基本用法

注册表是Windows操作系统中用于存储配置信息的数据库。它包含了关于系统硬件、已安装的应用程序、用户账户设置以及系统设置的信息。 特别地,当我们需要某些软件的配置配息时,主要在HKEY_CURRENT_USER和HKEY_LOCAL_MACHINE下的SoftWare内进行查询操作。 …...

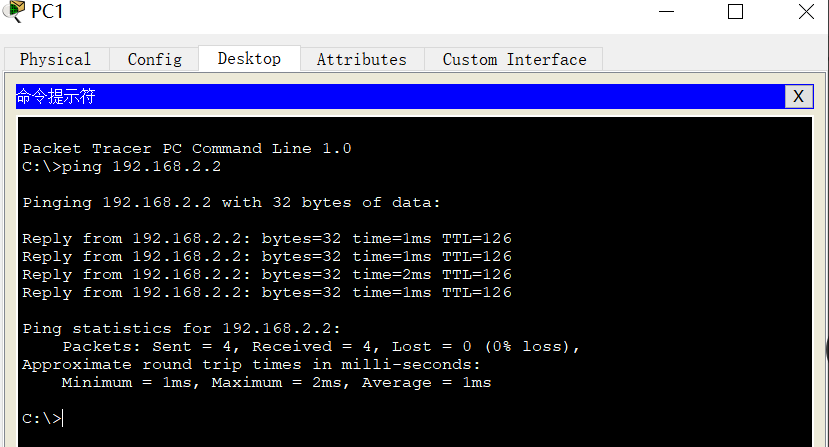

计算机网络|| 路由器和交换机的配置

一、实验目的 1. 了解路由器和交换机的工作模式和使用方法; 2. 熟悉 Cisco 网络设备的基本配置命令; 3. 掌握 Cisco 路由器的基本配置方式及配置命令; 4. 掌握路由器和交换机的基本配置与管理方法。 二、实验环境 1. 运行 Windows 操作…...

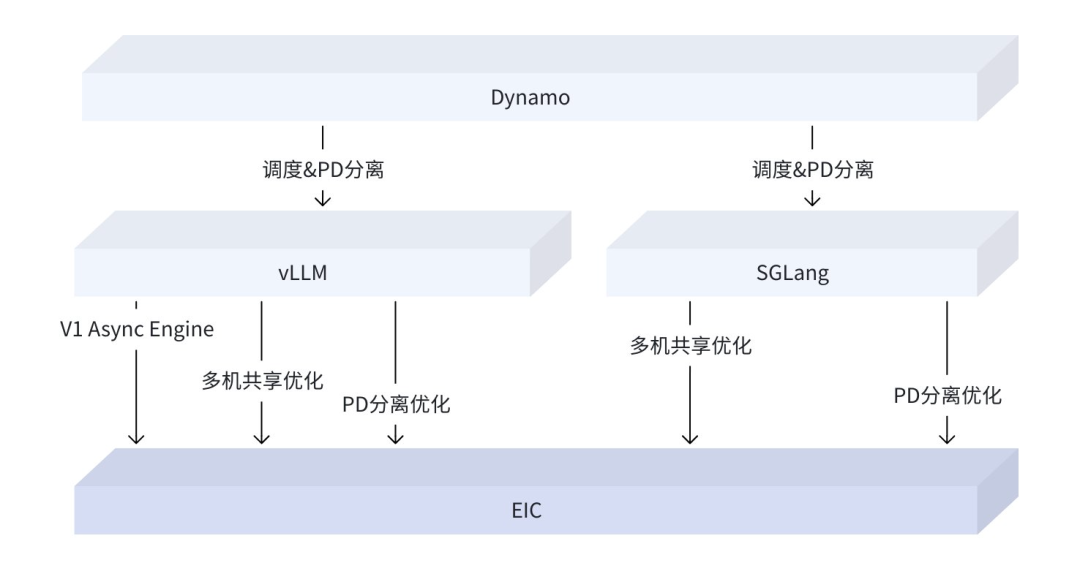

推理加速新范式:火山引擎高性能分布式 KVCache (EIC)核心技术解读

资料来源:火山引擎-开发者社区 分布式 KVCache 的兴起 背景 在大模型领域,随着模型参数规模的扩大和上下文长度增加,算力消耗显著增长。在 LLM 推理过程中,如何减少算力消耗并提升推理吞吐已经成为关键性优化方向。以多轮对话场…...

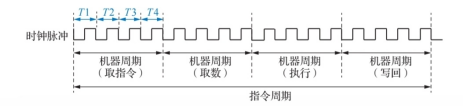

中央处理器(CPU)(概述、指令周期)

一、概述 主要功能:(1)程序控制(2)操作控制(3)时序控制(4)数据加工(5)中断处理 组成:早期冯诺依曼计算机的 CPU 主要由运算器和控制…...