STM32F4X NVIC中断概念

STM32F4X NVIC中断概念

- CPU查询状态两种方式

- 轮询查询

- 中断查询

- STM32有关中断的概念

- 中断向量表

- 系统中断

- 外设中断

- 中断号

- 中断优先级

- STM32F4X NVIC控制器

- NVIC控制器简介

- NVIC寄存器

- 优先级分组

- STM32F4X中断配置

- 优先级分组设置

- 配置外设中断

CPU查询状态两种方式

在讲解中断的概念之前,先了解一些CPU查询状态的两种方法,分别是轮询查询和中断查询。

轮询查询

轮询查询的方法是在规定的时间内循环查询某个外设的状态。举个日常生活的例子来做进一步的说明,比如你的朋友告诉你早上要到你家拜访,但是没说具体的拜访时间,在早上的那段时间你正在打扫卫生,因为你不知到你的朋友什么时候到,所以你必须每隔一段时间,比如每隔10分钟就开门查看一次,看你朋友是否已经到。类比到CPU也是一样的道理,比如串口需要接收一个数据,如果使用轮询的方式,CPU就必须每隔一段时间去查询串口接收寄存器的标志位是否有数据,如果没有就继续等待下一次时间继续查询,如果有就读取数据。轮询查询的缺点就是CPU需要频繁读取外设状态,很耗CPU的时间。

中断查询

中断查询的意思就是当某个外设有数据时,就会给CPU发一个信号,告诉CPU有数据到了,要处理,在外设没有给信号的时间,CPU可以去做其他的事情。同样用上面的生活例子做个说明,你的朋友告诉你早上要到你家拜访,没说具体的拜访时间,但是你告诉他如果到了就按下门铃,因为有门铃这个信号,所以当门铃没有响的时候,就代表朋友没有到,你可以去做其他的事情,不用再去频繁开门看你朋友是否已经到,当门铃响的时候,就代表朋友到了,这时候才去开门。

所以中断就是CPU可以暂停当前的工作,去执行中断处理函数中的任务,处理完之后再继续执行暂停的工作。

STM32有关中断的概念

中断向量表

在STM32F4的启动文件中,定义了STM32F4这款芯片的中断向量表,其中包含了16个系统中断和82个外设中断。中断向量表的作用是给MCU的所有中断服务函数都设置一个地址,这样中断到的时候CPU就会到相应的地址去执行中断服务函数。

系统中断

无论是哪一家MCU厂商,只要是用Crotex-M4的架构,其系统中断都是一样的,MCU厂商不能改变系统中断。

DCD __initial_sp ; Top of Stack

DCD Reset_Handler ; Reset Handler

DCD NMI_Handler ; NMI Handler

DCD HardFault_Handler ; Hard Fault Handler

DCD MemManage_Handler ; MPU Fault Handler

DCD BusFault_Handler ; Bus Fault Handler

DCD UsageFault_Handler ; Usage Fault Handler

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD SVC_Handler ; SVCall Handler

DCD DebugMon_Handler ; Debug Monitor Handler

DCD 0 ; Reserved

DCD PendSV_Handler ; PendSV Handler

DCD SysTick_Handler ; SysTick Handler

外设中断

外设中断是每家MCU厂商自己设计的,不同的MCU都有自己不同的外设,所以外设中断也会不同,STM32F4定义82个外设中断。

DCD WWDG_IRQHandler ; Window WatchDog

DCD PVD_IRQHandler ; PVD through EXTI Line detection

DCD TAMP_STAMP_IRQHandler ; Tamper and TimeStamps through the EXTI line

DCD RTC_WKUP_IRQHandler ; RTC Wakeup through the EXTI line

DCD FLASH_IRQHandler ; FLASH

DCD RCC_IRQHandler ; RCC

DCD EXTI0_IRQHandler ; EXTI Line0

DCD EXTI1_IRQHandler ; EXTI Line1

DCD EXTI2_IRQHandler ; EXTI Line2

DCD EXTI3_IRQHandler ; EXTI Line3

DCD EXTI4_IRQHandler ; EXTI Line4

DCD DMA1_Stream0_IRQHandler ; DMA1 Stream 0

DCD DMA1_Stream1_IRQHandler ; DMA1 Stream 1

DCD DMA1_Stream2_IRQHandler ; DMA1 Stream 2

DCD DMA1_Stream3_IRQHandler ; DMA1 Stream 3

DCD DMA1_Stream4_IRQHandler ; DMA1 Stream 4

DCD DMA1_Stream5_IRQHandler ; DMA1 Stream 5

DCD DMA1_Stream6_IRQHandler ; DMA1 Stream 6

DCD ADC_IRQHandler ; ADC1, ADC2 and ADC3s

DCD CAN1_TX_IRQHandler ; CAN1 TX

DCD CAN1_RX0_IRQHandler ; CAN1 RX0

DCD CAN1_RX1_IRQHandler ; CAN1 RX1

DCD CAN1_SCE_IRQHandler ; CAN1 SCE

DCD EXTI9_5_IRQHandler ; External Line[9:5]s

DCD TIM1_BRK_TIM9_IRQHandler ; TIM1 Break and TIM9

DCD TIM1_UP_TIM10_IRQHandler ; TIM1 Update and TIM10

DCD TIM1_TRG_COM_TIM11_IRQHandler ; TIM1 Trigger and Commutation and TIM11

DCD TIM1_CC_IRQHandler ; TIM1 Capture Compare

DCD TIM2_IRQHandler ; TIM2

DCD TIM3_IRQHandler ; TIM3

DCD TIM4_IRQHandler ; TIM4

DCD I2C1_EV_IRQHandler ; I2C1 Event

DCD I2C1_ER_IRQHandler ; I2C1 Error

DCD I2C2_EV_IRQHandler ; I2C2 Event

DCD I2C2_ER_IRQHandler ; I2C2 Error

DCD SPI1_IRQHandler ; SPI1

DCD SPI2_IRQHandler ; SPI2

DCD USART1_IRQHandler ; USART1

DCD USART2_IRQHandler ; USART2

DCD USART3_IRQHandler ; USART3

DCD EXTI15_10_IRQHandler ; External Line[15:10]s

DCD RTC_Alarm_IRQHandler ; RTC Alarm (A and B) through EXTI Line

DCD OTG_FS_WKUP_IRQHandler ; USB OTG FS Wakeup through EXTI line

DCD TIM8_BRK_TIM12_IRQHandler ; TIM8 Break and TIM12

DCD TIM8_UP_TIM13_IRQHandler ; TIM8 Update and TIM13

DCD TIM8_TRG_COM_TIM14_IRQHandler ; TIM8 Trigger and Commutation and TIM14

DCD TIM8_CC_IRQHandler ; TIM8 Capture Compare

DCD DMA1_Stream7_IRQHandler ; DMA1 Stream7

DCD FSMC_IRQHandler ; FSMC

DCD SDIO_IRQHandler ; SDIO

DCD TIM5_IRQHandler ; TIM5

DCD SPI3_IRQHandler ; SPI3

DCD UART4_IRQHandler ; UART4

DCD UART5_IRQHandler ; UART5

DCD TIM6_DAC_IRQHandler ; TIM6 and DAC1&2 underrun errors

DCD TIM7_IRQHandler ; TIM7

DCD DMA2_Stream0_IRQHandler ; DMA2 Stream 0

DCD DMA2_Stream1_IRQHandler ; DMA2 Stream 1

DCD DMA2_Stream2_IRQHandler ; DMA2 Stream 2

DCD DMA2_Stream3_IRQHandler ; DMA2 Stream 3

DCD DMA2_Stream4_IRQHandler ; DMA2 Stream 4

DCD ETH_IRQHandler ; Ethernet

DCD ETH_WKUP_IRQHandler ; Ethernet Wakeup through EXTI line

DCD CAN2_TX_IRQHandler ; CAN2 TX

DCD CAN2_RX0_IRQHandler ; CAN2 RX0

DCD CAN2_RX1_IRQHandler ; CAN2 RX1

DCD CAN2_SCE_IRQHandler ; CAN2 SCE

DCD OTG_FS_IRQHandler ; USB OTG FS

DCD DMA2_Stream5_IRQHandler ; DMA2 Stream 5

DCD DMA2_Stream6_IRQHandler ; DMA2 Stream 6

DCD DMA2_Stream7_IRQHandler ; DMA2 Stream 7

DCD USART6_IRQHandler ; USART6

DCD I2C3_EV_IRQHandler ; I2C3 event

DCD I2C3_ER_IRQHandler ; I2C3 error

DCD OTG_HS_EP1_OUT_IRQHandler ; USB OTG HS End Point 1 Out

DCD OTG_HS_EP1_IN_IRQHandler ; USB OTG HS End Point 1 In

DCD OTG_HS_WKUP_IRQHandler ; USB OTG HS Wakeup through EXTI

DCD OTG_HS_IRQHandler ; USB OTG HS

DCD DCMI_IRQHandler ; DCMI

DCD CRYP_IRQHandler ; CRYP crypto

DCD HASH_RNG_IRQHandler ; Hash and Rng

DCD FPU_IRQHandler ; FPU

中断号

中断号可以理解成每个中断的索引,是给用户使用的,中断号要跟中断向量表中的中断服务函数一一对应,在STM32F4中,中断号定义在stm32f4xx.h中

NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */MemoryManagement_IRQn = -12, /*!< 4 Cortex-M4 Memory Management Interrupt */BusFault_IRQn = -11, /*!< 5 Cortex-M4 Bus Fault Interrupt */UsageFault_IRQn = -10, /*!< 6 Cortex-M4 Usage Fault Interrupt */SVCall_IRQn = -5, /*!< 11 Cortex-M4 SV Call Interrupt */DebugMonitor_IRQn = -4, /*!< 12 Cortex-M4 Debug Monitor Interrupt */PendSV_IRQn = -2, /*!< 14 Cortex-M4 Pend SV Interrupt */SysTick_IRQn = -1, /*!< 15 Cortex-M4 System Tick Interrupt */

/****** STM32 specific Interrupt Numbers **********************************************************************/WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */PVD_IRQn = 1, /*!< PVD through EXTI Line detection Interrupt */TAMP_STAMP_IRQn = 2, /*!< Tamper and TimeStamp interrupts through the EXTI line */RTC_WKUP_IRQn = 3, /*!< RTC Wakeup interrupt through the EXTI line */FLASH_IRQn = 4, /*!< FLASH global Interrupt */RCC_IRQn = 5, /*!< RCC global Interrupt */EXTI0_IRQn = 6, /*!< EXTI Line0 Interrupt */EXTI1_IRQn = 7, /*!< EXTI Line1 Interrupt */EXTI2_IRQn = 8, /*!< EXTI Line2 Interrupt */EXTI3_IRQn = 9, /*!< EXTI Line3 Interrupt */EXTI4_IRQn = 10, /*!< EXTI Line4 Interrupt */DMA1_Stream0_IRQn = 11, /*!< DMA1 Stream 0 global Interrupt */DMA1_Stream1_IRQn = 12, /*!< DMA1 Stream 1 global Interrupt */DMA1_Stream2_IRQn = 13, /*!< DMA1 Stream 2 global Interrupt */DMA1_Stream3_IRQn = 14, /*!< DMA1 Stream 3 global Interrupt */DMA1_Stream4_IRQn = 15, /*!< DMA1 Stream 4 global Interrupt */DMA1_Stream5_IRQn = 16, /*!< DMA1 Stream 5 global Interrupt */DMA1_Stream6_IRQn = 17, /*!< DMA1 Stream 6 global Interrupt */ADC_IRQn = 18, /*!< ADC1, ADC2 and ADC3 global Interrupts */CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */TIM2_IRQn = 28, /*!< TIM2 global Interrupt */TIM3_IRQn = 29, /*!< TIM3 global Interrupt */TIM4_IRQn = 30, /*!< TIM4 global Interrupt */I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */SPI1_IRQn = 35, /*!< SPI1 global Interrupt */SPI2_IRQn = 36, /*!< SPI2 global Interrupt */USART1_IRQn = 37, /*!< USART1 global Interrupt */USART2_IRQn = 38, /*!< USART2 global Interrupt */USART3_IRQn = 39, /*!< USART3 global Interrupt */EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */FSMC_IRQn = 48, /*!< FSMC global Interrupt */SDIO_IRQn = 49, /*!< SDIO global Interrupt */TIM5_IRQn = 50, /*!< TIM5 global Interrupt */SPI3_IRQn = 51, /*!< SPI3 global Interrupt */UART4_IRQn = 52, /*!< UART4 global Interrupt */UART5_IRQn = 53, /*!< UART5 global Interrupt */TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */TIM7_IRQn = 55, /*!< TIM7 global interrupt */DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */ETH_IRQn = 61, /*!< Ethernet global Interrupt */ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */USART6_IRQn = 71, /*!< USART6 global interrupt */I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */DCMI_IRQn = 78, /*!< DCMI global interrupt */CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */FPU_IRQn = 81 /*!< FPU global interrupt

中断号是由MCU厂商定义的,用户不能修改。

中断优先级

正如人们在做事情的时候,会把事情的重要性进行划分,重要的事情先做,不重要的事情最后做。中断也是如此,STM32F4可以设置中断的优先级,优先级高的中断代表很重要,必须马上处理,优先级低的中断就代表没那么重要,可以晚点处理。

STM32F4X NVIC控制器

NVIC控制器简介

NVIC控制器是STM32F4X用来管理MCU中的外设中断的控制器,NVIC控制器可管理200多个中断,但是STM32F4只使用了其中的82个,所以STM32F4X对NVIC控制器做了些处理。

NVIC寄存器

在core_cm4.h中可以看到NVIC的寄存器位

typedef struct

{__IO uint32_t ISER[8]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */uint32_t RESERVED0[24];__IO uint32_t ICER[8]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */uint32_t RSERVED1[24];__IO uint32_t ISPR[8]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */uint32_t RESERVED2[24];__IO uint32_t ICPR[8]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */uint32_t RESERVED3[24];__IO uint32_t IABR[8]; /*!< Offset: 0x200 (R/W) Interrupt Active bit Register */uint32_t RESERVED4[56];__IO uint8_t IP[240]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register (8Bit wide) */uint32_t RESERVED5[644];__O uint32_t STIR; /*!< Offset: 0xE00 ( /W) Software Trigger Interrupt Register */

} NVIC_Type;

ISER:中断使能寄存器,总共有8个32位的寄存器,每一个位控制一个中断,总共可以控制256个中断。但是STM32F4X总共有82个外设中断,所以只用到了前3个寄存器。往该寄存器的相应位写1,则代表该位的中断被使能。

ICER:中断除能寄存器,该寄存器与ISER寄存器相反,往该寄存器的相应位写1,则代表该位的中断被除能。

ISPR:中断挂起寄存器,往该寄存器的相应位写1,则代表该位的中断被挂起。

ICPR:中断解挂起寄存器,往该寄存器的相应位写1,则代表该位的中断被解挂。

IABR:中断激活寄存器,当某个中断被执行时,该寄存器的对应位会被置1,可以读取该寄存器知道哪些中断被执行。

IP:中断优先级寄存器,通过设置该寄存器可以设置外设中断的优先级。

优先级分组

STM32F4X支持中断优先级分组,主要是由SCB->AIRCR这个寄存器实现分组功能。STM32F4X优先级总共可以分成5组。由SCB->AIRCR的bit8~bit10决定。具体的分组如下

| 分组 | AIRCR[8:10] | 结果 |

|---|---|---|

| 0 | 111 | 0位抢占优先级 4位响应优先级 |

| 1 | 110 | 1位抢占优先级 3位响应优先级 |

| 2 | 101 | 2位抢占优先级 2位响应优先级 |

| 3 | 100 | 3位抢占优先级 1位响应优先级 |

| 4 | 011 | 4位抢占优先级 0位响应优先级 |

STM32F4X的优先级规则如下:

- 抢占优先级高的中断可以打断抢占优先级低的中断

- 抢占优先级相同的,响应优先级高的中断不能打断响应优先级低的中断

- 抢占优先级相同的,如果两个中断同时发生,响应优先级高的中断先执行

- 抢占优先级和响应优先级相同的,哪个中断先发生就先执行。

STM32F4X中断配置

STM32F4X的中断配置有以下两个步骤

- 先配置优先级分组

- 配置相应外设的中断

优先级分组设置

设置优先级分组只需调用以下函数即可

#define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority4 bits for subpriority */

#define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority3 bits for subpriority */

#define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority2 bits for subpriority */

#define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority1 bits for subpriority */

#define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority0 bits for subpriority *//*

NVIC_PriorityGroup:对应的优先级分组

*/

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

该函数只需在初始化时设置一次即可。

配置外设中断

typedef struct

{uint8_t NVIC_IRQChannel; // 中断号 uint8_t NVIC_IRQChannelPreemptionPriority; // 抢占优先级 uint8_t NVIC_IRQChannelSubPriority; // 响应优先级 FunctionalState NVIC_IRQChannelCmd; // 是否使能

} NVIC_InitTypeDef;

/*

NVIC_InitStruct:中断结构体

*/

void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct)

比如现在需要配置串口接收中断,代码如下

NVIC_InitTypeDef NVIC_InitStruct;

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2); // 设置优先级分组为2,即2位抢占优先级和2位响应优先级NVIC_InitStruct.NVIC_IRQChannel = USART1_IRQn; // USART1 中断编号

NVIC_InitStruct.NVIC_IRQChannelPreemptionPriority = 1; // 抢占优先级为1

NVIC_InitStruct.NVIC_IRQChannelSubPriority = 1; // 响应优先级为1

NVIC_InitStruct.NVIC_IRQChannelCmd = ENABLE; // 使能中断

NVIC_Init(&NVIC_InitStruct); // 初始化中断void USART1_IRQHandler(void) // 中断处理函数

{// 业务代码

}

相关文章:

STM32F4X NVIC中断概念

STM32F4X NVIC中断概念 CPU查询状态两种方式轮询查询中断查询 STM32有关中断的概念中断向量表系统中断外设中断中断号中断优先级 STM32F4X NVIC控制器NVIC控制器简介NVIC寄存器优先级分组 STM32F4X中断配置优先级分组设置配置外设中断 CPU查询状态两种方式 在讲解中断的概念之…...

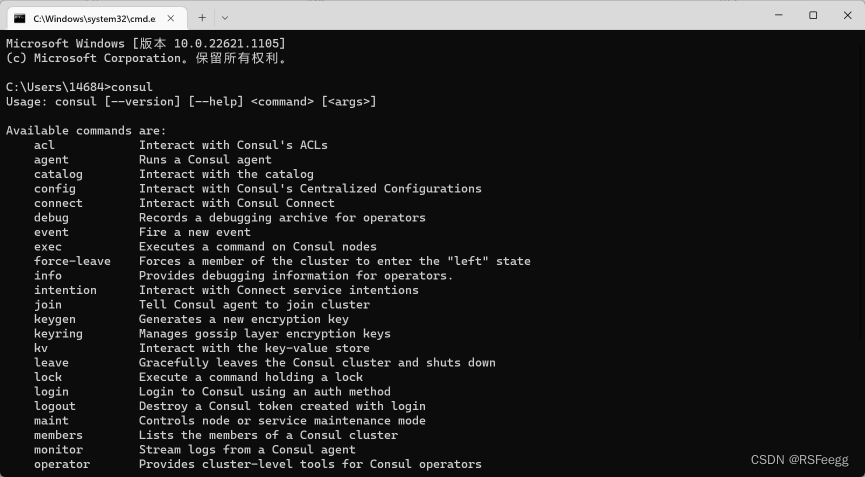

关于consul的下载方法

linux下 sudo yum install -y yum-utils sudo yum-config-manager --add-repo https://rpm.releases.hashicorp.com/RHEL/hashicorp.repo sudo yum -y install consulwindow下 https://developer.hashicorp.com/consul/downloads 然后把里面的exe文件放在gopath下就行了 验证…...

应用在汽车前照灯系统中的环境光传感芯片

为了保证行车照明的安全性和方便性,减轻驾驶员的劳动强度。近年来,出现了许多新的照明控制系统,例如用于日间驾驶的自动照明系统、光束调节系统、延迟控制等。尤其是汽车自适应前照灯系统,它是一种能够自动改变两种以上的光型以适…...

Python Flask+Echarts+sklearn+MySQL(评论情感分析、用户推荐、BI报表)项目分享

Python FlaskEchartssklearnMySQL(评论情感分析、用户推荐、BI报表)项目分享 项目背景: 随着互联网的快速发展和智能手机的普及,人们越来越倾向于在网上查找餐厅、购物中心、酒店和旅游景点等商户的点评和评分信息,以便做出更好的消费决策。…...

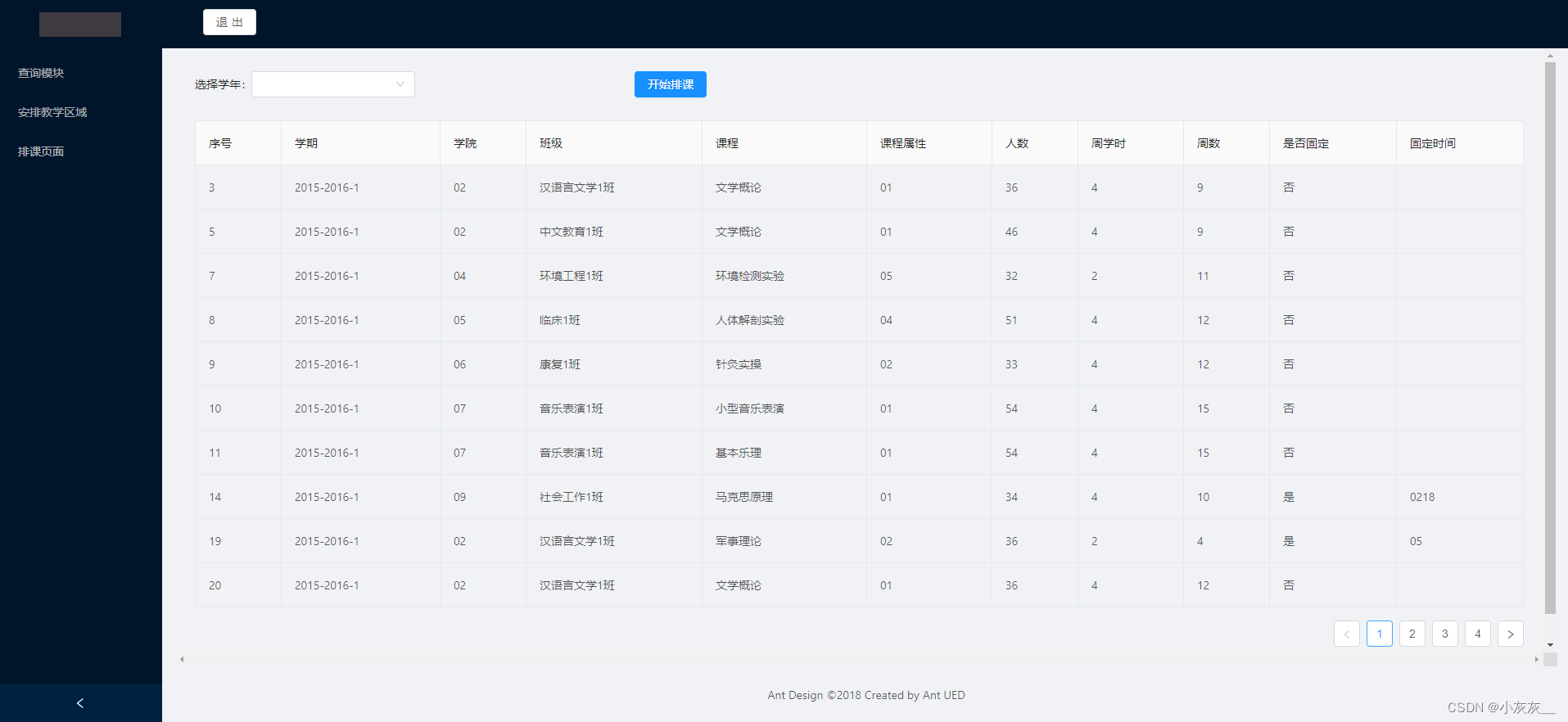

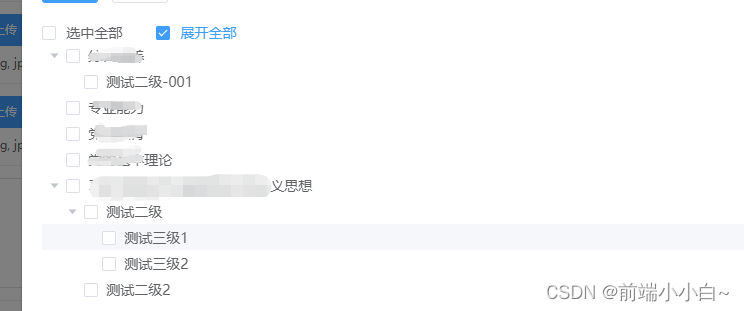

开源项目-高校自动排课系统

哈喽,大家好,今天给大家带来一个开源项目-基于遗传算法的一个高校自动排课系统,同时也是一个前后端分离项目。 前端:React 后端:SpringBoot+MyBatis+MySQL数据库 高校自动排课系统的主要功能包括查询模块,安排教学区域,排课页面三部分 登录 查询模块 可以根据学年…...

IP网络广播系统草坪音箱景区系统防水石头,草坪音箱的应用

IP网络广播系统草坪音箱景区系统防水石头,草坪音箱的应用 SV-7045V是深圳锐科达电子有限公司的一款防水网络草坪音箱,具有10/100M以太网接口,可将网络音源通过自带的功放和喇叭输出播放,可达到功率20W。常用场景:公园ip草坪音箱&…...

拒绝摆烂!C语言练习打卡第二天

🔥博客主页:小王又困了 📚系列专栏:每日一练 🌟人之为学,不日近则日退 ❤️感谢大家点赞👍收藏⭐评论✍️ 目录 一、选择题 📝1.第一题 📝2.第二题 📝…...

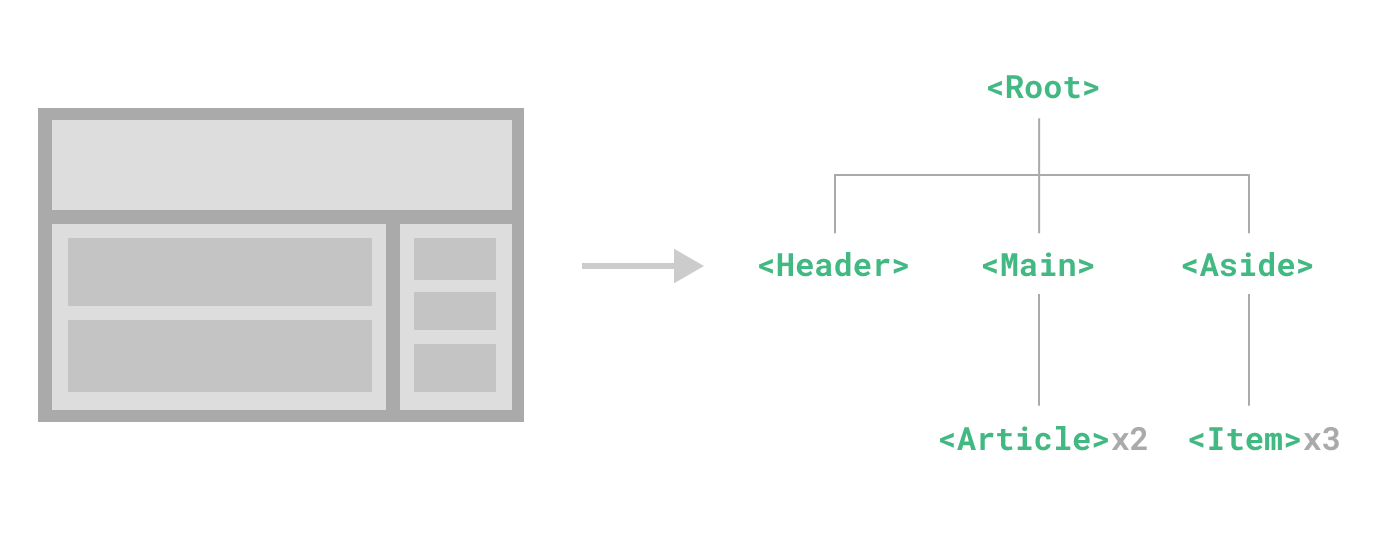

第四章:前端框架Vue基础入门

文章目录 一、Vue框架概述1.1 声明响应式的数据 二、Vue内置指令2.1、条件渲染指令v-if/v-show2.2 v-for: 列表渲染2.3、v-text/v-html 模板指令2.4 v-on:事件监听器2.6 动态绑定v-bind2.7 v-model表单元素值绑定 三、计算属性与监视3.1 计算属性computed3.2 watch侦听器3.3 wa…...

企业权限管理(十三)-用户关联角色操作

用户关联角色操作 从前台发送请求 <a href"${pageContext.request.contextPath}/user/findUserByIdAndAllRole.do?id${user.id}" class"btn bg-olive btn-xs">添加角色</a>查询用户以及用户可以添加的角色 usercontroller //查询用户以及用…...

深入理解Vue 3.0x中的Suspense和异步组件

深入理解Vue 3.0x中的Suspense和异步组件 Vue 3.0x作为Vue.js框架的最新版本,引入了许多创新特性,其中Suspense和异步组件是重要的改进之一。在本文中,我们将深入探讨这两个特性,了解它们如何为现代Web应用带来更好的性能和用户体…...

—— Ajax 原理)

Ajax 笔记(三)—— Ajax 原理

笔记目录 3. Ajax 原理3.1 XMLHttpRequest3.1.1 XHR 使用步骤3.1.2 查询参数3.1.3 数据提交 3.2 Promise3.2.1 Promise 使用步骤3.2.2 Promise 状态3.2.3 Promise 和 XHR 应用小案例 3.3 封装简易 axios3.3.1 核心封装代码3.3.2 支持传递查询参数3.3.3 支持传递请求体数据 Ajax…...

el-tree通过default-expand-all动态控制展开/折叠

1、如下图通过勾选框动态控制展开/折叠,全选/清空 2、实现方式如下:定义key,监听checked2修改treeKey,重新渲染tere;附加全选和清空。 <div class"tree"><el-checkbox v-model"checked1"…...

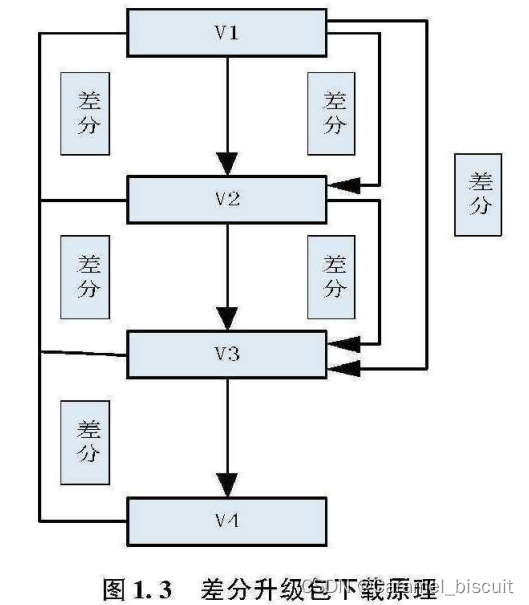

基于Bsdiff差分算法的汽车OTA升级技术研究(学习)

摘要 针对汽车OTA整包升级时,用户下载时间长,升级时间长,设备服务器端压力大等问题,本文提出了一种基于Bsdiff差分算法的汽车OTA升级技术。该算法能够对比新旧版本的差异,进行差分文件下载,减少软件包的下…...

如何使用CSS实现一个纯CSS的滚动条样式?

聚沙成塔每天进步一点点 ⭐ 专栏简介⭐ 使用CSS实现自定义滚动条样式⭐ 写在最后 ⭐ 专栏简介 前端入门之旅:探索Web开发的奇妙世界 记得点击上方或者右侧链接订阅本专栏哦 几何带你启航前端之旅 欢迎来到前端入门之旅!这个专栏是为那些对Web开发感兴趣…...

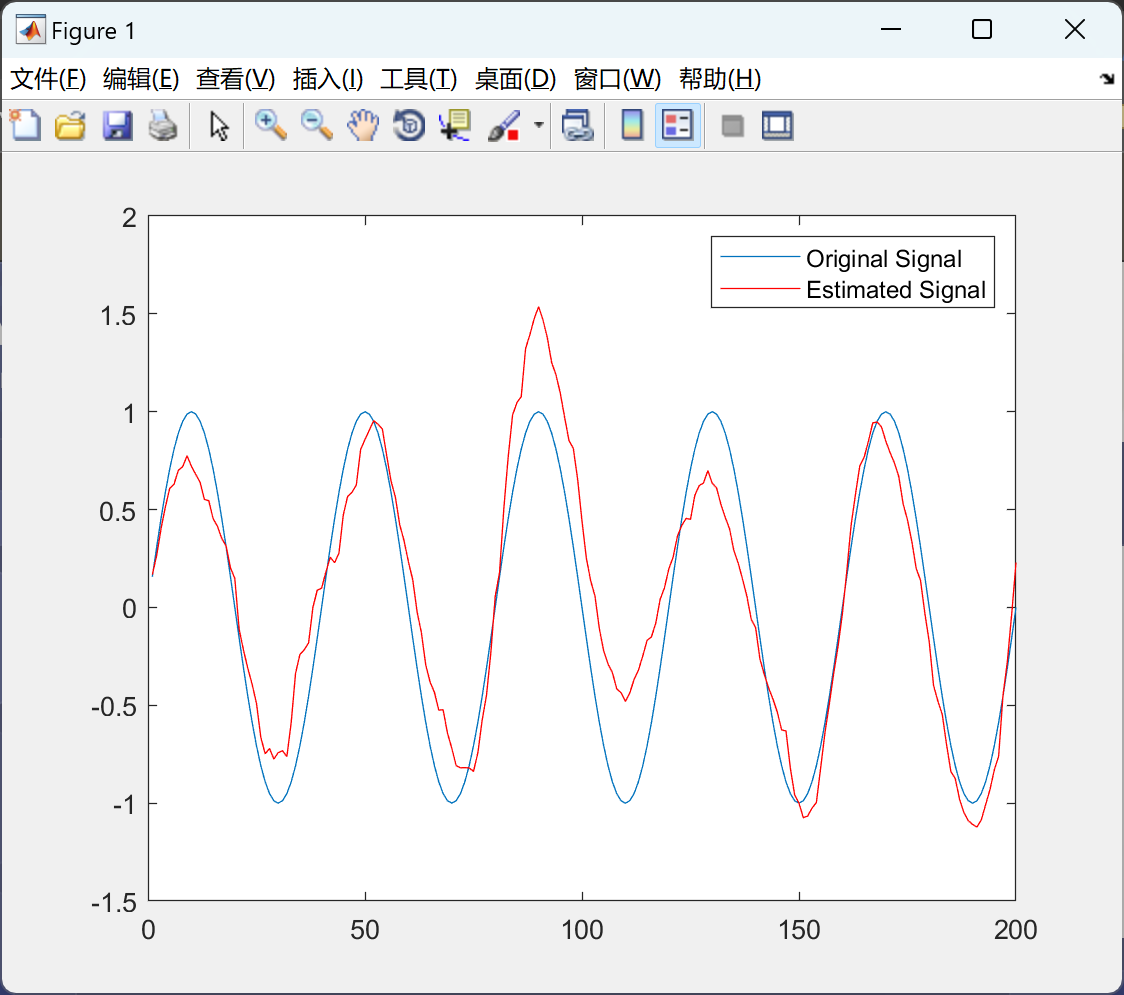

使用维纳过滤器消除驾驶舱噪音(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

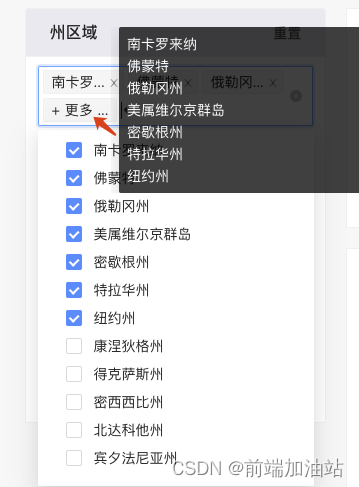

vue所有UI库通用)tree-select 下拉多选(设置 maxTagPlaceholder 隐藏 tag 时显示的内容,支持鼠标悬浮展示更多

如果可以实现记得点赞分享,谢谢老铁~ 1.需求描述 引用的下拉树形结构支持多选,限制选中tag的个数,且超过制定个数,鼠标悬浮展示更多已选中。 2.先看下效果图 3.实现思路 首先根据API文档,先设置maxTagC…...

进行 200 瓦太阳能 (PV) 模块设计以测量太阳能光伏阵列的电压、电流和功率、综合负荷频率和电压控制系统的方法研究(Simulink实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

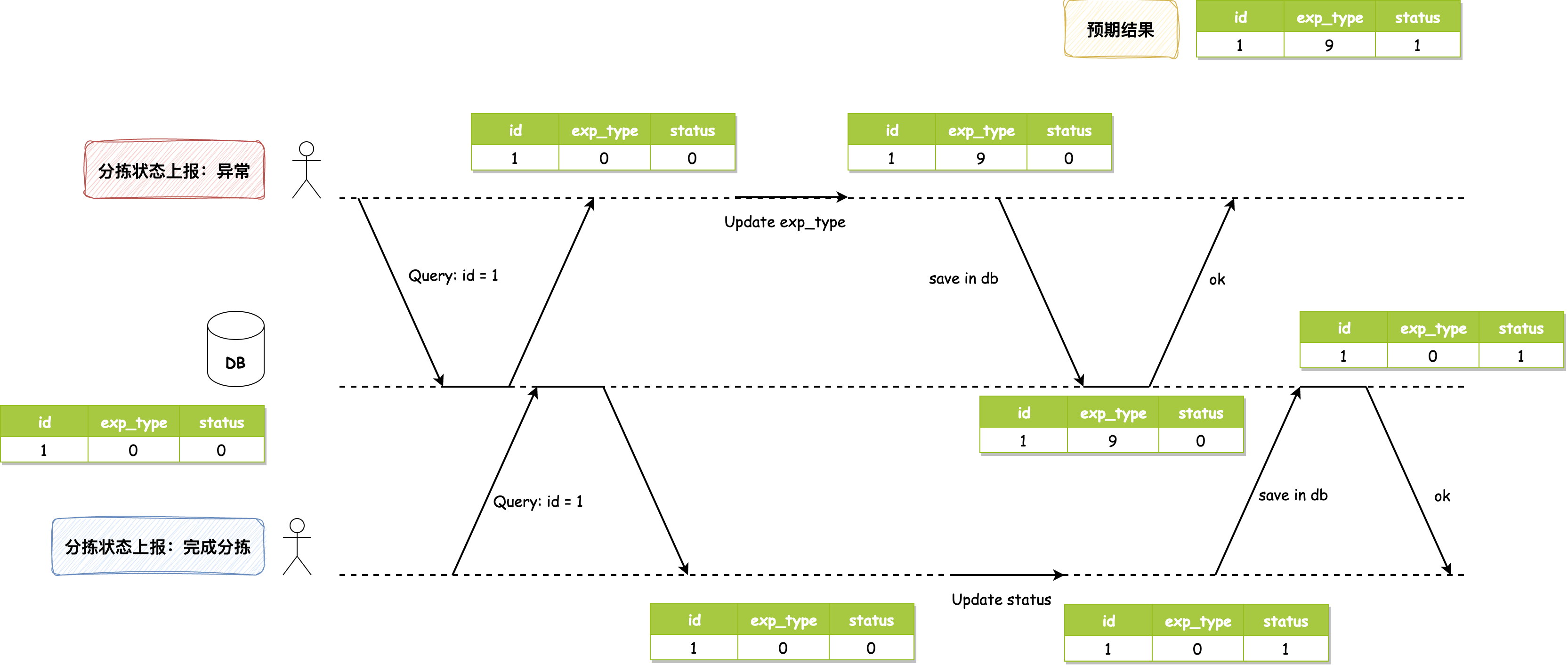

实战:工作中对并发问题的处理 | 京东物流技术团队

1. 问题背景 问题发生在快递分拣的流程中,我尽可能将业务背景简化,让大家只关注并发问题本身。 分拣业务针对每个快递包裹都会生成一个任务,我们称它为 task。task 中有两个字段需要关注,一个是分拣中发生的异常(exp…...

解决VSCode CPU高占问题的方法

如果你也遇到VSCode的CPU占用过高的问题,可以尝试使用官方自带的插件Bisect(扩展二分查找)功能来查找具体是哪个扩展出了问题。 找到“糟糕”的扩展可能很容易,也可能很困难。 打开扩展视图 ( CtrlShiftX ),禁用扩展&…...

tensorflow 1.x和3090、cuda部署

这里写目录标题 3090、cuda和tensorflow 1.x 3090、cuda和tensorflow 1.x 因为3090只支持cuda11.0的版本,而tensorflow1.已经不再维护,没有出支持cuda11.0的版本了。 nvidia提供了TF1.x对RTX 3090、cuda11等新硬件的支持。卸载已有的tensorflow-gpu包和…...

CANN/asc-devkit浮点ilogbf函数文档

ilogbf 【免费下载链接】asc-devkit 本项目是CANN 推出的昇腾AI处理器专用的算子程序开发语言,原生支持C和C标准规范,主要由类库和语言扩展层构成,提供多层级API,满足多维场景算子开发诉求。 项目地址: https://gitcode.com/can…...

Agent 一接文件树就开始改错目录:从 Working Directory Claim 到 Path Scope Fence 的工程实战

不少团队把文件树接进 Agent 后,第一次翻车往往不是改不动代码,而是改到了错误目录。一个修复本该落在 services/api,结果模型顺手把 infra/terraform 里的同名文件也改了;一个看似无害的批量替换,把 monorepo 里另一条…...

LicenseFinder高级配置指南:自定义许可证规则与决策继承

LicenseFinder高级配置指南:自定义许可证规则与决策继承 【免费下载链接】LicenseFinder Find licenses for your projects dependencies. 项目地址: https://gitcode.com/gh_mirrors/li/LicenseFinder LicenseFinder是一款强大的开源许可证管理工具…...

多语言交易所源码/币币交易+期权交易+永续合约+Defi借贷+新币申购+矿机理财/前端uniapp纯源码+后端php

简介: 多语言交易所源码/币币交易期权交易永续合约Defi借贷新币申购矿机理财/前端uniapp纯源码后端php 语言:7种,看图 前端是uniapp纯源码,只有手机端,后端是php框架,清理了后门的,是最开始蓝…...

乒乓球教程

【课程教程资料】乒乓球入门必看,全方位发球技巧教学 文件大小: 3.9GB内容特色: 3.9GB高清发球拆解,握拍站位旋转全囊括适用人群: 零基础球友、校园社团、陪练家长核心价值: 20课时速成稳定发球,直接提升实战得分率下载链接: https://pan.qu…...

对比使用Taotoken前后在模型API费用支出上的月度观察

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 对比使用Taotoken前后在模型API费用支出上的月度观察 作为一名个人开发者,我日常的开发工作离不开大语言模型的辅助&am…...

AI人工智能行业的现状:为什么说AI从业者的需求越来越大

一、AI产业爆发式增长:需求激增的时代底色2026年,人工智能产业已步入爆发式增长的黄金期,成为驱动全球经济复苏与产业变革的核心引擎。从全球市场来看,2025年AI市场规模达7575.8亿美元,同比增长18.7%,预计2…...

武汉大学等高校联手揭露AI助手的“记忆盲区“:它们真的记得你吗?

这项由武汉大学、香港中文大学和香港科技大学联合开展的研究以预印本形式于2026年5月发表,论文编号为arXiv:2605.06527,有兴趣深入了解的读者可以通过该编号查询完整论文。你有没有试过这样一件事:你和手机里的AI助手聊了很久,告诉…...

)

Win11自带加密真香!手把手教你用‘属性加密’保护私密文件夹(附防忘密码小技巧)

Win11原生加密全指南:从基础设置到高阶安全实践 在数字时代,隐私保护已成为每个电脑用户的刚需。当你刚升级到Win11系统,面对全新的界面和操作逻辑,可能会对如何保护敏感文件感到困惑。第三方加密软件固然功能强大,但它…...

多账号流量内容运营的数据归因与ROI优化:从经验驱动到算法决策的技术转型

📌 当一个团队同时运营20个以上的新媒体账号时,最大的问题不是"怎么发",而是"发了之后怎么知道哪条有用"。本文从数据工程角度,拆解多账号流量内容矩阵如何通过数据归因模型实现ROI优化,以星链引擎…...