AD7321代码SPI接口模数转换连接DAC0832输出verilog

名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出

软件:QuartusII

语言:VHDL

代码功能:

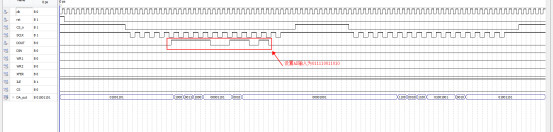

使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出

AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。

要求:有vhdl代码(详尽注释),有fpga连线图,有完整功能仿真结果,有方案分析。

演示视频:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出(代码在文末付费下载)软件:QuartusII语言:VHDL代码功能:使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。要求:有vhdl代码(详尽注释),有fp名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出(代码在文末付费下载)软件:QuartusII语言:VHDL代码功能:使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后,将数据通过DAC0832转换为模拟信号输出AD7321输入,(2000-输入)/6(仿真输出=009),DAC0832输出。要求:有vhdl代码(详尽注释),有fp![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=219

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=219

部分代码展示

LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all; --AD控制模块,输出011110011010 ENTITY AD7321 ISPORT (clk : IN STD_LOGIC;--时钟rst : IN STD_LOGIC;--复位CS_n : OUT STD_LOGIC;--AD控制信号SCLK : OUT STD_LOGIC;--AD控制信号DOUT : IN STD_LOGIC;--AD控制信号DIN : OUT STD_LOGIC;--AD控制信号DB : OUT STD_LOGIC_VECTOR(11 DOWNTO 0)--输出AD值); END AD7321; ARCHITECTURE behaval OF AD7321 ISTYPE State_type IS (s_init, s_cs_h, s_sclk, s_end); -- 定义状态SIGNAL state : State_type;SIGNAL cs_h_cnt : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";--CS计数SIGNAL sclk_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000";--sclk计数 BEGIN --状态机控制PROCESS (clk, rst)BEGINIF (rst = '1') THEN--复位state <= s_init;ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿CASE state ISWHEN s_init =>--初始状态state <= s_cs_h;WHEN s_cs_h =>--cS高电平状态IF (cs_h_cnt >= "1010") THEN--计数10个时钟state <= s_sclk;END IF;WHEN s_sclk =>--SCLK状态IF (sclk_cnt >= "00100000") THEN--计数32时钟state <= s_end;--结束END IF;WHEN s_end =>--结束状态state <= s_init;WHEN OTHERS =>END CASE;END IF;END PROCESS;--根据状态控制CS信号PROCESS (clk, rst)BEGINIF (rst = '1') THENCS_n <= '1';--复位ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿IF (state = s_cs_h) THEN--CS高电平状态CS_n <= '1';--输出高电平ELSIF (state = s_sclk) THEN--SCLK状态CS_n <= '0';--输出低电平END IF;END IF;END PROCESS;--根据状态控制SCLK信号PROCESS (clk, rst)BEGINIF (rst = '1') THENSCLK <= '1';--复位ELSIF (clk'EVENT AND clk = '1') THEN--时钟上升沿IF (state = s_sclk) THEN--SCLK状态SCLK <= NOT(sclk_cnt(0));--SCLK输出sclk_cnt(0)取反信号作为SCLKELSIF (state = s_end) THENSCLK <= '1';END IF;END IF;END PROCESS;

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

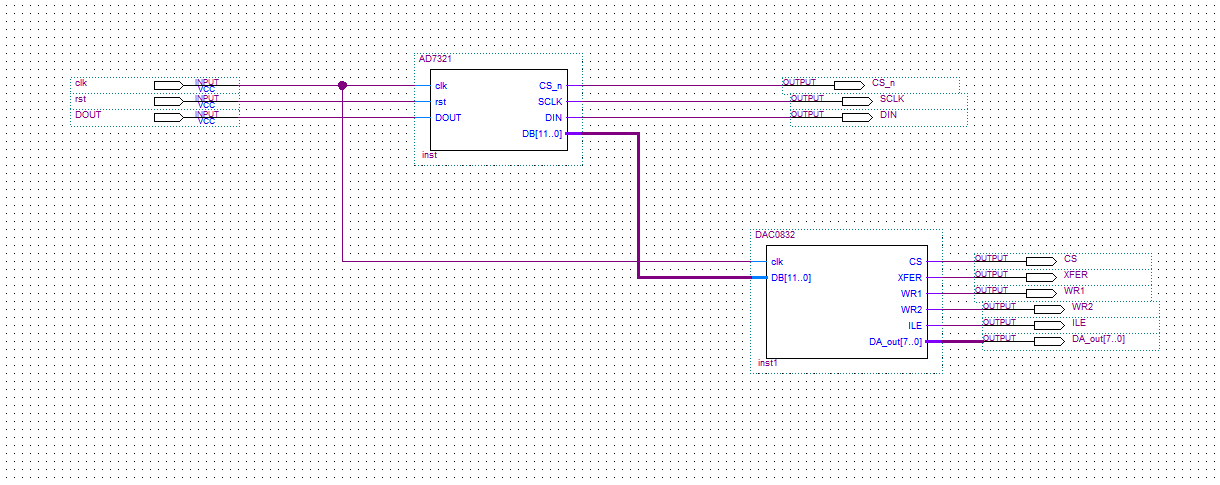

连线图

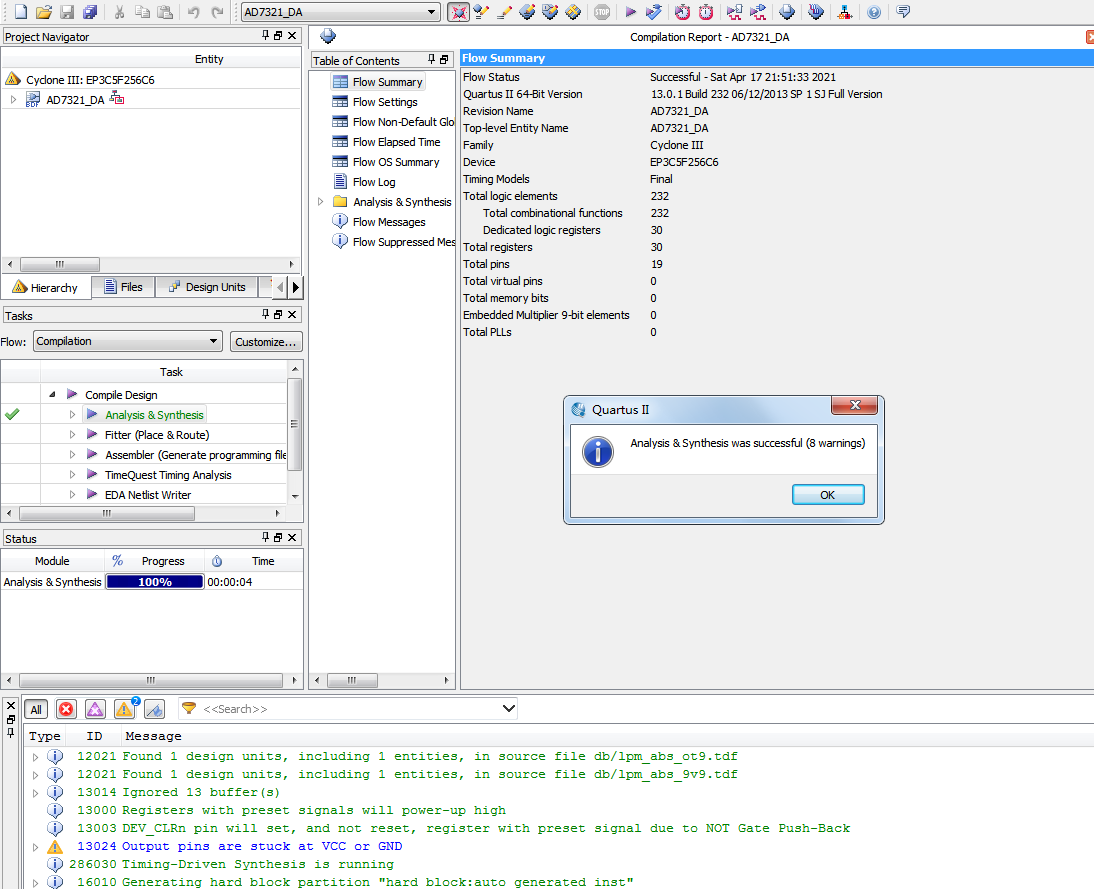

3. 程序编译

4. RTL图

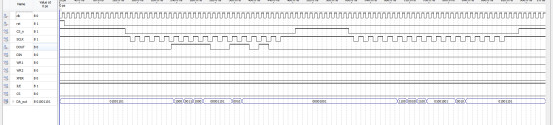

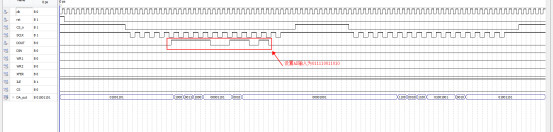

5. 仿真图

相关文章:

AD7321代码SPI接口模数转换连接DAC0832输出verilog

名称:AD7321代码12位ADC,SPI接口模数转换连接DAC0832输出 软件:QuartusII 语言:VHDL 代码功能: 使用VHDL语言编写代码,实现AD7321的控制,将模拟信号转换为数字信号,再经过处理后…...

JavaScript_Pig Game切换当前玩家

const current0El document.getElementById(current--0); const current1El document.getElementById(current--1); if (dice ! 1) {currentScore dice;current0El.textContent currentScore;} else {} });这是我们上个文章写的代码,这个代码明显是有问题的&…...

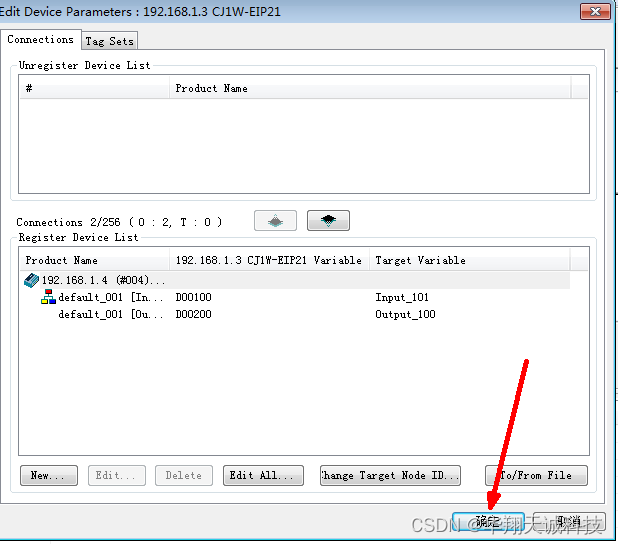

EtherNet Ip工业RFID读写器与欧姆龙PLC 配置示例说明

一、准备阶段 POE交换机欧姆龙PLC 支持EtherNet Ip协议CX-Programmer 9.5配置软件 二、配置读卡器 1、打开软件 2、选择网卡,如果多网卡的电脑请注意对应所接的网卡,网卡名一般为“Network adapter Realtek PCIe GBE Family” 3、点击“选择网卡”&…...

UE5简化打包大小

UE5.3默认空项目带初学者包的打包后1G多 简化思路: 1.不打包初学者包(或者创建时不包括初学者包,跳过第一条) 导航:ProjectSettings->Project->Packaging->Packaging->Advanced->List of maps to incl…...

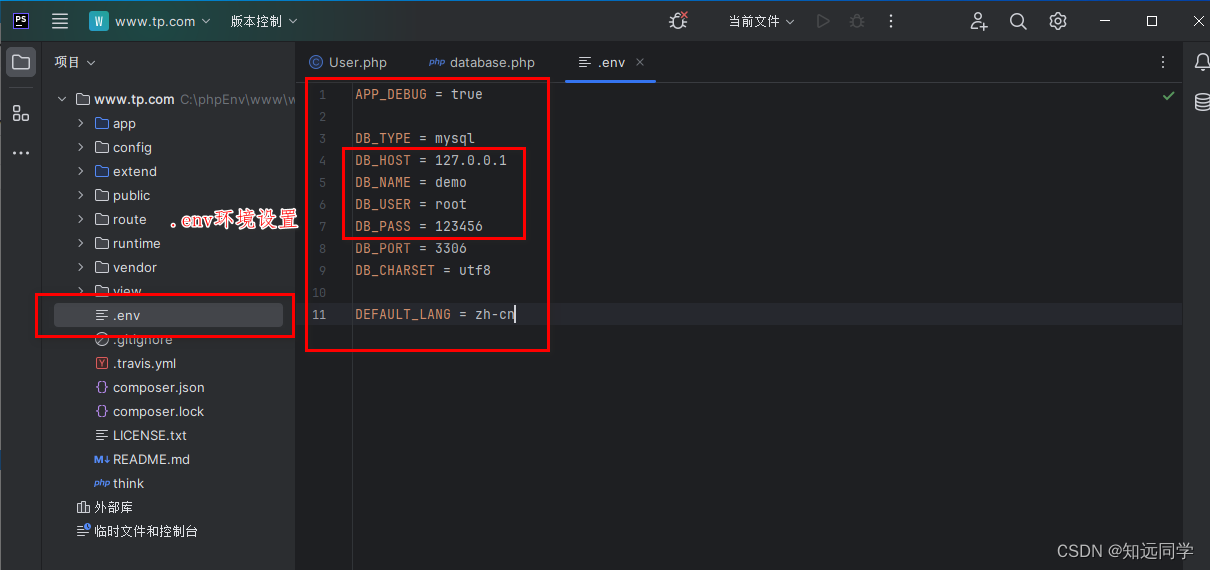

ThinkPHP8学习笔记

ThinkPHP8官方文档地址:ThinkPHP官方手册 一、composer换源 1、查看 composer 配置的命令composer config -g -l 2、禁用默认源镜像命令composer config -g secure-http false 3、修改为阿里云镜像源composer config -g repo.packagist composer https://mirror…...

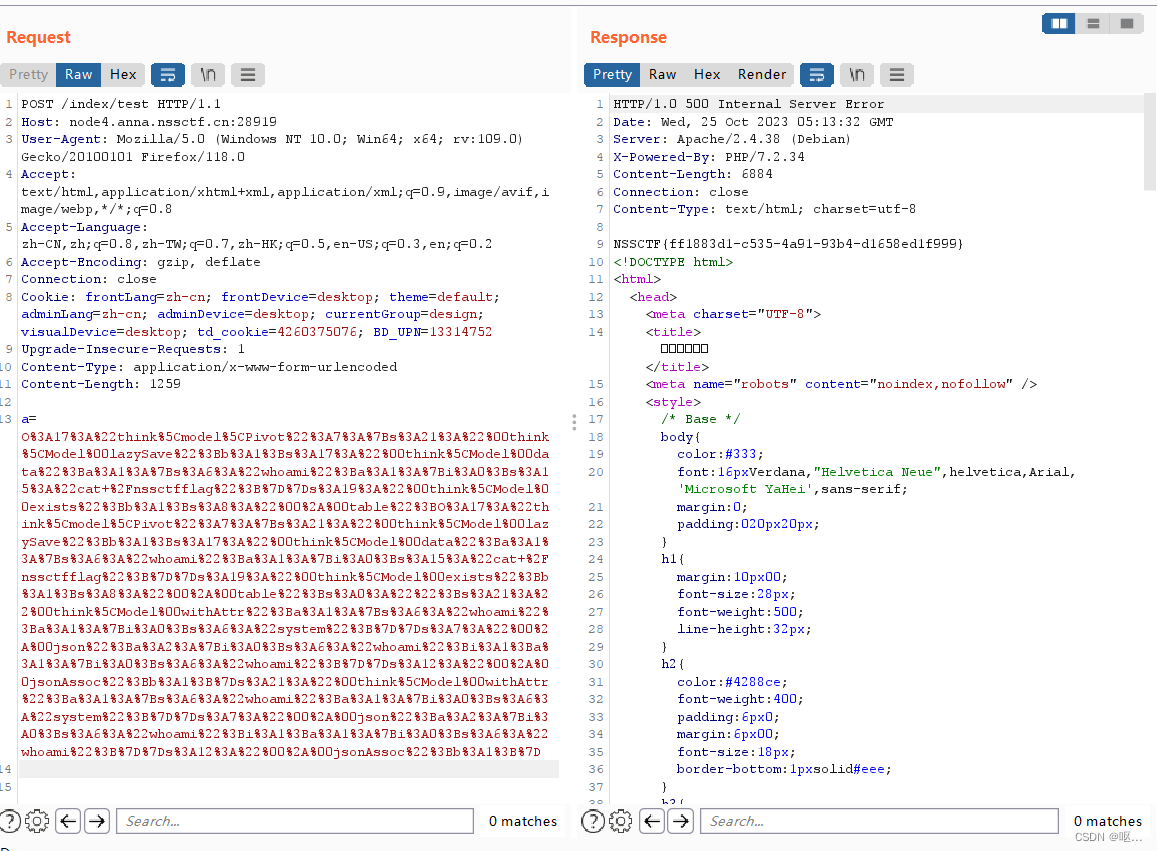

NSSCTF做题第9页(2)

[SWPUCTF 2022 新生赛]ez_1zpop <?php error_reporting(0); class dxg { function fmm() { return "nonono"; } } class lt { public $impohi; public $md51weclome; public $md52to NSS; function __construct() { $this-&…...

Rust笔记【1】

元组和解构语法 let tup : (i32, f64, u8) (666, 2.0, 1);let tup (666, 2.0, 1); let (x, y, z) tup;let x tup.0; let y tup.1; let z tup.2;数组类型 数组定义是方括号:[ ] 元组定义是小圆括号:( ) 结构体定义是大括号:{ }…...

代码随想录训练营day3:链表part1

理论 链表的增删操作时间复杂度O(1),查询时间复杂度O(n),因为要从头结点开始。使用场景和数据完全相反 链表的储存地址是不连续的。也和数组不同。 移除链表元素 利用虚拟头结点可以同意操作。不然删除头结点需要额外写。 记得返回的是虚拟头结点的next而不是虚拟头结点retu…...

Bootstrap的咖啡网站实例代码阅读笔记

目录 01-index.html的完整代码02-图片可以通过类 rounded-circle 设置为圆形显示03-<li class"nav-item mt-1 a">中,类mt-1是什么意思?类a又是什么意思?04-href"javascript:void(0);"是什么意思?05-类f…...

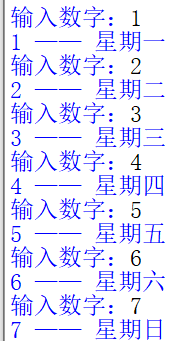

2021年06月 Python(二级)真题解析#中国电子学会#全国青少年软件编程等级考试

Python等级考试(1~6级)全部真题・点这里 一、单选题(共25题,每题2分,共50分) 第1题 执行下列代码后,运行结果是? seq[hello,good,morning] s*.join(seq) print(s)A: hello*good*m…...

FileWriter文件字符输出流

一.概念 以内存为基准,把内存中的数据以字符形式写出到文件中 二.构造器 public FileWriter(Filefile) 创建字节输出流管道与源文件对象接通 public FileWriter(String filepath) 创建字节输出流管道与源文件路径接通 public Filewriter(File file,boolean append) …...

Vue的八个基础命令及作用

1.v-text 作用:获取data数据, 设置标签的内容,以纯文本进行显示v-text 会覆盖 标签中的内容,如果想要拼接数据,可以直接在v-text中拼接如果拼接的是数字:直接使用 “”如果拼接的是字符串,需要使用与外部不同的引号进…...

Log日志详解分析

目录 1、log日志的用途2、log日志级别3、什么时候需要输出日志1. 系统启动参数、环境变量2. 异常捕获处3. 函数获得期望之外的结果时4. 关键操作 4、日志输出的内容5、 注意事项1. 日志信息不明确2. 特殊异常处理3. 日志输出顺序4. 临时调试日志 6、xml文件配置7、linux下查看日…...

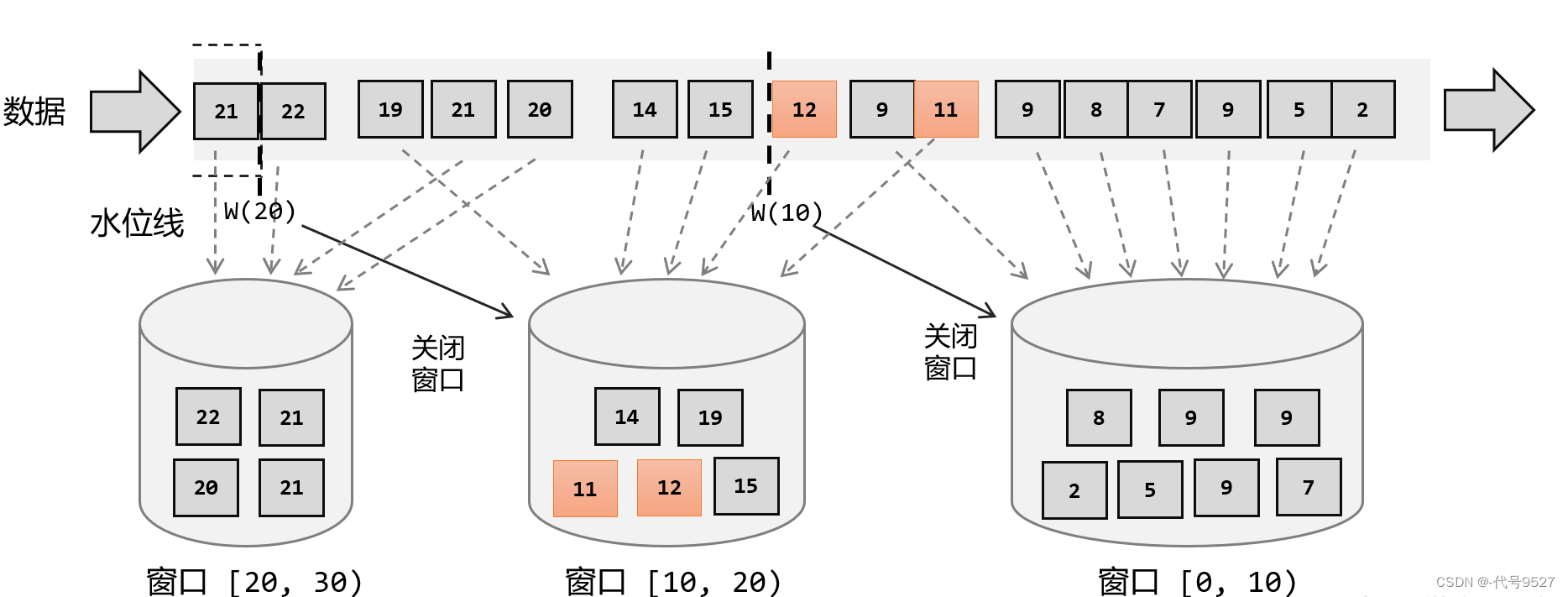

【API篇】九、Flink的水位线

文章目录 1、Flink时间语义2、事件时间和窗口3、水位线4、水位线和窗口的工作原理 1、Flink时间语义 事件时间处理时间 举个例子就是,一条数据在23:59:59产生,在00:00:01被处理,前者为事件时间,后者为处理时间。 从Flink1.12版本…...

#经典论文 异质山坡的物理模型 2 有效导水率

Binley, A., Beven, K., & Elgy, J. (1989). A physically based model of heterogeneous hillslopes: 2. Effective hydraulic conductivities. Water Resources Research, 25(6), 1227–1233. https://doi.org/10.1029/WR025i006p01227 这篇论文指出, 每个输…...

)

Java面试题-Redis-第一天(Redis简单介绍)

目录 一、Redis是什么?优缺点? 二、Redis为什么这么快? 三、Redis相较于Memcached有哪些优势? 四、为什么使用Redis做缓存? 五、为什么要用Redis而不用map/guava做缓存? 六、Redis的常用场景有哪些&am…...

Java 生成和读取JSON文件

下面的demo当中 ,是将json文件放到了zip包当中。如果不需要,可以拿掉。 1、生成对象JSON文件 public static void crateJson() {try {String orcPath "D:\\doc\\ts_service_orchestration.json";// 对象集合或者对象都可以List<DataPO>…...

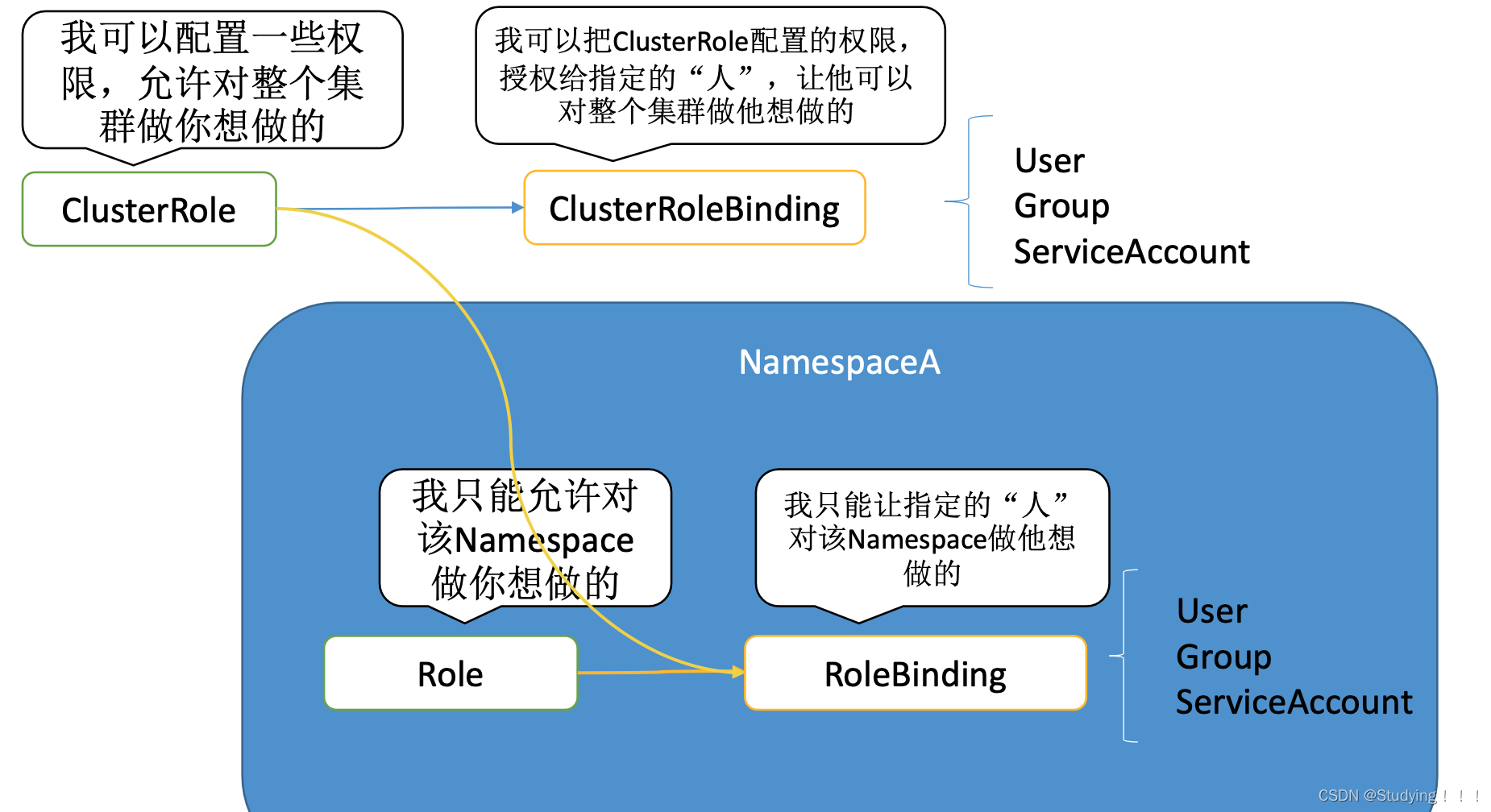

k8s-----26、细粒度权限管理 RBAC

0、导读 每一个用户对API资源进行操作都需要通经过以下三个步骤: 第一步:对客户端访问进行认证操作,确认是否具有访问k8s权限(也就是通过serviceaccount) token(共享秘钥) SSL(双向SSL认证) …通过任何一个认证即表示认证通过,进入下一步第二步:授权检查,确认是否对资源…...

【Unity ShaderGraph】| 制作一个 高级流体水球效果

前言 【Unity ShaderGraph】| 快速制作一个 流体水球效果一、效果展示二、简易流体水球效果三、进阶流体水球效果四、应用实例 前言 本文将使用ShaderGraph制作一个 高级流体水球 ,可以直接拿到项目中使用。对ShaderGraph还不了解的小伙伴可以参考这篇文章…...

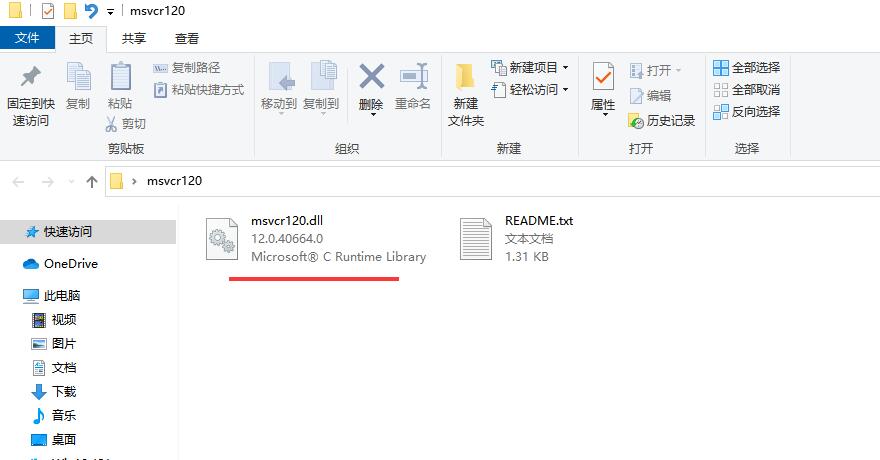

日常软件游戏丢失msvcp120dll怎么修复?分享5个修复方法

在计算机使用过程中,我们经常会遇到一些错误提示,其中之一就是“msvcp120dll丢失”。那么,究竟什么是msvcp120dll文件?当它丢失时,我们会遇到哪些问题呢?本文将从以下几个方面进行详细阐述。 msvcp120dll是…...

spring-ai 第一步集成入门

spring-ai 第一步入门 官网spring ai 做什么?涉及相关概念检索增加RAG工具调用 spring-ai 第一步入门 官网 spring-ai网址【https://spring.io/projects/spring-ai】 Spring AI 目前支持将输入和输出处理为语言、图像和音频的模型 spring ai 做什么?…...

全文交给降AI工具处理,文本质量会变差吗?实测说话

全文交给降AI工具处理,文本质量会变差吗?实测说话 “全文交给工具处理,会不会被改得乱七八糟?” 这是很多同学在考虑用降AI工具时最大的顾虑,也是一个合理的问题。 我实测了几个工具处理前后的文本质量对比…...

电力设施智能检测:TTPLA数据集赋能电网巡检自动化全流程指南

电力设施智能检测:TTPLA数据集赋能电网巡检自动化全流程指南 【免费下载链接】ttpla_dataset aerial images dataset on transmission towers and power lines 项目地址: https://gitcode.com/gh_mirrors/tt/ttpla_dataset 在电力行业数字化转型进程中&…...

如何快速搭建Galgame社区平台:一站式开源解决方案指南

如何快速搭建Galgame社区平台:一站式开源解决方案指南 【免费下载链接】kun-touchgal-next TouchGAL是立足于分享快乐的一站式Galgame文化社区, 为Gal爱好者提供一片净土! 项目地址: https://gitcode.com/gh_mirrors/ku/kun-touchgal-next 你是否曾为寻找Gal…...

NormalMap-Online:本地GPU加速的3D材质增强解决方案

NormalMap-Online:本地GPU加速的3D材质增强解决方案 【免费下载链接】NormalMap-Online NormalMap Generator Online 项目地址: https://gitcode.com/gh_mirrors/no/NormalMap-Online 在3D建模领域,表面细节的呈现往往决定了模型的真实感与品质。…...

seo外包需要提供哪些资料

SEO外包需要提供哪些资料? 在当今数字化时代,SEO(搜索引擎优化)已经成为了企业提升在线可见度和吸引潜在客户的重要手段。当然,很多企业选择通过外包的方式来实现高效的SEO,但要让外包团队真正为你的网站带…...

RVC模型训练全攻略:如何用3分钟打造专属语音模型

RVC模型训练全攻略:如何用3分钟打造专属语音模型 1. 引言:为什么选择RVC? 在当今数字内容创作蓬勃发展的时代,拥有一个独特的语音模型已经成为许多创作者和企业的刚需。RVC(Retrieval-Based Voice Conversion&#x…...

Matplotlib横坐标刻度从原点开始的3种实用方法

1. 为什么横坐标刻度从原点开始很重要 做数据可视化时,我们经常需要展示数据从零开始的变化趋势。比如展示销售额增长、用户数量变化或者实验数据对比时,如果横坐标不从零开始,很容易造成视觉上的误导。我见过不少新手做的图表,因…...

安卓集成Google TTS引擎:实现离线中文语音播报的完整实践

1. 为什么需要Google TTS引擎 很多安卓开发者都遇到过这样的需求:在应用中实现文字转语音功能。系统自带的Pico TTS引擎虽然轻量,但最大的痛点就是不支持中文。我去年开发一个盲人辅助应用时就踩过这个坑,测试时发现语音输出全是英文…...

openclaw行为式AI重构:从昂贵Token到高效对象协作

从昂贵的token消耗到高效的对象协作,重新设计行为式AI的核心架构 问题诊断:为什么当前行为式AI如此“昂贵”? OpenClaw等工具的核心架构依赖生成式大模型作为“大脑”,通过反复的推理-行动循环完成任务。这种设计导致: 高Token消耗的根源 重复的上下文传递:每次循环都需…...