xilinx fpga ddr mig axi

硬件

参考:

https://zhuanlan.zhihu.com/p/97491454

https://blog.csdn.net/qq_22222449/article/details/106492469

https://zhuanlan.zhihu.com/p/26327347

https://zhuanlan.zhihu.com/p/582524766

包括野火、正点原子的资料

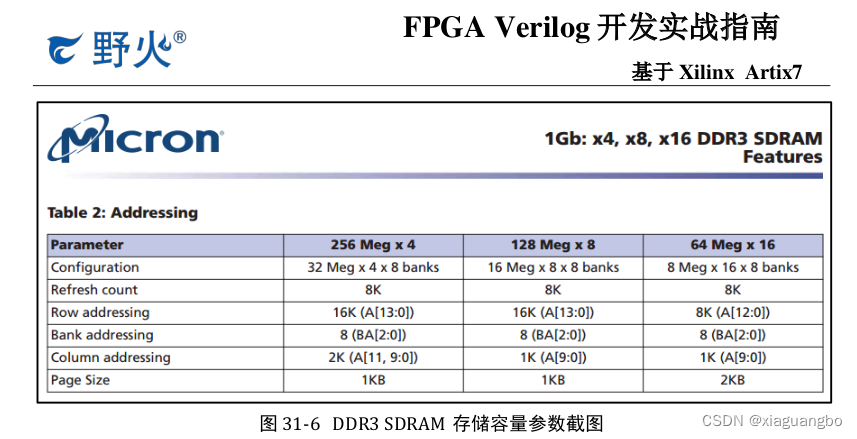

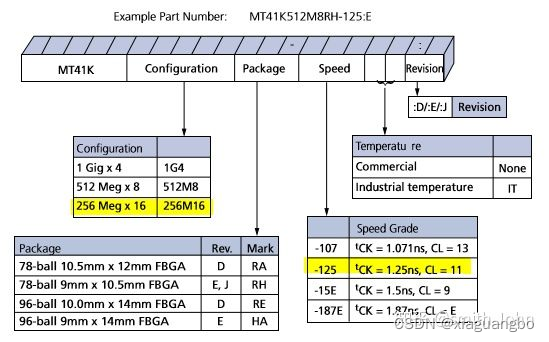

一片内存是 1Gbit 128MByte 16bit DDR3,也就是下图里的 64Meg x 16,mig 里要选 …64M16…,这个关系到地址线的个数,下图中同容量不同位宽的内存芯片的 ‘… addressing’ 部分是有不同的,有的少有的多。在硬件上只要连 A0-A12 就行了,除非是要兼容更大的内存

行地址(row addr)总线为 A0-A12,行地址位宽为 13 位 , 行地址数为 8192(213)(8K) 行,列地址(column addr)为 A0-A9,位宽为 10 位 , 列地址数为1024(210)(1K)列,单个 Bank 中包含的存储单元个数为行地址数(8192)与列地址数(1024)相乘,8K×1K=8M(8Meg);“16”表示数据位宽,即每个存储单元存储数据的 bit 数;8Meg 与 16 相乘表示单个 Bank 中可存储的 Bit 数;“8 banks”表示一片 SDRAM 中包含的 Bank 个数,此 DDR3 SDRAM 芯片包含 8 个 Bank;由此可得 DDR3 SDRAM 芯片的存储容量为:1024MBit (8Meg×16×8 banks)

如果是 256MByte 16bit 位宽的内存,banks 同样为 8 的话,那就是 16Meg(地址数) x 16bit x 8 banks,Row addr 就有 14 位,那么 mig 里就选 …128M16…

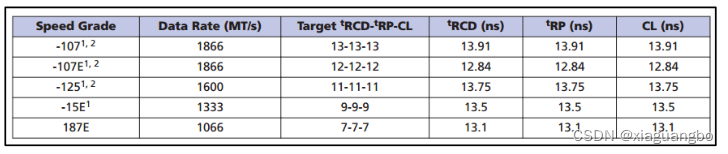

假设 mig ip 里的 Memory Part 选择 MT41J128M16XX-125,结尾数字里的意思:

假设 mig ip 里的 Memory Part 选择 MT41J128M16XX-125,结尾数字里的意思:

Data Rate 是传输频率,电脑上的 DDR3 1866 就是这个意思

-125 所支持的最小时钟周期 tCK = 1.25ns,对应芯片支持的最大 IO 时钟频率为 800MHz,数据传输频率就是 1600MHz。传输频率 x 位宽 = 传输速率,MT41J128M16XX-125 的位宽是 16bit,最大传输速率就是 1600MHz x 16bit(2Byte) = 3200MB = 3.125GiB

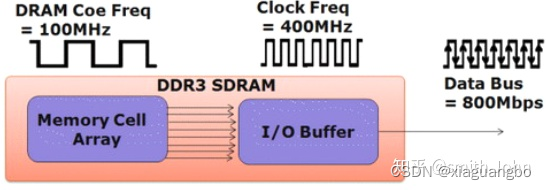

下图是各频率之间的关系,100MHz 核心频率 = 400MHz IO 频率 = 800MHz 传输频率。mig ip 传输 400MHz IO 频率给 ddr3,ddr3 内部获得 100MHz 的核心频率

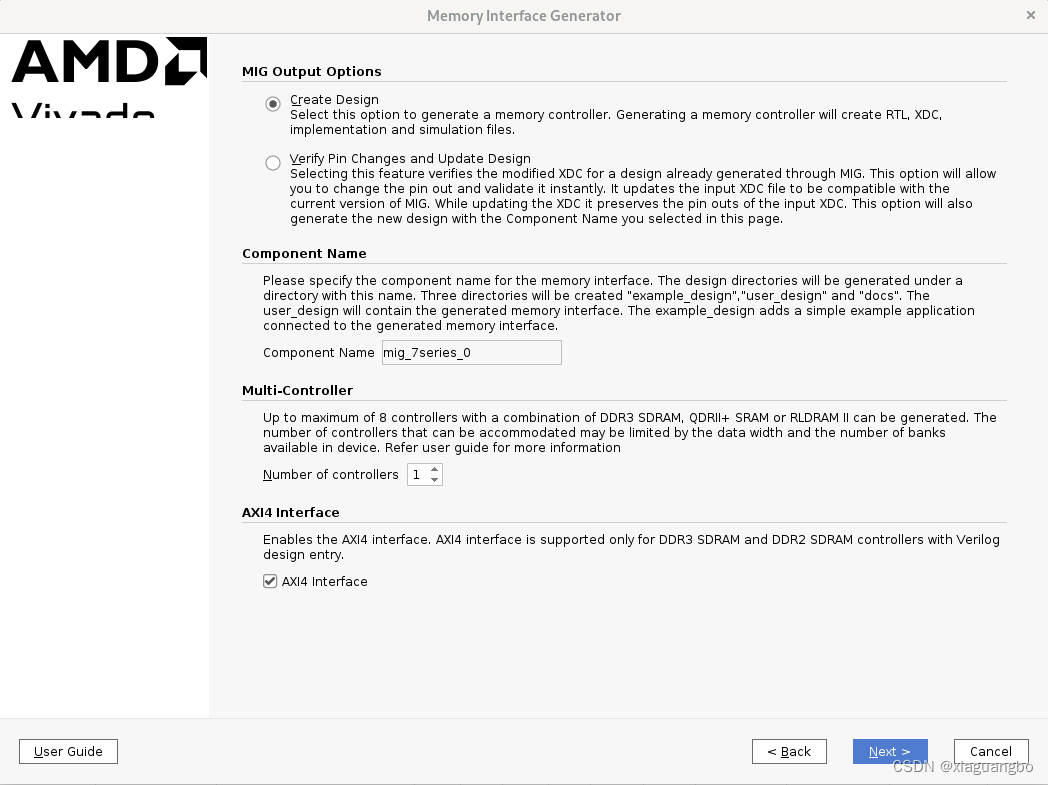

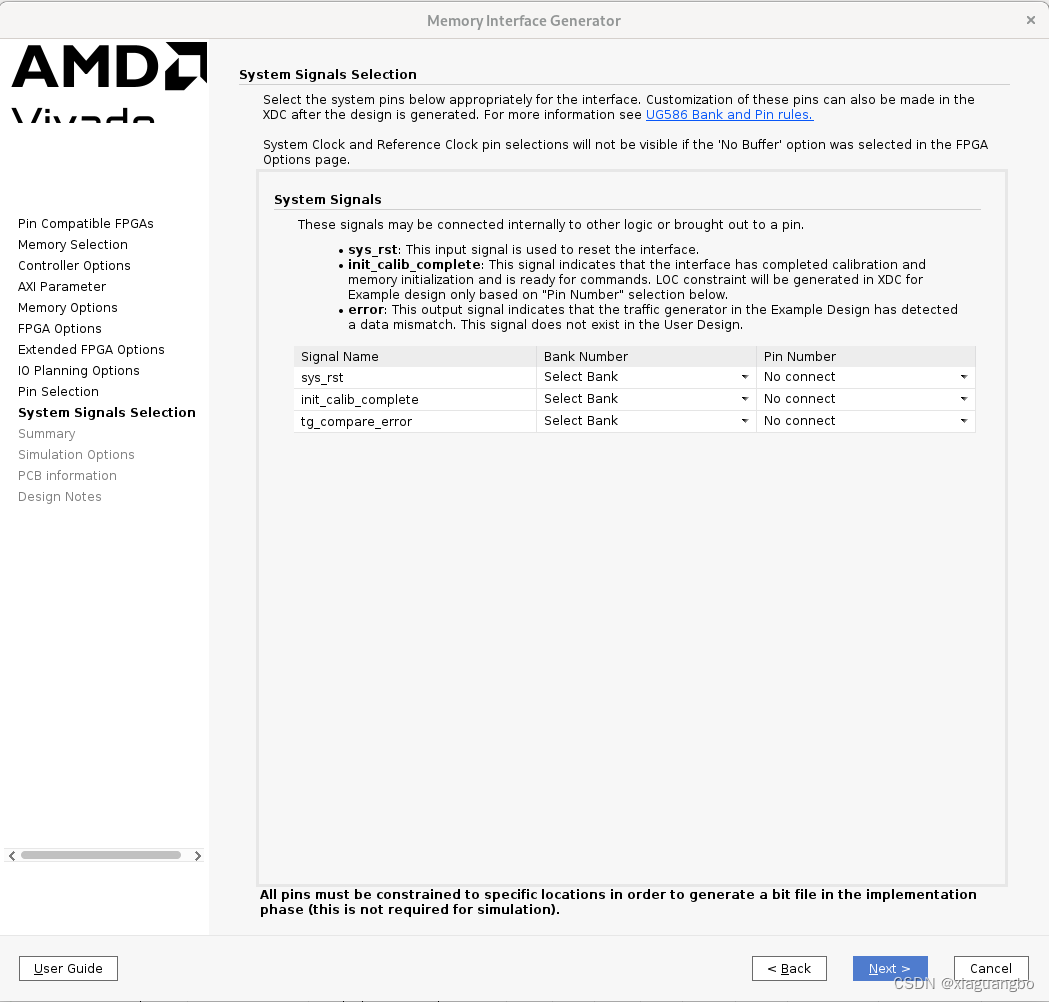

MIG ip 配置

下图:

勾选了 AXI

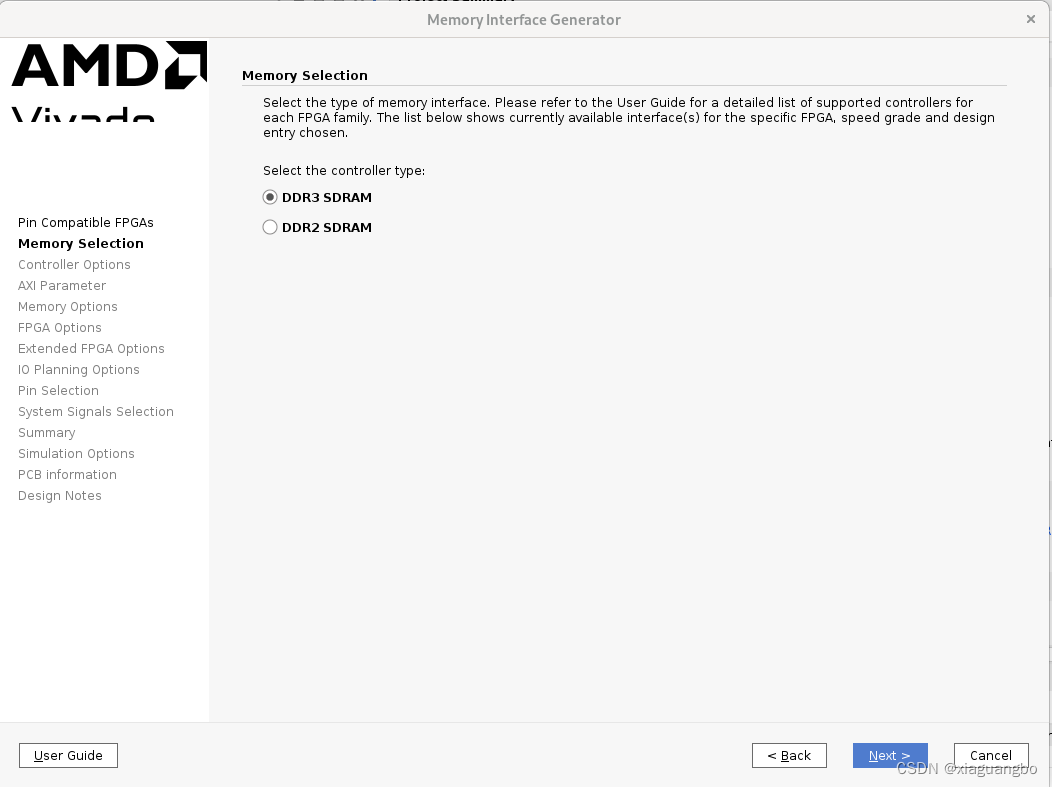

下图:

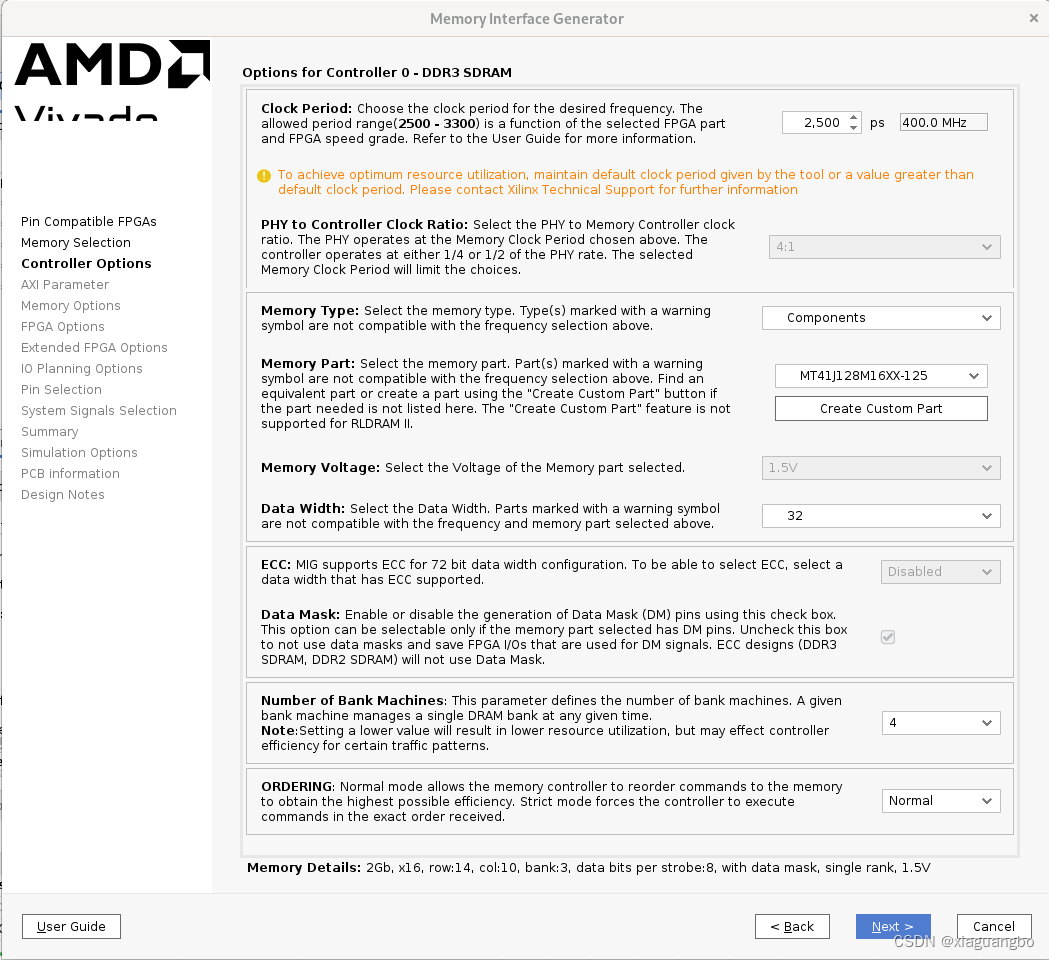

Clock Period:400MHz,是给 DDR3 的 IO 时钟,一片内存的传输速率就是 800MHz * 16bit(2Byte) = 1600MB = 1.5625GiByte,两片就是 3200MB = 3.125GiByte

PHY to Controller Clock Ratio:mig ip 反给用户的时钟,因为之前勾选了 axi,也就是 axi 给用户用的时钟,Clock Period 除以 4,所以 axi 的时钟是 100MHz

Data Width:两片内存就是 32bit

Number of Bank Machines: 不是 banks 数,是一种 bank 控制策略,保持默认

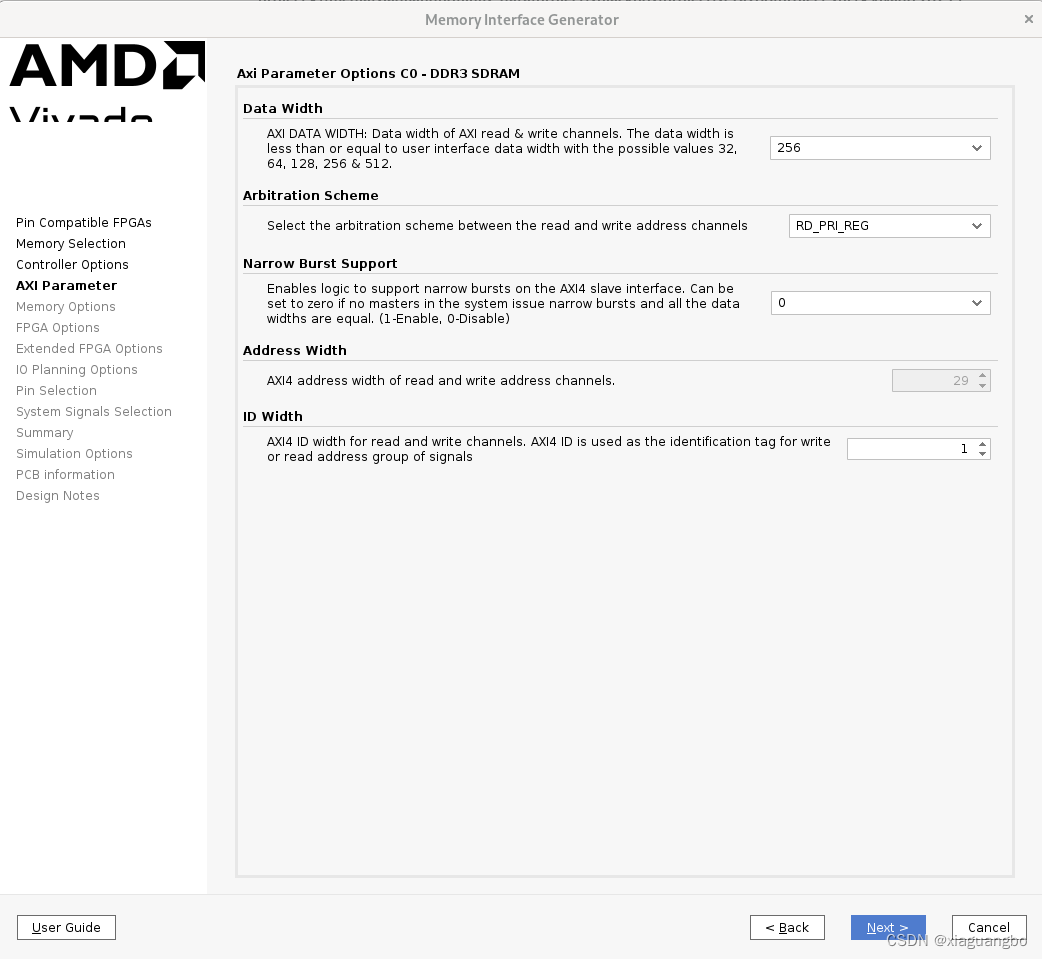

下图:

下图:

Data Width:AXI 的位宽,AXI 时钟(100MHz) x AXI 的位宽(32Byte) = 3200MByte,这样才可能跑满两片 ddr3 的速率

下图:

Input Clock Period:用户给 mig ip 的时钟,用 mmcm 传给 mig

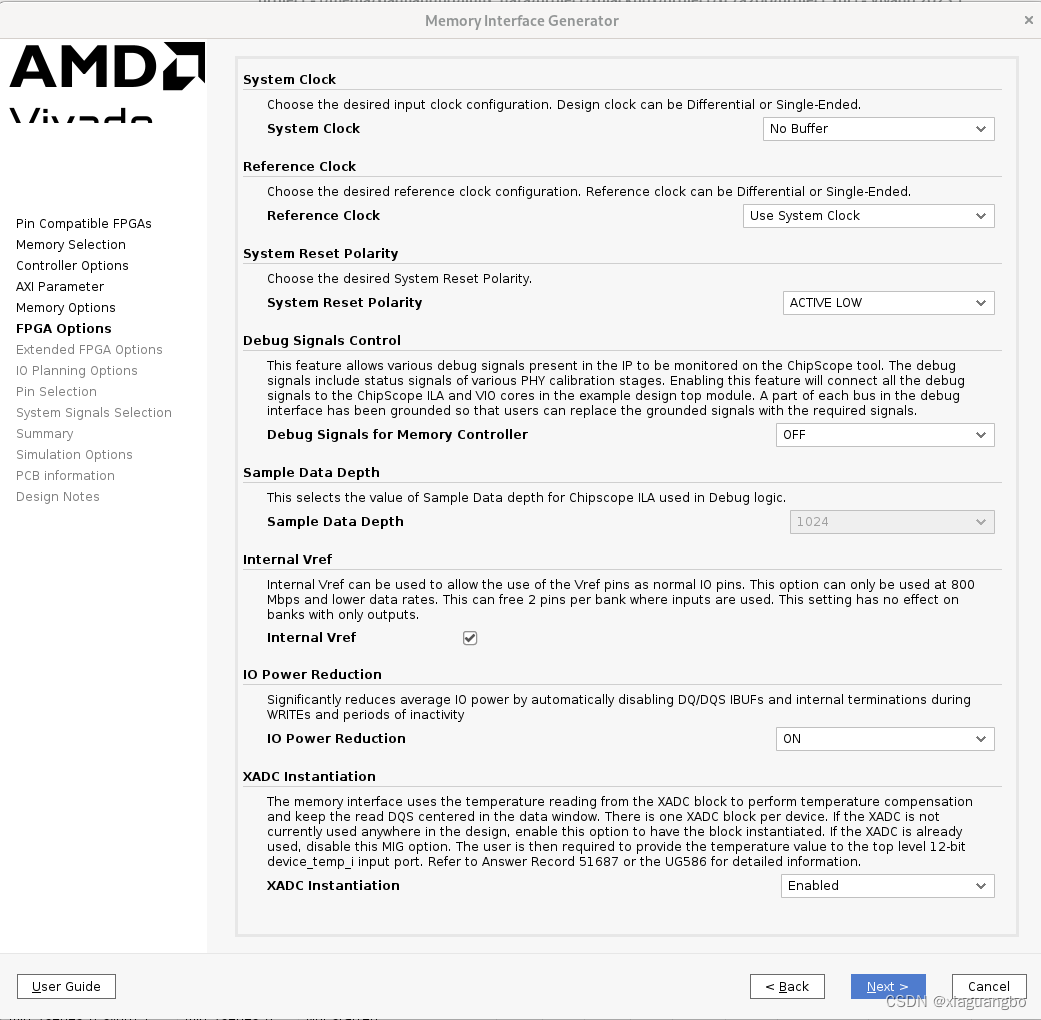

下图:

Reference Clock:前一步 mig ip 的时钟输入选 200MHz 这里才能选 Use System Clock,这样 ip 实例化的时候就可以少一个 ref_clk 的接口

Internal Vref:

使用内部 Vref。Vref 是 FPGA 的 IO Bank 参考电压引脚,一般要外接参考电压,但是这里若传输速率小于等于 800MHz 就可以不用外接,转而使用内部 Vref,然后该 Vref 引脚就可以空出来给用户使用,这里 mig 需要两个 IO Bank,就能空出 4 个 Vref 引脚(不同的 Bank 的 Vref 引脚数不一样),然后就可以把这两个 Vref 连到 ddr 的地址线上。如果 ddr 的 IO 已经连了 Vref 就必选了,不然 IO Bank 没参考电压

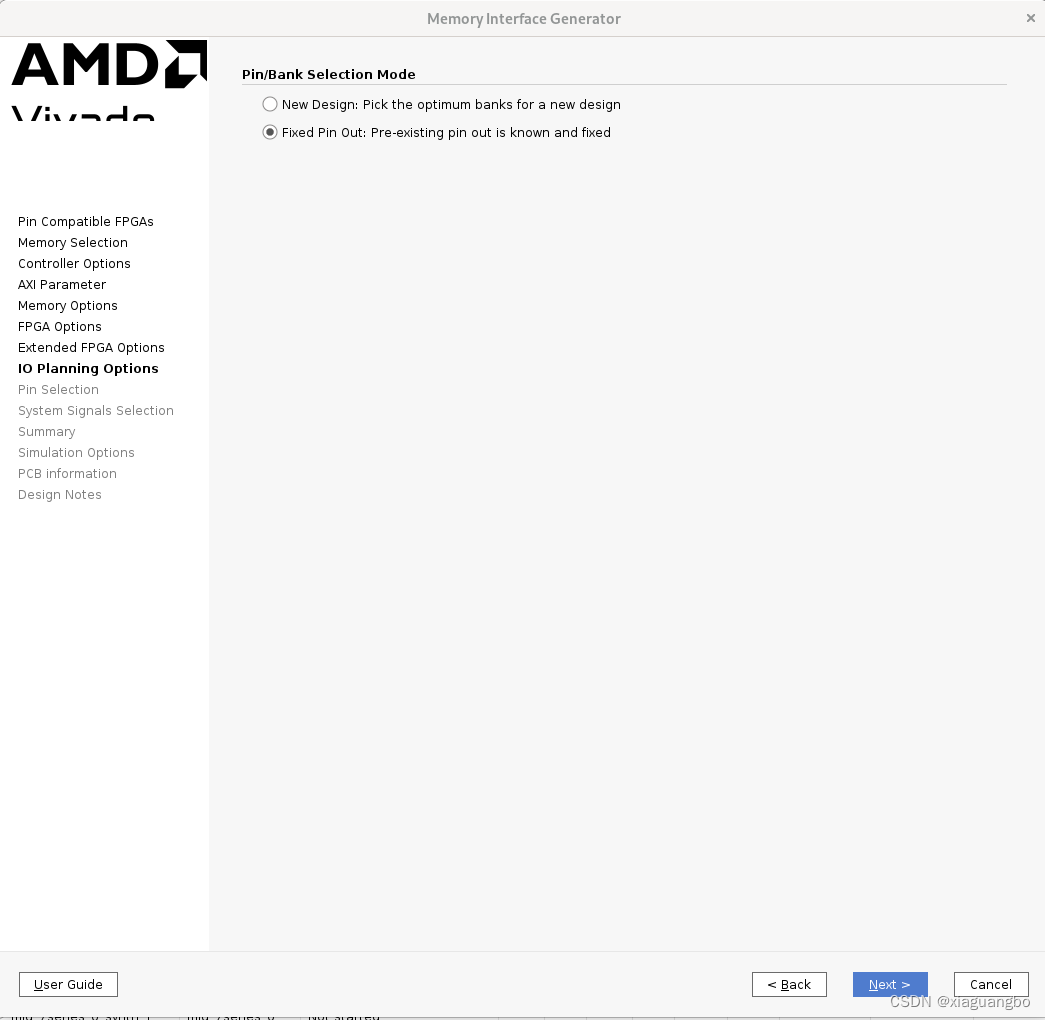

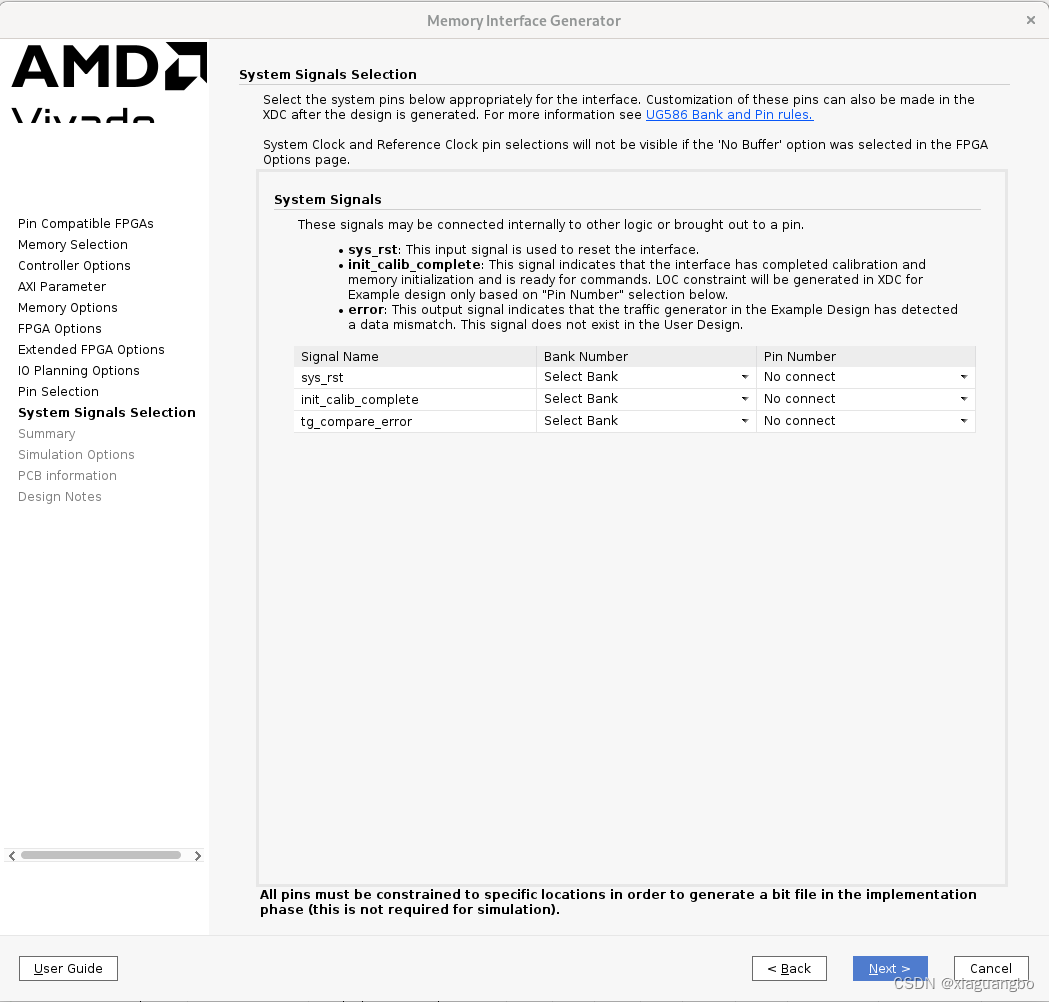

下图:

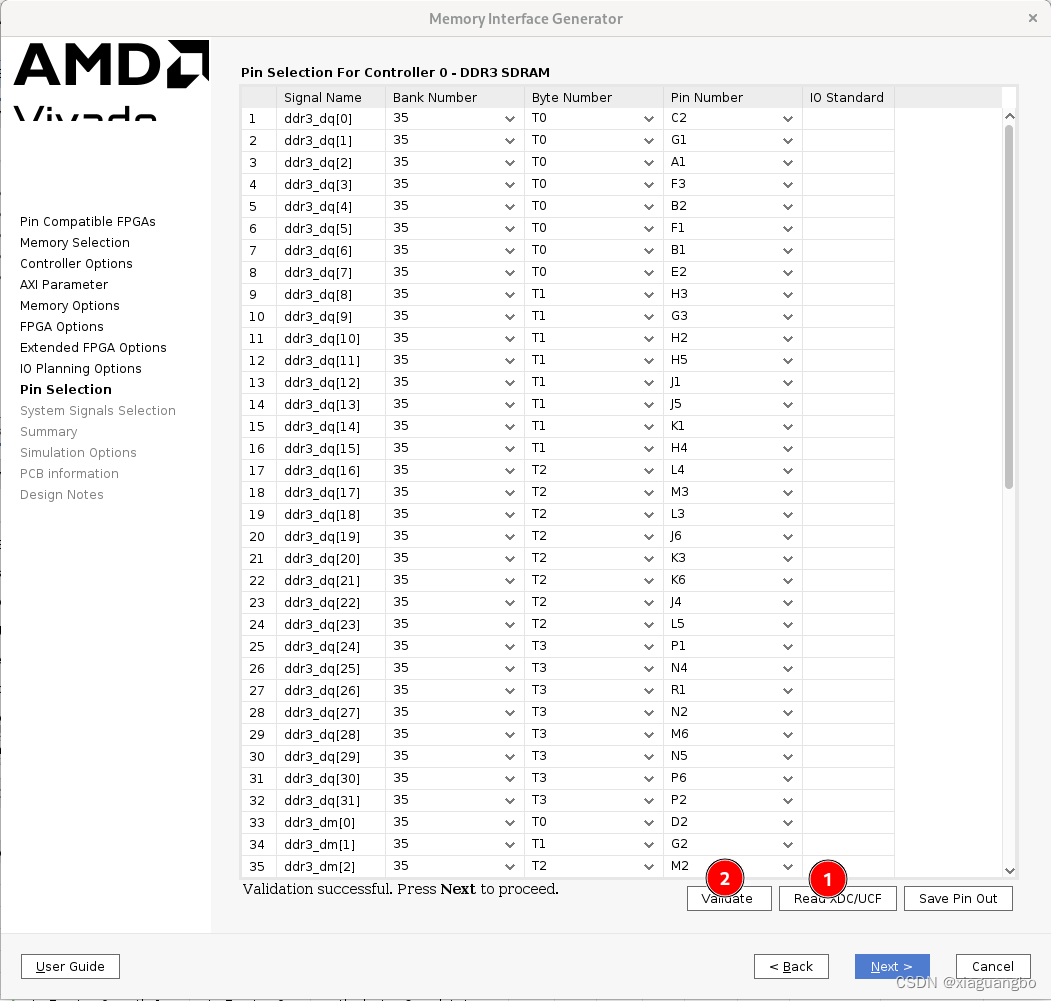

先读取 .ucf,再校验

ddr3.ucf:

# clock, reset

NET "ddr3_ck_p[0]" LOC = "R3";

NET "ddr3_ck_n[0]" LOC = "R2";

NET "ddr3_reset_n" LOC = "W6";# global control

NET "ddr3_cs_n[0]" LOC = "AB3";

NET "ddr3_cke[0]" LOC = "T5";

NET "ddr3_odt[0]" LOC = "U5";

NET "ddr3_we_n" LOC = "AA1";# address control

NET "ddr3_ba[0]" LOC = "AA3";

NET "ddr3_ba[1]" LOC = "Y3";

NET "ddr3_ba[2]" LOC = "Y4";

NET "ddr3_ras_n" LOC = "V4";

NET "ddr3_cas_n" LOC = "W4";# address

NET "ddr3_addr[0]" LOC = "AA4";

NET "ddr3_addr[1]" LOC = "AB2";

NET "ddr3_addr[2]" LOC = "AA5";

NET "ddr3_addr[3]" LOC = "AB5";

NET "ddr3_addr[4]" LOC = "AB1";

NET "ddr3_addr[5]" LOC = "U3";

NET "ddr3_addr[6]" LOC = "W1";

NET "ddr3_addr[7]" LOC = "T1";

NET "ddr3_addr[8]" LOC = "V2";

NET "ddr3_addr[9]" LOC = "U2";

NET "ddr3_addr[10]" LOC = "Y1";

NET "ddr3_addr[11]" LOC = "W2";

NET "ddr3_addr[12]" LOC = "Y2";

NET "ddr3_addr[13]" LOC = "U1";# data control

NET "ddr3_dqs_p[0]" LOC = "E1";

NET "ddr3_dqs_p[1]" LOC = "K2";

NET "ddr3_dqs_p[2]" LOC = "M1";

NET "ddr3_dqs_p[3]" LOC = "P5";

NET "ddr3_dqs_n[0]" LOC = "D1";

NET "ddr3_dqs_n[1]" LOC = "J2";

NET "ddr3_dqs_n[2]" LOC = "L1";

NET "ddr3_dqs_n[3]" LOC = "P4";NET "ddr3_dm[0]" LOC = "D2";

NET "ddr3_dm[1]" LOC = "G2";

NET "ddr3_dm[2]" LOC = "M2";

NET "ddr3_dm[3]" LOC = "M5";# data

NET "ddr3_dq[0]" LOC = "C2";

NET "ddr3_dq[1]" LOC = "G1";

NET "ddr3_dq[2]" LOC = "A1";

NET "ddr3_dq[3]" LOC = "F3";

NET "ddr3_dq[4]" LOC = "B2";

NET "ddr3_dq[5]" LOC = "F1";

NET "ddr3_dq[6]" LOC = "B1";

NET "ddr3_dq[7]" LOC = "E2";

NET "ddr3_dq[8]" LOC = "H3";

NET "ddr3_dq[9]" LOC = "G3";

NET "ddr3_dq[10]" LOC = "H2";

NET "ddr3_dq[11]" LOC = "H5";

NET "ddr3_dq[12]" LOC = "J1";

NET "ddr3_dq[13]" LOC = "J5";

NET "ddr3_dq[14]" LOC = "K1";

NET "ddr3_dq[15]" LOC = "H4";

NET "ddr3_dq[16]" LOC = "L4";

NET "ddr3_dq[17]" LOC = "M3";

NET "ddr3_dq[18]" LOC = "L3";

NET "ddr3_dq[19]" LOC = "J6";

NET "ddr3_dq[20]" LOC = "K3";

NET "ddr3_dq[21]" LOC = "K6";

NET "ddr3_dq[22]" LOC = "J4";

NET "ddr3_dq[23]" LOC = "L5";

NET "ddr3_dq[24]" LOC = "P1";

NET "ddr3_dq[25]" LOC = "N4";

NET "ddr3_dq[26]" LOC = "R1";

NET "ddr3_dq[27]" LOC = "N2";

NET "ddr3_dq[28]" LOC = "M6";

NET "ddr3_dq[29]" LOC = "N5";

NET "ddr3_dq[30]" LOC = "P6";

NET "ddr3_dq[31]" LOC = "P2";

代码

mig.v:

module mig (input clk,input rst_n,// ddr3output [13 : 0] ddr3_addr, // output [13 : 0] ddr3_addroutput [ 2 : 0] ddr3_ba, // output [ 2 : 0] ddr3_baoutput ddr3_cas_n, // output ddr3_cas_noutput ddr3_ck_n, // output ddr3_ck_noutput ddr3_ck_p, // output ddr3_ck_poutput ddr3_cke, // output ddr3_ckeoutput ddr3_ras_n, // output ddr3_ras_noutput ddr3_reset_n, // output ddr3_reset_n output ddr3_we_n, // output ddr3_we_ninout [31 : 0] ddr3_dq, // inout [31 : 0] ddr3_dqinout [ 3 : 0] ddr3_dqs_n, // inout [ 3 : 0] ddr3_dqs_ninout [ 3 : 0] ddr3_dqs_p, // inout [ 3 : 0] ddr3_dqs_poutput [ 0 : 0] ddr3_cs_n, // output [ 0 : 0] ddr3_cs_noutput [ 3 : 0] ddr3_dm, // output [ 3 : 0] ddr3_dmoutput [ 0 : 0] ddr3_odt, // output [ 0 : 0] ddr3_odt// user// axioutput ui_clk, // output ui_clkoutput ui_clk_sync_rst, // output ui_clk_sync_rst// read addressinput [28 : 0] s_axi_araddr, // input [28 : 0] s_axi_araddrinput [ 7 : 0] s_axi_arlen, // input [ 7 : 0] s_axi_arleninput s_axi_arvalid, // input s_axi_arvalidoutput s_axi_arready, // output s_axi_arready// read dataoutput [255 : 0] s_axi_rdata, // output [255 : 0] s_axi_rdataoutput s_axi_rlast, // output s_axi_rlastinput s_axi_rready, // input s_axi_rreadyoutput s_axi_rvalid, // output s_axi_rvalid// write addressinput [28 : 0] s_axi_awaddr, // input [28 : 0] s_axi_awaddrinput [ 7 : 0] s_axi_awlen, // input [ 7 : 0] s_axi_awleninput s_axi_awvalid, // input s_axi_awvalidoutput s_axi_awready, // output s_axi_awready// wirte datainput [255 : 0] s_axi_wdata, // input [255 : 0] s_axi_wdatainput [ 31 : 0] s_axi_wstrb, // input [ 31 : 0] s_axi_wstrbinput s_axi_wlast, // input s_axi_wlastinput s_axi_wvalid, // input s_axi_wvalidoutput s_axi_wready, // output s_axi_wready// write responseoutput s_axi_bvalid, // output s_axi_bvalidinput s_axi_bready // input s_axi_bready

);mig_7series_0 mig_7series_0_i (.sys_clk_i(clk),.sys_rst (rst_n),// ddr3.ddr3_addr (ddr3_addr), // output [13 : 0] ddr3_addr.ddr3_ba (ddr3_ba), // output [ 2 : 0] ddr3_ba.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n.ddr3_ck_n (ddr3_ck_n), // output ddr3_ck_n.ddr3_ck_p (ddr3_ck_p), // output ddr3_ck_p.ddr3_cke (ddr3_cke), // output ddr3_cke.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n.ddr3_reset_n (ddr3_reset_n), // output ddr3_reset_n.ddr3_we_n (ddr3_we_n), // output ddr3_we_n.ddr3_dq (ddr3_dq), // inout [31 : 0] ddr3_dq.ddr3_dqs_n (ddr3_dqs_n), // inout [ 3 : 0] ddr3_dqs_n.ddr3_dqs_p (ddr3_dqs_p), // inout [ 3 : 0] ddr3_dqs_p.init_calib_complete(), // output init_calib_complete.ddr3_cs_n (ddr3_cs_n), // output [ 0 : 0] ddr3_cs_n.ddr3_dm (ddr3_dm), // output [ 3 : 0] ddr3_dm.ddr3_odt (ddr3_odt), // output [ 0 : 0] ddr3_odt// user// axi.ui_clk (ui_clk), // output ui_clk.ui_clk_sync_rst(ui_clk_sync_rst), // output ui_clk_sync_rst.mmcm_locked (), // output mmcm_locked.aresetn (rst_n), // input aresetn.app_sr_req (0), // input app_sr_req.app_ref_req (0), // input app_ref_req.app_zq_req (0), // input app_zq_req.app_sr_active (), // output app_sr_active.app_ref_ack (), // output app_ref_ack.app_zq_ack (), // output app_zq_ack// read address.s_axi_arid (0), // input [ 0 : 0] s_axi_arid.s_axi_araddr (s_axi_araddr), // input [28 : 0] s_axi_araddr.s_axi_arlen (s_axi_arlen), // input [ 7 : 0] s_axi_arlen.s_axi_arsize (5), // input [ 2 : 0] s_axi_arsize.s_axi_arburst(1), // input [ 1 : 0] s_axi_arburst.s_axi_arlock (0), // input [ 0 : 0] s_axi_arlock.s_axi_arcache(0), // input [ 3 : 0] s_axi_arcache.s_axi_arprot (0), // input [ 2 : 0] s_axi_arprot.s_axi_arqos (0), // input [ 3 : 0] s_axi_arqos.s_axi_arvalid(s_axi_arvalid), // input s_axi_arvalid.s_axi_arready(s_axi_arready), // output s_axi_arready// read data.s_axi_rid (), // output [ 0 : 0] s_axi_rid.s_axi_rdata (s_axi_rdata), // output [255 : 0] s_axi_rdata.s_axi_rresp (), // output [ 1 : 0] s_axi_rresp.s_axi_rlast (s_axi_rlast), // output s_axi_rlast.s_axi_rvalid(s_axi_rvalid), // output s_axi_rvalid.s_axi_rready(s_axi_rready), // input s_axi_rready// write address.s_axi_awid (0), // input [ 0 : 0] s_axi_awid.s_axi_awaddr (s_axi_awaddr), // input [28 : 0] s_axi_awaddr.s_axi_awlen (s_axi_awlen), // input [ 7 : 0] s_axi_awlen.s_axi_awsize (5), // input [ 2 : 0] s_axi_awsize.s_axi_awburst(1), // input [ 1 : 0] s_axi_awburst.s_axi_awlock (0), // input [ 0 : 0] s_axi_awlock.s_axi_awcache(0), // input [ 3 : 0] s_axi_awcache.s_axi_awprot (0), // input [ 2 : 0] s_axi_awprot.s_axi_awqos (0), // input [ 3 : 0] s_axi_awqos.s_axi_awvalid(s_axi_awvalid), // input s_axi_awvalid.s_axi_awready(s_axi_awready), // output s_axi_awready// wirte data.s_axi_wdata (s_axi_wdata), // input [255 : 0] s_axi_wdata.s_axi_wstrb (s_axi_wstrb), // input [ 31 : 0] s_axi_wstrb.s_axi_wlast (s_axi_wlast), // input s_axi_wlast.s_axi_wvalid(s_axi_wvalid), // input s_axi_wvalid.s_axi_wready(s_axi_wready), // output s_axi_wready// write response.s_axi_bid (), // output [0 : 0] s_axi_bid.s_axi_bresp (), // output [1 : 0] s_axi_bresp.s_axi_bvalid(s_axi_bvalid), // output s_axi_bvalid.s_axi_bready(s_axi_bready) // input s_axi_bready

);endmodule

work:

module work (input clk,input rst_n,// ddr3output [13 : 0] ddr3_addr,output [ 2 : 0] ddr3_ba,output ddr3_cas_n,output ddr3_ck_n,output ddr3_ck_p,output ddr3_cke,output ddr3_ras_n,output ddr3_reset_n,output ddr3_we_n,inout [31 : 0] ddr3_dq,inout [ 3 : 0] ddr3_dqs_n,inout [ 3 : 0] ddr3_dqs_p,output [ 0 : 0] ddr3_cs_n,output [ 3 : 0] ddr3_dm,output [ 0 : 0] ddr3_odt

);// mig

wire mig_clk;wire mig_ui_clk;

wire mig_ui_clk_sync_rst;reg [28 : 0] mig_s_axi_araddr;

reg [ 7 : 0] mig_s_axi_arlen;

reg mig_s_axi_arvalid;

wire mig_s_axi_arready;wire [255 : 0] mig_s_axi_rdata;

wire mig_s_axi_rlast;

wire mig_s_axi_rvalid;reg [28 : 0] mig_s_axi_awaddr;

reg [ 7 : 0] mig_s_axi_awlen;

reg mig_s_axi_awvalid;

wire mig_s_axi_awready;reg [255 : 0] mig_s_axi_wdata;

reg [ 31 : 0] mig_s_axi_wstrb;

reg mig_s_axi_wlast;

reg mig_s_axi_wvalid;

wire mig_s_axi_wready;wire mig_s_axi_bvalid;mig mig_i (.clk (mig_clk),.rst_n(rst_n),// ddr3.ddr3_addr (ddr3_addr), // output [13 : 0] ddr3_addr.ddr3_ba (ddr3_ba), // output [ 2 : 0] ddr3_ba.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n.ddr3_ck_n (ddr3_ck_n), // output ddr3_ck_n.ddr3_ck_p (ddr3_ck_p), // output ddr3_ck_p.ddr3_cke (ddr3_cke), // output ddr3_cke.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n.ddr3_reset_n (ddr3_reset_n), // output ddr3_reset_n.ddr3_we_n (ddr3_we_n), // output ddr3_we_n.ddr3_dq (ddr3_dq), // inout [31 : 0] ddr3_dq.ddr3_dqs_n (ddr3_dqs_n), // inout [ 3 : 0] ddr3_dqs_n.ddr3_dqs_p (ddr3_dqs_p), // inout [ 3 : 0] ddr3_dqs_p.ddr3_cs_n (ddr3_cs_n), // output [ 0 : 0] ddr3_cs_n.ddr3_dm (ddr3_dm), // output [ 3 : 0] ddr3_dm.ddr3_odt (ddr3_odt), // output [ 0 : 0] ddr3_odt// user// axi.ui_clk (mig_ui_clk), // output ui_clk.ui_clk_sync_rst(mig_ui_clk_sync_rst), // output ui_clk_sync_rst// read address.s_axi_araddr (mig_s_axi_araddr), // input [28 : 0] s_axi_araddr.s_axi_arlen (mig_s_axi_arlen), // input [ 7 : 0] s_axi_arlen.s_axi_arvalid(mig_s_axi_arvalid), // input s_axi_arvalid.s_axi_arready(mig_s_axi_arready), // output s_axi_arready// read data.s_axi_rdata (mig_s_axi_rdata), // output [255 : 0] s_axi_rdata.s_axi_rlast (mig_s_axi_rlast), // output s_axi_rlast.s_axi_rvalid(mig_s_axi_rvalid), // output s_axi_rvalid.s_axi_rready(mig_s_axi_rvalid), // input s_axi_rready// write address.s_axi_awaddr (mig_s_axi_awaddr), // input [28 : 0] s_axi_awaddr.s_axi_awlen (mig_s_axi_awlen), // input [ 7 : 0] s_axi_awlen.s_axi_awvalid(mig_s_axi_awvalid), // input s_axi_awvalid.s_axi_awready(mig_s_axi_awready), // output s_axi_awready// wirte data.s_axi_wdata (mig_s_axi_wdata), // input [255 : 0] s_axi_wdata.s_axi_wstrb (mig_s_axi_wstrb), // input [ 31 : 0] s_axi_wstrb.s_axi_wlast (mig_s_axi_wlast), // input s_axi_wlast.s_axi_wvalid(mig_s_axi_wvalid), // input s_axi_wvalid.s_axi_wready(mig_s_axi_wready), // output s_axi_wready// write response.s_axi_bvalid(mig_s_axi_bvalid), // output s_axi_bvalid.s_axi_bready(mig_s_axi_bvalid) // input s_axi_bready

);// mig 读写测试

reg [255 : 0] wdata;reg [3 : 0] step;always @(posedge mig_ui_clk) begin if(mig_ui_clk_sync_rst) beginmig_s_axi_araddr <= 0;mig_s_axi_arlen <= 0;mig_s_axi_arvalid <= 0;mig_s_axi_awaddr <= 0;mig_s_axi_awlen <= 0;mig_s_axi_awvalid <= 0;mig_s_axi_wdata <= 0;mig_s_axi_wstrb <= 0;mig_s_axi_wlast <= 0;mig_s_axi_wvalid <= 0;wdata <= 0;step <= 0;endelse begincase (step)0: begin// 准备写地址mig_s_axi_awaddr <= 0;mig_s_axi_awlen <= 1 - 1;mig_s_axi_awvalid <= 1; // 写地址有效wdata <= wdata + 1;step <= step + 1;end1: begin// 待地址写入成功if (mig_s_axi_awready) beginmig_s_axi_awvalid <= 0; // 写地址无效// 准备写数据mig_s_axi_wdata <= wdata;mig_s_axi_wstrb <= {256{1'b1}};mig_s_axi_wlast <= 1;mig_s_axi_wvalid <= 1; // 写数据有效step <= step + 1;endend2: begin// 待数据写入成功// 只写了一次可以直接判断if (mig_s_axi_wready) beginmig_s_axi_wlast <= 0;mig_s_axi_wvalid <= 0; // 写数据无效step <= step + 1;endend3: begin// 待写响应有效if (mig_s_axi_bvalid) beginstep <= step + 1;endend// 至此,写入成功4: begin// 准备读地址mig_s_axi_araddr <= 0;mig_s_axi_arlen <= 1 - 1;mig_s_axi_arvalid <= 1; // 读地址有效step <= step + 1;end5: begin// 待地址写入成功if (mig_s_axi_arready) beginmig_s_axi_arvalid <= 0; // 读地址无效step <= step + 1;endend6: begin// 待数据接收if (mig_s_axi_rvalid) beginstep <= 0;endendendcaseend

endclk_wiz_0 clk_wiz_0_i (.clk_in1(clk), // input clk_in1.resetn (rst_n), // input reset// user.clk_out1(mig_clk), // output clk_out1 200M

);ila_0 ila_0_i (.clk(mig_ui_clk), // input wire clk.probe0(step), // input wire [3:0] probe0 .probe1(mig_s_axi_rdata) // input wire [255:0] probe1

);endmodule

相关文章:

xilinx fpga ddr mig axi

硬件 参考: https://zhuanlan.zhihu.com/p/97491454 https://blog.csdn.net/qq_22222449/article/details/106492469 https://zhuanlan.zhihu.com/p/26327347 https://zhuanlan.zhihu.com/p/582524766 包括野火、正点原子的资料 一片内存是 1Gbit 128MByte 16bit …...

《golang设计模式》第三部分·行为型模式-04-迭代器模式(Iterator)

文章目录 1. 概念1.1 角色1.2 类图 2. 代码示例2.1 需求2.2 代码2.3 类图 1. 概念 迭代器(Iterator)能够在不暴露聚合体内部表示的情况下,向客户端提供遍历聚合元素的方法。 1.1 角色 InterfaceAggregate(抽象聚合)…...

python加上ffmpeg实现音频分割

前言: 这是一个系列的文章,主要是使用python加上ffmpeg来对音视频文件进行处理,包括音频播放、音频格式转换、音频文件分割、视频播放等。 系列文章链接: 链接1: python使用ffmpeg来制作音频格式转换工具(优化版) 链接2:<Python>PyQt5+ffmpeg,简单视频播放器的编写(…...

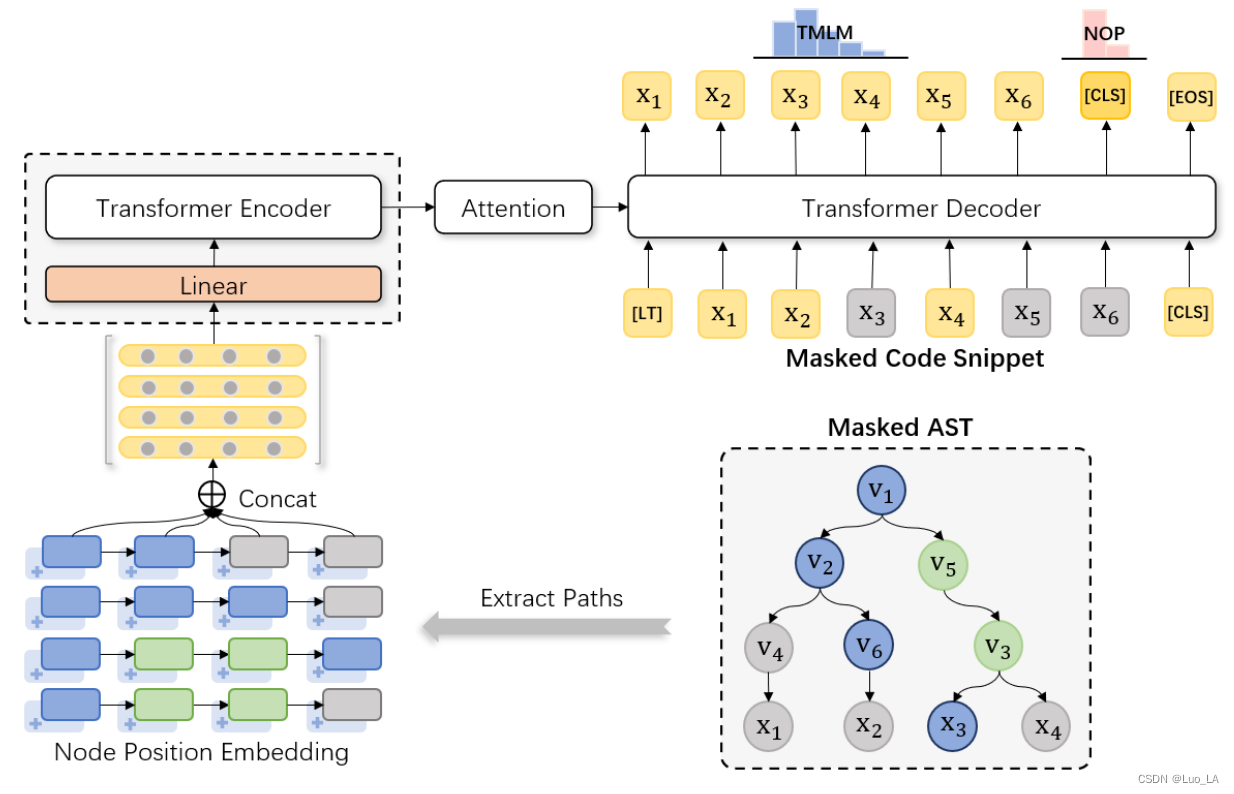

LLM之Prompt(一):5个Prompt高效方法在文心一言3.5的测试对比

在Effective Prompt: 编写高质量Prompt的14个有效方法文中我们了解了14个编写Prompt的方法(非常感谢原作者),那么这些Prompt在具体大模型中的效果如何呢?本文以百度文心一言3.5版本大模型在其中5个方法上做个测试对比。 第1条&am…...

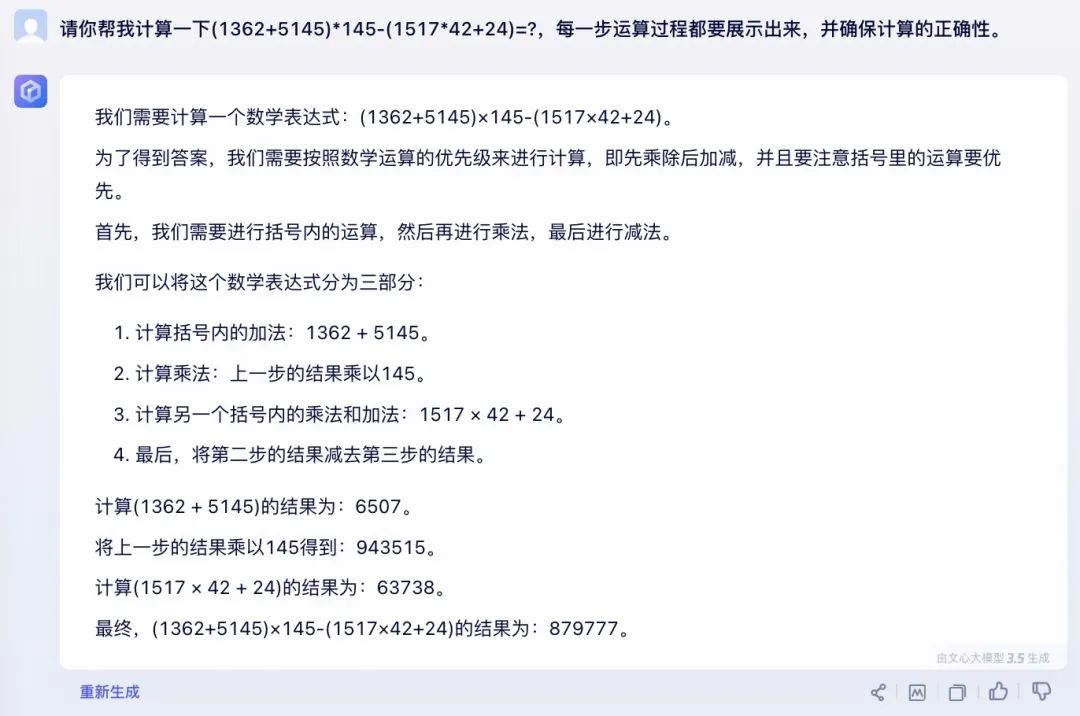

TreeBERT:基于树的编程语言预训练模型。

TreeBERT https://arxiv.org/abs/2105.12485 Comments: Accepted by UAI2021 Subjects: Machine Learning (cs.LG); Programming Languages (cs.PL) Cite as: arXiv:2105.12485 [cs.LG] 1 Introduction 现有挑战: 设计适当的机制来学习程序的语法结构 代码是强结…...

)

生成小程序的二维码的base64码(中间logo可以自定义)

1.生成基础二维码 /*** 生成微信小程序二维码,带参数,最终转成base64* param page 当前小程序相对页面 必须是已经发布的小程序存在的页面(否则报错),例如 pages/index/index, 根路径前不要填加 /,不能携带参数(参数请放在scene字段里),如果不…...

【音视频 | Ogg】Ogg封装格式详解——包含Ogg封装过程、数据包(packet)、页(page)、段(segment)等

😁博客主页😁:🚀https://blog.csdn.net/wkd_007🚀 🤑博客内容🤑:🍭嵌入式开发、Linux、C语言、C、数据结构、音视频🍭 🤣本文内容🤣&a…...

ubuntu 22.04 安装ros2 iron

目录 一、镜像 二、ifconfig 三、ssh连接不上 四、安装iron 一、镜像 123云盘直接下载 二、ifconfig sudo apt install net-tools 三、ssh连接不上 sudo apt install openssh-server 四、安装iron Ubuntu (Debian packages) — ROS 2 Documentation: Iron document…...

PHP语言、B/S手术麻醉临床信息管理系统源码

手术麻醉临床信息管理系统有着完善的临床业务功能,能够涵盖整个围术期的工作,能够采集、汇总、存储、处理、展现所有的临床诊疗资料。通过该系统的实施,能够规范麻醉科的工作流程,实现麻醉手术过程的信息数字化,自动生…...

Win11安装网络打印机

https://support.microsoft.com/zh-cn/windows/%E5%9C%A8-windows-%E4%B8%AD%E5%AE%89%E8%A3%85%E6%89%93%E5%8D%B0%E6%9C%BA-cc0724cf-793e-3542-d1ff-727e4978638b...

逆向学习记录(3)工具介绍jadx、gda和jeb

1、jadx 下载地址如下,目前最新版本为v1.4.7,改成想要下载的版本号就能下载对应的版本。 https://github.com/skylot/jadx/releases/tag/v1.4.7 下载后解压,进入对应路径的bin文件夹内,运行jadx-gui.bat。 2、gda 下载地址和gi…...

C#,数值计算——偏微分方程,Mglin的计算方法与源程序

1 文本格式 using System; using System.Collections.Generic; namespace Legalsoft.Truffer { public class Mglin { private int n { get; set; } private int ng { get; set; } private double[,] uj1 { get; set; } private Lis…...

一机服务万人,拓世法宝AI智能商业数字人一体机,解锁文旅新表达

在人工智能的强劲推动下,人们走进了一个令人振奋的数字化时代。如何让文化传承与现代科技完美融合,成为一个十分有趣的议题,当AI技术结合文旅生活,便悄然开启了一种全新的旅游服务模式——AI数字文旅。 在我国国家博物馆、文旅大…...

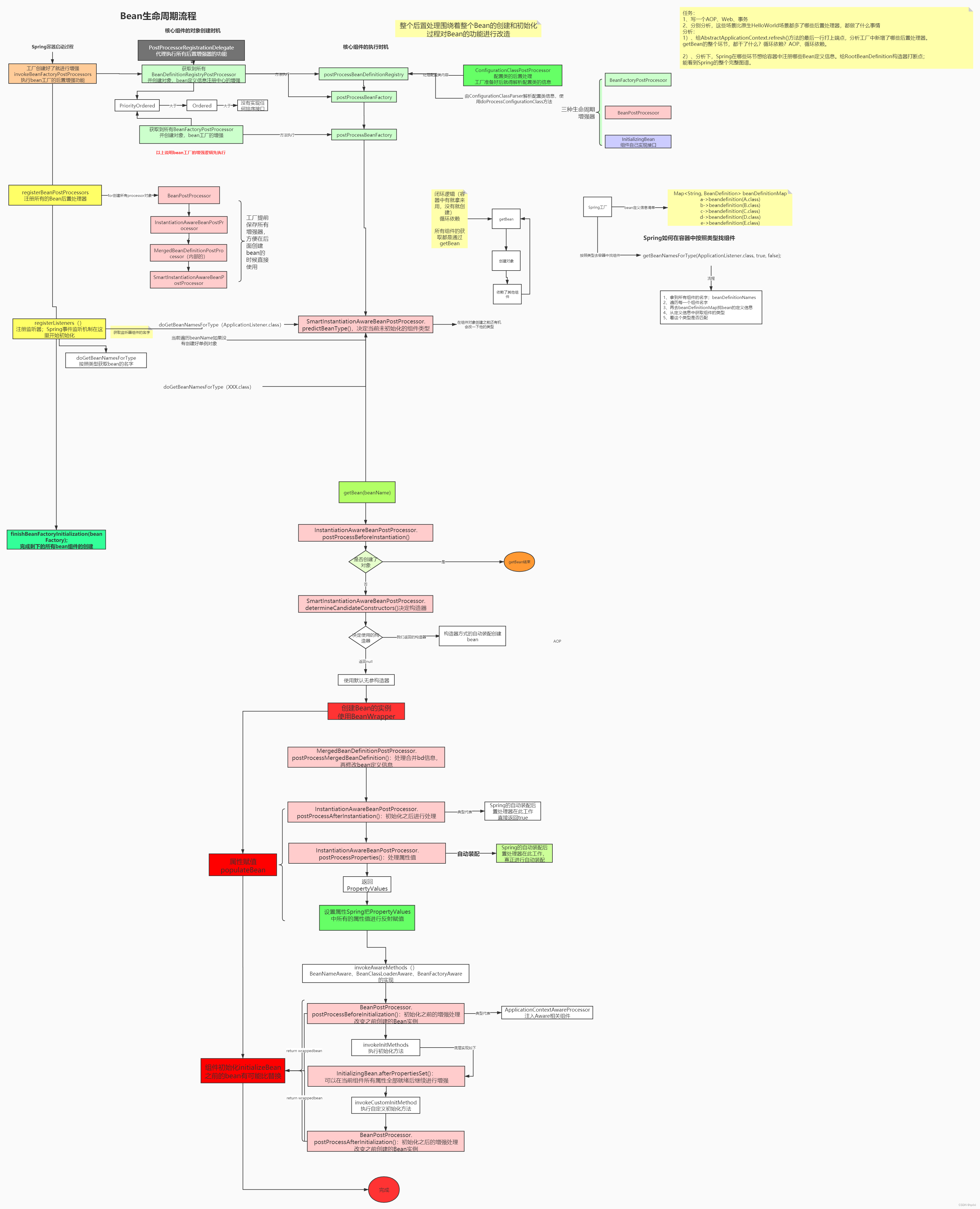

【源码解析】聊聊SpringBean是如何初始化和创建

我们知道通过类进行修复不同的属性,比如单例、原型等,而具体的流程是怎么样的呢,这一篇我们开始从源码的视角分析以下。 刷新方法 在刷新容器中有一个方法,其实就是 Bean创建的过程。 finishBeanFactoryInitialization(beanFact…...

【0基础学Java第六课】-- 数组的定义与使用

6 数组的定义与使用 6.1 什么是数组6.2 数组的创建及初始化6.2.1 数组的创建:6.2.2 数组的初始化 6.3 数组的使用6.3.1 数组中元素的访问6.3.2 Java中JVM当中的内存划分6.3.3 遍历数组 6.4 数组是引用类型6.4.1 初始JVM的内存分布6.4.2 基本类型变量与引用类型变量的…...

后台项目Gradle打包jar,不包含依赖jar并放到外部路径

# 1.Gradle打包jar # 2.依赖jar包外放到其他目录 # 3.保留引用关系 # 4.去掉引入的缓存build.gradle// 需要放到dependencies下面 // 傻逼问题 1 这个jar打包还得主动开 jar.enabled true // 1.清除上一次的lib目录 task clearJar(type: Delete) {delete "$buildDir\\lib…...

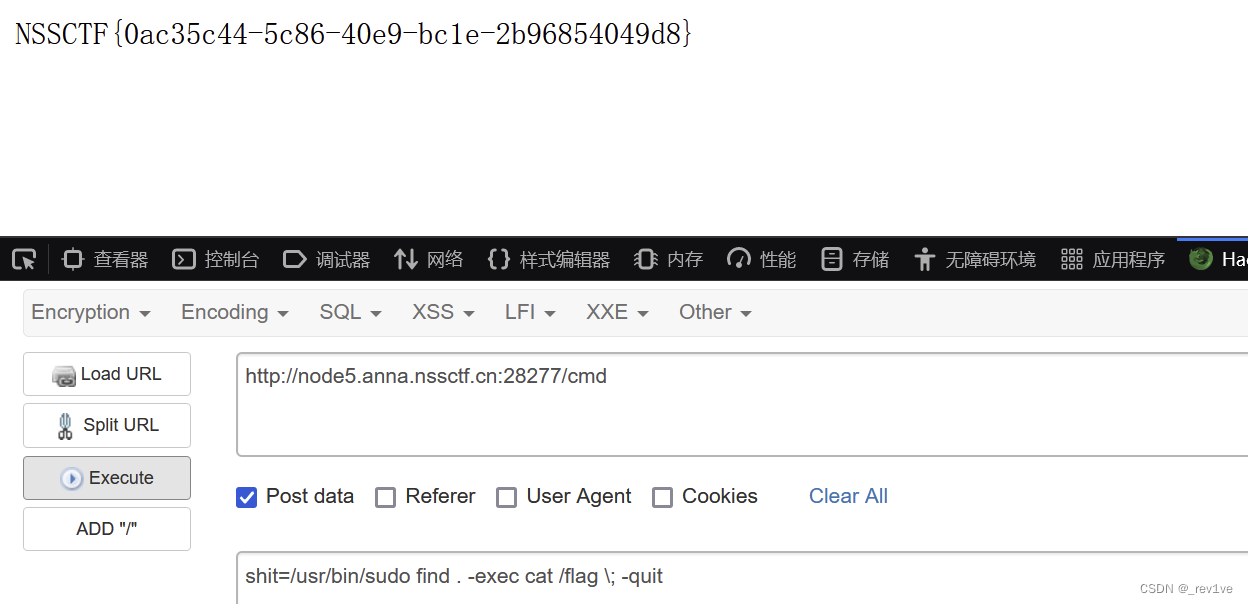

NSSCTF web刷题记录4

文章目录 [NSSRound#4 SWPU]1zweb(revenge)[强网杯 2019]高明的黑客[BJDCTF 2020]Cookie is so subtle![MoeCTF 2021]fake game[第五空间 2021]PNG图片转换器[ASIS 2019]Unicorn shop[justCTF 2020]gofs[UUCTF 2022 新生赛]phonecode[b01lers 2020]Life On Mars[HZNUCTF 2023 f…...

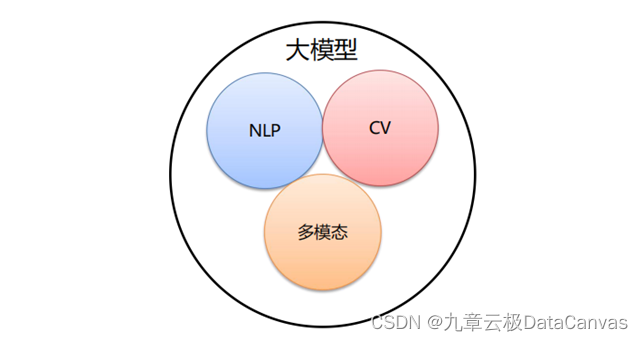

什么是大模型?一文读懂大模型的基本概念

大模型是指具有大规模参数和复杂计算结构的机器学习模型。本文从大模型的基本概念出发,对大模型领域容易混淆的相关概念进行区分,并就大模型的发展历程、特点和分类、泛化与微调进行了详细解读,供大家在了解大模型基本知识的过程中起到一定参…...

数据结构之队的实现

𝙉𝙞𝙘𝙚!!👏🏻‧✧̣̥̇‧✦👏🏻‧✧̣̥̇‧✦ 👏🏻‧✧̣̥̇:Solitary-walk ⸝⋆ ━━━┓ - 个性标签 - :来于“云”的“羽球人”。…...

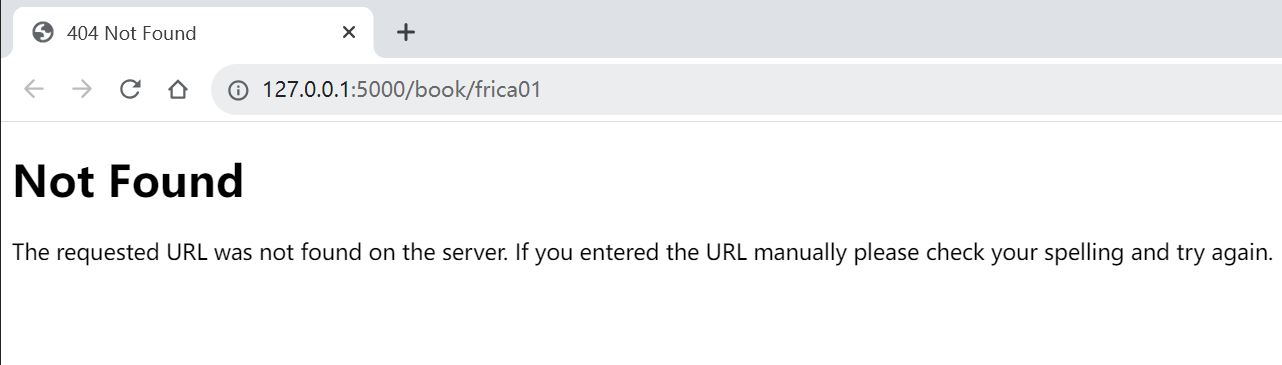

【实战Flask API项目指南】之三 路由和视图函数

实战Flask API项目指南之 路由和视图函数 本系列文章将带你深入探索实战Flask API项目指南,通过跟随小菜的学习之旅,你将逐步掌握 Flask 在实际项目中的应用。让我们一起踏上这个精彩的学习之旅吧! 前言 当小菜踏入Flask后端开发的世界时&…...

WebDataset社区支持:如何获取帮助与参与讨论

WebDataset社区支持:如何获取帮助与参与讨论 【免费下载链接】webdataset A high-performance Python-based I/O system for large (and small) deep learning problems, with strong support for PyTorch. 项目地址: https://gitcode.com/gh_mirrors/we/webdatas…...

3步永久解锁IDM:从试用期烦恼到终身免费使用的完整指南

3步永久解锁IDM:从试用期烦恼到终身免费使用的完整指南 【免费下载链接】IDM-Activation-Script IDM Activation & Trail Reset Script 项目地址: https://gitcode.com/gh_mirrors/id/IDM-Activation-Script IDM Activation Script(IAS&#…...

【100%通过率】华为OD机试真题2026双机位C卷 C++ 实现【红黑图】

目录 题目 思路 Code 题目 众所周知红黑树时一种平衡树,它最突出的特性就是不能有两个相连的红色节点。那我们定义一个红黑图,也就是一张无向图中,每个节点可能是红黑两种颜色,但我们保证没有两个相邻的红色节点。 现在给一张未染色的无向图,只能染红黑两种颜色,问总共…...

微信小程序对接实战:快速开发集成通义千问1.5-1.8B模型的AI聊天应用

微信小程序对接实战:快速开发集成通义千问1.5-1.8B模型的AI聊天应用 你是不是也想过,给自己的微信小程序加上一个智能聊天助手?比如,做一个能解答用户问题的客服机器人,或者一个能陪你闲聊、帮你写文案的创意伙伴。听…...

易景信息冲刺港股:年营收32亿同比降8% 核心管理层出自龙旗科技

雷递网 雷建平 4月3日上海易景信息科技股份有限公司(简称:“易景信息”)日前递交招股书,准备在港交所上市。年营收32亿同比降8% 利润7022万易景信息是一家AI时代的全栈智能硬件产品解决方案提供商,产品组合包括智能手机、平板电脑…...

宿主机与虚拟机网络配置打通

Kali 虚拟机网络配置笔记 一、基础网络模式 1. 桥接模式 (Bridged) 目的:让虚拟机加入物理局域网配置: 选择物理网卡(非VMnet1/VMnet8)启用"复制物理网络连接状态"(推荐笔记本用户) 结果…...

学习javaday2

数据类型转换不能对布尔值进行转换不能把对象类型转换为不相干的类型在把高容量转换到低容量时,强制类型转换转换的时候肯存在内存溢出,或者精度问题public class Demo06 {public static void main(String[] args){//操作比较大的数的时候,注…...

Docker容器优化全攻略

Docker容器优化全攻略 引言:Docker的效率革命 哥们,别整那些花里胡哨的!作为一个前端开发兼摇滚鼓手,我最烦的就是容器体积大、启动慢、运行卡。Docker容器的优化直接关系到部署效率、运行性能和资源消耗。今天,我就给…...

燃料电池氢气供应系统,阳极压力非线性状态控制simulink模型;自适应反...)

质子交换膜(PEM)燃料电池氢气供应系统,阳极压力非线性状态控制simulink模型;自适应反...

质子交换膜(PEM)燃料电池氢气供应系统,阳极压力非线性状态控制simulink模型;自适应反步法控制; 燃料电池电堆模型:阴极流道,阳极流道,膜水合传递,输出电压模型、 氢气回路…...

MS5540C传感器驱动开发:类SPI协议与校准算法详解

1. MS5540C传感器库深度解析:面向嵌入式工程师的底层驱动开发指南 MS5540C系列是TE Connectivity(原Measurement Specialties)推出的高精度、低功耗数字压力/温度复合传感器,广泛应用于潜水设备、气象站、工业过程监控及水下机器人…...