Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- FPGA图像处理方案

- FPGA视频拼接叠加融合方案推荐

- 3、设计思路详解

- Video Mixer介绍

- 4、工程代码1:2路视频拼接 HDMI 输出

- PL 端 FPGA 逻辑设计

- PS 端 SDK 软件设计

- 5、工程代码2:4路视频拼接 HDMI 输出

- PL 端 FPGA 逻辑设计

- PS 端 SDK 软件设计

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证并演示

- 准备工作

- 输出静态演示

- 输出动态演示

- 8、福利:工程源码获取

Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

1、前言

没玩过视频拼接都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。

目前市面上主流的FPGA视频拼接方案如下:

1:Xilinx的HLS方案,该方案简单,易于实现,但只能用于Xilinx自家的FPGA;

2:非纯Verilog方案,大部分代码使用Verilog实现,但中间的fifo或ram等使用了IP,导致移植性变差,难以在Xilinx、Altera和国产FPGA之间自由移植;

3:纯Verilog方案;

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为960x540@30Hz分辨率;工程用一路摄像头数据复制一份来模拟两路摄像头输入;然后调用2个Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;然后调用2个Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,VDMA需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Mixer IP核做两路视频拼接操作,Video Mixer需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;

提供两套vivado2019.1版本的工程源码和技术支持,两套工程的区别在于拼接的视频路数不同方式不同,详情如下:

第一套vivado工程源码:输入,OV5640摄像头;2路拼接输出,HDMI显示器;

第二套vivado工程源码:输入,OV5640摄像头;4路拼接输出,HDMI显示器;

Xilinx Zynq-7000系列FPGA实现视频拼接显示的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;整个工程调用Zynq软核做IP的配置,Zynq的配置在SDK里以C语言软件代码的形式运行,所以整个工程包括FPGA逻辑设计和SDK软件设计两部分,需要具备FPGA和嵌入式C语言的综合能力,不适合初学者或者小白;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

FPGA图像处理方案

我的主页目前有FPGA图像处理专栏,改专栏收录了我目前手里已有的FPGA图像处理方案,包括图像缩放、图像识别、图像拼接、图像融合、图像去雾、图像叠加、图像旋转、图像增强、图像字符叠加等等;以下是专栏地址:

点击直接前往

FPGA视频拼接叠加融合方案推荐

我的主页目前有FPGA视频拼接叠加融合专栏,改专栏收录了我目前手里已有的FPGA视频拼接叠加融合方案,从实现方式分类有基于HSL实现的视频拼接、基于纯verilog代码实现的视频拼接;从应用上分为单路、2路、3路、4路、8路、16路视频拼接;视频缩放+拼接;视频融合叠加;从输入视频分类可分为OV5640摄像头视频拼接、SDI视频拼接、CameraLink视频拼接等等;以下是专栏地址:

点击直接前往

3、设计思路详解

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为960x540@30Hz分辨率;工程用一路摄像头数据复制一份来模拟两路摄像头输入;然后调用2个Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;然后调用2个Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,VDMA需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Mixer IP核做两路视频拼接操作,Video Mixer需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;

提供两套vivado2019.1版本的工程源码和技术支持,两套工程的区别在于拼接的视频路数不同方式不同,详情如下:

第一套vivado工程源码:输入,OV5640摄像头;2路拼接输出,HDMI显示器;

第二套vivado工程源码:输入,OV5640摄像头;4路拼接输出,HDMI显示器;

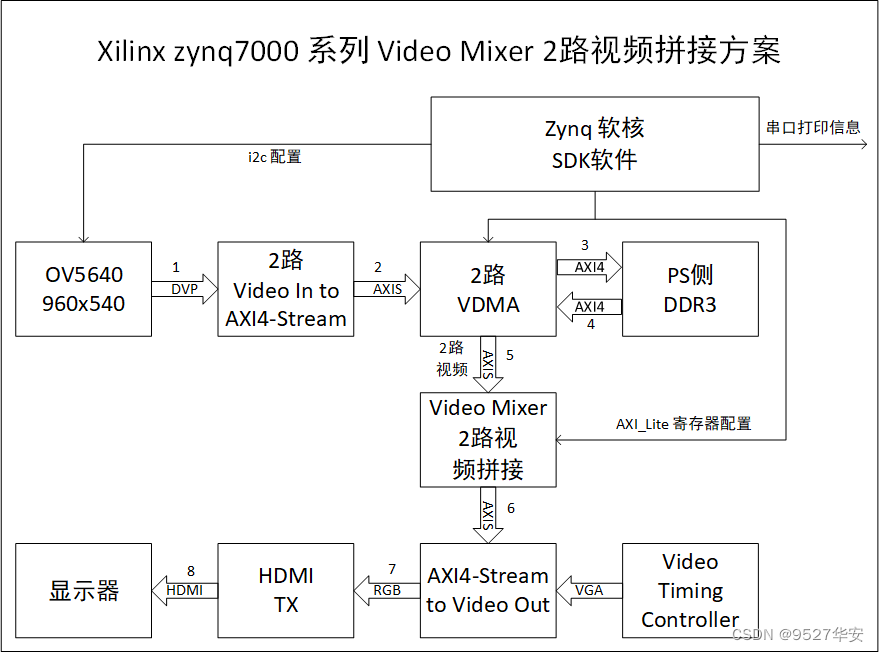

第一套vivado工程源码设计框图如下:

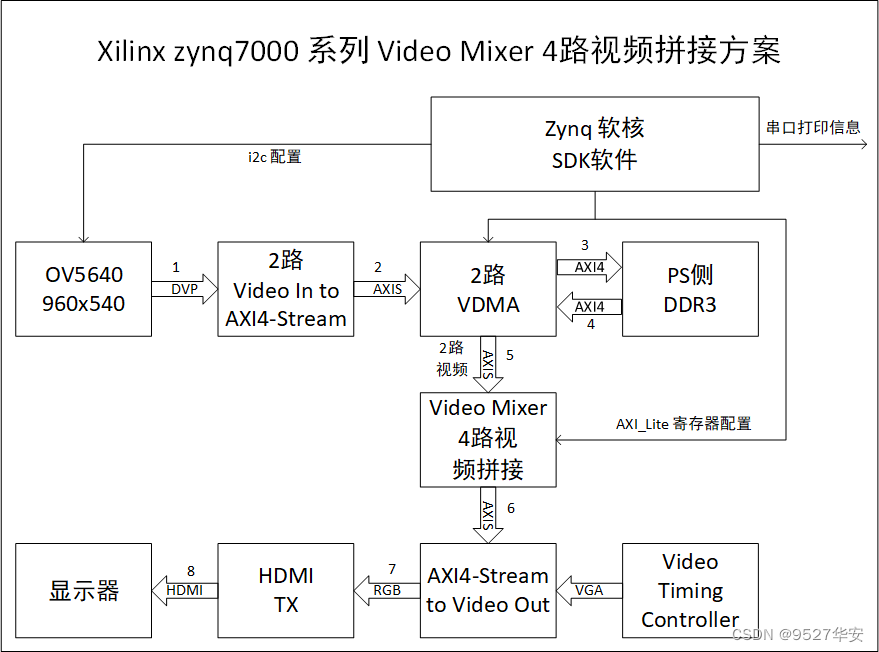

第二套vivado工程源码设计框图如下:

框图解释:箭头表示数据流向,箭头内文字表示数据格式,箭头外数字表示数据流向的步骤;

Video Mixer介绍

由于工程所用到的IP都是常用IP,所以这里重点介绍一下Video Mixer IP;

支持最大分辨率:8K,即可以处理高达8K的视频;

支持最多16层视频拼接叠加,即最多可拼接16路视频;

输入视频格式:AXI4-Stream;

输出视频格式:AXI4-Stream;

需要SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;

提供自定义的配置API,通过调用该库函数即可轻松使用,具体参考SDK代码;

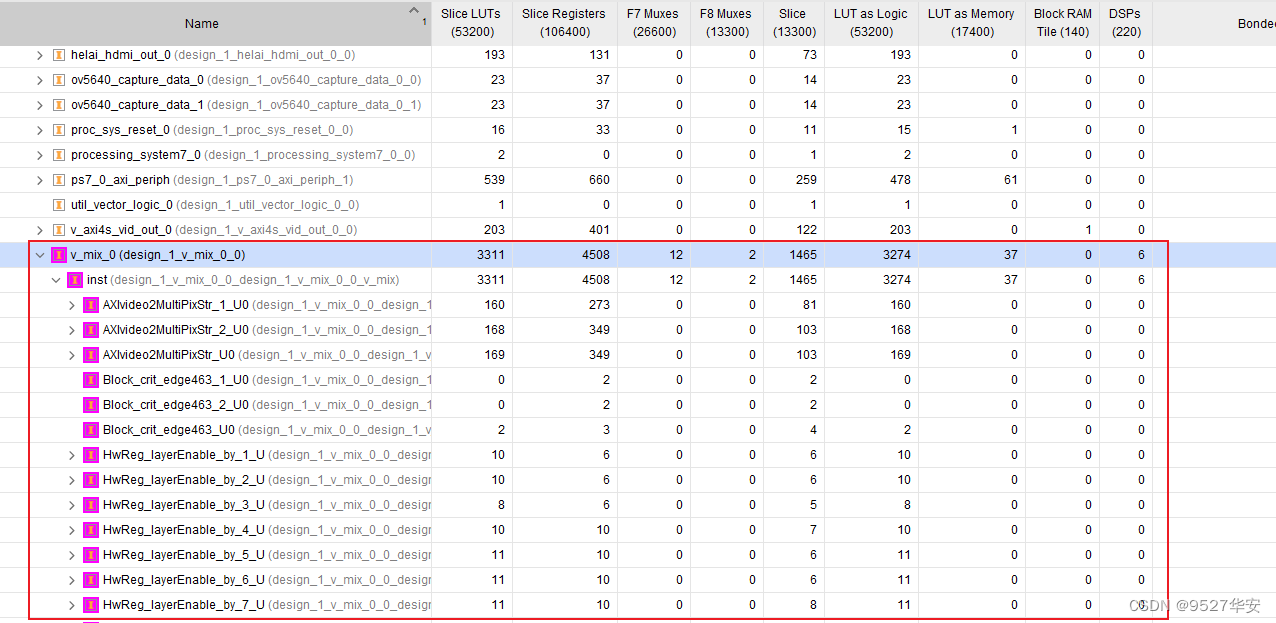

模块占用的FPGA逻辑资源更小,相比于自己写的HLS视频拼接而言,官方的Video Mixer资源占用大约减小30%左右,且更高效:

Video Mixer逻辑资源如下,请谨慎评估你的FPGA资源情况;

4、工程代码1:2路视频拼接 HDMI 输出

PL 端 FPGA 逻辑设计

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率960x540;

输出:HDMI,1920x1080黑色背景下拼接2路视频输出;

工程作用:Xilinx Zynq-7000系列FPGA实现视频拼接显示, HDMI 输出;

工程BD如下:

工程代码架构如下:

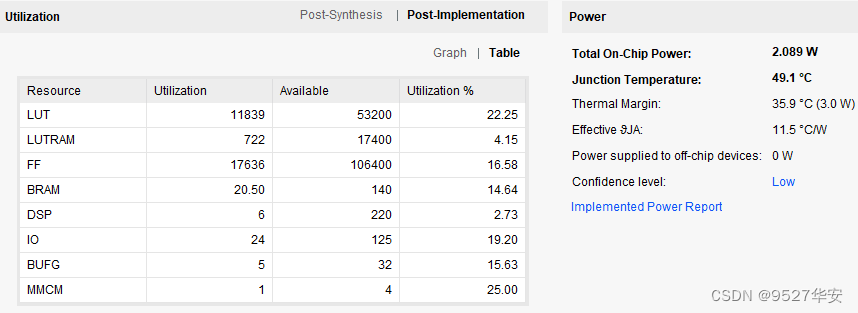

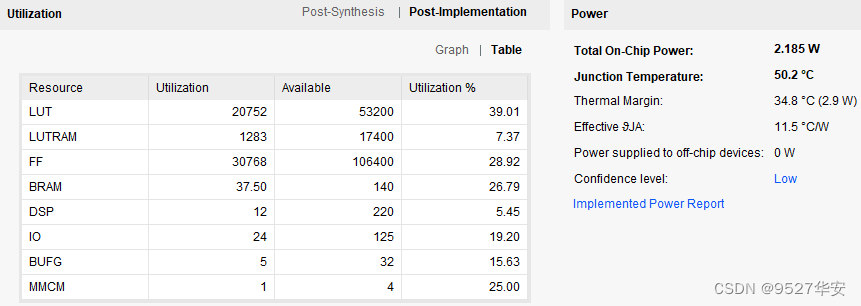

工程的资源消耗和功耗如下:

PS 端 SDK 软件设计

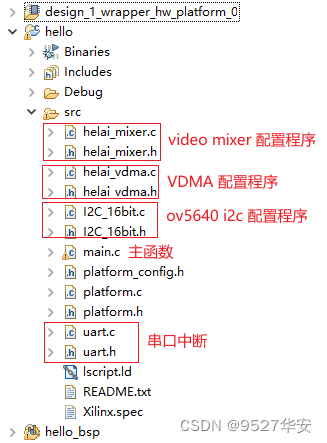

PS 端 SDK 软件工程代码架构如下:

PS工程主函数如下:

#include "I2C_16bit.h"

#include "xiicps.h"

#include "xil_io.h"

#include "xparameters.h"

#include "helai_vdma.h"

#include "helai_mixer.h"

#include "uart.h"XIicPs Iic;

XScuGic Intc; //中断控制器驱动程序实例

XUartPs Uart_Ps; //串口驱动程序实例

void main()

{uart_init(&Uart_Ps); //串口初始化uart_intr_init(&Intc, &Uart_Ps); //串口中断初始化I2C_config_init(); //ov5640 配置完成helai_vdma(); // VDMA 配置完成helai_mixer(); // video mixer 配置完成print("zynq7020 两路视频拼接:\n\r");print("输入视频分辨率:960x540\n\r");print("1920x1080黑色背景下拼接两路视频输出\n\r");while (1) ;

}

5、工程代码2:4路视频拼接 HDMI 输出

PL 端 FPGA 逻辑设计

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率960x540;

输出:HDMI,1920x1080黑色背景下拼接4路视频输出;

工程作用:Xilinx Zynq-7000系列FPGA实现视频拼接显示, HDMI 输出;

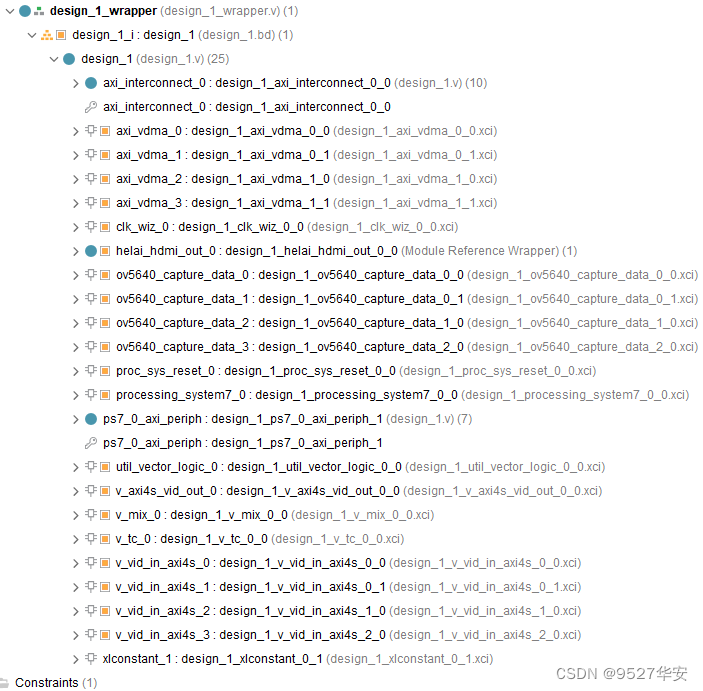

工程BD如下:

工程代码架构如下:

工程的资源消耗和功耗如下:

PS 端 SDK 软件设计

PS 端 SDK 软件工程代码架构如下:

#include "I2C_16bit.h"

#include "xiicps.h"

#include "xil_io.h"

#include "xparameters.h"

#include "helai_vdma.h"

#include "helai_mixer.h"

#include "uart.h"XIicPs Iic;

XScuGic Intc; //中断控制器驱动程序实例

XUartPs Uart_Ps; //串口驱动程序实例

void main()

{uart_init(&Uart_Ps); //串口初始化uart_intr_init(&Intc, &Uart_Ps); //串口中断初始化I2C_config_init(); //ov5640 配置完成helai_vdma(); // VDMA 配置完成helai_mixer(); // video mixer 配置完成print("zynq7020 四路视频拼接:\n\r");print("输入视频分辨率:960x540\n\r");print("1920x1080黑色背景下拼接四路视频输出\n\r");while (1) ;

}

6、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证并演示

准备工作

Zynq7000系列开发板;

OV5640摄像头;

HDMI显示器,支持1080P;

输出静态演示

工程1:ov5640输入分辨率960x540,2路视频拼接输出如下:

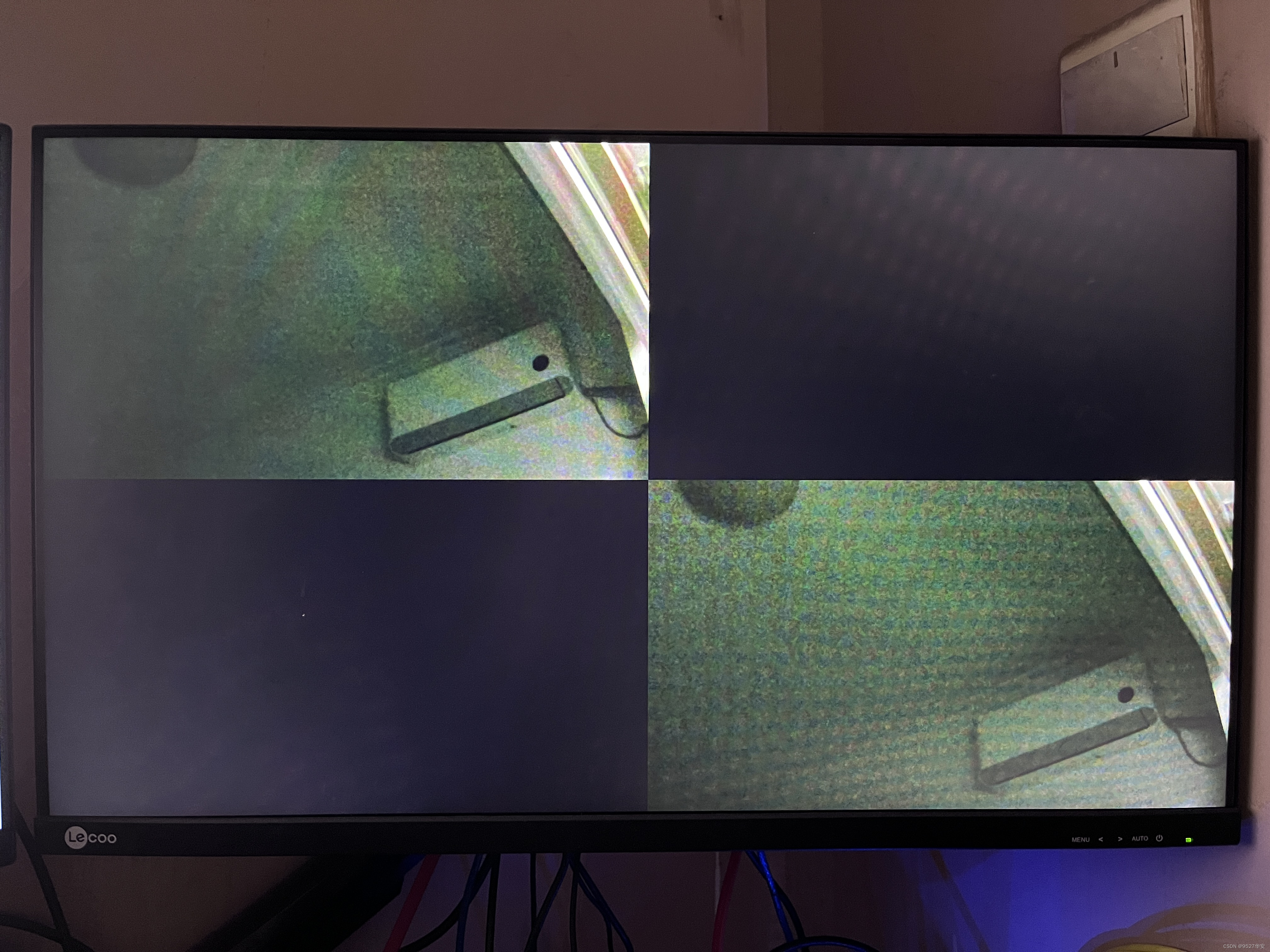

工程2:ov5640输入分辨率960x540,4路视频拼接输出如下:

输出动态演示

录制了一个小视频,输出动态演示如下:

video-mixer-hdmi

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA视频拼接叠加融合方案推荐 3、设计思路详解Video Mixer介绍 4、工程代码1:2路视频拼接 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:4路视频拼接 HDMI 输出PL 端 FPGA 逻辑设…...

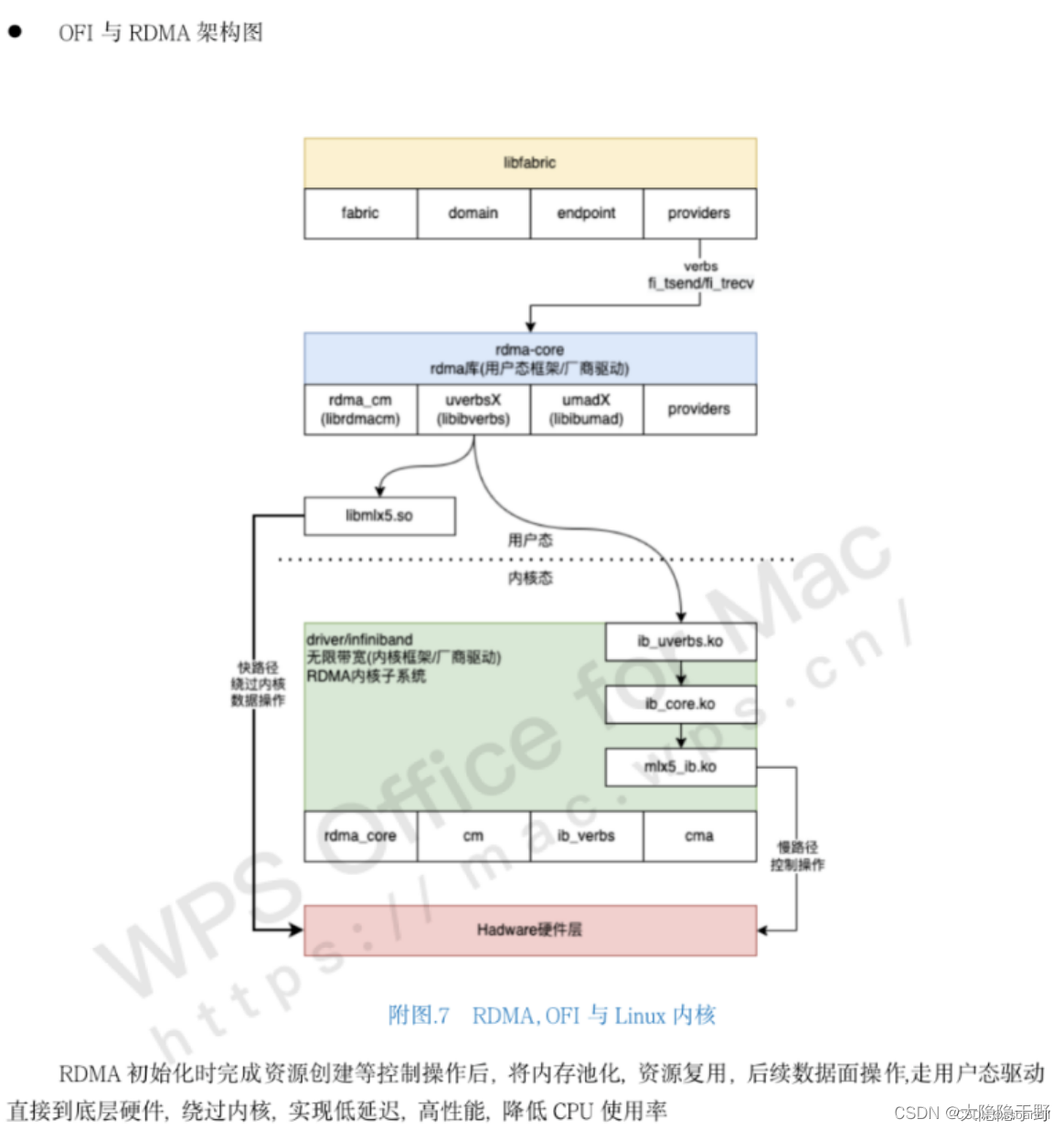

DAOS低时延与高性能RDMA网络

什么是RDMA RDMA(Remote Direct Memory Access)远程直接内存访问是一种技术,它使两台联网的计算机能够在主内存中交换数据,而无需依赖任何一台计算机的处理器、缓存或操作系统。与基于本地的直接内存访问 ( DMA ) 一样,…...

城市管理实景三维:打造智慧城市的新引擎

城市管理实景三维:打造智慧城市的新引擎 在城市管理领域,实景三维技术正逐渐成为推动城市发展的新引擎。通过以精准的数字模型呈现城市真实场景,实景三维技术为城市决策提供了全新的思路和工具。从规划设计到交通管理,从环境保护到…...

Python3.11+Pyside6开发电影下载程序

VideoSave是一款使用Python3.11Pyside6编写的提供下载电影/电视剧的软件,支持注册、登录、搜索、下载、查看日志等功能,提供了Window、Mac系统安装包。 先上效果图 提供功能 节省寻找资源的时间 ⌚️模糊搜索指定影片 🐴查看影片下载日志 &…...

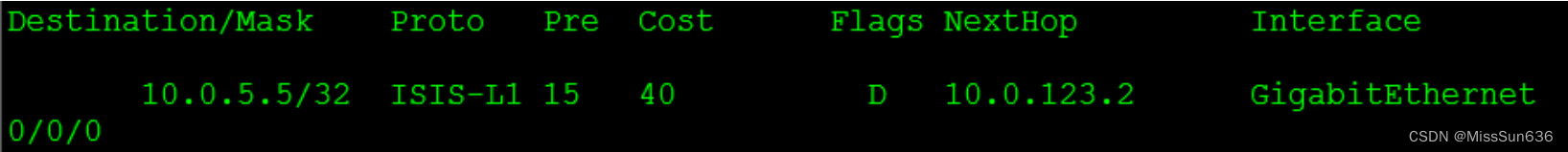

HCIP-七、IS-IS 综合实验

七、IS-IS 综合实验 实验拓扑实验需求及解法1.如图所示,配置所有路由器的接口IP地址。2.运行IS-IS,进程号13.IS-IS优化4.路径优化 实验拓扑 实验需求及解法 本实验模拟IS-IS综合网络,完成以下需求: 1.如图所示,配置所…...

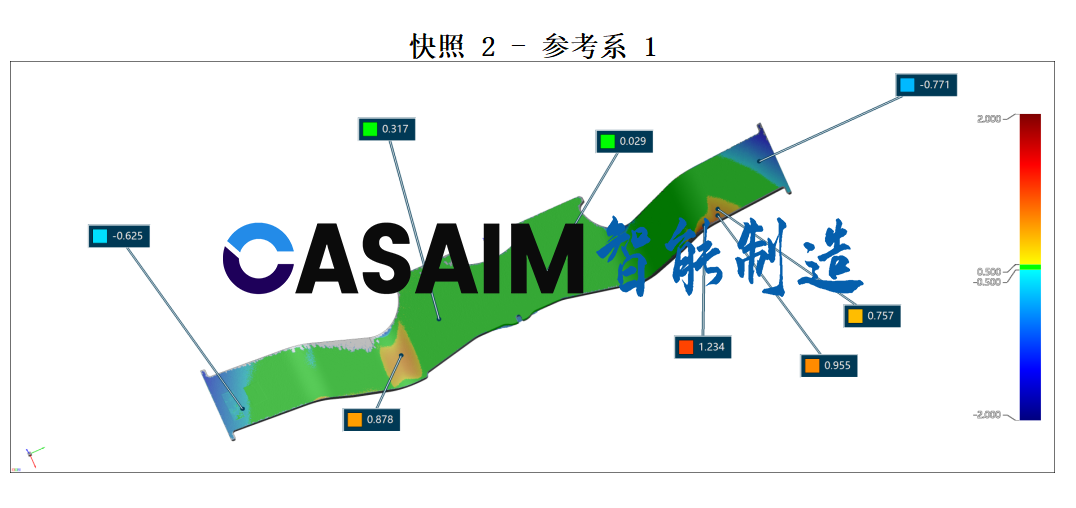

广西桂林钢结构钣金折弯件3d扫描全尺寸偏差检测-CASAIM中科广电

钣金是一种针对金属薄板(通常在6mm以下)的综合冷加工工艺,包括剪、冲/切/复合、折、焊接、铆接、拼接、成型(如汽车车身)等,其显著的特征就是同一零件厚度一致,通过钣金工艺加工出的产品叫做钣金…...

飞翔的小鸟游戏

一.建一个bird的类,放入素材 二.代码 1.Bird类 package bird;import javax.imageio.ImageIO; import java.awt.image.BufferedImage; import java.io.IOException;/** 小鸟类* */ public class Bird {int x;// 坐标int y;int width; // 宽高int height;BufferedIm…...

计算机网络之运输层

一、概述 物理层、数据链路层以及网络层它们共同解决了将主机通过异构网络互联起来所面临的的问题,实现了主机到主机的通信 但实际上在计算机网络中进行通信的真正实体是位于通信两端主机中的进程 如何为运行在不同主机上的应用进程提供直接的通信服务时运输层的任务…...

2023软件应用类下载系统平台源码/手机软件应用、新闻资讯下载站/软件库网站源码

源码简介: 这个是最新软件应用类平台源码、手机应用下载系统源码、软件应用市场下载站源码、新闻资讯软件下载。2023软件应用类平台源码/手机软件应用、新闻资讯下载站,它是软件库网站源码。 最新软件应用类平台源码 手机应用下载系统源码 软件应用市场…...

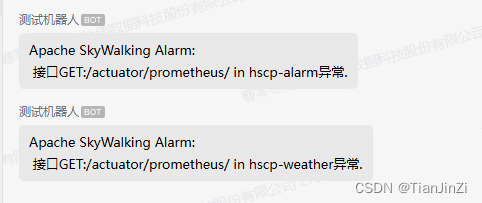

SkyWalking配置报警推送到企业微信

1、先在企业微信群里创建一个机器人,复制webhook的地址: 2、找到SkyWalking部署位置的alarm-settings.yml文件 编辑,在最后面加上此段配置 !!!一定格式要对,不然一直报警报不出来按照网上指导…...

educoder中Hive -- 索引和动态分区调整

第1关:Hive -- 索引 ---创建mydb数据库 create database if not exists mydb; ---使用mydb数据库 use mydb; ---------- Begin ---------- ---创建staff表 create table staff( id int, name string, sex string) row format delimited fields terminated by , stored…...

http与https有什么区别,https攻击要如何防护

我们在浏览网站时,在网址的前面经常会看到http// 或者https//的显示。同样是http,加了s与不加s是有什么区别,加了s又有哪些用处。 http,中文叫做超文本传输协议。它是一种用于分布式、协作式和超媒体信息系统的应用层协议。是基于…...

nginx+keepalived

一、简介 很久没有配置keepalived了,最近业务医院需要配置前置机做转发,并且配置keepalived. 因为医院的生产环境和外界是完全隔离的,所以需要做前置机做网络请求转发 二、服务器列表 角色IP备注nginx keepalived master192.168.1.22ngin…...

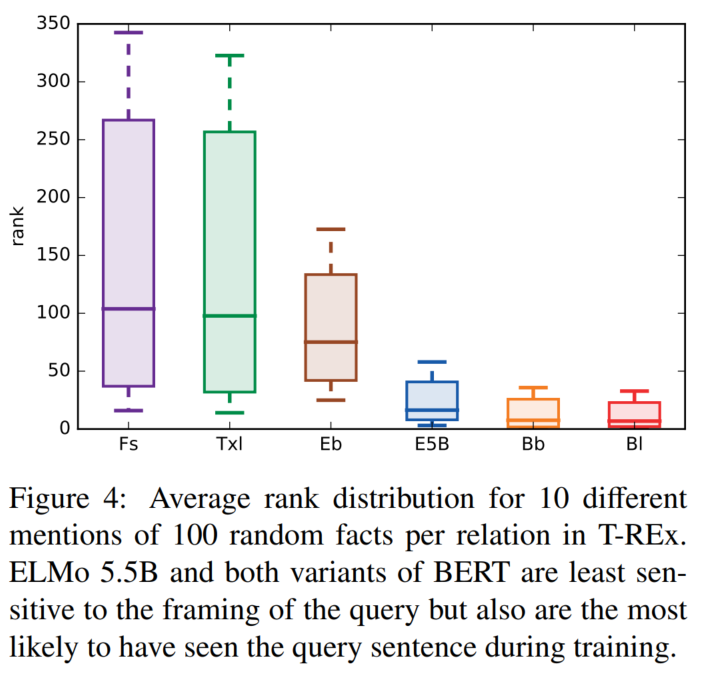

Re51:读论文 Language Models as Knowledge Bases?

诸神缄默不语-个人CSDN博文目录 诸神缄默不语的论文阅读笔记和分类 论文名称:Language Models as Knowledge Bases? ArXiv网址:https://arxiv.org/abs/1909.01066 官方GitHub项目:https://github.com/facebookresearch/LAMA 本文是2019年…...

.NET 使用配置文件

我简单测试了一下json格式配置文件,在这里记录一下,方便以后查看。 需要引用的库: Microsoft.Extensions.Hosting 创建json格式文件:appsettings.json 在工程文件中包含json文件: <ItemGroup><Content In…...

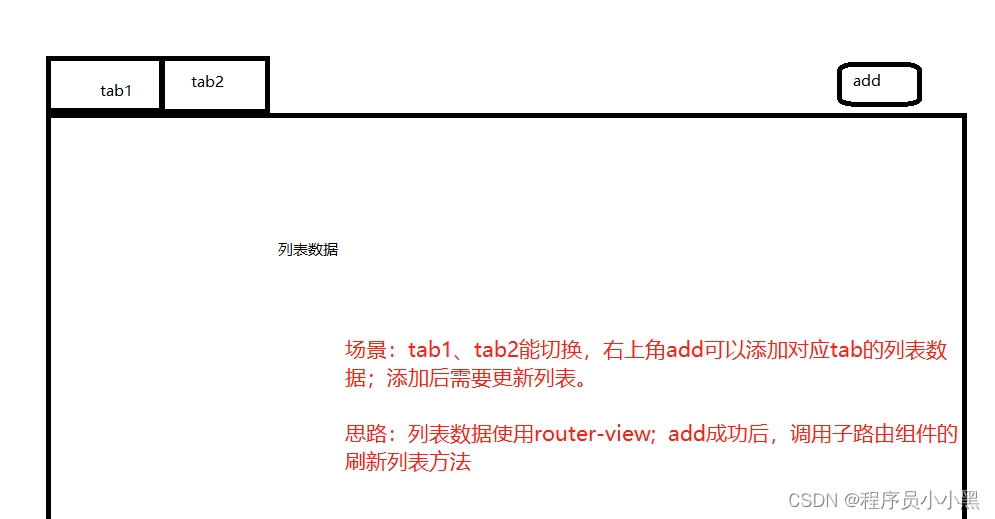

vue 通过ref调用router-view子组件的方法

由于用的vue2.7版本,但用了vue3 setup的语法; 注意:是vue2的template结构,vue3的setup语法;非这种情况需要举一反三。 处理方案: 1、对router-view加上ref template修改 直接对router-view加上ref&#x…...

在全球碳市场中崭露头角的中碳CCNG

在全球气候治理的大背景下,中国碳中和发展集团有限公司(简称中国碳中和)正在成为全球碳交易市场的一个重要参与者。随着国际社会对碳排放的日益关注,中国碳中和凭借其在碳资产开发、咨询与管理等领域的深厚积累,正成为…...

uni-app - 弹出框

目录 1.基本介绍 2.原生uinapp 通过uni.showActionSheet实现 3.使用组件 Popup 弹出层 ③效果展示 1.基本介绍 弹出框让我们在需要时在屏幕底部弹出一个菜单,它通常用于在各种应用程序中进行选择操作。Uniapp为我们提供了基本的底部弹出框组件,但它也有…...

深度学习之基于Tensorflow卷积神经网络鸟类目标识别检测系统

欢迎大家点赞、收藏、关注、评论啦 ,由于篇幅有限,只展示了部分核心代码。 文章目录 一项目简介 二、功能三、系统四. 总结 一项目简介 基于Tensorflow的卷积神经网络(Convolutional Neural Networks,CNN)在鸟类目标识…...

关闭EntityFramework日志输出SQL

项目场景: 提示:这里简述项目相关背景: EntityFramework日志输出SQL 问题描述 提示:这里描述项目中遇到的问题: EntityFramework日志输出SQL,造成发布后,无效日志太多,且容器化部…...

【4】为什么Go能挂住成千上万个goroutine,线程却没爆?一次讲透GMP调度模型

如果你写 Go 写的久了,很容易对一件事习以为常:请求来了,起一个 goroutine;后台任务想并发跑,再起几个 goroutine;网络连接一多,程序里挂着成千上万个 goroutine,好像也不算什么稀奇…...

android 原生桌面上有一个搜索栏图标,如何去掉?

android 原生桌面上有一个搜索栏图标,如何去掉?下载下面的资源解决!通过网盘分享的文件:去掉桌面的google图标-2.zip 链接: https://pan.baidu.com/s/15FFPgw-O0FCyZBi99o_MXg?pwd27dm 提取码: 27dm...

微信小程序图片裁剪终极实战:we-cropper完整开发指南

微信小程序图片裁剪终极实战:we-cropper完整开发指南 【免费下载链接】we-cropper 微信小程序图片裁剪工具 项目地址: https://gitcode.com/gh_mirrors/we/we-cropper we-cropper是一款专为微信小程序设计的轻量级canvas图片裁剪工具,能够帮助开发…...

文墨共鸣大模型企业级部署架构:高可用与内网穿透访问方案

文墨共鸣大模型企业级部署架构:高可用与内网穿透访问方案 最近和几个做企业服务的朋友聊天,他们都在头疼同一个问题:好不容易把大模型部署到内网了,性能也调优了,但怎么让外部的合作伙伴或者移动端的应用安全地访问呢…...

如何5分钟快速部署GreaterWMS:终极开源仓库管理系统指南

如何5分钟快速部署GreaterWMS:终极开源仓库管理系统指南 【免费下载链接】GreaterWMS This Inventory management system is the currently Ford Asia Pacific after-sales logistics warehousing supply chain process . After I leave Ford , I start this projec…...

番茄小说下载器深度解密:Rust高性能架构如何征服百万字下载挑战

番茄小说下载器深度解密:Rust高性能架构如何征服百万字下载挑战 【免费下载链接】Tomato-Novel-Downloader 番茄小说下载器不精简版 项目地址: https://gitcode.com/gh_mirrors/to/Tomato-Novel-Downloader 想象一下这样的场景:你在地铁通勤时想追…...

Navicat重置工具:Mac用户的终极试用期延长解决方案

Navicat重置工具:Mac用户的终极试用期延长解决方案 【免费下载链接】navicat_reset_mac navicat mac版无限重置试用期脚本 Navicat Mac Version Unlimited Trial Reset Script 项目地址: https://gitcode.com/gh_mirrors/na/navicat_reset_mac Navicat作为Ma…...

Allegro异形焊盘避坑指南:Shape Symbol导入层设置与阻焊开窗的正确姿势

Allegro异形焊盘设计实战:从Shape Symbol导入到阻焊开窗的完整避坑手册 在高速连接器与金手指封装设计中,异形焊盘的精确实现往往是工程师面临的第一个技术门槛。许多用户按照教程步骤操作时,常会在DXF导入失败、阻焊开窗不规范等环节反复踩坑…...

Go微服务开发利器:Kratos Blades工具集核心功能与实战指南

1. 项目概述:一把为Go微服务架构量身定制的“瑞士军刀”如果你正在用Go语言构建微服务,尤其是深度使用Kratos框架,那么你一定对项目依赖管理、代码生成、服务治理这些繁琐但又至关重要的“脏活累活”感到头疼。手动执行go mod tidy、反复敲打…...

当英雄联盟回放文件成为技术考古现场:ROFL播放器的多格式兼容挑战与解决方案

当英雄联盟回放文件成为技术考古现场:ROFL播放器的多格式兼容挑战与解决方案 【免费下载链接】ROFL-Player (No longer supported) One stop shop utility for viewing League of Legends replays! 项目地址: https://gitcode.com/gh_mirrors/ro/ROFL-Player …...