verilog编程题

verilog编程题

文章目录

- verilog编程题

- 序列检测电路(状态机实现)

- 分频电路

- 计数器

- 译码器

- 选择器

- 加减器

- 触发器

- 寄存器

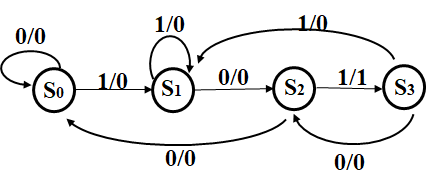

序列检测电路(状态机实现)

module Detect_101(input clk,input rst_n,input data,output flag_101);parameter S0 = 0,S1 = 1,S2 = 2,S3 = 3;reg [1:0] state;always @(posedge clk or negedge rst_n)beginif(rst_n == 1'b0)beginstate <= S0;endelse begincase(state)S0: if(data == 1)state <= S1;else state <= S0;S1: if(data == 0)state <= S2;else state <= S1;S2:if(data == 1)state <= S3;else state <= S0;S3:if(data == 1)state <= S1;else state <= S2;default:state <=S0; endcaseend

endassign flag_101 = (state == S3)? 1'b1: 1'b0;endmodule

分频电路

采用触发器反向输出端连接到输入端的方式,可构成简单的 2 分频电路。

以此为基础进行级联,可构成 4 分频,8 分频电路。

按题目要求,几分频就留哪个。

module even_divisor# (parameter DIV_CLK = 10 )(input rstn ,input clk,output clk_div2,output clk_div4,output clk_div10);//2 分频reg clk_div2_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginclk_div2_r <= 'b0 ;endelse beginclk_div2_r <= ~clk_div2_r ;endendassign clk_div2 = clk_div2_r ;//4 分频reg clk_div4_r ;always @(posedge clk_div2 or negedge rstn) beginif (!rstn) beginclk_div4_r <= 'b0 ;endelse beginclk_div4_r <= ~clk_div4_r ;endendassign clk_div4 = clk_div4_r ;//N/2 计数reg [3:0] cnt ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt <= 'b0 ;endelse if (cnt == (DIV_CLK/2)-1) begincnt <= 'b0 ;endelse begincnt <= cnt + 1'b1 ;endend//输出时钟reg clk_div10_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginclk_div10_r <= 1'b0 ;endelse if (cnt == (DIV_CLK/2)-1 ) beginclk_div10_r <= ~clk_div10_r ;endendassign clk_div10 = clk_div10_r ;

endmodule

计数器

module Count

(input clk ,input rst_n ,output reg [ 3:0] cnt

);always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt <= 4'd0;else if(cnt==4'd9)cnt <= 4'd0;elsecnt <= cnt + 1'b1;

endendmodule

译码器

`timescale 10ns/1ns

module decode3_8 (data_out,data_in,enable) ;

input [2:0] data_in;

input enable;

output [7:0] data_out;

reg [7:0] data_out;always @(data_in or enable)

beginif (enable==1)case (data_in )3'b000: data_out=8'b11111110;3'b001: data_out=8'b11111101;3'b010: data_out=8'b11111011;3'b011: data_out=8'b11110111;3'b100: data_out=8'b11101111;3'b101: data_out=8'b11011111;3'b110: data_out=8'b10111111;3'b111: data_out=8'b01111111;default: data_out=8'bxxxxxxxx;endcaseelsedata_out=8'b11111111;

endendmodule

选择器

代码为4选1,如果题目是2选1或者更多选1就case后进行更改

module mux_4_1 (input C, D, E, F,input [1:0] S,output reg Mux_out

);always @ (C or D or E or F or S) begincase(S)2'b00 : Mux_out = C;2'b01 : Mux_out = D;2'b10 : Mux_out = E;default : Mux_out = F;endcase

endendmodule

加减器

16位加减法器。当sub为1时,是减法;当sub为0时是加法。

看题目要求,有几位写几位

module top_module(input [31:0] a,input [31:0] b,input sub,output [31:0]sum);

wire [31:0]xor_1;

wire [15:0]sum_1;

wire [15:0]sum_2;

wire cout_1,cout_2;

//xor xor_gate(xor_1,b,sub);//逻辑或,我们这里的设计不应该是逻辑或,应该是下边的按位取或

assign xor_1 = b^{32{sub}} ;//按位异或

assign sum = {sum_2,sum_1};

add16 u1_add16(.a(a[15:0]),.b(xor_1[15:0]),.cin(sub),.sum(sum_1),.cout(cout_1));

add16 u2_add16(.a(a[31:16]),.b(xor_1[31:16]),.cin(cout_1),.sum(sum_2),.cout(cout_2));endmodule触发器

带同步清0、同步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)input d,clk,set,reset;output q,qn;reg q,qn;always @ (posedge clk)beginif(reset) begin q<=0;qn<=1;end//同步清0,高有效else if(set) begin q<=1;qn<=1;end //同步置1,高有效else begin q<=~d;qn<=~d;endend endmodule

寄存器

有异步清零端的n位寄存器,看题目要求,有几位n就写几

module regn(D,clk,reset,Q);parameter n=16;input [n-1] D;input clk,reset;output [n-1] reg Q;always @(negedge reset,posedge clk)if(!reset) //复位端reset低电平有效Q<=0;elseQ<=D;endmodule

相关文章:

verilog编程题

verilog编程题 文章目录 verilog编程题序列检测电路(状态机实现)分频电路计数器译码器选择器加减器触发器寄存器 序列检测电路(状态机实现) module Detect_101(input clk,input rst_n,input data,o…...

What is `addArgumentResolvers` does in `WebMvcConfigurer` ?

addArgumentResolvers 在SpringMVC框架中,主要用于向Spring容器注册自定义的参数解析器。在处理HTTP请求时,SpringMVC会使用这些参数解析器将请求中的数据(如查询参数、路径变量、表单数据等)转换并注入到控制器方法的参数中。 使…...

[NSSCTF Round#16 Basic]RCE但是没有完全RCE

RCE但是没有完全RCE wp 题目代码: 第一关 <?php error_reporting(0); highlight_file(__file__); include(level2.php); if (isset($_GET[md5_1]) && isset($_GET[md5_2])) {if ((string)$_GET[md5_1] ! (string)$_GET[md5_2] && md5($_GET[m…...

LTD营销枢纽(乐通达)成为杭州市中小企业数字化转型遴选服务商

为推进国家中小企业数字化转型城市试点建设,赋能中小企业信息化、智能化、新型工业化能力水平提升,杭州市经信局公开招募了具备高质量服务能力的中小企业数字化转型服务商。经过公开征集、专家评审等多个环节,LTD营销枢纽凭借其在数字化转型领…...

详细分析Mybatis中的<foreach>标签

目录 前言1. 基本语法2. Demo3. 实际例子 前言 对于Java专栏:Java专栏 对于Mybatis的相关知识可看我之前的文章:Mybatis从入门到精通(全) 对于其余Java框架可看我之前的文章:java框架 零基础从入门到精通的学习路线 附…...

linux-挂载Samba共享

linux-挂载Samba共享 1、linux服务器启动Samba共享服务 2、客户端电脑安装cifs-utils dnf install cifs-utils # 或 yum install cifs-utils3、挂载共享目录 # 创建挂目录 mkdir /share # 使用mount命令挂在共享目录,-t协议类型 -o用户名密码 共享目录访问地址 挂…...

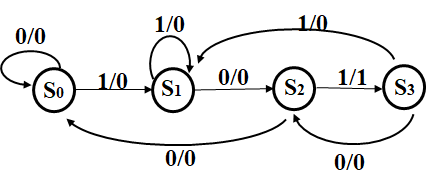

Java入门IDEA基础语法

1:Java入门 1.1 Java简介 Java是什么: Java是一门非常优秀的计算机语言 语言:人与人交流沟通的表达方式 计算机语言:人与计算机之间进行信息交流沟通的一种特殊语言 Java之父:詹姆斯高斯林(James Gosli…...

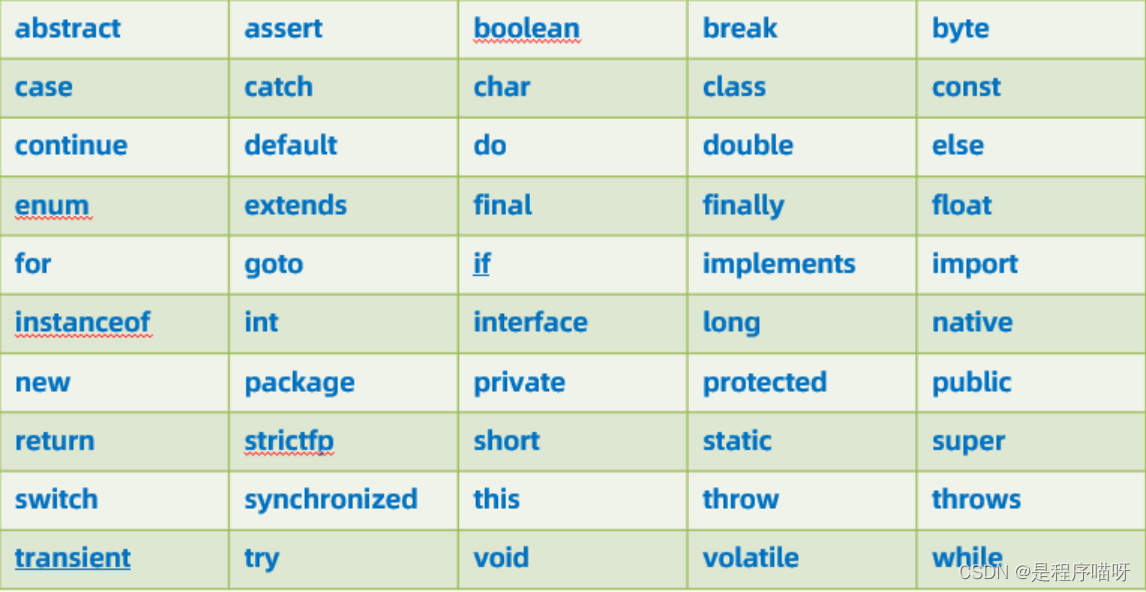

【小白专用】C# 连接 MySQL 数据库

C# – Mysql 数据库连接 1. 配置环境 #前提:电脑已安装Mysql服务; Visual Studio 安装Mysql依赖库: 工具 -> NuGet 包管理器 -> 管理解决方案的 NuGet程序包 —> 搜索, 安装Mysql.Data (Oracle); (安装成功后&…...

Django登录注销视图

Django在身份验证框架中包含了一些你可以直接使用的表单和视图。在大多数情况下,可以使用默认的Django认证视图。 Django在django.contrib.auth.views提供了以下基于类的视图来处理身份验证: LoginView:处理登录表单并登录用户 LogoutView&a…...

云原生到底是什么意思

云原生到底是什么意思? 引言 随着云计算技术的迅速发展,云原生成为了一个备受关注的话题。云原生不仅仅是一种新的软件架构,更是一种变革性的开发方法论。本文将深入解析云原生的意义、特点以及为什么它在现代软件开发中变得如此重要。 云…...

【银行测试】银行项目,信用卡业务测试+常问面试(三)

目录:导读 前言一、Python编程入门到精通二、接口自动化项目实战三、Web自动化项目实战四、App自动化项目实战五、一线大厂简历六、测试开发DevOps体系七、常用自动化测试工具八、JMeter性能测试九、总结(尾部小惊喜) 前言 银行测试-信用卡业…...

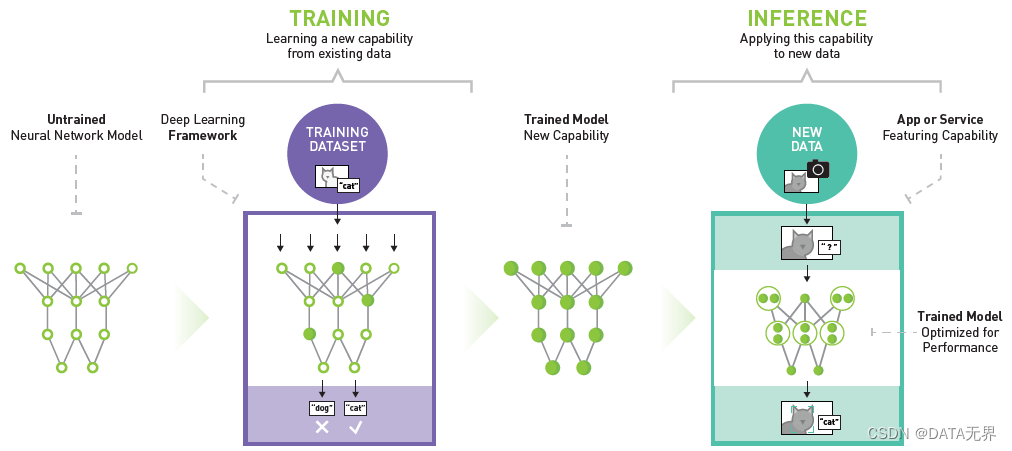

AI大模型学习笔记之二:什么是 AI 大模型的训练和推理?

在人工智能(AI)的领域中,我们经常听到训练(Training) 和 推理(Inference) 这两个词汇,它们是构建强大 AI 模型的关键步骤。我们通过类比人类的学习过程来理解这两个概念,可以更加自然而生动地理…...

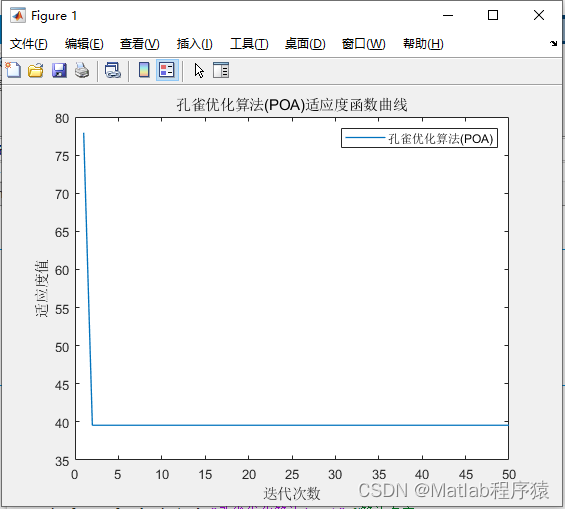

【MATLAB源码-第113期】基于matlab的孔雀优化算法(POA)机器人栅格路径规划,输出做短路径图和适应度曲线。

操作环境: MATLAB 2022a 1、算法描述 POA(孔雀优化算法)是一种基于孔雀羽毛开屏行为启发的优化算法。这种算法模仿孔雀通过展开其色彩斑斓的尾羽来吸引雌性的自然行为。在算法中,每个孔雀代表一个潜在的解决方案,而…...

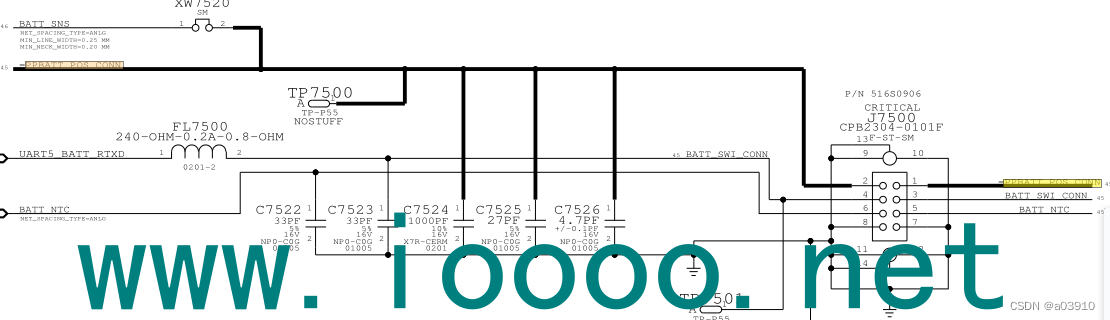

iphone 5s的充电时序原理图纸,iPAD充电讲解

上一篇写了iphone 5的时序。那是电池供电的开机时序。iphone 5s也是差不多的过程,不说了。现在看iphone5s手机充电时候的时序。iphone5s充电比iphone5充电简单了很多。 首先是usb接口接到手机上,usb线连接到J7接口上。J7接口不只是接usb,还能…...

react基础入门

1,了解react react并不是一个MVC框架,他只是一个很强大的javaScript库,主要作用是用来构建UI界面。 react的核心是封装一个个大大小小的组件(小到一个按钮,大到一个页面)来构建复杂的UI界面,每…...

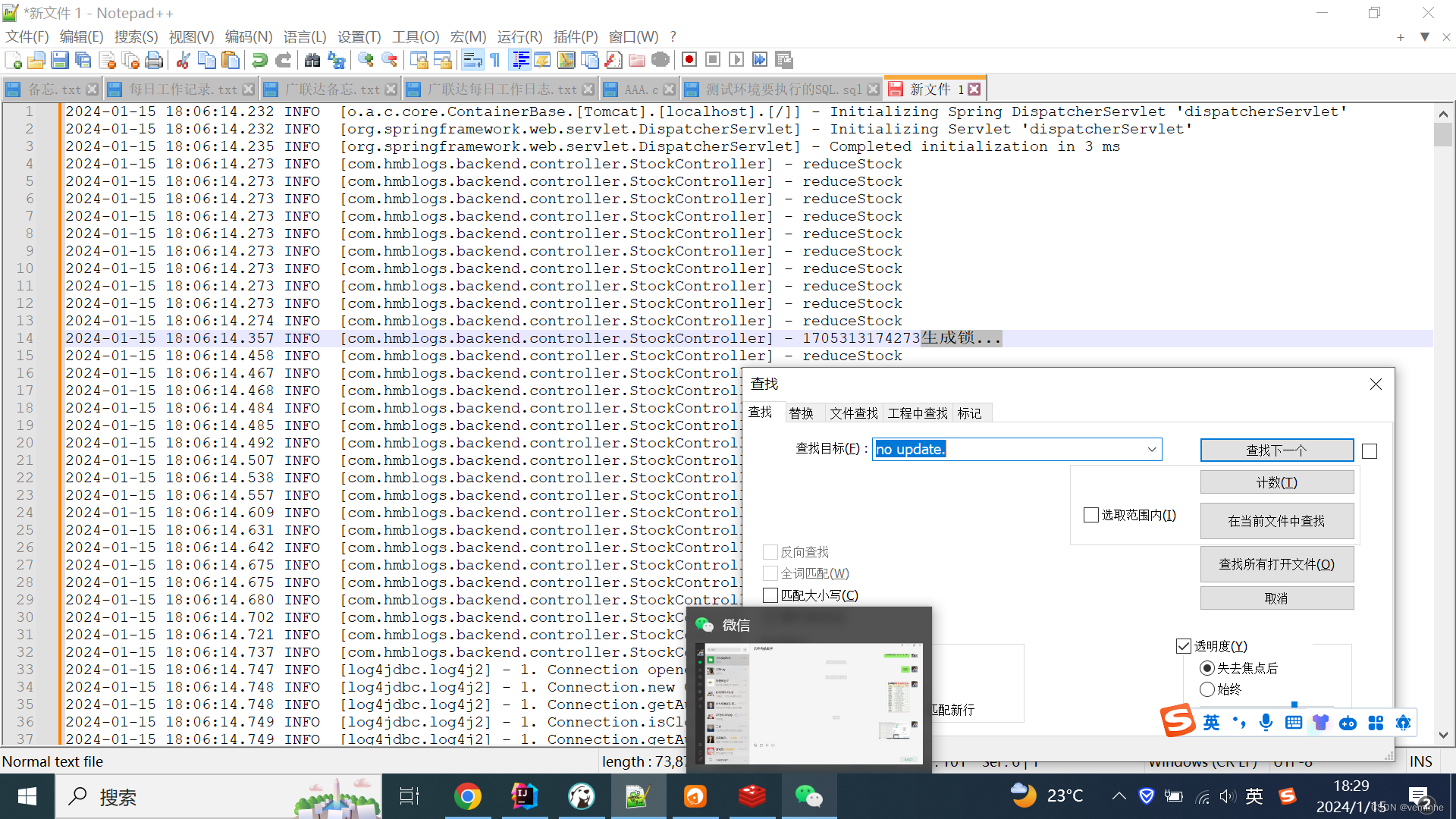

spring boot学习第八篇:通过spring boot、jedis实现秒单

参考:Redis实现分布式锁的7种方案 - 知乎 1、 准备数据库表,如下SQL表示库存表,有主键ID和库存数量字段 CREATE TABLE t_stock (id bigint(20) NOT NULL AUTO_INCREMENT,quantity bigint(20) NOT NULL,PRIMARY KEY (id) ) ENGINEInnoDB DEF…...

NineAi 新版AI系统网站源码 ChatGPT

简介: Nine AI.ChatGPT是基于ChatGPT开发的一个人工智能技术驱动的自然语言处理工具,它能够通过学习和理解人类的语言来进行对话,还能根据聊天的上下文进行互动,真正像人类一样来聊天交流,甚至能完成撰写邮件、视频脚本、文案、翻译、代码,写论文等任务。 NineAi 新版A…...

开源监控服务一瞥:Prometheus、Grafana、Zabbix、Nagios、Icinga和Open-Falcon

前言 随着信息技术的发展,监控服务在维护系统稳定性和性能方面变得越来越重要。本文将比较一些流行的开源监控服务,以帮助你选择适合你需求的解决方案。 监控服务对比 监控服务特点优势不足性能扩展性安全性Prometheus- 多维度数据模型- 监控容器化环…...

使用WAF防御网络上的隐蔽威胁之扫描器

在网络安全领域,扫描器是用于侦察和识别网络系统漏洞的工具。 它们可以帮助网络管理员识别安全漏洞,也可能被攻击者用来寻找攻击目标。 扫描器的基本概念 定义:扫描器是一种自动化工具,用于探测网络和服务器中的漏洞、开放端口、…...

企业信息安全管理制度

随着信息化程度的日益推进,企业信息的脆弱性也日益暴露。如何规范日趋复杂的信息安全保障体系建设,如何进行信息风险评估保护企业的信息资产不受侵害,已成为当前行业实现信息化运作亟待解决的问题。 一、企业的信息及其安全隐患 在我公司&am…...

深入解析dlopen:动态库加载的机制与实践

1. 动态库加载的两种方式 在C/C开发中,动态库(Dynamic Library)的使用是提升代码复用性和灵活性的重要手段。动态库加载主要分为隐式链接和显式链接两种方式,它们各有特点,适用于不同场景。 隐式链接是最常见的方式&am…...

解决打印机标签尺寸匹配问题

在开发应用程序时,经常会遇到与打印机相关的各种问题,尤其是当需要打印特定尺寸的标签时。如果您正在开发一个可以打印产品标签的应用,并且遇到标签尺寸不匹配的问题,那么本文将为您提供详细的解决方案。 问题背景 假设您正在与同事开发一个可以打印产品标签的应用。您需…...

Umi-OCR服务化集成方案:构建企业级OCR自动化工作流的技术实现

Umi-OCR服务化集成方案:构建企业级OCR自动化工作流的技术实现 【免费下载链接】Umi-OCR Umi-OCR: 这是一个免费、开源、可批量处理的离线OCR软件,适用于Windows系统,支持截图OCR、批量OCR、二维码识别等功能。 项目地址: https://gitcode.c…...

ILI9341 TFT驱动库:裸机SPI显示驱动设计与优化

1. SPI_TFT_ILI9341 库概述SPI_TFT_ILI9341 是一个面向嵌入式平台的轻量级图形驱动库,专为基于 ILI9341 显示控制器的 2.4 英寸、240320 分辨率 SPI 接口 TFT-LCD 模块设计。该库不依赖操作系统,可直接运行于裸机环境(Bare Metal)…...

HarmonyOS6 半年磨一剑 - RcCheckbox 组件事件体系与交互逻辑

文章目录前言一、点击处理链1.1 核心点击处理函数1.2 两个点击入口二、三事件分层设计2.1 三个事件的对比2.2 事件使用示例三、labelDisabled 局部禁止机制3.1 设计意图3.2 适用场景四、RcCheckboxGroup 的数量限制拦截4.1 min/max 拦截机制4.2 数量限制示例总结前言 一个看似…...

thermalmonitordDisabler:突破iOS性能枷锁的终极方案——彻底解决过热降频问题指南

thermalmonitordDisabler:突破iOS性能枷锁的终极方案——彻底解决过热降频问题指南 【免费下载链接】thermalmonitordDisabler A tool used to disable iOS daemons. 项目地址: https://gitcode.com/gh_mirrors/th/thermalmonitordDisabler 当你在直播过程中…...

从一道蓝桥杯EDA赛题,聊聊平衡车硬件设计中那些‘不起眼’却关键的安全电路

平衡车硬件设计中的安全电路:从蓝桥杯赛题到工程实战 去年调试一款平衡车原型机时,我曾遇到一个诡异现象:每次电池快耗尽时,电机就会突然失控。经过三天排查,最终发现问题出在电源检测电路的分压电阻取值上——这个看似…...

终极指南:Ledger会计系统数据备份与灾难恢复策略

终极指南:Ledger会计系统数据备份与灾难恢复策略 【免费下载链接】ledger Double-entry accounting system with a command-line reporting interface 项目地址: https://gitcode.com/gh_mirrors/le/ledger Ledger作为一款强大的复式记账系统,其核…...

如何创建自定义编程连字符号:Hasklig字体开发终极指南

如何创建自定义编程连字符号:Hasklig字体开发终极指南 【免费下载链接】Hasklig Hasklig - a code font with monospaced ligatures 项目地址: https://gitcode.com/gh_mirrors/ha/Hasklig Hasklig是一款专为程序员设计的等宽字体,它通过创新的连…...

YOLOv7-d2实例分割深度教程:SparseInst模型原理与实战

YOLOv7-d2实例分割深度教程:SparseInst模型原理与实战 【免费下载链接】yolov7_d2 🔥🔥🔥🔥 (Earlier YOLOv7 not official one) YOLO with Transformers and Instance Segmentation, with TensorRT acceleration! &am…...