使用 Verilog 做一个可编程数字延迟定时器 LS7211-7212

今天的项目是在 Verilog HDL 中实现可编程数字延迟定时器。完整呈现了延迟定时器的 Verilog 代码。

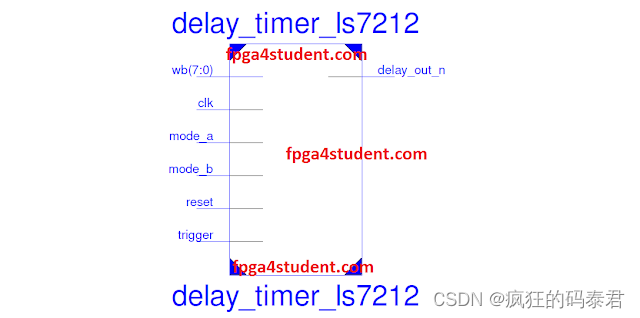

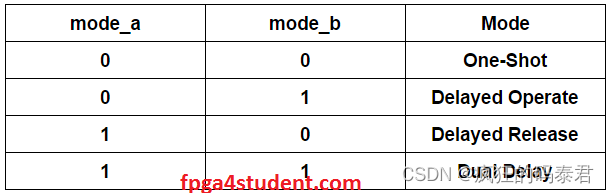

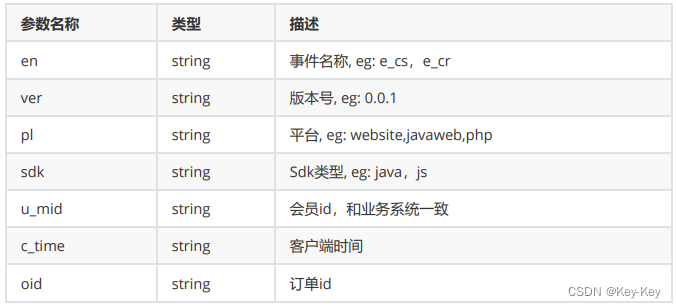

所实现的数字延迟定时器是 CMOS IC LS7212,用于生成可编程延迟。延迟定时器的规格可以在这里轻松找到。基本上,延迟定时器有 4 种操作模式:一次性 (OS)、延迟操作 (DO)、延迟释放 (DR)、双延迟 (DD)。这四种模式将通过输入 mode_a 和 mode_b 选择。

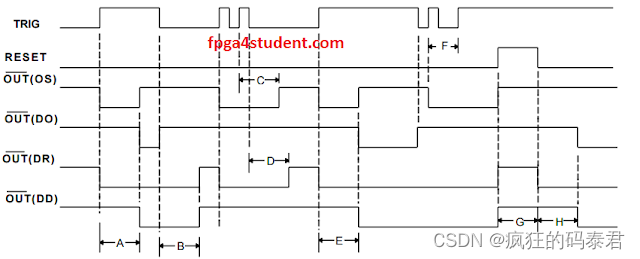

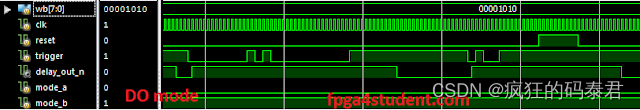

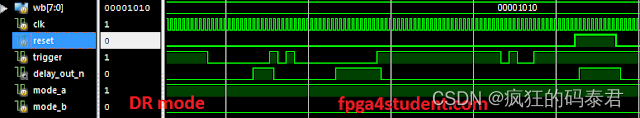

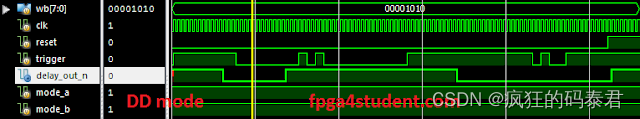

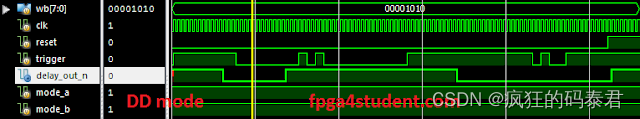

wb[7:0] 输入用于根据延迟定时器规范中给定的方程对延迟进行编程。要了解更多它在每种模式下的工作原理以及输入如何控制延迟,请参阅其数据表。以下波形显示了每种模式下延迟的产生方式。

以下是可编程数字延迟定时器 LS7212 的 Verilog 代码。

//fpga4student.com: FPga projects, Verilog projects, VHDL projects// Verilog project: Verilog code for delay timer LS7212 module delay_timer_ls7212 ( input [7:0] wb, // weighting bits input clk, // clock inputinput reset, // timer reset input trigger, // trigger input input mode_a, mode_b, // mode bits A and B output reg delay_out_n // delay output, active low ); reg[7:0] PULSE_WIDTH ; reg [7:0] DELAY; reg [7:0] TIMER=0; reg trigger_sync_1=0,trigger_sync_2=0; wire trigger_rising,trigger_falling; reg timer_start=0,out_low=0; wire timer_clear2,timer_clear3,timer_clear; reg [1:0] mode; reg reset_timer1=0,reset_timer2=0,reset_timer=0; wire reset_timer3,reset_det; reg reset_det1=0,reset_det2=0;

//fpga4student.com: FPga projects, Verilog projects, VHDL projectsalways @(posedge clk) begin trigger_sync_1 <= trigger; // the first Flip-Flop trigger_sync_2 <= trigger_sync_1;// the second Flip-Flop reset_timer1 <= reset_timer; reset_timer2 <= reset_timer1; reset_det1 <= reset; reset_det2 <= reset_det1; end // Identify the zero to one transitions on trigger signal assign trigger_rising = trigger_sync_1 & (~trigger_sync_2); assign trigger_falling = trigger_sync_2 & (~trigger_sync_1); assign reset_timer3 = reset_timer1 & (~reset_timer2); assign reset_det = reset_det2 & (~reset_det1); // sample Mode and wb always @(trigger_rising,trigger_falling,mode_a,mode_b,wb) begin if(trigger_falling == 1 || trigger_rising == 1) begin PULSE_WIDTH = wb; DELAY = (2*wb + 1)/2; mode = {mode_a,mode_b}; end end // modes always @(mode,reset,trigger_falling,trigger_rising,TIMER,reset,trigger,PULSE_WIDTH,DELAY,reset_det) begin case(mode) 2'b00: // One-Shot Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(trigger_rising==1) begin out_low <= 1; timer_start <= 1; reset_timer <= 1; end else if(TIMER>=PULSE_WIDTH) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end end 2'b01: // Delayed Operate Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(reset_det==1 && trigger==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_rising==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_falling==1 || trigger == 0) begin out_low <= 0; reset_timer <= 1; timer_start <= 0; end else if(TIMER >= DELAY) begin out_low <= 1; timer_start <= 0; reset_timer <= 1; end //else // reset_timer <= 0; end 2'b10: // Delayed Release Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(trigger_rising==1 || trigger == 1) begin out_low <= 1; end else if(trigger_falling==1 ) begin timer_start <= 1; reset_timer <= 0; end else if(TIMER>=DELAY) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end end 2'b11: // Delayed Dual Mode begin if(reset) begin out_low <= 0; timer_start <= 0; reset_timer <= 1; end else if(reset_det==1 && trigger==1) begin timer_start <= 1; reset_timer <= 0; end else if(trigger_falling==1 || trigger_rising==1 ) begin timer_start <= 1; reset_timer <= 0; end else if(TIMER>=DELAY) begin out_low <= trigger; timer_start <= 0; reset_timer <= 1; end end endcase end

//fpga4student.com: FPga projects, Verilog projects, VHDL projects// timer always @(posedge clk or posedge timer_clear) begin if(timer_clear) TIMER <= 0; else if(timer_start) TIMER <= TIMER + 1; end assign timer_clear = reset_timer3 | trigger_rising == 1 | timer_clear3 ; assign timer_clear2 = (trigger_rising == 1)|(trigger_falling == 1); assign timer_clear3 = timer_clear2 & (mode == 2'b11); //delay output always @(posedge clk) begin if(out_low == 1) delay_out_n <= 0; else delay_out_n <= 1; end endmodule

延迟定时器的 Testbench Verilog 代码:

`timescale 1ns / 1ps

//fpga4student.com: FPga projects, Verilog projects, VHDL projects

// Testbench Verilog code for delay timermodule tb_ls7212; // Inputs reg [7:0] wb; reg clk; reg reset; reg trigger; reg mode_a; reg mode_b; // Outputs wire delay_out_n; //fpga4student.com: FPga projects, Verilog projects, VHDL projects// Instantiate the Unit Under Test (UUT) delay_timer_ls7212 uut ( .wb(wb), .clk(clk), .reset(reset), .trigger(trigger), .mode_a(mode_a), .mode_b(mode_b), .delay_out_n(delay_out_n) ); initial begin // Initialize Inputs wb = 10; mode_a = 0; mode_b = 0; reset = 0; trigger = 0; #500; trigger = 1; #15000; trigger = 0; #15000; trigger = 1; #2000; trigger = 0; #2000; trigger = 1; #2000; trigger = 0; #20000; trigger = 1; #30000; trigger = 0; #2000; trigger = 1; #2000; trigger = 0; #4000; trigger = 1; #10000; reset = 1; #10000; reset = 0; // Delay Operate // Add stimulus here end initial begin clk = 0; forever #500 clk = ~clk; end endmodule

//fpga4student.com: FPga projects, Verilog projects, VHDL projects

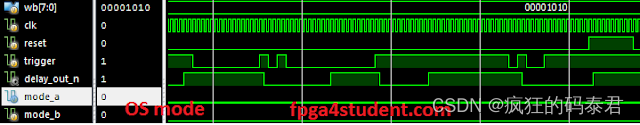

Verilog 中数字延迟定时器的仿真波形

One-Shot Mode

Delayed Operate Mode

Delayed Release Mode

Delay Dual Mode

可编程延迟定时器的 Verilog 代码是可综合的,并且可以在 FPGA 上实现。

相关文章:

使用 Verilog 做一个可编程数字延迟定时器 LS7211-7212

今天的项目是在 Verilog HDL 中实现可编程数字延迟定时器。完整呈现了延迟定时器的 Verilog 代码。 所实现的数字延迟定时器是 CMOS IC LS7212,用于生成可编程延迟。延迟定时器的规格可以在这里轻松找到。基本上,延迟定时器有 4 种操作模式:…...

戏说c语言文章汇总

c语言的起源GNU C和标准C第一篇: hello c!第二篇: 为什么需要编译第三篇: 当你运行./a.out时,发生了什么?第四篇: 简单的加法器第五篇: 两个正数相加竟然变成了负数!第六篇: 西西弗斯推石头(循环)第七篇: 九九乘法表(双循环)第八篇: 如果上天…...

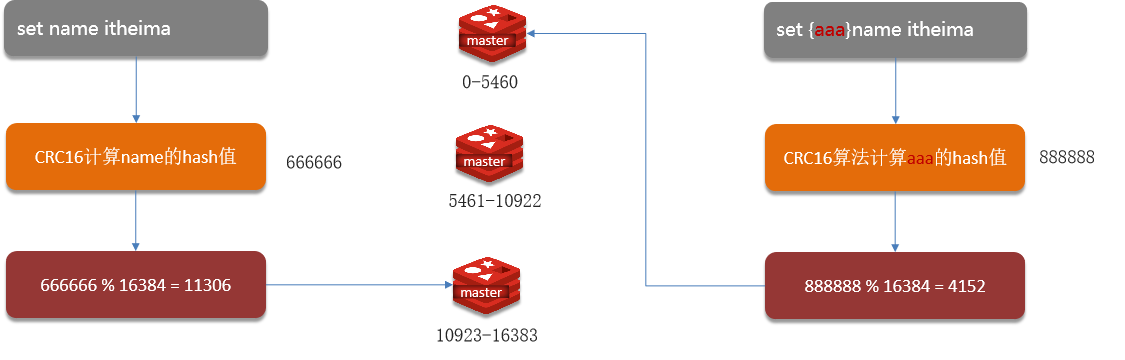

面试redis篇-12Redis集群方案-分片集群

原理 主从和哨兵可以解决高可用、高并发读的问题。但是依然有两个问题没有解决: 海量数据存储问题高并发写的问题 使用分片集群可以解决上述问题,分片集群特征: 集群中有多个master,每个master保存不同数据每个master都可以有…...

【Java EE初阶二十三】servlet的简单理解

1. 初识servlet Servlet 是一个比较古老的编写网站的方式,早起Java 编写网站,主要使用 Servlet 的方式,后来 Java 中产生了一个Spring(一套框架),Spring 又是针对 Servlet 进行了进一步封装,从而让我们编写网站变的更简单了;Sprin…...

c++ http操作接口

很简单的使用libcurl来操作http与服务器来通讯,包含http与https,对外只开放 #include "request.h" #include "response.h" #include "url.h" 三个头文件,简单易用,使用的实例如下: vo…...

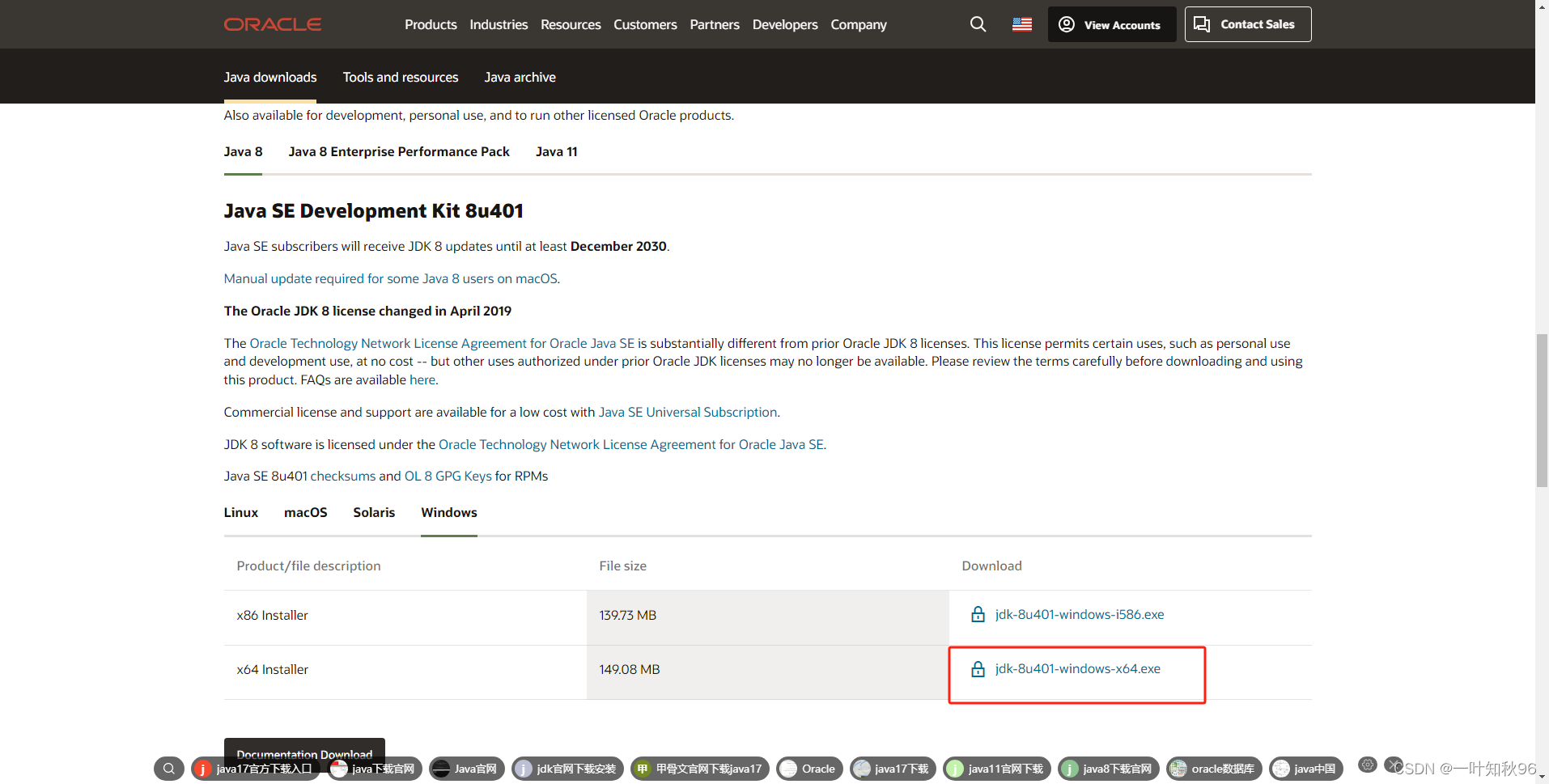

oracle官网下载早期jdk版本

Java Downloads | Oracle JDK Builds from Oracle 以上压缩版,以下安装版 Java Downloads | Oracle 该链接往下拉能看到jdk8和jdk11的安装版 -- end...

Python爬虫实战:图片爬取与保存

引言: 在本文中,我们将学习如何使用Python创建一个简单的图片爬虫。 我们将利用requests库来发送HTTP请求,BeautifulSoup库来解析HTML页面,以及os和shutil库来下载和保存图片。通过这个教程,你将学会如何爬取网…...

CMS垃圾回收器

CMS垃圾回收 CMS GC的官方名称为“Mostly Concurrenct Mark and Sweep Garbage Collector”(最大-并发-标记-清除-垃圾收集器)。 作用范围: 老年代 算法: 并发标记清除算法。 启用参数:-XX:UseConMarkSweepGC 默认回收…...

【力扣白嫖日记】184.部门工资最高的员工

前言 练习sql语句,所有题目来自于力扣(https://leetcode.cn/problemset/database/)的免费数据库练习题。 今日题目: 184.部门工资最高的员工 表:Employee 列名类型idintnamevarcharsalaryvarchardepartmentIdint …...

JAVA讲解算法-排序算法-选择排序算法-02

一、定义 选择排序法是一种不稳定的排序算法。它的工作原理是每一次从待排序的数据元素中选出最小(或最大)的一个元素,存放在序列的起始位置,然后,再从剩余未排序元素中继续寻找最小(大)元素&a…...

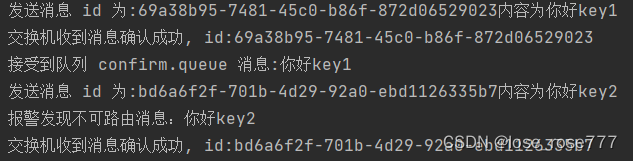

【初始RabbitMQ】高级发布确认的实现

在生产环境中由于一些不明原因,导致 rabbitmq 重启,在 RabbitMQ 重启期间生产者消息投递失败, 导致消息丢失,需要手动处理和恢复。于是,我们开始思考,如何才能进行 RabbitMQ 的消息可靠投递呢? …...

用39块钱的全志V851se视觉开发板做了个小相机,还可以物品识别、自动追焦!

用39块钱的V851se视觉开发板做了个小相机。 可以进行物品识别、自动追焦! 这个超低成本的小相机是在V851se上移植使用全志在线开源版本的Tina Linux与OpenCV框架开启摄像头拍照捕获视频,并结合NPU实现Mobilenet v2目标分类识别以及运动追踪等功能…并最终…...

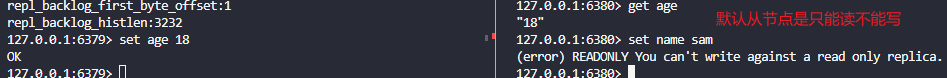

主从复制实现Redis集群

主从复制实现Redis集群实验 (一主二从): 实验环境: 使用Docker 搭建 Redis 版本 5.0.5 打开一个终端窗口,在其中运行如下命令创建一个名为redis-master的Redis容器。注意,它的端口是6379 (本地的端口:映射到容器的端口) docker run -itd--name redis-m…...

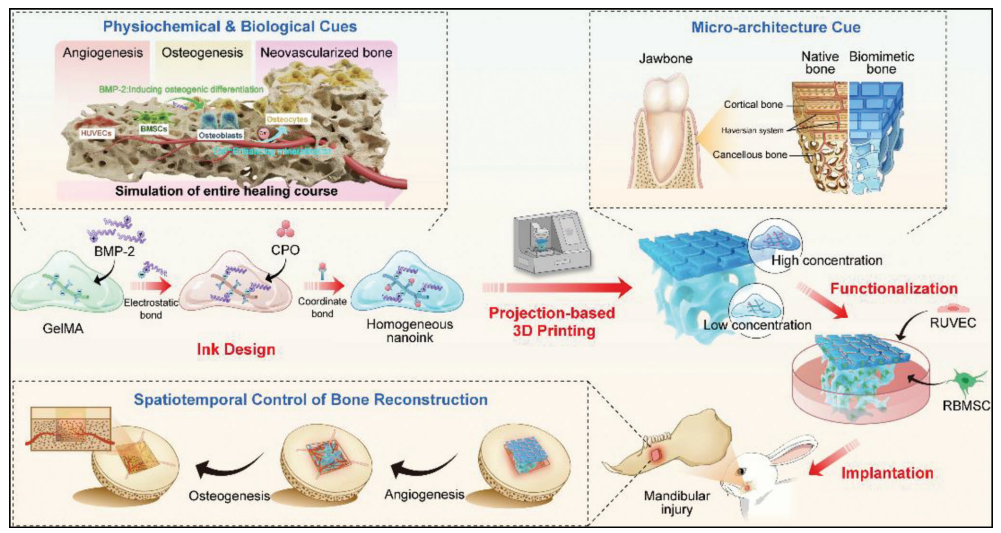

高分文献解读|3D打印骨支架实现梯度密度颌骨功能性重建

近月,浙江大学医学院附属口腔医院谢志坚教授团队与浙江大学化学系唐睿康教授团队、机械工程学院贺永教授团队合作,在期刊《Advanced Functional Materials》(IF19)上发表题为“A Hierarchical 3D Graft Printed with Nanoink for …...

大型电商日志离线分析系统(一)

一、项目需求分析 某大型网站日志离线分析系统 1.1 概述 该部分的主要目标就是描述本次项目最终七个分析模块的页面展示。 1.2 工作流 在我们的demo展示中,我们使用jqueryecharts的方式调用程序后台提供的rest api接口,获取json数据,然后…...

FL Studio Fruity Edition2024中文入门版Win/Mac

FL Studio Fruity Edition2024是一款功能强大的音乐制作软件,适合初学者和音乐爱好者使用。它提供了丰富的音乐制作工具,包括音频录制、编辑、混音以及MIDI制作等功能,帮助用户轻松创作出动人的音乐作品。 FL Studio 21.2.3 Win-安装包下载如…...

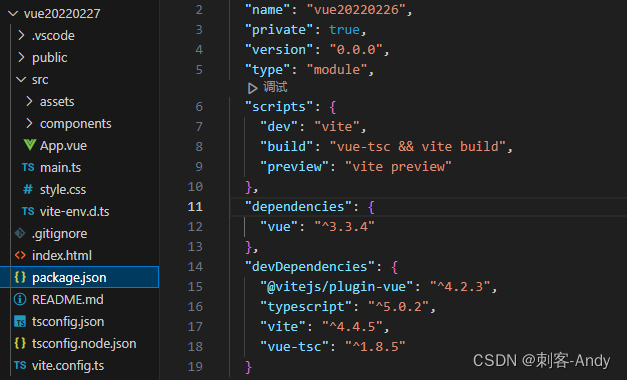

学习vue3第二节(使用vite 创建vue3项目)

使用vite 创建vue3项目 node 安装请移步 node官网: https://nodejs.p2hp.com/ node 版本控制 请移步 nvm官网:https://nvm.uihtm.com/ vite 生成vue项目完整版 请移步 vite官网:https://cn.vitejs.dev/ 1、使用 npm 或者 yarn 创建vue3 项目…...

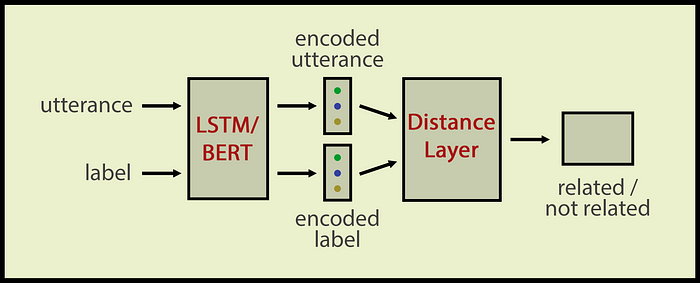

基于Siamese网络的zero-shot意图分类

原文地址:Zero-Shot Intent Classification with Siamese Networks 通过零样本意图分类有效定位域外意图 2021 年 9 月 24 日 意图识别是面向目标对话系统的一项重要任务。意图识别(有时也称为意图检测)是使用标签对每个用户话语进行分类的任务,该标签…...

Java架构师之路五、微服务:微服务架构、服务注册与发现、服务治理、服务监控、容器化等。

目录 微服务架构: 服务注册与发现: 服务治理: 服务监控: 容器化: 上篇:Java架构师之路四、分布式系统:分布式架构、分布式数据存储、分布式事务、分布式锁、分布式缓存、分布式消息中间件、…...

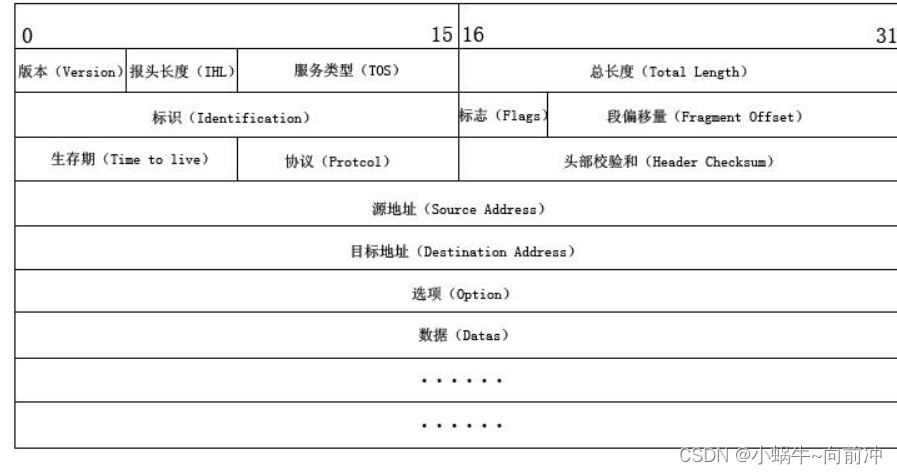

[计算机网络]--IP协议

前言 作者:小蜗牛向前冲 名言:我可以接受失败,但我不能接受放弃 如果觉的博主的文章还不错的话,还请点赞,收藏,关注👀支持博主。如果发现有问题的地方欢迎❀大家在评论区指正 目录 一、IP协议…...

LabVIEW 强度图与强度图表

LabVIEW 中强度图(Intensity Graph)与强度图表(Intensity Chart)均可接收二维数组作为输入,用于二维数据色彩可视化,二者核心差异体现在前面板运行行为上。强度图单次刷新、仅显示当前一组数据࿰…...

治愈不内卷!星露谷物语v1.6.15,承包你的所有温柔时光

如果你被快节奏的生活压得喘不过气,被内耗裹挟得身心俱疲,那一定要试试《星露谷物语》v1.6.15版本——这款Steam好评率98%的治愈神作,用一方小小农场,给你一个逃离喧嚣的精神避风港。 今天,就有免费的pc资源࿱…...

)

别再看枯燥的代码了!用这组超萌的Python图解,3天搞定基础语法(附速查表)

别再看枯燥的代码了!用这组超萌的Python图解,3天搞定基础语法(附速查表) 第一次打开Python教程时,你是不是也被满屏的def、class和缩进符号劝退?作为过来人,我完全理解那种面对抽象符号时的茫然…...

从智能窗户到海水淡化:拆解《Solar Energy Materials and Solar Cells》里的那些“跨界”太阳能技术

太阳能技术的跨界革命:从建筑节能到淡水获取的创新路径 清晨的阳光透过智能窗户自动调节室内亮度,海水在太阳能装置中悄然转化为清洁淡水——这些看似科幻的场景,正通过材料科学的突破逐步成为现实。在能源转型的全球背景下,太阳能…...

Qwen3字幕系统保姆级教程:清音刻墨Web端上传/分析/导出详解

Qwen3字幕系统保姆级教程:清音刻墨Web端上传/分析/导出详解 1. 什么是清音刻墨字幕系统 清音刻墨是一款基于通义千问Qwen3-ForcedAligner核心技术的智能字幕生成平台。它能将音频或视频中的语音内容,精确地转换成带有时间轴的字幕文件。 想象一下这样…...

如何快速解密Wii U游戏文件:CDecrypt终极指南

如何快速解密Wii U游戏文件:CDecrypt终极指南 【免费下载链接】cdecrypt Decrypt Wii U NUS content — Forked from: https://code.google.com/archive/p/cdecrypt/ 项目地址: https://gitcode.com/gh_mirrors/cd/cdecrypt 还在为无法访问Wii U游戏文件而烦…...

YOLO12开源大模型:支持ONNX/Triton导出适配生产推理引擎

YOLO12开源大模型:支持ONNX/Triton导出适配生产推理引擎 1. YOLO12模型概述 YOLO12是2025年最新发布的目标检测模型,由美国纽约州立大学布法罗分校和中国科学院大学联合研发。这个模型带来了革命性的突破——采用了以注意力为中心的架构,在…...

)

别再只盯着众测了!我是如何用FOFA和爱企查,挖到4张CNVD证书的(附完整资产筛选脚本思路)

资产猎人的精准撒网术:从海量数据中筛选高价值漏洞目标 在漏洞挖掘的世界里,最令人沮丧的莫过于花费数周时间研究一个系统,最终却发现目标公司根本不满足CNVD证书的发放条件。我曾经历过无数次这样的挫败,直到开发出一套系统化的…...

终极指南:如何让Mac鼠标滚轮像触控板一样丝滑滚动

终极指南:如何让Mac鼠标滚轮像触控板一样丝滑滚动 【免费下载链接】Mos 一个用于在 macOS 上平滑你的鼠标滚动效果或单独设置滚动方向的小工具, 让你的滚轮爽如触控板 | A lightweight tool used to smooth scrolling and set scroll direction independently for y…...

Windows窗口置顶终极指南:用PinWin告别频繁切换的烦恼![特殊字符]

Windows窗口置顶终极指南:用PinWin告别频繁切换的烦恼!🎯 【免费下载链接】PinWin Pin any window to be always on top of the screen 项目地址: https://gitcode.com/gh_mirrors/pin/PinWin 你是否曾经在写代码时频繁切换窗口查看文…...