Intel FPGA (1):线性序列机

Intel FPGA (1):线性序列机

前提摘要

-

个人说明:

- 限于时间紧迫以及作者水平有限,本文错误、疏漏之处恐不在少数,恳请读者批评指正。意见请留言或者发送邮件至:“Email:noahpanzzz@gmail.com”。

- 本博客的工程文件均存放在:GitHub:https://github.com/panziping。

- 本博客的地址:CSDN:https://blog.csdn.net/ZipingPan。

-

参考:

- 芯片型号:Intel EP4CE10F17C8(Cyclone IV E)

- 《数字电子技术基础》-阎石

- 《FPGA自学笔记—设计与验证》袁玉卓,曾凯锋,梅雪松

- 《Verilog 数字系统设计教程》夏宇闻

- 《Verilog HDL 高级数字设计》Michael D.Ciletti

- 《Intel FPGA/CPLD设计》(基础篇)王欣 王江宏等

- 《Intel FPGA/CPLD设计》(高级篇)王江宏 蔡海宁等

- 《综合与时序分析的设计约束 Synopsys设计约束(SDC)实用指南》Sridhar Gangadharan

-

日期:

- 2024-01-01

正文

点亮LED灯

硬件资源

由原理图可知,FPGA的IO口输出低电平,则LED点亮。

程序编写

module led_test(led

);output led;assign led = 1'b0;endmodule

点亮LED灯进阶

将LED点亮200ms,熄灭800ms。

程序编写

module led_test(clk,rst_n,led

);input clk;input rst_n;output reg led;reg [27:0] r_led_cnt;localparam LED_CNT_MAX = 28'd50_000_000;localparam LED_CNT_TURN = 28'd40_000_000;always@(posedge clk or negedge rst_n) beginif(!rst_n)r_led_cnt <= 'd0;else if(r_led_cnt == LED_CNT_MAX-1)r_led_cnt <= 'd0;elser_led_cnt <= r_led_cnt + 1'd1;endalways@(posedge clk or negedge rst_n) beginif(!rst_n)led <= 1'd1;else if(r_led_cnt == LED_CNT_TURN-1)led <= 1'd0;else if(r_led_cnt == LED_CNT_MAX-1)led <= 1'd1;elseled <= led;endendmodule

波形图

由上述实验可以发现,通过计数器可以产生一个占空比不是50%的周期信号。那么是不是由此可以引申,通过计数器对时钟计数,产生一串带有数字信息的信号。

线性序列机(LSM)

产生一段信号,包含的内容为11011010,每个码元所占用的时间为50us。

module tx_test(clk,rst_n,tx

);input clk;input rst_n;output reg tx;reg [15:0] r_tim_cnt;localparam TIM_CNT_MAX = 16'd20_000;localparam DATA0 = 16'd2_500;localparam DATA1 = 16'd5_000;localparam DATA2 = 16'd7_500;localparam DATA3 = 16'd10_000;localparam DATA4 = 16'd12_500;localparam DATA5 = 16'd15_000;localparam DATA6 = 16'd17_500;localparam DATA7 = 16'd20_000;always@(posedge clk or negedge rst_n) beginif(!rst_n)r_tim_cnt <= 'd0;else if(r_tim_cnt == TIM_CNT_MAX-1)r_tim_cnt <= 'd0;elser_tim_cnt <= r_tim_cnt + 1'd1;endalways@(posedge clk or negedge rst_n) beginif(!rst_n)tx <= 1'd1;else if(r_tim_cnt == DATA0 - 1'd1)tx <= 1'd0;else if(r_tim_cnt == DATA1 - 1'd1)tx <= 1'd1;else if(r_tim_cnt == DATA2 - 1'd1)tx <= 1'd0;else if(r_tim_cnt == DATA3 - 1'd1)tx <= 1'd1;else if(r_tim_cnt == DATA4 - 1'd1)tx <= 1'd1;else if(r_tim_cnt == DATA5 - 1'd1)tx <= 1'd0;else if(r_tim_cnt == DATA6 - 1'd1)tx <= 1'd1;else if(r_tim_cnt == DATA7 - 1'd1)tx <= 1'd1;else tx <= tx;end// always@(posedge clk or negedge rst_n) begin

// if(!rst_n)

// tx <= 1'd1;

// else

// case(r_tim_cnt)

// DATA0-1'd1: tx <= 1'd0;

// DATA1-1'd1: tx <= 1'd1;

// DATA2-1'd1: tx <= 1'd0;

// DATA3-1'd1: tx <= 1'd1;

// DATA4-1'd1: tx <= 1'd1;

// DATA5-1'd1: tx <= 1'd0;

// DATA6-1'd1: tx <= 1'd1;

// DATA7-1'd1: tx <= 1'd1;

// default:tx <= tx;

// endcase

// end

// endmodule

波形图

由上述实验可以发现,通过线性序列机产生了8bits(11011010)的信号。那么是不是对于串行信号都可以通过线性序列机进行输出。

数码管驱动

上述是线性序列机(LSM)的简单应用。

这一部分展示线性序列机应用在数码管驱动电路中(完整请见(Intel FPGA (3):数码管显示)),需要通过线性序列机产生三个信号seg_sclk(sh_cp),seg_rclk(st_cp),seg_dio(ds)。

波形图

程序编写

module hc595_driver(clk,rst_n,seg_data,seg_data_valid_go,seg_sclk,seg_rclk,seg_dio

);input clk;input rst_n;input [15:0] seg_data;input seg_data_valid_go;output reg seg_sclk;output reg seg_rclk;output reg seg_dio;reg [15:0] r_seg_data;always@(posedge clk or negedge rst_n) beginif(!rst_n)r_seg_data <= 'd0;else if(seg_data_valid_go == 1'b1)r_seg_data <= seg_data;elser_seg_data <= r_seg_data;endlocalparam DIV_CNT_MAX = 4; //fsh_cp = 6.25MHzreg [2:0] r_div_cnt;always@(posedge clk or negedge rst_n) beginif(!rst_n)r_div_cnt <= 'd0;else if(r_div_cnt == DIV_CNT_MAX -1)r_div_cnt <= 'd0;else r_div_cnt <= r_div_cnt + 1'b1;endwire w_sclk_pluse; //SH_CPassign w_sclk_pluse = (r_div_cnt == DIV_CNT_MAX -1) ? 1'b1 :1'b0;reg [4:0] r_sclk_edge_cnt; //SH_CPalways@(posedge clk or negedge rst_n) beginif(!rst_n)r_sclk_edge_cnt <= 'd0;else if(w_sclk_pluse == 1'b1)if(r_sclk_edge_cnt == 5'd31)r_sclk_edge_cnt <= 'd0;elser_sclk_edge_cnt <= r_sclk_edge_cnt + 1'd1;elser_sclk_edge_cnt <= r_sclk_edge_cnt;endalways@(posedge clk or negedge rst_n) beginif(!rst_n) beginseg_sclk <= 1'd0;seg_rclk <= 1'd0;seg_dio <= 1'd0;endelse begincase(r_sclk_edge_cnt)5'd0 : begin seg_sclk = 1'b0; seg_rclk = 1'b1; seg_dio = r_seg_data[15]; end //Q2H(HEX_DP)5'd1 : begin seg_sclk = 1'b1; seg_rclk = 1'b0; end 5'd2 : begin seg_sclk = 1'b0; seg_dio = r_seg_data[14]; end //Q2G(HEX_G)5'd3 : begin seg_sclk = 1'b1; end5'd4 : begin seg_sclk = 1'b0; seg_dio = r_seg_data[13]; end //Q2F(HEX_F)5'd5 : begin seg_sclk = 1'b1; end5'd6 : begin seg_sclk = 1'b0; seg_dio = r_seg_data[12]; end //Q2E(HEX_E)5'd7 : begin seg_sclk = 1'b1; end5'd8 : begin seg_sclk = 1'b0; seg_dio = r_seg_data[11]; end //Q2D(HEX_D) 5'd9 : begin seg_sclk = 1'b1; end5'd10: begin seg_sclk = 1'b0; seg_dio = r_seg_data[10]; end //Q2C(HEX_C) 5'd11: begin seg_sclk = 1'b1; end5'd12: begin seg_sclk = 1'b0; seg_dio = r_seg_data[9]; end //Q2B(HEX_B) 5'd13: begin seg_sclk = 1'b1; end5'd14: begin seg_sclk = 1'b0; seg_dio = r_seg_data[8]; end //Q2A(HEX_A)5'd15: begin seg_sclk = 1'b1; end5'd16: begin seg_sclk = 1'b0; seg_dio = r_seg_data[7]; end //Q1H(HEX_SEL7) 5'd17: begin seg_sclk = 1'b1; end5'd18: begin seg_sclk = 1'b0; seg_dio = r_seg_data[6]; end //Q1G(HEX_SEL6)5'd19: begin seg_sclk = 1'b1; end5'd20: begin seg_sclk = 1'b0; seg_dio = r_seg_data[5]; end //Q1F(HEX_SEL5)5'd21: begin seg_sclk = 1'b1; end5'd22: begin seg_sclk = 1'b0; seg_dio = r_seg_data[4]; end //Q1E(HEX_SEL4) 5'd23: begin seg_sclk = 1'b1; end5'd24: begin seg_sclk = 1'b0; seg_dio = r_seg_data[3]; end //Q1D(HEX_SEL3) 5'd25: begin seg_sclk = 1'b1; end5'd26: begin seg_sclk = 1'b0; seg_dio = r_seg_data[2]; end //Q1C(HEX_SEL2) 5'd27: begin seg_sclk = 1'b1; end5'd28: begin seg_sclk = 1'b0; seg_dio = r_seg_data[1]; end //Q1B(HEX_SEL1) 5'd29: begin seg_sclk = 1'b1; end5'd30: begin seg_sclk = 1'b0; seg_dio = r_seg_data[0]; end //Q1A(HEX_SEL0)5'd31: begin seg_sclk = 1'b1; enddefault:;endcaseendendendmodule

总结

线性序列机可以画出任意波形的数字信号!常用作为最低层RTL设计。

本文均为原创,欢迎转载,请注明文章出处:CSDN:https://blog.csdn.net/ZipingPan。百度和各类采集站皆不可信,搜索请谨慎鉴别。技术类文章一般都有时效性,本人习惯不定期对自己的博文进行修正和更新,因此请访问出处以查看本文的最新版本。

非原创博客会在文末标注出处,由于时效原因,可能并不是原创作者地址(已经无法溯源)。

相关文章:

Intel FPGA (1):线性序列机

Intel FPGA (1):线性序列机 前提摘要 个人说明: 限于时间紧迫以及作者水平有限,本文错误、疏漏之处恐不在少数,恳请读者批评指正。意见请留言或者发送邮件至:“Email:noahpanzzzgmail.com”。本博客的工程文件均存放在…...

翻译: 硅谷软件工程师面试:准备所需的一切

没有人有时间去做成百上千道LeetCode题目,好消息是你实际上并不需要做那么多题目就能够在FAANG公司找到工作! 我曾经在Grab工作,这是东南亚的一家共享出行公司,但我对工作感到沮丧,想要进入FAANG公司,但我…...

视频推拉流EasyDSS点播平台云端录像播放异常的问题排查与解决

视频推拉流EasyDSS视频直播点播平台可提供一站式的视频转码、点播、直播、视频推拉流、播放H.265视频等服务,搭配RTMP高清摄像头使用,可将无人机设备的实时流推送到平台上,实现无人机视频推流直播、巡检等应用。 有用户反馈,项目现…...

kubuntu23.10安装sdl2及附加库和 sfml2.5.1

2024年3月28号,四,晚上kubuntu23.10下安装了sdl2的如下,没有安装gfx。 sudo apt install libsdl2-dev sudo apt install libsdl2-image-dev sudo apt install libsdl2-ttf-dev sudo apt install libsdl2-mixer-dev sudo apt install libsdl2…...

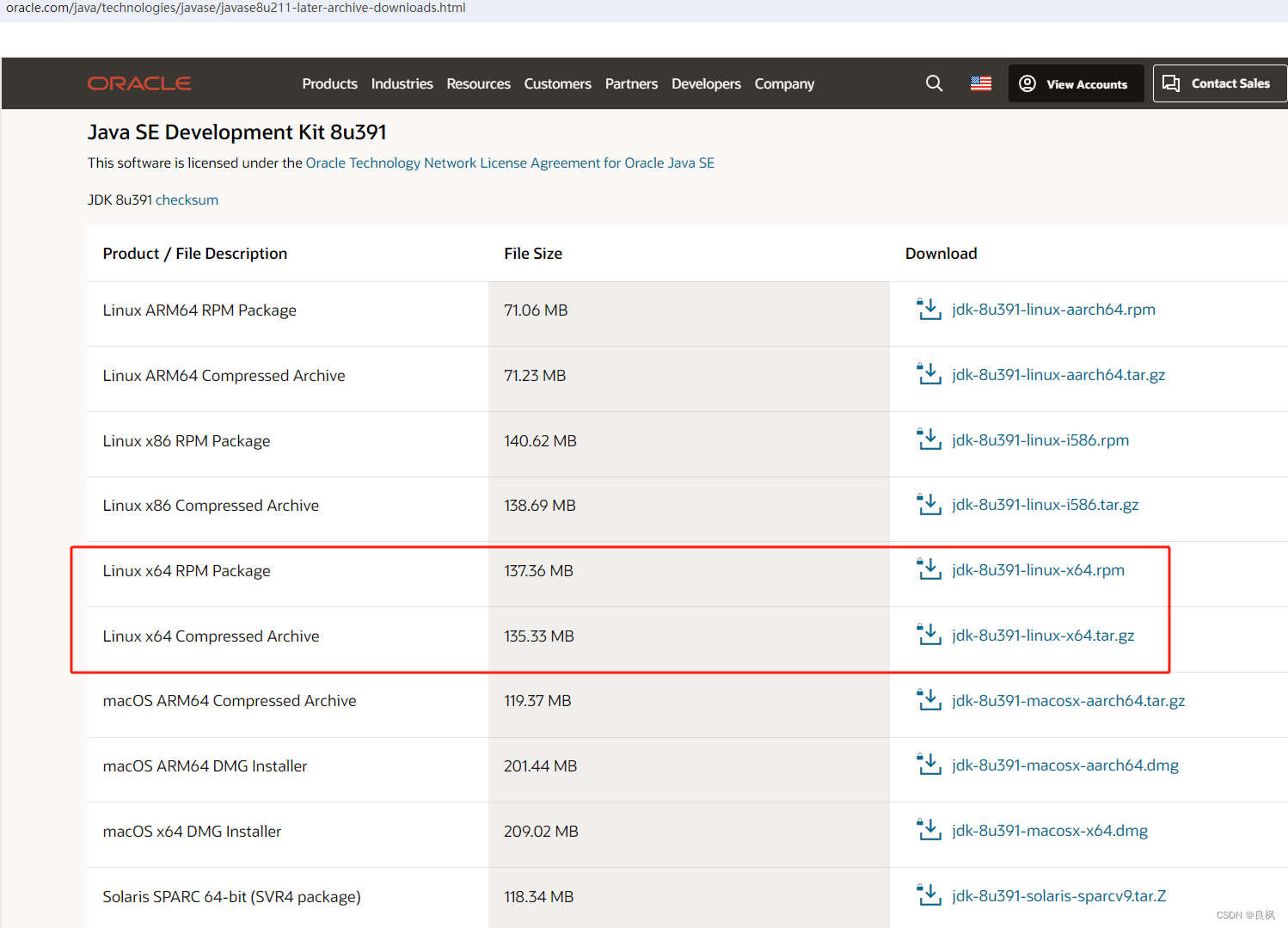

Centos JDK1.8 下载安装

https://www.oracle.com/java/technologies/javase/javase8u211-later-archive-downloads.html 一 RPM包安装 rpm -ivh jdk-8u391-linux-x64.rpm /etc/profile export JAVA_HOME/usr/java/jdk1.8.0-x64 export PATH$JAVA_HOME/bin:$PATHsource /etc/profile二 tar.gz 包手动…...

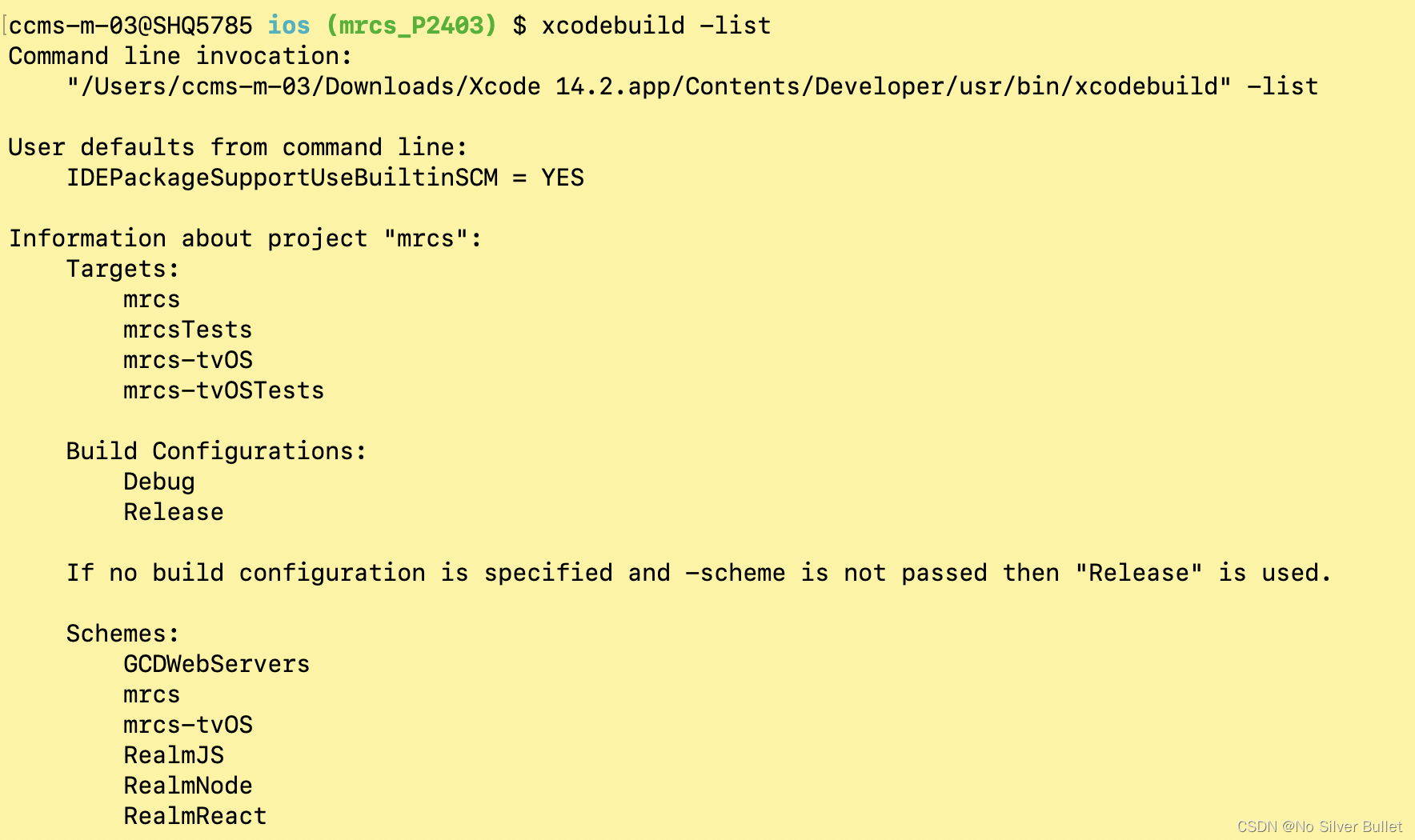

iOS开发进阶(十四):xcodebuild 命令应用详解

文章目录 一、前言二、xcodebuild 命令汇总三、xcodebuild 可选命令四、exportOptionsPlist文件内容配置说明五、项目实操六、拓展阅读 一、前言 关于iOS组包,详参博文《ReactNative进阶(三十四):Jenkins 流水线 组包 iOS 应用包…...

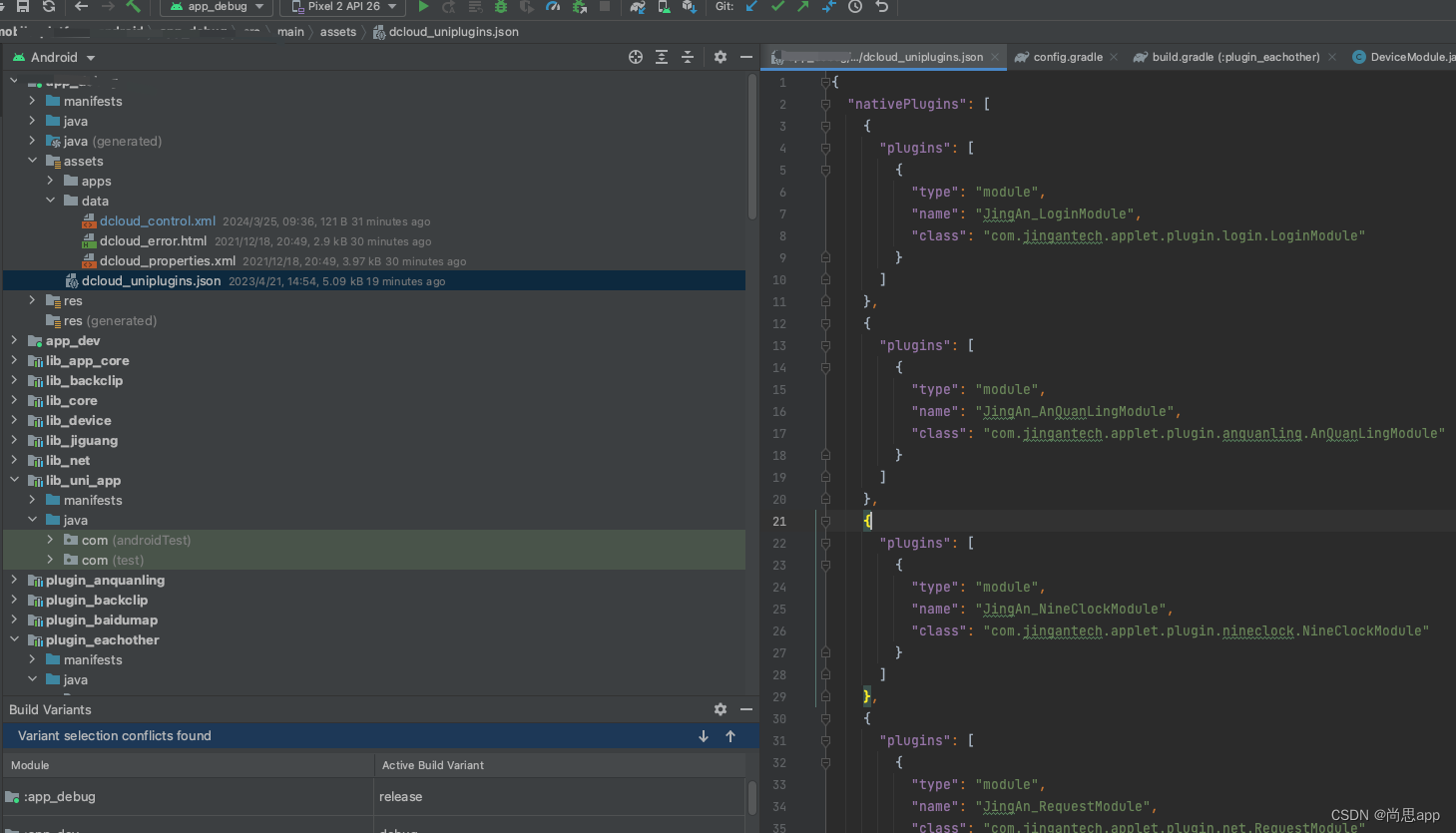

uniapp 开发之原生Android插件

开发须知 在您阅读此文档时,我们假定您已经具备了相应Android应用开发经验,使用Android Studio开发过Android原生。也应该对HTML,JavaScript,CSS等有一定的了解, 并且熟悉在JavaScript和JAVA环境下的JSON格式数据操作等。 为了插件开发者更方便快捷的开…...

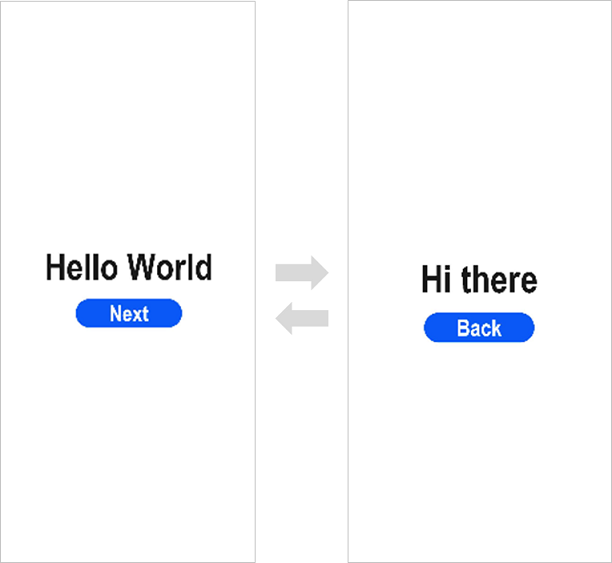

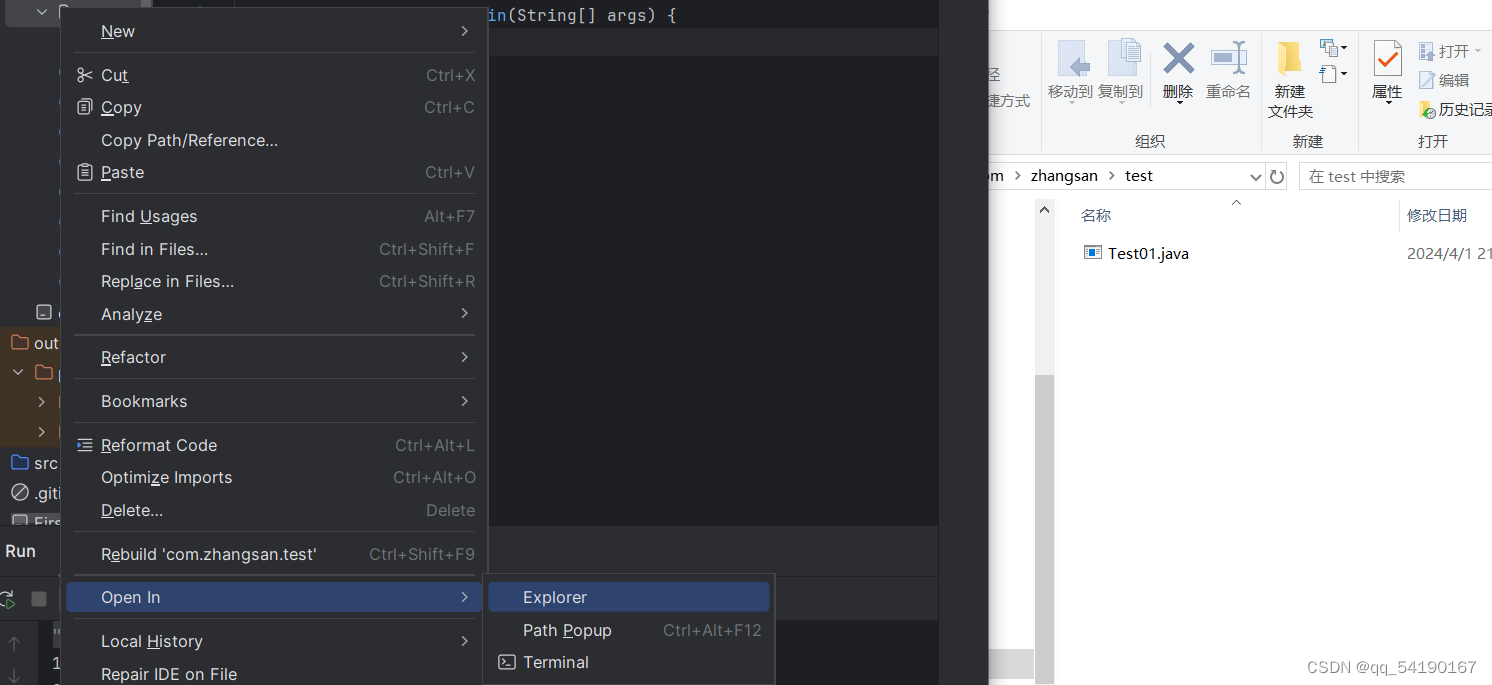

构建第一个JS应用(FA模型)

创建JS工程 若首次打开DevEco Studio,请点击Create Project创建工程。如果已经打开了一个工程,请在菜单栏选择File > New > Create Project来创建一个新工程。选择Application应用开发(本文以应用开发为例,Atomic Service对…...

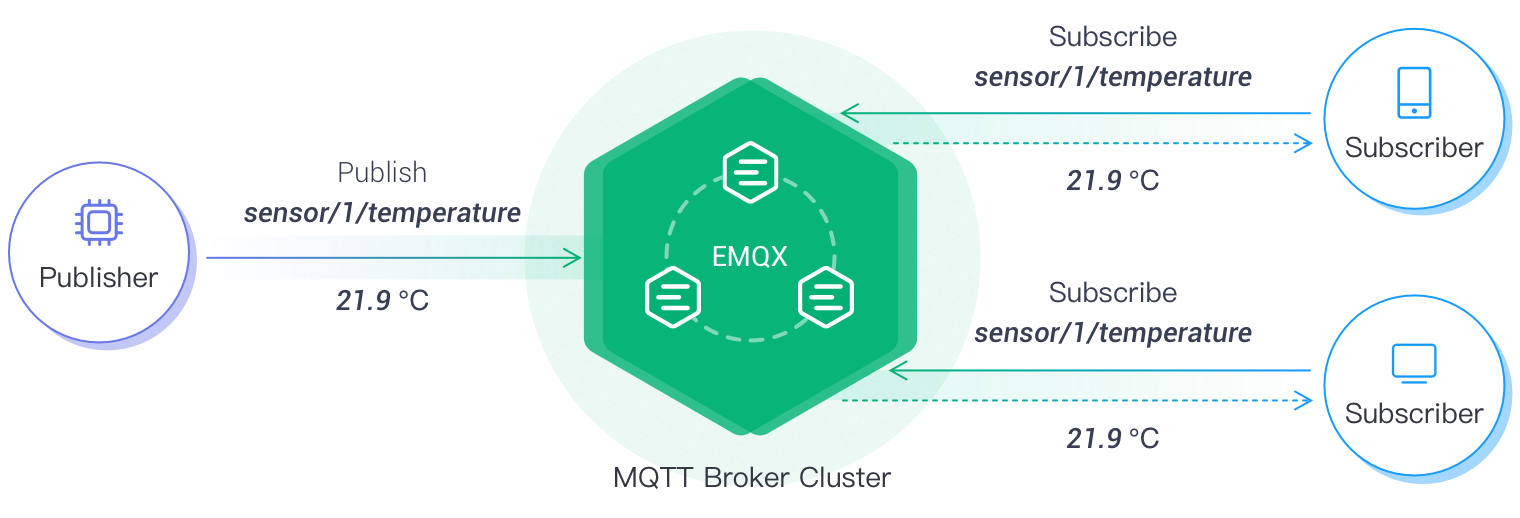

物联网学习2、MQTT 发布/订阅模式介绍

MQTT 发布/订阅模式 发布订阅模式(Publish-Subscribe Pattern)是一种消息传递模式,它将发送消息的客户端(发布者)与接收消息的客户端(订阅者)解耦,使得两者不需要建立直接的联系也不…...

docker--部署 (超详版) (五)

环境准备:docker,mysql,redis,镜像,nginx 把虚拟机打开,连接xshell,参考博客: https://blog.csdn.net/m0_74229802/article/details/136965820?spm1001.2014.3001.5501 一&#x…...

谷粒商城——通过接口幂等性防止重复提交订单

如果用户向后端服务提交多次相同订单的提交服务,那么后端应该只生成一条订单记录。 有一些操作天然是幂等的,如查询操作和删除操作等。 幂等性实现 1.token机制(仅这个方法适用于订单的重复提交) 后端先生成1个令牌将其记录在R…...

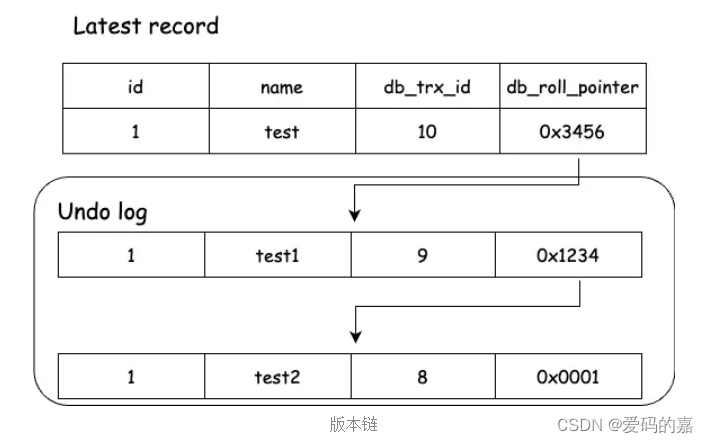

谈谈MVCC机制

在MySQL中,MVCC(多版本并发控制)是InnoDB存储引擎使用的并发控制机制。它提供对数据的并发访问,并确保多用户环境中数据的一致性和隔离性。 InnoDB通过“Undo log”存储每条记录的多个版本,提供历史记录供读取&#x…...

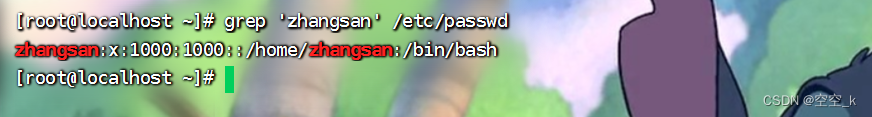

Linux之用户账号、用户组和与账号有关的系统文件

目录 一、基本介绍 1.用户和用户组 2.UID和GID 二、 账户管理 1.查看用户的UID和GID 2.添加账户 3.删除账号 4.修改账号 5.账户口令 三、分组管理 1.新增用户组 2.删除用户组 3.修改用户组 4.用户组切换 四、与账号有关的系统文件 1./etc/passwd 2./etc/shado…...

mac 安装 pip,如果你的电脑已经有 python3

文章目录 如果没装 如果你的电脑已经有 python3. 安装 pip 执行以下命令, 输入 python3 -m ensurepip --upgrade ,按下Enter就大功告成了! 安装后查看版本: pip3 -V 如果没装 先安装 python,建议使用 homebrew。 …...

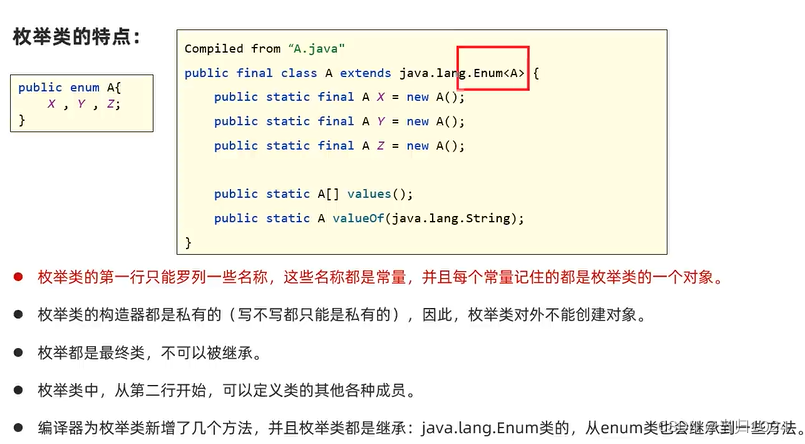

java 枚举

枚举的格式 枚举是一种特殊的类 枚举类的最开始必须罗列所有类型 枚举类提供了一些父类的方法 values() :获取所有的的枚举对象,是一个数组 public enum A {A1, A2, A3;String name;A() {this.name "default";}String getName() {return name;}void setName(Strin…...

Java学习之类和对象、内存底层

目录 表格结构和类结构 表格的动作和类的方法 与面向过程的区别 具体实现 对象和类的详解 类的定义 属性(field 成员变量) 方法 示例--编写简单的学生类 简单内存分析(理解面向对象) 构造方法(构造器 constructor) 声明格式: 四…...

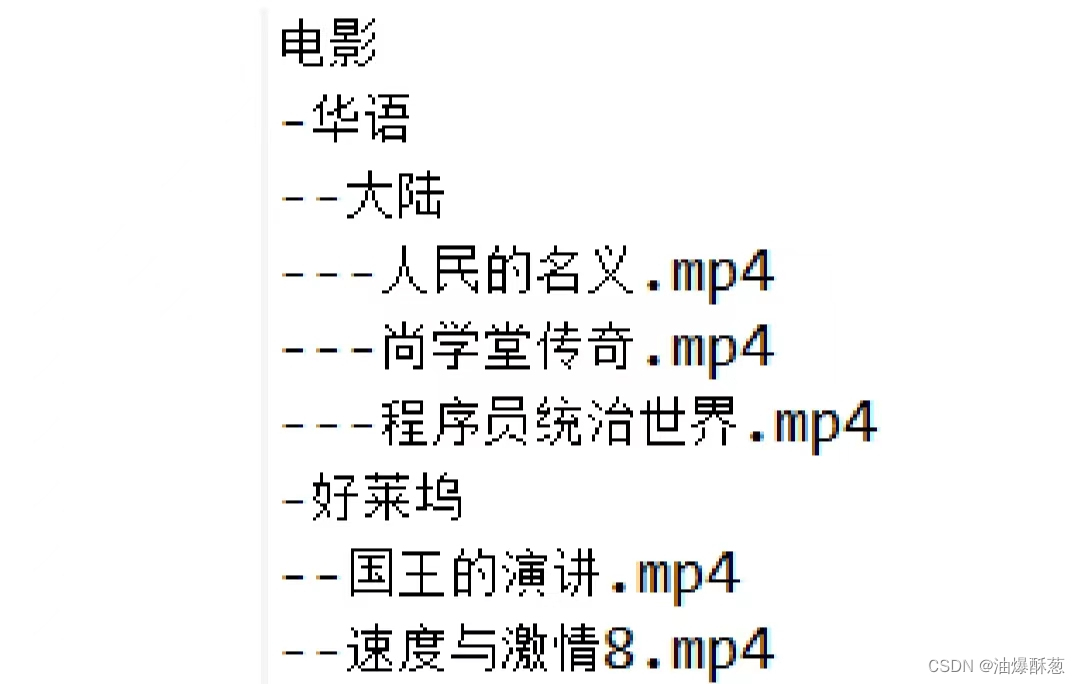

递归遍历目录结构和树状展现

在D盘下创建文件夹“电影”,在文件夹“电影”下创建“华语”、“好莱坞”,在文件夹“华语”下创建文件“人民的名义.mp4”、“天安门传奇.mp4”、“程序员统治世界.mp4”,在文件夹“好莱坞”下创建文件“国王的演讲.mp4”、“速度与激情8.mp4…...

【C++的奇迹之旅(二)】C++关键字命名空间使用的三种方式C++输入输出命名空间std的使用惯例

文章目录 📝前言🌠 C关键字(C98)🌉 命名空间🌠命名空间定义🌉命名空间使用 🌠命名空间的使用有三种方式:🌉加命名空间名称及作用域限定符🌠使用using将命名空间中某个成员…...

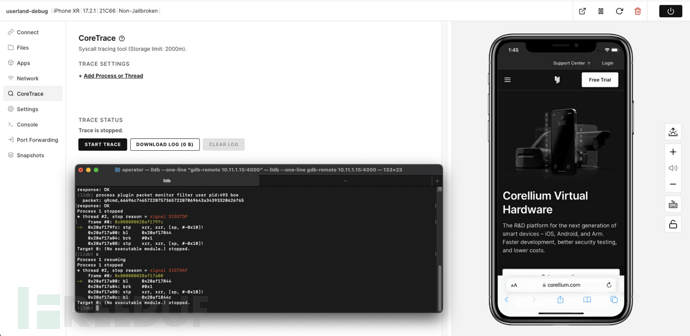

如何通过针对iOS的动态分析技术绕过反调试机制

在这篇文章中,我们将跟大家介绍和分析一种针对iOS的新型安全研究技术,该技术能够让iOS应用程序的调试过程更加轻松,并解决那些可能会延缓我们步伐的阻碍。 如果你要对一个采用了反调试技术的iOS应用程序或二进制文件进行调试的话,…...

33.Python从入门到精通—Python3 正则表达式 re.match函数 re.search方法 re.match与re.search的区别

33.从入门到精通:Python3 正则表达式 re.match函数 re.search方法 re.match与re.search的区别 Python3 正则表达式re.match函数re.search方法re.match与re.search的区别 Python3 正则表达式 在 Python3 中,可以使用 re 模块来进行正则表达式的匹配和处理…...

R3nzSkin英雄联盟皮肤修改器完整教程:免费体验全皮肤的终极指南

R3nzSkin英雄联盟皮肤修改器完整教程:免费体验全皮肤的终极指南 【免费下载链接】R3nzSkin Skin changer for League of Legends (LOL) 项目地址: https://gitcode.com/gh_mirrors/r3n/R3nzSkin R3nzSkin是一款专为《英雄联盟》玩家设计的开源皮肤修改工具&a…...

Windows上的APK安装革命:如何用开源工具无缝运行安卓应用

Windows上的APK安装革命:如何用开源工具无缝运行安卓应用 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 还在为Windows和安卓生态之间的鸿沟而烦恼吗&…...

AzurLaneAutoScript:基于图像识别与智能调度的碧蓝航线全自动脚本架构解析

AzurLaneAutoScript:基于图像识别与智能调度的碧蓝航线全自动脚本架构解析 【免费下载链接】AzurLaneAutoScript Azur Lane bot (CN/EN/JP/TW) 碧蓝航线脚本 | 无缝委托科研,全自动大世界 项目地址: https://gitcode.com/gh_mirrors/az/AzurLaneAutoSc…...

开源机械爪OpenClaw Max:从设计原理到实践应用全解析

1. 项目概述:从开源机械爪到OpenClaw Max的进化之路如果你和我一样,对机器人、自动化或者DIY硬件充满热情,那么“机械爪”这个组件一定不会陌生。它就像是机器人的“手”,是实现抓取、搬运、操作等复杂任务的核心执行器。市面上有…...

ESXi 8.0 最低存储要求:8GB 起步,这样装最稳

在部署 VMware ESXi 8.0 虚拟化环境时,存储规划是基础且关键的一步,很多新手常混淆系统引导盘与虚拟机数据盘的要求。核心结论清晰:ESXi 8.0 最低需 8GB SD 卡 / USB 作为引导介质,同时必须搭配独立的数据存储;生产环境…...

AI开发者实战指南:从工具全景到本地知识库搭建

1. 从Awesome List到实战地图:一份AI开发者工具全景解析如果你是一名AI开发者、研究者,或者只是对构建AI应用充满好奇的技术爱好者,面对浩如烟海的工具、框架和平台,最头疼的恐怕就是“我该从哪里开始?”这个问题。网上…...

跨设备代码同步工具cursor-sync:设计原理与工程实践指南

1. 项目概述:一个为开发者设计的代码同步工具如果你和我一样,经常在多个设备上切换着写代码——比如在公司用台式机,回家用笔记本,甚至偶尔在平板上改几行——那你一定对“代码同步”这个痛点深有体会。手动复制粘贴、用U盘倒腾、…...

工业现场故障排查:从温度敏感故障到CMOS浮空输入根因分析

1. 项目概述:一个“脾气暴躁”的堆垛起重机 在工业现场,最让人头疼的往往不是那些彻底罢工的设备,而是那些“时好时坏”、“看心情工作”的间歇性故障。它们像幽灵一样,在你想复现问题时消失得无影无踪,等你一离开又悄…...

AI建站工具怎么选?一份让你不踩坑的选型标准与对比指南

AI建站工具怎么选?一份让你不踩坑的选型标准与对比指南市面上号称AI建站的工具层出不穷,有的只是给模板加了个AI抠图功能,有的则能真正从0生成代码。对于非技术背景的中小企业主或运营来说,选错工具不仅浪费钱,更浪费时…...

基于MCP协议构建技术生态分析工具:架构设计与工程实践

1. 项目概述:一个技术生态分析工具的诞生最近在折腾一个挺有意思的东西,一个叫apifyforge/tech-ecosystem-analysis-mcp的项目。光看这个名字,可能有点唬人,但说白了,它就是一个用来“解剖”技术生态系统的工具。想象一…...