状态机设计举例

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者公众号【AIShareLab】回复 FPGA 也可获取。

文章目录

- 汽车尾灯控制电路设计

- 应用算法状态机设计十字路口交通灯控制电路

- 1.ASM图的状态框、判断框和输出框。

- 2.ASM图中各种逻辑框之间的时间关系

- 3.十字路口交通灯控制电路设计举例

- 状态机设计准则

- FSM输出方法

- 有限状态机HDL描述规则

- 可靠性与容错性

汽车尾灯控制电路设计

重点介绍构造状态图的两种方法:一是试探法,二是基于算法状态机构造状态图的方法。

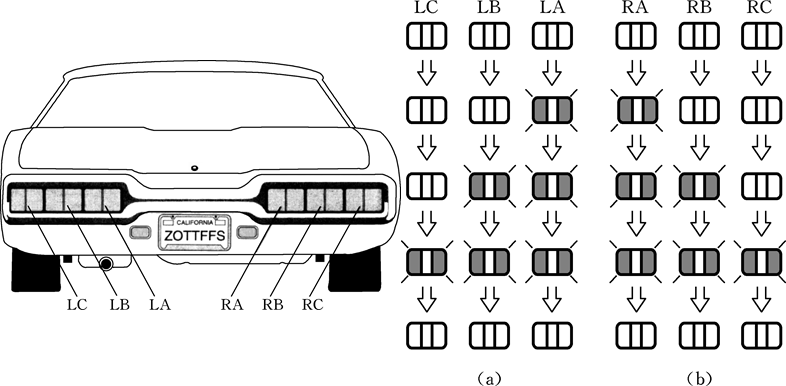

例 (试探法)汽车尾灯发出的信号主要是给后面行驶汽车的司机看的,通常汽车驾驶室有刹车开关(HAZ)、左转弯开关(LEFT)和右转弯开关(RIGHT),司机通过操作这3个开关给出车辆的行驶状态。假设在汽车尾部左、右两侧各有3个指示灯,分别用LA、LB、LC、RA、RB、RC表示,如图所示。这些灯的亮、灭规律如下:

- 汽车正常行驶时,尾部两侧的6个灯全部熄灭。

- 刹车时,汽车尾灯工作在告警状态,所有6个灯按一定频率闪烁(或一直保持常亮状态)。

- 左转弯时,左侧3个灯轮流顺序点亮(或按一定频率闪烁),其规律如图(a)所示,右侧灯全灭。

- 右转弯时,右侧3个灯轮流顺序点亮(或按一定频率闪烁),其规律如图(b)所示,左侧灯全灭。

假设电路的输入时钟信号为CP,CP的频率对于汽车尾灯所要求的闪烁频率。试根据上述要求设计出一个时钟同步的状态机来控制汽车的尾灯。

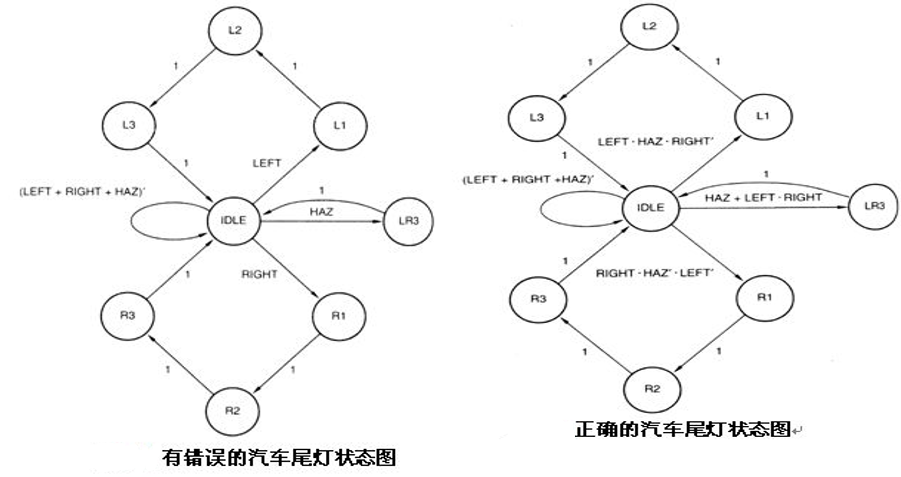

(1)画出原始状态图

选择Moore机设计该电路,则尾灯的亮、灭直接由状态译码就可以得到。由设计要求可知:汽车左转弯时,右边的灯不亮而左边的灯依次循环点亮,即0个、1个、2个或3个灯亮,分别用L0、L1、L2、L3表示,状态机在4个状态中循环。同理,汽车右转弯时,状态机也会在4个状态中循环,即左边灯不亮而右边的灯有0个、1个、2个或3个灯亮,分别用R0、R1、R2、R3表示。由于L0和R0都表示6个灯不亮,所以合起来用IDLE表示。将6个灯都亮的状态用LR3表示。可得原始的状态图就画出来了,如图所示。

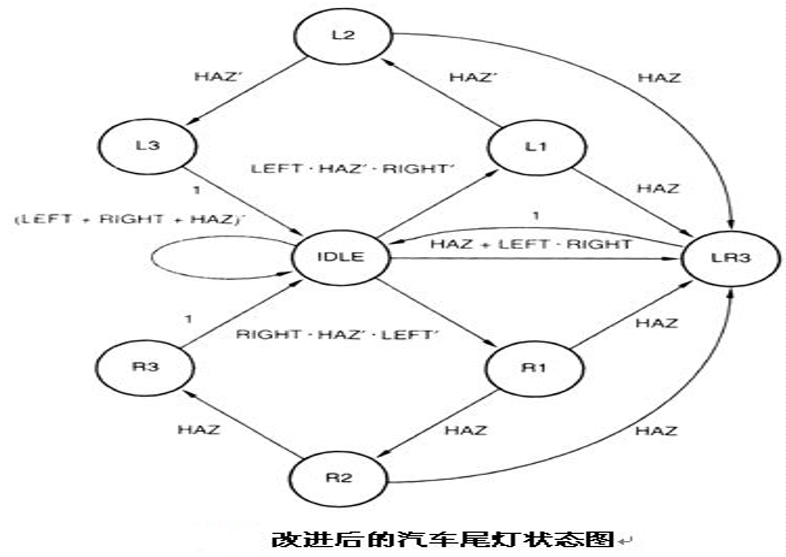

分析一下下图,就会发现一个没有考虑到的实际问题,即如果多个输入同时有效,状态机如何工作呢?下图解决了多个输入同时有效的问题,并将LEFT和RIGHT同时有效的情况处理成告警状态。经过改进且具有这一特性的状态图如下所示。

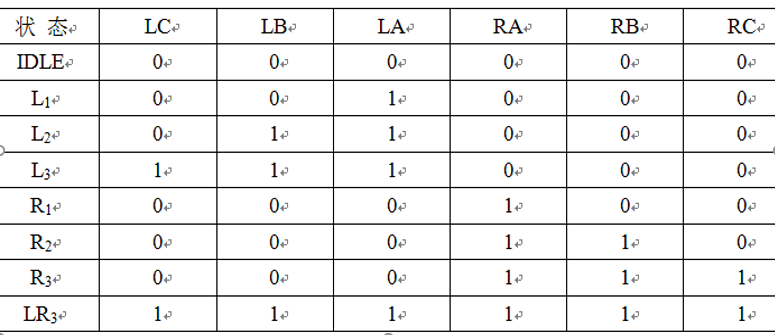

(2)列出电路的输出

由于电路的输出信号较多,不便于写在状态图中,所以单独列出输出逻辑真值表,如表所示。

(3)选择一种编码方案,对上述状态图进行状态分配,然后用Verilog HDL描述状态图和输出逻辑。

状态图完成后,必须进行完备性和互斥性的检查。

①完备性的检查方法是:对于每一个状态,将所有脱离这一状态的条件表达式进行逻辑或运算,如果结果为1就是完备的。否则不完备,也就是说状态图进入某状态后,却不能跳出该状态。

②互斥性的检查方法是:对于每一个状态,将所有脱离这一状态的条件表达式找出来,然后任意两个表达式进行逻辑与运算,如果结果为0就是互斥的。也就是要保证在任何时候不会同时激活两个脱离状态的转换,即从一个状态跳到两个状态。

应用算法状态机设计十字路口交通灯控制电路

算法状态机ASM(Algorithmic State Machine)图是描述数字系统控制算法的流程图。应用ASM图设计数字系统,可以很容易将语言描述的设计问题变成时序流程图的描述,根据时序流程图就可以得到电路的状态图和输出函数,从而得出相应的硬件电路。

1.ASM图的状态框、判断框和输出框。

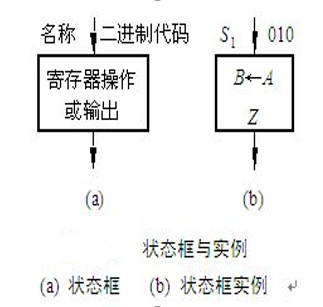

ASM图中有三种基本的符号,即状态框、判断框和输出框。数字系统控制序列中的状态用状态框表示,如图(a)所示。图(b)为状态框实例。图中的箭头表示系统状态的流向。

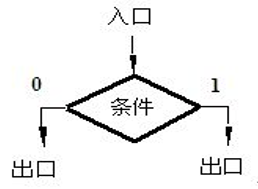

判断框表示状态变量对控制器工作的影响,如图所示:

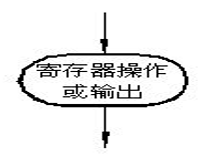

条件输出框如下图所示,条件框的入口必定与判断框的输出相连。

2.ASM图中各种逻辑框之间的时间关系

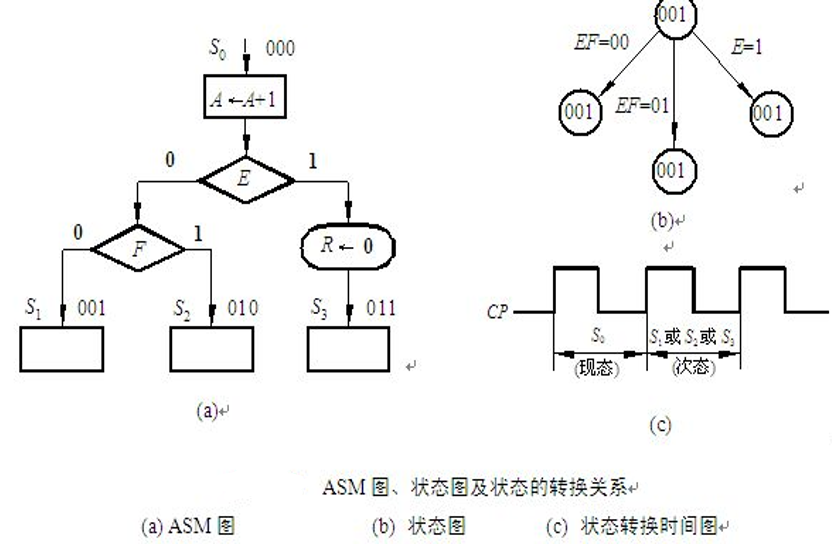

从表面上来看ASM图与程序流程图很相似,但实际上有很大的差异。程序流程图只表示事件发生的先后顺序,没有时间概念,而ASM图则不同,它表示事件的精确时间间隔顺序。在ASM图中每一个状态框表示一个时钟周期内的系统状态,状态框和与之相连的判断框,条件输出框所规定的操作,都是在一个共同的时钟周期实现的,同时系统的控制器从现在状态(现态)转移到下一个状态(次态)。因此,可以很容易将图(a)所示的ASM图转换成状态图,如图(b)所示,其中E和F为状态转换条件。与ASM图不同,状态图无法表示寄存器操作。

图(c)给出了ASM图的各种操作及状态转换的时间图。

3.十字路口交通灯控制电路设计举例

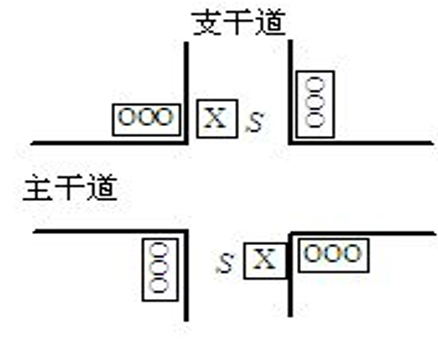

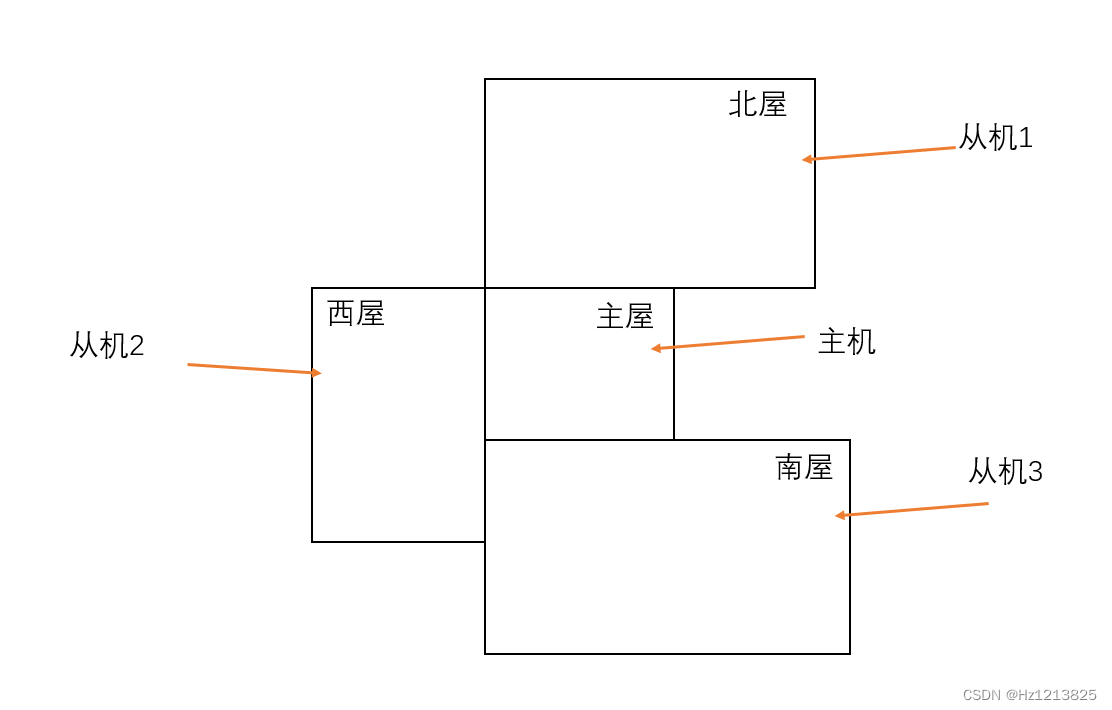

例(基于算法状态机构造状态图的方法)图4.4.10表示位于主干道和支干道的十字路口交通灯系统,支干道两边安装有传感器S(Sensor),试设计一个主干道和支干道十字路口的交通灯控制电路,其技术要求如下:

- 一般情况下,保持主干道畅通,主干道绿灯亮、支干道红灯亮,并且主干道绿灯亮的时间不得少于60秒。

- 主干道车辆通行时间已经达到60秒,且支干道有车时,则主干道红灯亮、支干道绿灯亮,但支干道绿灯亮的时间不得超过30秒。

- 每次主干道或支干道绿灯变红灯时,黄灯先亮5秒钟。

设计步骤:

- 明确系统的功能,进行逻辑抽象

- 确定系统方案并画出ASM图

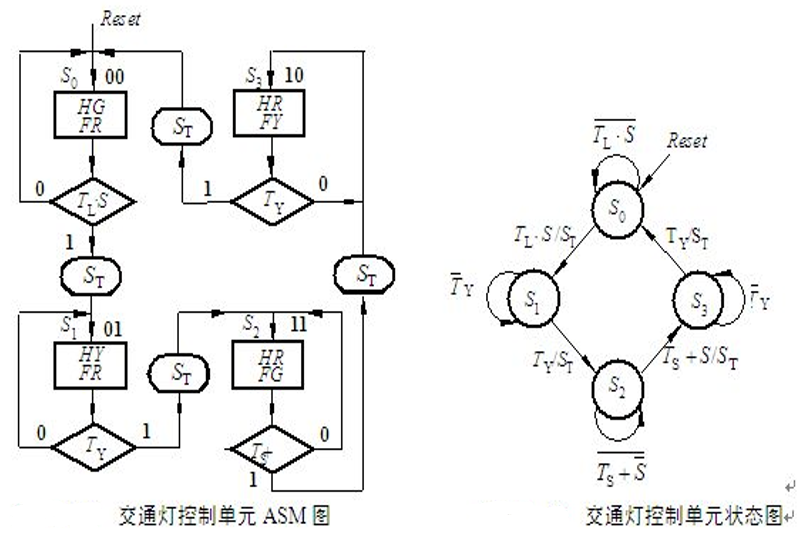

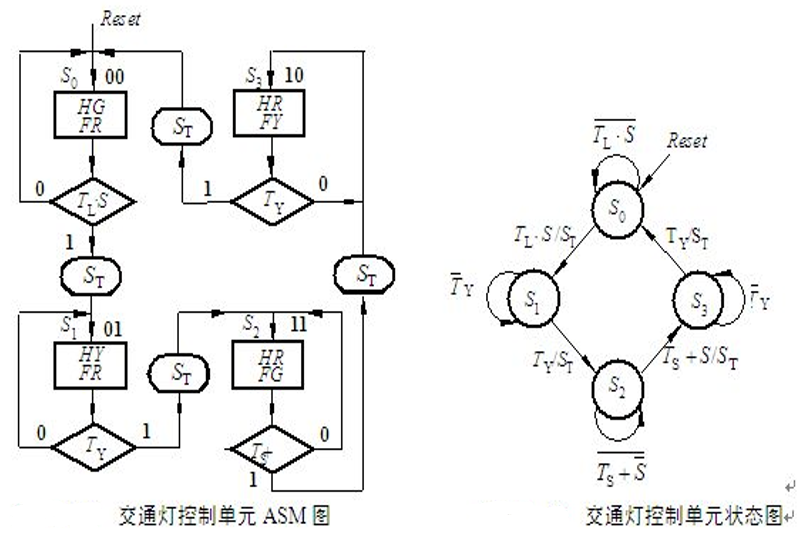

交通灯控制单元的控制过程分为四个阶段,对应的输出有四种状态,分别用S0, S1, S2和S3表示:

S0状态:主干道绿灯亮支干道红灯亮,此时若支干道有车等待通过,而且主干道绿灯已亮足规定的时间间隔TL(60s),控制器发出状态转换信号ST,控制器从状态S0转换到S1。

S1状态:主干道黄灯亮,支干道红灯亮,进入此状态,黄灯亮足规定的时间间隔TY(5s)时,控制器发出状态转换信号ST,控制器从状态S1转换到S2。

S2状态:支干道绿灯亮,主干道红灯亮,若此时支干道继续有车,则继续保持此状态,但支干道绿灯亮的时间不得超过TS(30s)时间间隔,否则控制单元发出状态转换信号ST,控制器转换到S3状态。

S3状态:支干道黄灯亮,主干道红灯亮,此时状态与S1状态持续的时间间隔相同,均为TY(5s) ,时间到时,控制器发出ST信号,控制器从状态S3回到S0状态。

对上述S0、S1、S2和S3四种状态按照格雷码进行状态编码,分别为00,01,11和10,由此得到交通灯控制单元的ASM图如图所示。依此类推得出所示的状态图。

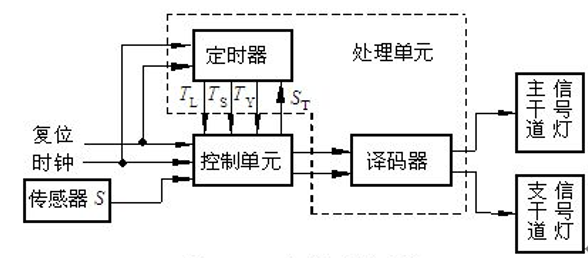

(3)交通灯控制器各功能模块电路的框架设计

通过分析交通灯控制电路的要求可知,系统主要由传感器S(Sensor)、时钟脉冲产生器(CLK )、定时器(TL, TS, TY)、控制器及译码器构成,传感器S在有车辆通过时发出一个高电平信号。

①设计控制器

根据交通灯控制单元的ASM图,得出其状态图如图4.4.13所示。ASM图中的状态框与状态图中的状态相对应,判断框中的条件是状态转换的输入条件,条件输出框与控制单元状态转换的输出相对应。状态图是描述状态之间的转换。

②设计定时器

定时器由与系统秒脉冲同步的计数器构成,时钟脉冲上升沿到来时,在控制信号ST作用下,计数器从零开始计数,并向控制器提供模M5、M30和M60信号,即TY、TS和TL定时时间信号。

③设计译码器

当交通灯控制电路处于不同工作状态时,交通信号灯按一定的规律与之对应。

(4)用Verilog HDL描述交通灯控制电路

根据以上设计思路,可以写出交通灯控制电路的Verilog HDL代码如下:

//--------------- controller.v ---------------

// Traffic Signal Controller

//State definition HighWay Country

`define S0 2'b00 //GREEN RED,采用宏定义方式给出状态编码

`define S1 2'b01 //YELLOW RED,不建议采用此方法

`define S2 2'b11 //RED GREEN

`define S3 2'b10 //RED YELLOW

module controller (CLK, S, nRESET, HG, HY, HR, FG, FY, FR, TimerH, TimerL);

//I/O ports

input CLK, S, nRESET; //if S=1, indicates that there is car on the country road

output HG, HY, HR, FG, FY, FR;

//declared output signals are registers

reg HG, HY, HR, FG, FY, FR;

output [3:0] TimerH;

output [3:0] TimerL;

reg [3:0] TimerH, TimerL;

//Internal state variables

wire Tl, Ts, Ty; //timer output signals

reg St; //state translate signal

reg [1:0] CurrentState, NextState; //FSM state register/*===== Description of the timer block =====*/

always @(posedge CLK or negedge nRESET )

begin: counterif (~nRESET) {TimerH, TimerL} <= 8'h00; else if (St) {TimerH, TimerL} <= 8'h00; else if ((TimerH == 5) & (TimerL == 9)) begin {TimerH, TimerL} <= {TimerH, TimerL}; endelse if (TimerL == 9) begin TimerH <= TimerH + 1; TimerL <= 0; endelse begin TimerH <= TimerH; TimerL <= TimerL + 1; end

end // BCD counter

assign Ty = (TimerH==0)&(TimerL==4);

assign Ts = (TimerH==2)&(TimerL==9);

assign Tl = (TimerH==5)&(TimerL==9);/*===== Description of the signal controller block =====*/

//FSM register:State change only at positive edge of clock

always @(posedge CLK or negedge nRESET )begin: stateregif (~nRESET) //Signal controller starts in S0 stateCurrentState <= `S0;else CurrentState <= NextState;end //statereg// FSM combinational block: state machine using case statements

always @(S or CurrentState or Tl or Ts or Ty )begin: fsmcase(CurrentState)`S0: begin //S0是用define定义的,在引用时要加右撇号(反撇号)NextState = (Tl && S) ? `S1 :`S0;St = (Tl && S) ? 1:0;end`S1: beginNextState = (Ty) ? `S2 :`S1;St = (Ty) ? 1:0;end`S2: beginNextState = (Ts || ~S) ? `S3 :`S2;St = (Ts || ~S) ? 1:0;end`S3: beginNextState = (Ty) ? `S0 :`S3;St = (Ty) ? 1:0;endendcase

end //fsm

/*===== Description of the decoder block =====*/

//Compute values of main signal and country signal

always @(CurrentState)begincase (CurrentState)`S0: begin{HG, HY, HR} = 3'b100; //Highway signal is green{FG, FY, FR} = 3'b001; //Country signal is red end`S1: begin{HG, HY, HR} = 3'b010; //Highway signal is yellow{FG, FY, FR} = 3'b001; //Country signal is redend`S2: begin{HG, HY, HR} = 3'b001; //Highway signal is red{FG, FY, FR} = 3'b100; //Country signal is greenend`S3: begin{HG, HY, HR} = 3'b001; //Highway signal is red{FG, FY, FR} = 3'b010; //Country signal is yellowendendcaseend

endmodule

状态机设计准则

状态机要安全,是指FSM不会进入死循环,特别是不会进入非预知的状态,而且由于某些扰动进入非设计状态,也能很快的恢复到正常的状态循环中来。这里面有两层含意:

其一要求该FSM的综合实现结果无毛刺等异常扰动;

其二要求FSM要完备,即使受到异常扰动进入非设计状态,也能很快恢复到正常状态。

状态机的设计要满足设计的面积和速度的要求;

状态机的设计要清晰易懂、易维护.

FSM输出方法

ONE HOT编码

使用N位状态寄存器表达具有Ng 状态的FSM,每个状态具有独立的寄存器位。任意时刻只有1位寄存器为1,即hot point。此为one hot。

One hot 编码方程用简单的次态方程驱动,减少了状态寄存器之间的组合逻辑级数,因此提高了运行速度。同时是以牺牲寄存器逻辑资源和提高成本为代价的。

目标器件具有较多寄存器资源,寄存器之间组合逻辑较少时比较适用。

有限状态机HDL描述规则

单独用一个模块来描述一个有限状态机。这样易于简化状态的定义、调试和修改;同时,也可使用EDA工具来进行综合与优化。

使用代表状态名的参数(parameter)来给状态赋值,不使用宏定义(define)。宏定义产生全局定义,参数则仅仅定义一个模块内的局部定义常量。不宜产生冲突。

在always组合块中使用阻塞赋值,在always时序块中使用非阻塞赋值。

可靠性与容错性

状态机应该有一个默认(default)状态,当转移条件不满足,或者状态发生了突变时,要能保证逻辑不会陷入“死循环” ;

状态机剩余状态的设置(3个去向):

a) 转入空闲状态,等待下一个工作任务的到来;

b) 转入指定的状态,去执行特定任务;

c) 转入预定义的专门处理错误的状态,如预警状态。

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

相关文章:

状态机设计举例

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。 🔥文章和代码已归档至【Github仓库…...

Kubernetes1.25中Redis单机和集群部署实例二

1、概述我们知道在 Kubernetes 容器编排平台中, 我们可以非常方便的进行应用的扩容缩, 同时也能非常方便的进行业务的迭代,本章主要讲解在Kubernetes1.25搭建Redis单实例和Redis集群主从同步的环境流程步骤, 如果是高频访问重要的线上业务我们最好是部署在物理机器上…...

【STM32】【HAL库】遥控关灯0 概述

相关连接 【STM32】【HAL库】遥控关灯0 概述 【STM32】【HAL库】遥控关灯1主机 【STM32】【HAL库】遥控关灯2 分机 【STM32】【HAL库】遥控关灯3 遥控器 需求 家里有几个房间,开关距离床都挺远的 睡觉想要关灯的时候需要下床 因此设计了本次项目 需要满足以下要求: 可以控…...

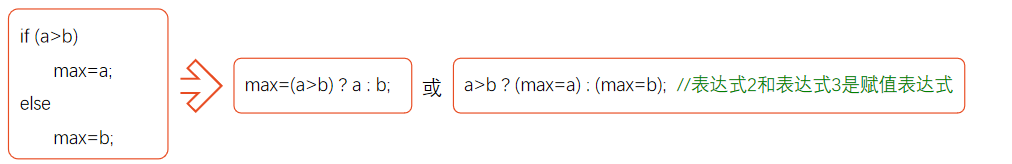

C语言学习笔记(三): 选择结构程序设计

if语句 if(){} if (a1){printf("hehe");} //单独一个ifif(){}else{} int a 1, b 2;if (a b) {printf("haha"); //if else}else{printf("hehe");}if(){}else if(){} int a 1, b 2;if (a b) {printf("haha");}else if (a …...

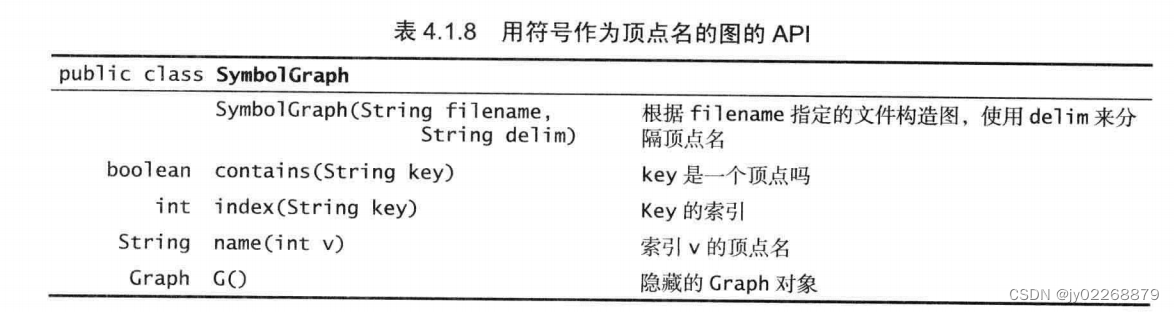

图----无向图

1.定义 图的定义:图是由一组顶点和一组能够将两个顶点相连的边组成 边:edge 顶点:vertex 连通图:如果从任意一个顶点都存在一条路径到达另外一个任意顶点,我们称这幅图是连通图。 非连通图:由若干连通的…...

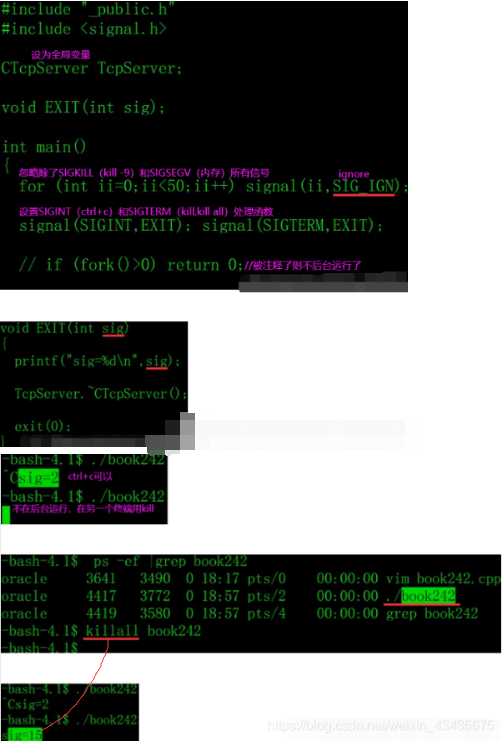

【C++1】函数重载,类和对象,引用,/string类,vector容器,类继承和多态,/socket,进程信号

文章目录1.函数重载:writetofile(),Ctrue和false,C0和非02.类和对象:vprintf构造函数:对成员变量初始化析构函数:一个类只有一个,不允许被重载3.引用:C中&取地址,C中…...

JetpackCompose从入门到实战学习笔记8—ConstraintLayout的简单使用

JetpackCompose从入门到实战学习笔记8—ConstraintLayout的简单使用 1.简介: Compose 中的 ConstraintLayout ConstraintLayout 是一种布局,让您可以相对于屏幕上的其他可组合项来放置可组合项。它是一种实用的替代方案,可代替使用多个已嵌…...

Spring Boot 快速入门(绝对经典)

目录 1、理论概述 1.1、什么是Spring Boot? 1.2、Spring Boot的特点 1.3、开发环境 2、实战——创建和配置项目 2.1、Spring Boot项目创建的两种方式 2.1.1、方法一:通过网站构建项目 2.1.2、使用Spring Initializr创建(推荐) 2.2、…...

golang context上下文

文章目录一、为什么需要context二、context 接口三、Background 方法四、 with 系列函数1、WithCancel 方法2、WithDeadline 方法3、WithTimeout 方法4、WithValue 方法五、使用注意事项一、为什么需要context 在 Go http包的Server中,每一个请求在都有一个对应的 …...

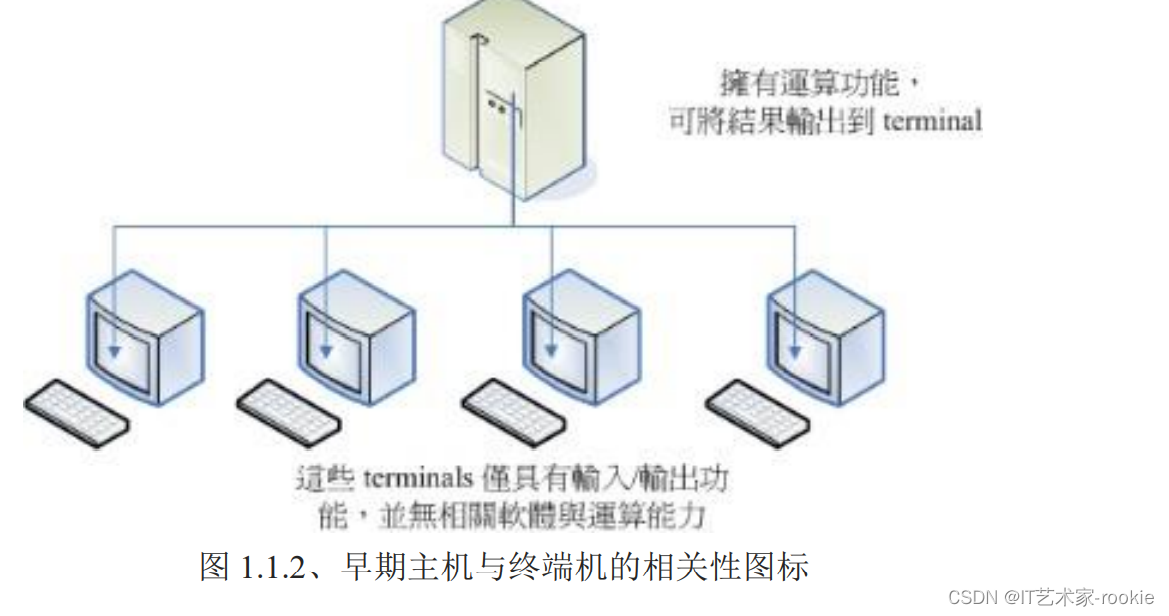

Linux---Linux是什么

Linux 便成立的核心网站: http://www.kernel.org Linux是什么 Linux 就是一套操作系统 Linux 就是核心与系统呼叫接口那两层 软件移植:如果能够参考硬件的功能函数并据以修改你的操作系统程序代码, 那经过改版后的操作系统就能够在另一个硬…...

C语言(Tgmath.h库(C99),exit和atexit)

一.Tgmath.h库(C99) C99标准提供得tgmath.h头文件定义了泛型类型宏。比如在math.h中为一个函数定义了3中类型(float,double和long double)的版本,那么tgmath.h文件就创建一个泛型类型宏,与原来的float,double和long double版本的…...

LeetCode 刷题系列 -- 739. 每日温度

给定一个整数数组 temperatures ,表示每天的温度,返回一个数组 answer ,其中 answer[i] 是指对于第 i 天,下一个更高温度出现在几天后。如果气温在这之后都不会升高,请在该位置用 0 来代替。示例 1:输入:temperatures …...

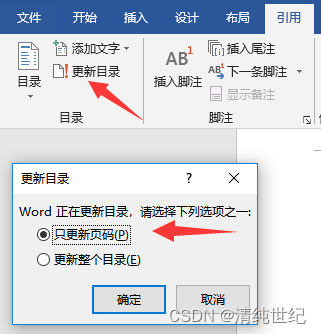

如何生成毕业论文的目录和创建模板

有粉丝同学最近在写毕业论文,其中比较让人恼火的是毕业论文的目录,折腾了几遍没弄好,想让我写个简单地教程,那就来吧。主要分为三步:第一步是从模板里面提取标题的样式,第二步是对自己的论文使用设置好的标…...

新来的23岁软件测试员上来秀了波操作,把几个老员工看傻了

春招了,公司来了个小伙子,一看简历,嘿?22岁,这不刚毕业的小毛孩子嘛,结果没想到人家上来就把现有项目的性能优化了一遍,给公司节省了一半的成本,这种“王炸”打法,直接给…...

Window10开放某个端口

需求:由于防火墙原因,开放某个端口:如9999 在开始那里搜索防火墙-进入防火墙 第一步:核实是否启动了防火墙,之后进行 第二步:点击“高级设置”,→“入站规则”→“新建规则”→“端口”→ “下一步” …...

进阶7 分页查询

进阶7 分页查询!!! 目录概述练习题概述 应用场景:当要显示的数据一页显示不全,需要分页提交SQL请求 语法: select 查询列表 from 表名 【join type join 表2 on 连接条件 where 筛选条件 group by 分组字段…...

利用升序定时器链表处理非活动连接

参考自游双《Linux高性能服务器编程》 背景 服务器同常需要定期处理非活动连接:给客户发一个重连请求,或关闭该连接,或者其他。我们可以通过使用升序定时器链表处理非活动连接,下面的代码利用alarm函数周期性的触发SIGALRM信号&a…...

MySQL 开发规范

一、数据库命名规范所有数据对象名称必须小写 :db_user禁止使用MySQL 保留关键字,若是则引用 临时表以tmp_ 开头,备份表以bak_ 开头并以时间戳结尾所有存储相同数据的列名和列类型必须一致二、数据库基本设计规范1、MySQL…...

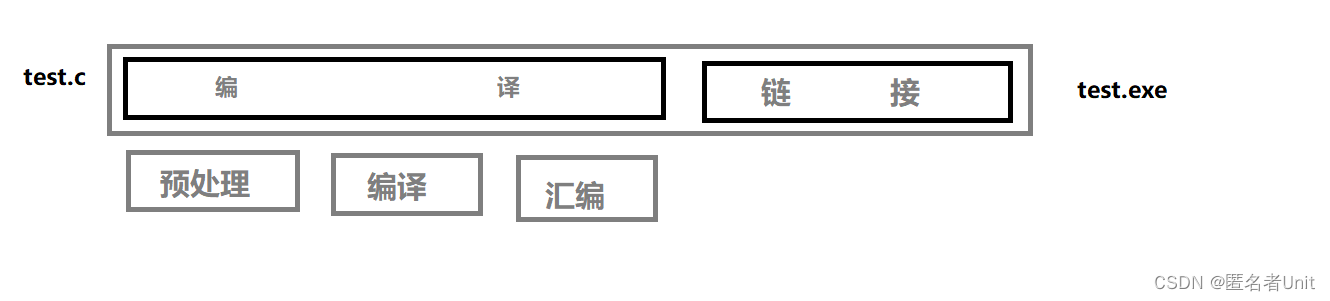

【C语言进阶】预处理与程序环境

目录一.详解编译与链接1.前言2.翻译环境3.剖析编译过程4.运行环境二.预处理详解1.预定义符号2.剖析#define(1).定义标识符(2).定义宏(3).替换规则(4).#和##(5).宏与函数的对比(6).#undef3.条件编译4.文件包含(1).头文件包含的方式(2).嵌套文件包含一.详解编译与链接 1.前言 在…...

【Docker知识】将环境变量传递到容器

一、说明 程序通常通过与软件捆绑在一起的配置来控制操作,环境变量允许用户在运行时设置它们。但是,在 Docker 容器中运行进程会使事情变得复杂,那么如何将环境变量传递给容器呢?下面介绍若干个传递办法。 二、环境变量有何用途 环…...

从OCP协议到3D寄生提取:EDA/IP技术演进与工程实践深度解析

1. 行业动态综述:从新闻简报到深度洞察每周追踪EDA(电子设计自动化)和IP(知识产权核)领域的动态,已经成了我从业十几年来的一个习惯。这不仅仅是看看新闻,更像是定期参加一场虚拟的行业技术交流…...

版本:UEFI-OC095-)

Hyper-V下安装macOS(引导文件macOS.Monterey.14.x.UEFI.vhdx)版本:UEFI-OC095-

用于windows自带hyper-v虚拟机安装macos14时使用的虚拟磁盘,具体如何安装请参考文章...

LayerDivider:如何用3步将单张插画自动分层为可编辑PSD文件?

LayerDivider:如何用3步将单张插画自动分层为可编辑PSD文件? 【免费下载链接】layerdivider A tool to divide a single illustration into a layered structure. 项目地址: https://gitcode.com/gh_mirrors/la/layerdivider 你是否曾经面对一张精…...

2026购物机器人操作指南:工作原理与使用教程

在电商自动化和AI技术不断发展的背景下,购物机器人(Shopping Bot)正在成为越来越多人关注的工具。无论是用于限量商品抢购、价格监控,还是电商数据采集,它都在改变传统的线上购物方式。本文将从基础概念出发࿰…...

智能网联汽车窄路车流预测与协同通行【附仿真】

✨ 长期致力于智能网联汽车、窄路段、短时车流量预测、协同通行研究工作,擅长数据搜集与处理、建模仿真、程序编写、仿真设计。 ✅ 专业定制毕设、代码 ✅ 如需沟通交流,点击《获取方式》 (1)窄路车流时空异质图特征构建ÿ…...

ChatGPT和Gemini聊天记录导出

AI对话记录导出技术演进:从碎片化到结构化管理的范式突破 一、技术革命带来的新痛点:AI对话资产的管理困境 在生成式AI技术日臻成熟的今天,开发者与AI的交互频率呈指数级增长。以ChatGPT日均处理30亿次查询、Gemini日均生成内容超2亿次的数…...

无需写代码!用 PackSoft 做数字展厅大屏

前言 做过展厅项目的朋友都懂这种痛—— 客户参观来了,讲解员打开浏览器,地址栏、书签栏、收藏夹全暴露在屏幕上,旁边还挂着一个没关的 QQ 弹窗……高端大气的数字展厅,体验瞬间拉低一个档次。 更麻烦的是:大屏全屏…...

哔哩下载姬完全指南:从入门到精通的全能B站视频下载方案

哔哩下载姬完全指南:从入门到精通的全能B站视频下载方案 【免费下载链接】downkyi 哔哩下载姬downkyi,哔哩哔哩网站视频下载工具,支持批量下载,支持8K、HDR、杜比视界,提供工具箱(音视频提取、去水印等&…...

期末弯道超车:虎贲等考 AI 课程论文功能,让结课作业又快又规范

一到期末周,多门课程论文扎堆来袭,选题、框架、文献、内容、格式样样让人头疼。熬夜赶工、东拼西凑、格式混乱,不仅拿不到高分,还容易被老师退回重改。通用 AI 写出来的内容口语化、文献虚假、结构不完整,完全不符合学…...

基于Next.js与Prisma构建宠物社区应用:全栈开发实战解析

1. 项目概述:一个为宠物爱好者打造的社区应用最近在GitHub上闲逛,发现了一个挺有意思的开源项目,叫jtsang4/happypaw。光看名字,“Happy Paw”(快乐的爪子),就能猜到这八成是和宠物相关的。点进…...