HDLBits中文版,标准参考答案 |2.5 More Verilog Features | 更多Verilog 要点

关注 望森FPGA 查看更多FPGA资讯

这是望森的第 7 期分享

这是望森的第 7 期分享

作者 | 望森

来源 | 望森FPGA

目录

1 Conditional ternary operator | 条件三目运算符

2 Reduction operators | 归约运算器

3 Reduction: Even wider gates | 归约:更宽的门电路

4 Combinational for-loop: Vector reversal 2 | 组合 for 循环:向量反转 2

5 Combinational for-loop: 255-bit population count | 组合 for 循环:255 位人口计数

6 Generate for-loop: 100-bit binary adder 2 | Generate for 循环:100 位二进制加法器 2

7 Generate for-loop: 100-digit BCD adder | Generate for 循环:100 位 BCD 加法器

本文中的代码都能够正常运行,请放心食用😋~

练习的官方网站是:https://hdlbits.01xz.net/

注:作者将每个练习的知识点都放在了题目和答案之后

1 Conditional ternary operator | 条件三目运算符

题目:

给定四个无符号数,找出最小值。无符号数可以用标准比较运算符 (a < b) 进行比较。使用条件运算符制作双向最小电路,然后组合其中几个以创建 4 路最小电路。您可能需要一些wire向量来获取中间结果。

答案:

module top_module (input [7:0] a, b, c, d,output [7:0] min);//wire [7:0] minab;wire [7:0] mincd;assign minab = (a<b)? a: b;assign mincd = (c<d)? c: d;assign min = (minab<mincd)? minab: mincd;endmodule知识点:

Verilog 有一个三元条件运算符 ( ? : ),与 C 非常相似:

(condition ? if_true : if_false)

这可用于根据一行中的条件 (mux!) 选择两个值中的一个,而无需在组合 always 块中使用 if-then。

示例:

(0 ? 3 : 5) // 这是 5,因为条件为假。

(sel ? b : a) // 由 sel 选择的 a 和 b 之间的 2 对 1 多路复用器。

always @(posedge clk) // T 触发器。

q <= toggle ? ~q : q;

always @(*) // 单输入 FSM 的状态转换逻辑

case (state)

A: next = w ? B : A;

B: next = w ? A : B;

endcase

assign out = ena ? q : 1'bz; // 三态缓冲器

((sel[1:0] == 2'h0) ? a : // 3 对 1 多路复用器

(sel[1:0] == 2'h1) ? b : c )

2 Reduction operators | 归约运算器

题目:

奇偶校验通常用作在通过不完美信道传输数据时检测错误的简单方法。创建一个电路,用于计算 8 位字节的奇偶校验位(将第 9 位添加到字节)。我们将使用“偶”奇偶校验,其中奇偶校验位只是所有 8 个数据位的异或。

答案:

module top_module (input [7:0] in,output parity); assign parity = ^in;endmodule知识点:

您已经熟悉了两个值之间的按位运算,例如 a & b 或 a ^ b。有时,您想要创建一个对一个向量的所有位进行运算的宽门,例如 (a[0] & a[1] & a[2] & a[3] ... ),如果向量很长,这会变得很繁琐。

归约运算符可以对向量的位进行 AND、OR 和 XOR 运算,从而产生一位输出:

& a[3:0] // AND: a[3]&a[2]&a[1]&a[0]. Equivalent to (a[3:0] == 4'hf)

| b[3:0] // OR: b[3]|b[2]|b[1]|b[0]. Equivalent to (b[3:0] != 4'h0)

^ c[2:0] // XOR: c[2]^c[1]^c[0]

这些是只有一个操作数的一元运算符(类似于 NOT 运算符 ! 和 ~)。您还可以反转这些运算符的输出以创建 NAND、NOR 和 XNOR 门,例如 (~& d[7:0])。

现在您可以重新访问 4 输入门和 100 输入门。

3 Reduction: Even wider gates | 归约:更宽的门电路

题目:

构建一个具有 100 个输入的组合电路,in[99:0]。

有 3 个输出:

-

out_and:100 个输入与门的输出。

-

out_or:100 个输入或门的输出。

-

out_xor:100 个输入异或门的输出。

答案:

module top_module( input [99:0] in,output out_and,output out_or,output out_xor

);assign out_and = ∈assign out_or = |in;assign out_xor = ^in;endmodule4 Combinational for-loop: Vector reversal 2 | 组合 for 循环:向量反转 2

题目:

给定一个 100 位输入向量 [99:0],反转其位顺序。

答案:

module top_module( input [99:0] in,output [99:0] out

);genvar i;generate for(i=0;i<100;i=i+1)begin:name1assign out[i] = in[99-i];endendgenerateendmodule知识点:

错解及分析:

module top_module( input [99:0] in,output [99:0] out

);genvar i;generate for(i=0;i<99;i=i+1)beginout[i] = in[99-i];endendgenerateendmoduleError (10170): Verilog HDL syntax error at top_module.v(9) near text: "="; expecting ".", or an identifier. Check for and fix any syntax errors that appear immediately before or at the specified keyword.

通过组合逻辑进行变量赋值,需要使用assign语句。

Error (10644): Verilog HDL error at top_module.v(8): this block requires a name File: /home/h/work/hdlbits.18346683/top_module.v Line: 8

需要给 Generate 中的 for 循环块命名。

5 Combinational for-loop: 255-bit population count | 组合 for 循环:255 位人口计数

题目:

“人口计数”电路计算输入向量中“1”的数量。为 255 位输入向量构建人口计数电路。

答案:

module top_module( input [254:0] in,output [7:0] out );integer i;always@(*)begin:name1out = 8'd0;for(i=0;i<255;i=i+1)beginif(in[i])out = out + 1;elseout = out;endendendmodule6 Generate for-loop: 100-bit binary adder 2 | Generate for 循环:100 位二进制加法器 2

题目:

通过实例化 100 个全加器来创建一个 100 位二进制行波进位加法器。该加法器将两个 100 位数和一个进位相加,以产生 100 位和并输出进位。为了鼓励您实际实例化全加器,还输出行波进位加法器中每个全加器的进位。cout[99] 是最后一个全加器的最终进位,也是您通常看到的进位。

答案:

module top_module( input [99:0] a, b,input cin,output [99:0] cout,output [99:0] sum );full_adder adder_0( .a(a[0]), .b(b[0]),.cin(cin),.cout(cout[0]),.sum(sum[0]) );genvar i;generate for(i=1;i<100;i=i+1)begin:name1full_adder adder_i( .a(a[i]), .b(b[i]),.cin(cout[i-1]),.cout(cout[i]),.sum(sum[i]) );endendgenerateendmodulemodule full_adder( input a, b,input cin,output cout,output sum );assign cout = a&b | a&cin | b&cin;assign sum = a ^ b ^ cin;endmodule7 Generate for-loop: 100-digit BCD adder | Generate for 循环:100 位 BCD 加法器

题目:

您将获得一个名为 bcd_fadd 的 BCD 一位数加法器,它将两个 BCD 数字和进位相加,并产生一个和及进位输出。

module bcd_fadd (

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

实例化 100 个 bcd_fadd 副本以创建一个 100 位 BCD 行波进位加法器。您的加法器应将两个 100 位 BCD 数字(打包成 400 位向量)和一个进位相加,以产生一个 100 位和及进位输出。

答案:

module top_module( input [399:0] a, b,input cin,output cout,output [399:0] sum );wire [99:0] cout_t;bcd_fadd add_0(.a(a[3:0]),.b(b[3:0]),.cin(cin),.cout(cout_t[0]),.sum(sum[3:0]) );genvar i;generate for (i=1;i<100;i=i+1)begin:name1bcd_fadd add_i(.a(a[i*4+3:i*4]),.b(b[i*4+3:i*4]),.cin(cout_t[i-1]),.cout(cout_t[i]),.sum(sum[i*4+3:i*4]) );endendgenerateassign cout = cout_t[99];endmodule- END -

公z号/CSDN/EETOP搜索【望森FPGA】,查看更多FPGA资讯~

相关推荐文章,点击跳转:

望森FPGA的HDLBits合集

相关文章:

HDLBits中文版,标准参考答案 |2.5 More Verilog Features | 更多Verilog 要点

关注 望森FPGA 查看更多FPGA资讯 这是望森的第 7 期分享 作者 | 望森 来源 | 望森FPGA 目录 1 Conditional ternary operator | 条件三目运算符 2 Reduction operators | 归约运算器 3 Reduction: Even wider gates | 归约:更宽的门电路 4 Combinational fo…...

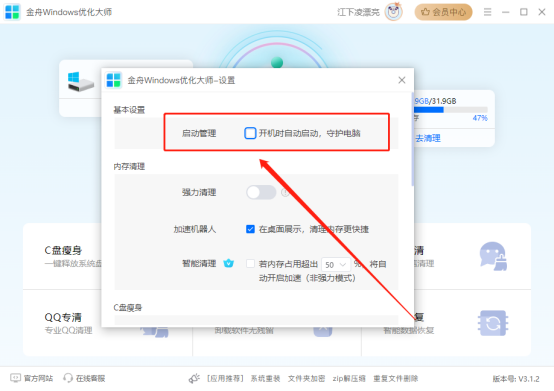

提升开机速度:有效管理Windows电脑自启动项,打开、关闭自启动项教程分享

日常使用Windows电脑时,总会需要下载各种各样的办公软件。部分软件会默认开机自启功能,开机启动项是指那些在电脑启动时自动运行的程序和服务。电脑开机自启太多的情况下会导致电脑卡顿,开机慢,运行不流畅的情况出现,而…...

数据库简单介绍

数据库是现代信息技术中用于存储、管理和检索数据的重要工具。数据库技术的发展经历了多个阶段,从早期的层次模型和网状模型,到关系型数据库的兴起,再到NoSQL和NewSQL的多样化发展。数据库系统已经成为现代信息系统的核心和基础设施。 数据库…...

运用MinIO技术服务器实现文件上传——利用程序上传图片(二 )

在上一篇文章中,我们已经在云服务器中安装并开启了minio服务,本章我们将为大家讲解如何利用程序将文件上传到minio桶中 下面介绍MinIO中的几个核心概念,这些概念在所有的对象存储服务中也都是通用的。 - **对象(Object࿰…...

C语言 | Leetcode C语言题解之第461题汉明距离

题目: 题解: int hammingDistance(int x, int y) {int s x ^ y, ret 0;while (s) {s & s - 1;ret;}return ret; }...

Qt 3D、QtQuick、QtQuick 3D 和 QML 的关系

理清 Qt 3D、QtQuick、QtQuick 3D 和 QML 的关系 在开发图形界面应用时,特别是在使用 Qt 框架时,开发者可能会接触到多个概念,如 Qt 3D、QtQuick、QtQuick 3D 和 QML。这些术语分别代表了 Qt 中不同的模块或技术,但由于它们的功能…...

软件设计师(软考学习)

数据库技术 数据库基础知识 1. 数据库中的简单属性、多值属性、复合属性、派生属性简单属性:指不能够再分解成更小部分的属性,通常是数据表中的一个列。例如学生表中的“学号”、“姓名”等均为简单属性。 多值属性:指一个属性可以有多个值…...

第一讲:Go语言开发入门:环境搭建与基础语法

文章目录 环境搭建windows环境搭建Mac环境搭建安装GO使用 Homebrew 安装 Go手动下载安装 Go 配置环境变量配置环境变量检查 Go 是否正确安装 验证安装:编写第一个 Go 程序创建 Go 工作区编写 Hello World 程序运行程序编译程序 常用的 Go 命令 Go语言基础语法1. 变量…...

Linux CentOS stream9配置本地yum源

在Linux系统中,yum源配置是一个重要的环节。把系统安装时配置的国外yum源转换为国内yum源,能够帮助系统快速安装软件包。对于网络环境不稳定或无法联网的系统,配置本地yum源,可以让用户在离线状态下也能进行软件包的安装,十分重要。 一、国内源 在使用Linux的日常工作中…...

std::string

std::string是C标准库中的一个基本类模板,专门用于处理字符串。它提供了一个可变长度的字符序列,以及一系列用于字符串操作的方法。std::string是值类型,这意味着当它作为函数参数传递或赋值时,整个字符串数据会被复制。 std::st…...

【Docker】03-自制镜像

1. 自制镜像 2. Dockerfile # 基础镜像 FROM openjdk:11.0-jre-buster # 设定时区 ENV TZAsia/Shanghai RUN ln -snf /usr/share/zoneinfo/$TZ /etc/localtime && echo $TZ > /etc/timezone # 拷贝jar包 COPY docker-demo.jar /app.jar # 入口 ENTRYPOINT ["ja…...

Java GC 分类,8和9使用的哪种?

Java的垃圾收集器(Garbage Collector, GC)负责自动管理内存,回收不再使用的对象所占用的空间。随着JVM的发展,出现了多种不同特性的垃圾收集器来适应不同的应用场景和性能需求。在Java 8中,主要有以下几种垃圾收集器&a…...

【Docker从入门到进阶】01.介绍 02.基础使用

1. 介绍 1.1. 什么是 Docker Docker 是一个开源的平台,用于开发、发布和运行应用程序。它使开发者能够以更精简的方式封装应用及其依赖,做到“打包一次,到处运行”。通过 Docker,您可以创建轻量级、可移植的容器,每个…...

GraphRAG-Local-UI - 基于 GraphRAG 支持本地的聊天UI

文章目录 一、关于 GraphRAG-Local-UI 🕸️特点🌟🗺️路线图最近更新即将推出的功能 二、📦安装和设置三、使用入门🚀1、创建索引目录2、添加示例数据(可选)3、初始化索引文件夹4、配置设置5、定…...

Java 根据字符生成背景透明的图片

上代码 package com.example.demotest.controller;/*** Author shaolin* Date 2024-10-08 10:11**/import javax.imageio.ImageIO; import java.awt.*; import java.awt.image.BufferedImage; import java.awt.image.ColorModel; import java.awt.image.WritableRaster; impor…...

树莓派3b安装ubuntu18.04服务器系统server配置网线连接

下载ubuntu镜像网址 img镜像,即树莓派官方烧录器使用的镜像网址 ubuntu18.04-server:ARM/RaspberryPi - Ubuntu Wiki 其他版本:Index of /ubuntu/releases 下载后解压即可。 发现使用官方烧录器烧录配置时配置wifi无论如何都不能使用&am…...

【AIGC】2022-NIPS-视频扩散模型

2022-NIPS-Video Diffusion Models 视频扩散模型摘要1. 引言2. 背景3. 视频扩散模型3.1. 重建引导采样以改进条件生成 4. 实验4.1. 无条件视频建模4.2. 视频预测4.3. 文本条件视频生成4.3.1 视频与图像建模的联合训练4.3.2 无分类器指导的效果4.3.3 更长序列的自回归视频扩展 5…...

从零开始构建:Python自定义脚本自动化你的日常任务

从零开始构建:Python自定义脚本自动化你的日常任务 Python 作为一种简洁且功能强大的编程语言,被广泛应用于各种自动化任务中。通过编写 Python 脚本,你可以轻松地将日常重复性工作自动化,例如文件操作、数据处理、网络爬虫、系统…...

【python实操】python小程序之对象的属性操作

引言 python小程序之对象的属性操作 文章目录 引言一、对象的属性操作1.1 题目1.2 代码1.3 代码解释 二、思考2.1 添加属性2.2 获取属性 一、对象的属性操作 1.1 题目 给对象添加属性 1.2 代码 class Cat:# 在缩进中书写⽅法def eat(self):# self 会⾃动出现,暂不管print(f…...

HCIP——网络类型及数据链路层协议

目录 网络类型的分类 数据链路层协议 MA网络 以太网协议 P2P网络 HDLC---高级数据链路控制协议 HDLC网络搭建 PPP---点到点协议 PPP协议的优点 PPP数据帧封装结构编辑 PPP会话的搭建 路建立阶段---LCP建立 认证阶段 PAP CHAP 网络层协议协商阶段---NCP协商 网…...

Python视频自动化处理:基于FFmpeg与OpenCV的编程式剪辑框架实践

1. 项目概述与核心价值最近在折腾视频剪辑自动化流程,发现了一个挺有意思的开源项目AmitDigga/fabric-video-editor。这名字一看就带着点“缝合怪”的味道,fabric这个词在编程领域通常指代一个框架或结构,而video-editor则直指视频编辑。简单…...

个人股票数据中枢构建指南:从多源聚合到Python量化分析

1. 项目概述:一个为个人投资者打造的股票数据中枢如果你和我一样,是个喜欢自己动手折腾、对市场数据有“洁癖”的个人投资者,那你肯定也经历过这样的烦恼:想分析一只股票,数据源五花八门,格式千奇百怪&…...

海洋AI工具集seait:从数据处理到模型部署的工程实践指南

1. 项目概述:一个面向“海洋”的AI工具集最近在GitHub上闲逛,发现了一个挺有意思的项目,叫seait。第一眼看到这个名字,我下意识地把它拆成了“sea”和“it”,心想这大概是个和海洋或者海事相关的IT工具。点进去一看&am…...

英雄联盟智能BP与战绩查询:你的排位赛终极助手

英雄联盟智能BP与战绩查询:你的排位赛终极助手 【免费下载链接】Seraphine 英雄联盟战绩查询工具 项目地址: https://gitcode.com/gh_mirrors/se/Seraphine 你是否曾经在排位赛BP阶段手忙脚乱,不知道该禁用哪个英雄?或者想了解队友和对…...

RAG落地方案

1. RAG分析1.1 为什么需要 Rerank?要理解 Rerank 的价值,得先理解向量检索到底"差"在哪。RAG 的第一阶段检索,通常用的是双塔(Bi-Encoder)架构的 Embedding 模型。它的工作方式是把 Query 和每个文档分别独立…...

开发者技能图谱实战指南:从结构化知识到可执行代码的进阶之路

1. 项目概述:一个面向开发者的技能图谱与实战仓库最近在GitHub上闲逛,发现了一个挺有意思的仓库,叫GuDaStudio/skills。乍一看名字,你可能会觉得这又是一个普通的“技能清单”或者“学习路线图”项目。但点进去仔细研究后…...

不想做程序员了,听说网络安全前景好,现在转行还来得及吗?

不想做程序员了,听说网络安全前景好,现在转行还来得及吗? 我去年四月份被裁员,找了两个月工作,面试寥寥无几,就算有也都是外包,而且外包也没面试通过。我经历了挫败,迷茫࿰…...

TV Bro电视浏览器:如何在Android电视上享受完整网页浏览体验的终极指南

TV Bro电视浏览器:如何在Android电视上享受完整网页浏览体验的终极指南 【免费下载链接】tv-bro Simple web browser for android optimized to use with TV remote 项目地址: https://gitcode.com/gh_mirrors/tv/tv-bro 您是否曾经尝试在智能电视上浏览网页…...

集成三相桥驱动的MCU:AiP8F7201电机控制方案解析

1. 项目概述:为什么我们需要“集成三相桥式驱动的微控制器”?在电机控制领域,尤其是消费电子、家电、工业自动化这些我们每天都会接触到的场景里,工程师们一直在和一堆“麻烦”作斗争。想象一下,你要设计一个驱动无刷直…...

手机短剧拉片软件2026推荐,助力高效内容分析

手机短剧拉片软件2026推荐,助力高效内容分析在当今的影视行业中,手机短剧以其短小精悍、节奏紧凑的特点受到了广大观众的喜爱。对于创作者来说,如何深入分析这些短剧,学习其中的创作技巧,成为了提升自身水平的关键。据…...