硬件语言Verilog HDL牛客刷题day03 时序逻辑部分

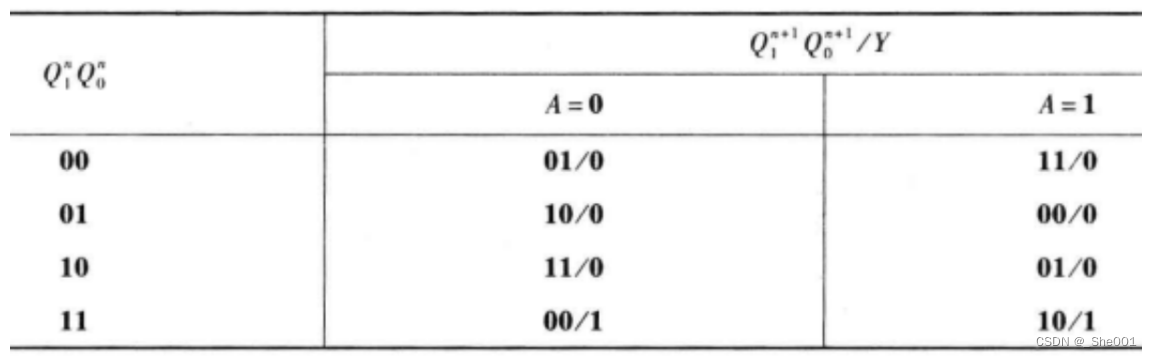

1.VL21 根据状态转移表实现时序电路

1.题目:

某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

2.解题思路

2.1 首先同步时序电路 , 时钟上升沿触发, 复位信号rst 低电平无效.

2.2 D 触发器 是一个看 A 输入的 触发器。

2.3 使用状态机。

3.解题代码

`timescale 1ns/1nsmodule seq_circuit(input A ,input clk ,input rst_n,output wire Y

);//根据表格 的要求我们知道,这个需要输出 Y Y与次态的 Q1,Q0 有关

reg q0,q1;

always@(posedge clk or negedge rst_n)beginif(~rst_n)q1<=0;elsebeginq1<= A ^ q0 ^ q1;endend

always@(posedge clk or negedge rst_n)beginif(~rst_n)q0<= 0;elsebeginq0 <= ~q0;endendassign Y = q0 & q1;endmodule2.VL22 根据状态转移图实现时序电路

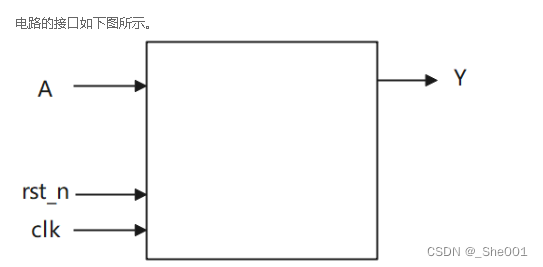

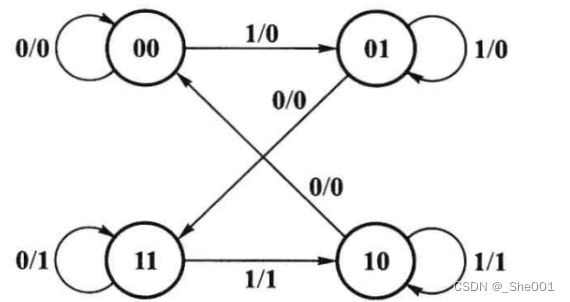

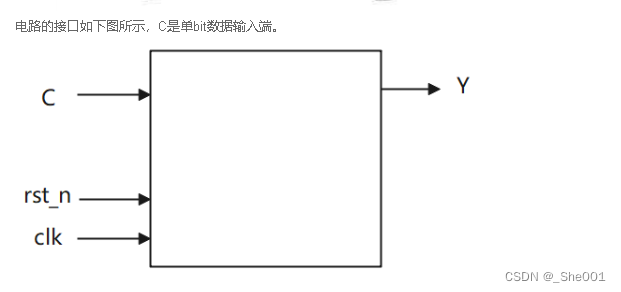

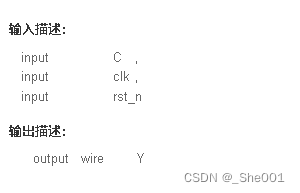

1.题目:

某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

2.解题思路

使用三段式

1)一段式:整个状态机写到一个always模块里面,在该模块中既描述状态转移,又描述状态的输入和输出;

(2)二段式:用两个always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;

(3)三段式:在两个always模块描述方法基础上,使用三个always模块,一个always模块采用 同步时序 描述状态转移,一个always采用组合逻辑判断状态转移条件,描述状态转移规律,另一个always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。

3.解题感想

3.1 在硬件电路的时候, 次态和现态,不好表达, 但是总的来说,使用 always 能解决。

3.2 使用三段式 的时候 , 题目解决简单一些。

3.3 列出一个 固定值的变量 使用 parameter 定义。

4.解题代码

`timescale 1ns/1nsmodule seq_circuit(input wire clk ,input wire rst_n,input wire C ,output reg Y

);reg [1:0] state, next_state;parameter ST0 = 2'd0;parameter ST1 = 2'd1;parameter ST2 = 2'd2;parameter ST3 = 2'd3;always@(posedge clk or negedge rst_n) beginif (~rst_n)state <= 2'd0;elsestate <= next_state;endalways@(*) begincase(state)ST0: next_state = C ? ST1 : ST0;ST1: next_state = C ? ST1 : ST3;ST2: next_state = C ? ST2 : ST0;ST3: next_state = C ? ST2 : ST3;default: next_state = ST0;endcaseendalways@(*) beginif(((state == ST2) && C) || (state == ST3))Y = 1'b1;elseY = 1'b0;endendmodule3.VL23 ROM的简单实现

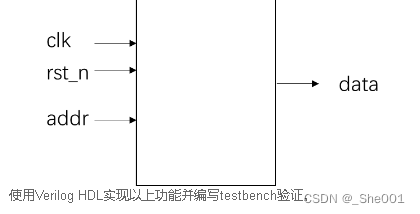

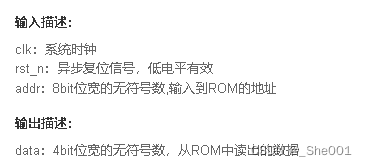

1.题目:

实现一个深度为8,位宽为4bit的ROM,数据初始化为0,2,4,6,8,10,12,14。可以通过输入地址addr,输出相应的数据data。

接口信号图如下:

2.解题思路

2.1 开辟一个 深度为 8 ,位宽为 4 bit 的数据寄存器。

2.2 向开辟的寄存器里面 存入数据。

2.3 调取这个寄存器的数据, 直接访问器地址。

3.解题感想

3.1 开辟一个 深度为8 位宽为 4 的寄存器的 方法是 前面是 宽度,后面是深度。

例如: reg[3:0] L[7:0]; //深度为8 ,位宽为4 .

4.解题代码

`timescale 1ns/1ns

module rom(input clk,input rst_n,input [7:0]addr,output [3:0]data

);

reg[3:0] ROM_DATA[7:0];

always@(posedge clk or negedge rst_n)beginif(~rst_n)beginROM_DATA[0] <=4'd0;ROM_DATA[1] <=4'd2;ROM_DATA[2] <=4'd4;ROM_DATA[3] <=4'd6;ROM_DATA[4] <=4'd8;ROM_DATA[5] <=4'd10;ROM_DATA[6] <=4'd12;ROM_DATA[7] <=4'd14;endelseROM_DATA[0] <=4'd0;ROM_DATA[1] <=4'd2;ROM_DATA[2] <=4'd4;ROM_DATA[3] <=4'd6;ROM_DATA[4] <=4'd8;ROM_DATA[5] <=4'd10;ROM_DATA[6] <=4'd12;ROM_DATA[7] <=4'd14;end

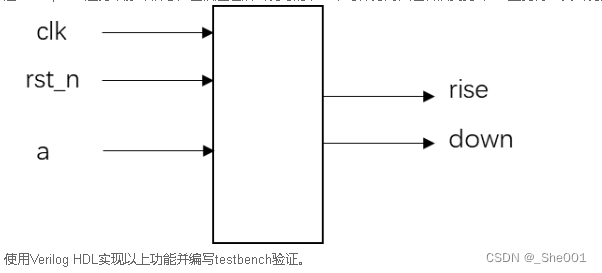

assign data = ROM_DATA[addr];endmodule4.VL24 边沿检测

1.题目:

有一个缓慢变化的1bit信号a,编写一个程序检测a信号的上升沿给出指示信号rise,当a信号出现下降沿时给出指示信号down。

注:rise,down应为单脉冲信号,在相应边沿出现时的下一个时钟为高,之后恢复到0,一直到再一次出现相应的边沿。

2.解题思路

2.1 首先是一个 次态 和 现态的问题 ,

2.2 两个 always 分别控制 次态的赋值, 和 次态和现态的对比来输出 rise 和 down 的值.

3. 解题感想

3.1 使用 if else 嵌套 if else 要使模块专一化, 就是每个部分使用 隔断语句区分 (begin end) ( 并行语句) 。

4. 解题代码

`timescale 1ns/1ns

module edge_detect(input clk,input rst_n,input a,output reg rise,output reg down

);

reg a1;

//首先搞定a

always@(posedge clk or negedge rst_n)//建立一个寄存器保存上一个时态的信号beginif(~rst_n)a1 <= 0;elsea1 <= a;endalways@(posedge clk or negedge rst_n)beginif(~rst_n)beginrise <= 0;down <= 0;endelse beginif(a & ~a1)//上一时态为 低电平, 现态为 高点品beginrise <=1'b1;down <=1'b0;endelse if(~a & a1) //次态为 高点品 , 现态 为 低电平beginrise <=0;down <=1;endelsebeginrise <=0;down <=0;endendendendmodule相关文章:

硬件语言Verilog HDL牛客刷题day03 时序逻辑部分

1.VL21 根据状态转移表实现时序电路 1.题目: 某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。 2.解题思路 2.1 首先同步时序电路 , 时钟上升沿触发, 复位信号rst 低电…...

day31 ● 455.分发饼干 ● 376. 摆动序列 ● 53. 最大子序和

● 455.分发饼干 ● 376. 摆动序列 ● 53. 最大子序和 在本次的题目中,我们使用了贪心算法来解决三个问题:分发饼干、摆动序列、最大子序和。这三个问题都可以使用贪心算法来解决,而且贪心算法的时间复杂度相对较低,能够在较短的…...

MobTech 秒验|本机号码一键登录会泄露隐私吗

本机号码一键登录是一种新型的应用登录方式,它可以利用运营商的数据网关认证能力,实现手机号免密登录,提高用户体验和转化率,降低验证成本和流失率。本机号码一键登录支持三大运营商号码认证,3秒内完成手机号验证&…...

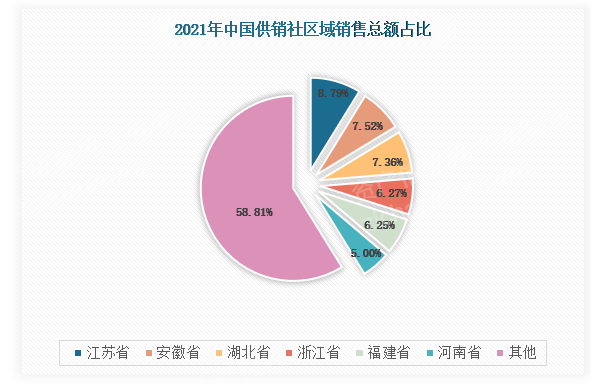

2023年供销合作社研究报告

第一章 行业概况 1.1 供销合作社概述 中华全国供销合作总社,是中华人民共和国全国供销合作社的联合组织。中华全国供销合作总社的前身可以追溯到1949年11月成立的中央合作事业管理局。在新中国成立初期,供销合作社就基本形成了自上而下、覆盖全国的组织…...

【ansible】实施任务控制

目录 实施任务控制 一,循环(迭代)--- loop 1,利用loop----item循环迭代任务 2,item---loop循环案例 1,定义item循环列表 2,通过变量应用列表格式 3,字典列表(迭代嵌套子…...

49天精通Java,第11天,java接口和抽象类的异同,default关键字

目录一、什么是接口二、接口的特点三、接口和类的区别四、接口和抽象类的区别五、接口的声明方式六、default默认方法大家好,我是哪吒。 一、什么是接口 Java接口是一系列方法的声明,是一些方法特征的集合,一个接口只有方法的特征没有方法的…...

JAVA练习99-逆波兰表达式求值

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 目录 前言 一、题目-逆波兰表达式求值 1.题目描述 2.思路与代码 2.1 思路 2.2 代码 总结 前言 提示:这里可以添加本文要记录的大概内容: 4月5…...

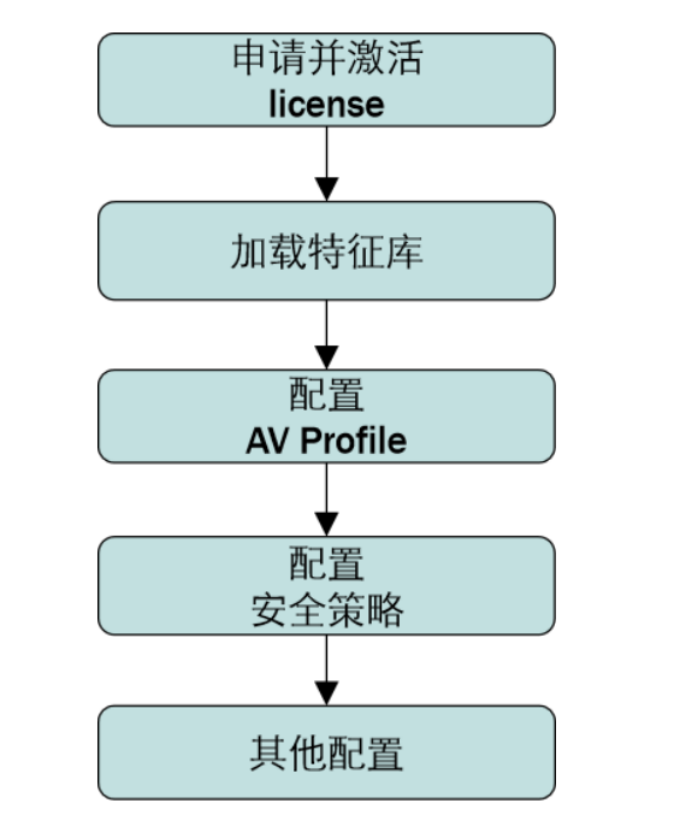

恶意软件、恶意软件反杀技术以及反病毒技术的详细介绍

1.恶意软件简单介绍恶意软件是指在计算机系统上执行恶意任务的病毒、蠕虫和特洛伊木马的程序,通过破坏软件进程来实施控制。腾讯移动安全实验室发布的数据显示,恶意软件由多种威胁组成,会不断弹出,所以需要采取多种方法和技术来进…...

【数据库运维】mysql备份恢复练习

目录 数据库备份,数据库为school,素材如下 1.创建student和score表 2.为student表和score表增加记录 3.备份数据库school到/backup目录 4.备份MySQL数据库为带删除表的格式,能够让该备份覆盖已有数据库而不需要手动删除原有数据库 5.直接将My…...

刷题30-对称的二叉树

对称的二叉树 思路:用递归,首先明白递归中止的条件是什么 搬用别人的看法: 做递归思考三步: 1.递归的函数要干什么? 函数的作用是判断传入的两个树是否镜像。 输入:TreeNode left, TreeNode right 输出…...

精选简历模板

1.应届生通用简历模板(.docx) 适用于应届生找工作的学生群体 https://download.csdn.net/download/weixin_43042683/87652099https://download.csdn.net/download/weixin_43042683/87652099 部分缩略图如下: 2.研究生通用简历模板(.docx)…...

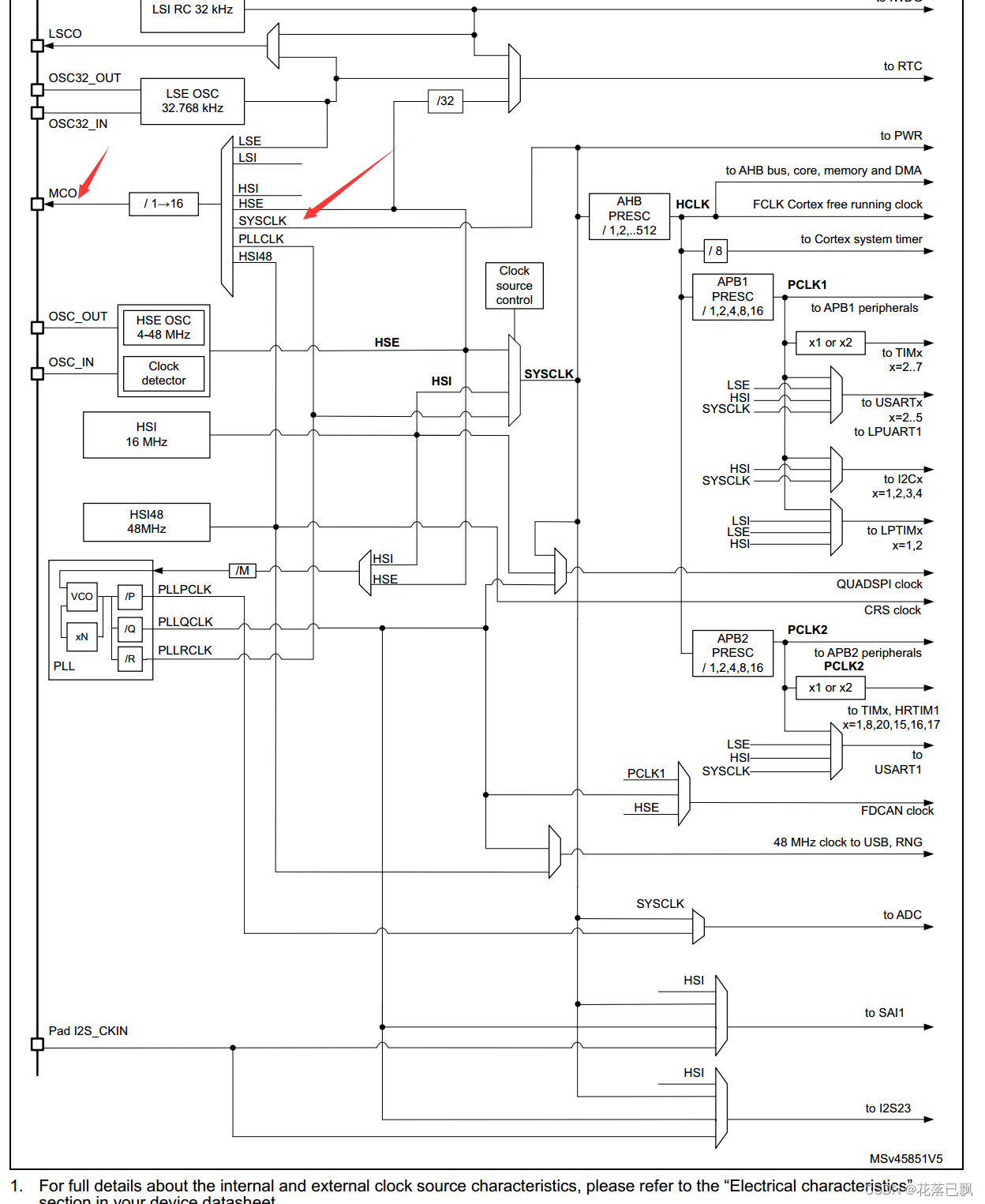

蓝桥杯嵌入式第十三届客观题解析

文章目录 前言一、题目1二、题目2三、题目3四、题目4五、题目5六、题目6七、题目7八、题目8九、题目9十、题目10总结前言 本篇文章将带大家来学习蓝桥杯嵌入式的客观题了,蓝桥杯嵌入式的客观题涉及到模电,数电,单片机等知识,需要非常扎实的基础,客观题不能急于求成只能脚…...

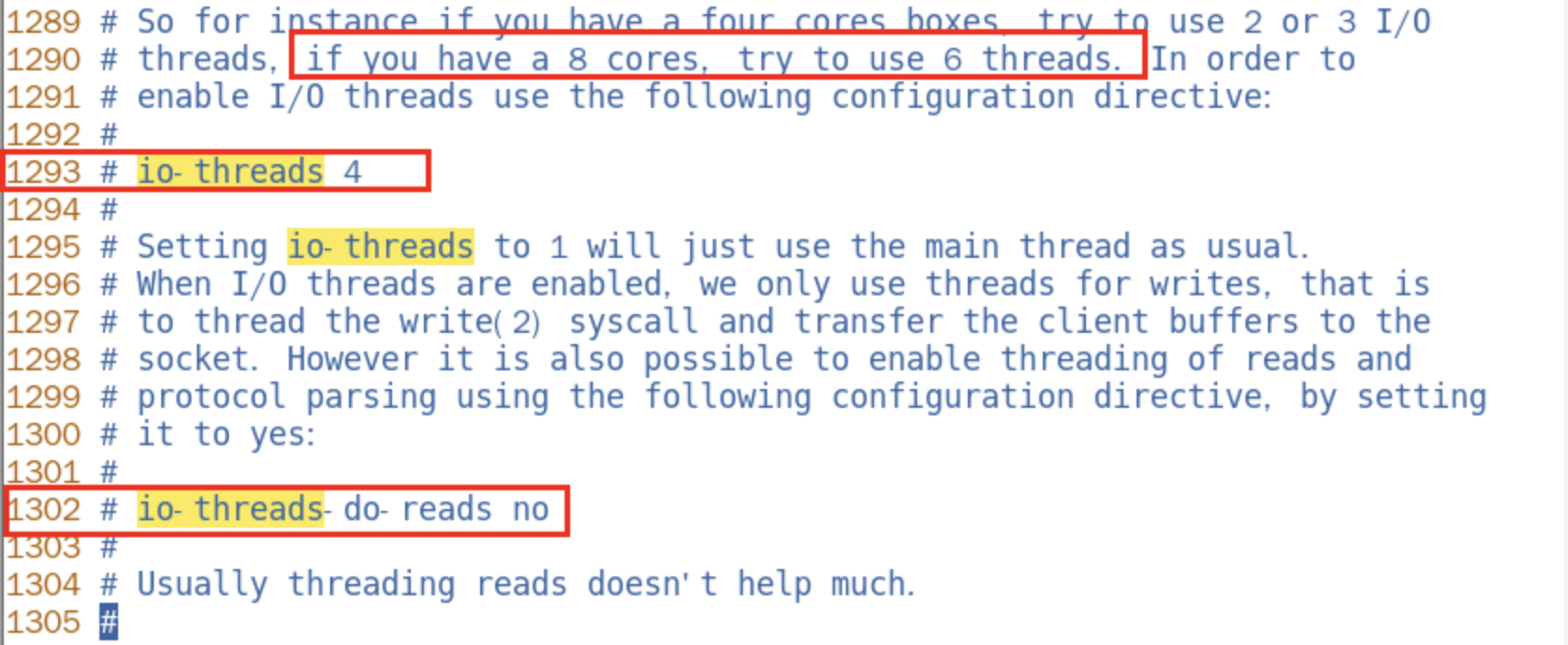

【Redis】线程问题

文章目录单线程版本演化工作流程为什么逐渐又加入了多线程特性?影响Redis性能的主要因素->网络I/O多线程工作流程Unix网络编程中的五种I/O模型I/O多路复用工作原理:select、poll、epoll为什么Redis快单线程与多线程的比较配置文件开启多线程单线程 版本演化 Re…...

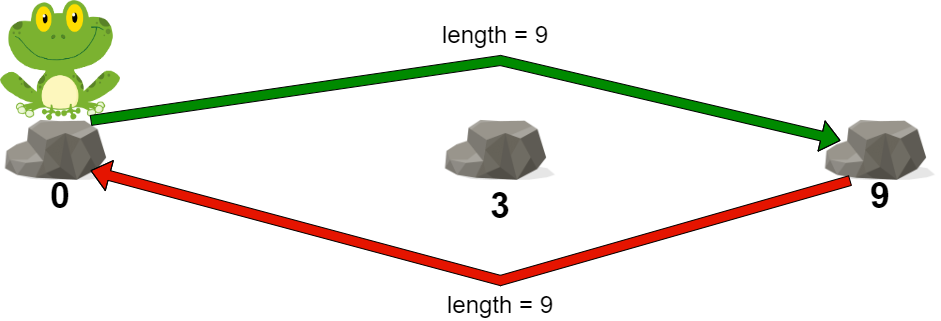

【算法题】2498. 青蛙过河 II

题目: 给你一个下标从 0 开始的整数数组 stones ,数组中的元素 严格递增 ,表示一条河中石头的位置。 一只青蛙一开始在第一块石头上,它想到达最后一块石头,然后回到第一块石头。同时每块石头 至多 到达 一次。 一次…...

【新2023Q2押题JAVA】华为OD机试 - 整理扑克牌

最近更新的博客 华为od 2023 | 什么是华为od,od 薪资待遇,od机试题清单华为OD机试真题大全,用 Python 解华为机试题 | 机试宝典【华为OD机试】全流程解析+经验分享,题型分享,防作弊指南华为od机试,独家整理 已参加机试人员的实战技巧本篇题解:整理扑克牌 题目 给定一组数…...

【hello C语言】文件操作

目录 1. 什么是文件? 2. 程序文件 3. 数据文件 4. 文件名 5. 文件类型 5.1 二进制文件 5.2 文本文件 5.3 数据在内存中的存储 6. 文件缓冲区 7. 文件指针 8. 文件的打开和关闭 9. 文件的顺序读写 10. 文件的随机读写 10.1 fseek:根据文件指针的位置和偏移…...

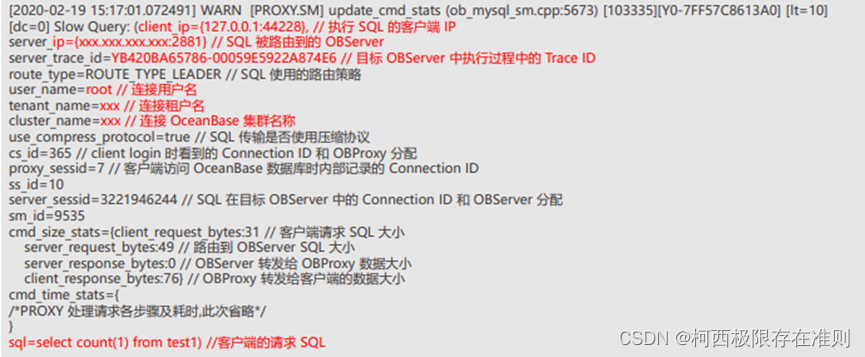

OBCP第八章 OB运维、监控与异常处理-数据库监控

系统监控视图:系统视图 OceanBase 数据库为多租户架构,租户分为两种类型:普通租户以及 sys 租户。OceanBase 数据库系统表都存储在 sys 租户,且主键中存储租户号(tenant_id),区分每个租户的内容…...

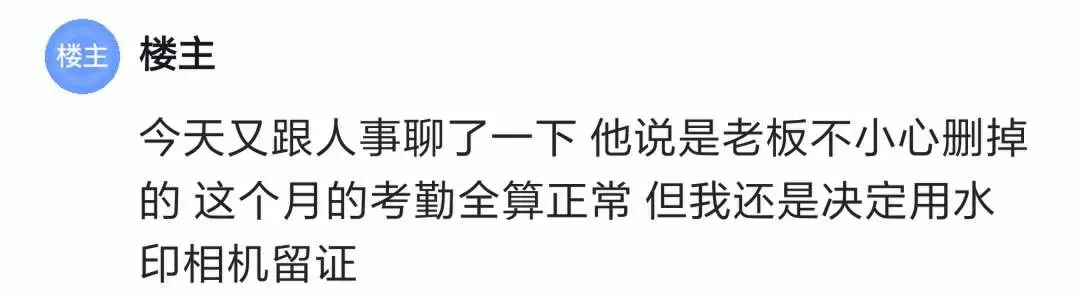

已经提了离职,还有一周就走,公司突然把我移出企业微信,没法考勤打卡, 还要继续上班吗?...

黎明前的黑暗最容易出事,离职前的几天也最容易出幺蛾子,比如下面这位网友的遭遇:已经提了离职,还有一周就正式离职了,公司突然把我移出企业微信,没法考勤打卡了, 还要继续上班吗?该怎…...

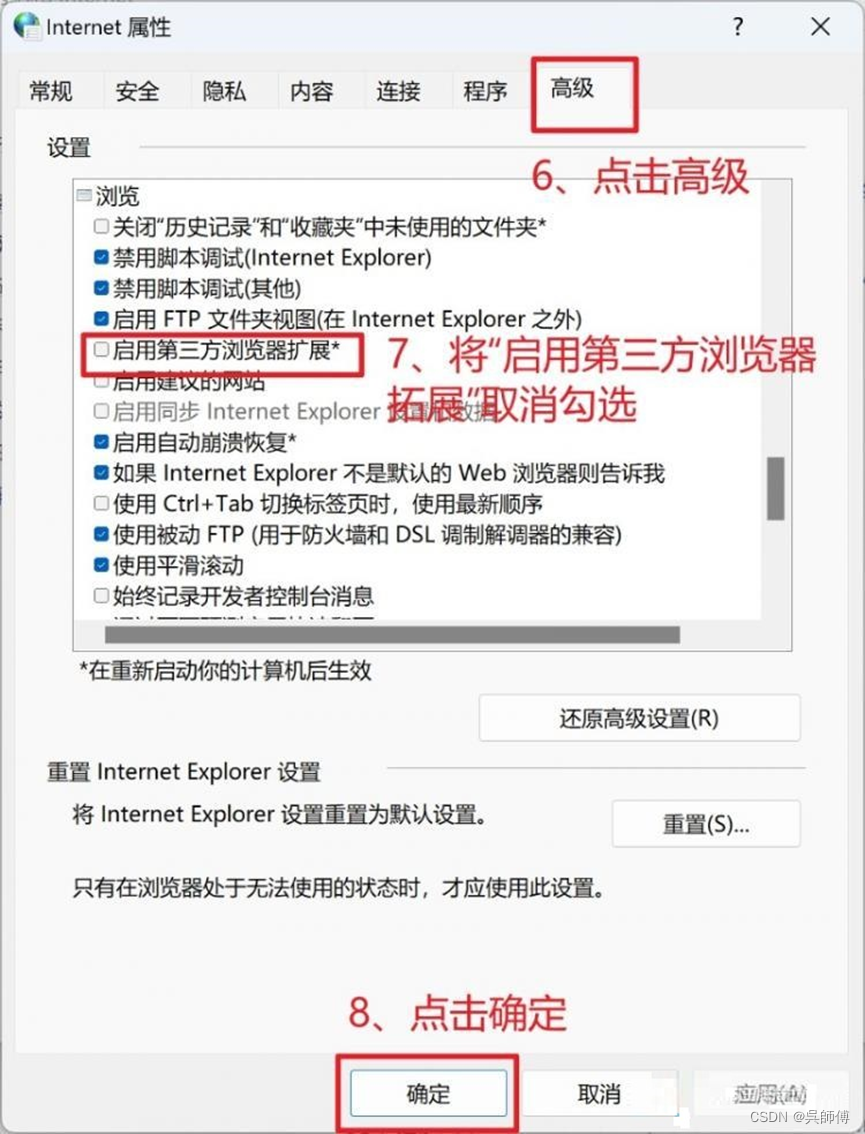

Win11启用IE方法

呉師傅 Win11是微软目前的最新系统,尽管该系统非常不错,但是还是有很多不一样的地方,有的用户发现Win11没有了IE浏览器,那么Win11没有IE浏览器怎么办呢,有的旧网页需要IE浏览器才能进入,下面就给大家提供一…...

有人靠ChatGPT 狂赚200W !有人到现在,连账号都没开通......

作者| Mr.K 编辑| Emma来源| 技术领导力(ID:jishulingdaoli)互联网风水轮流转,当初元宇宙盛极一时之际,在一些知识付费平台上,任何一个关于元宇宙的课程或培训,都很热销,有一定号召力的博主,登…...

GLM-4.1V-9B-Base行业落地:建筑图纸局部区域语义理解与标注建议

GLM-4.1V-9B-Base行业落地:建筑图纸局部区域语义理解与标注建议 1. 建筑行业的AI视觉理解需求 建筑设计和施工过程中,图纸理解与标注是一项耗时且容易出错的工作。传统方式需要经验丰富的工程师手动识别图纸中的各个元素,不仅效率低下&…...

手把手教你:5分钟为你的静态网站嵌入AnythingLLM智能聊天机器人

5分钟为静态网站集成AnythingLLM智能聊天室的实战指南 你是否想过在自己的个人博客或产品官网上添加一个能回答访客问题的AI助手?就像那些科技公司官网右下角弹出的智能客服一样。今天我要分享的,是如何用AnythingLLM在5分钟内为任何静态网站嵌入一个私有…...

扩散浓度曲线计算:从实例看 Pandat 代算与自行操作

扩散浓度曲线计算(Pandat代算或自己操作) 实例33: Al-4.06at%Mg/Al扩散偶在781K下退火36960s,Mg元素浓度随距离的变化曲线及实验数据对比如图a所示;Al-11at%Mg/Al扩散偶在773K下退火86400s,Mg元素浓度随距离的变化曲线及实验对比如图b所示&am…...

AI赋能情感短视频:5分钟打造电影级氛围感剪辑全攻略

深夜收到粉丝私信:“同样的素材,为什么专业博主的视频能让人眼眶湿润,我的却像流水账?”这个问题击中了短视频创作的核心痛点——氛围感缺失。传统剪辑需要导演思维专业技巧数小时打磨,而如今,借助AI工具&a…...

PredRNN++:从单元到系统,逐层拆解与实战解析

1. PredRNN核心单元拆解 PredRNN作为视频预测领域的里程碑模型,其核心创新在于Causal LSTM和GHU两大单元的设计。我们先从代码层面看看它们如何运作。 1.1 Causal LSTM的三明治结构 打开CausalLSTMCell.py文件,你会发现这个单元像三明治一样分为三层&…...

Jimeng LoRA在人工智能领域的创新应用:从理论到实践

Jimeng LoRA在人工智能领域的创新应用:从理论到实践 当AI模型能够像数字滤镜一样精准适配不同风格,人工智能的创作边界正在被重新定义。 1. 重新认识Jimeng LoRA:不只是微调,而是风格进化 Jimeng LoRA的出现彻底改变了我们对模型…...

Linux 内核中的内存管理:从物理内存到虚拟内存

Linux 内核中的内存管理:从物理内存到虚拟内存 引言 作为一名深耕操作系统和嵌入式开发的工程师,我深知资源管理的重要性。在系统开发中,合理的资源管理可以提高系统的性能和可靠性。在 Linux 内核中,内存管理是一个核心组件&…...

音频工程师必看:奈奎斯特采样定理在实际录音中的5个常见误区

音频工程师必看:奈奎斯特采样定理在实际录音中的5个常见误区 在专业音频制作领域,采样率设置是决定录音质量的基础性环节。许多工程师虽然熟悉44.1kHz或48kHz这些标准数字,却对背后的奈奎斯特采样定理存在认知偏差。这些误解轻则导致后期处理…...

这个插件使postgresql能访问ducklake数据湖。

存储库地址:https://github.com/relytcloud/pg_ducklake 拉取docker镜像 sudo docker pull docker.1ms.run/pgducklake/pgducklake:18-main 输入密码 18-main: Pulling from pgducklake/pgducklake d997cc310c98: Pull complete b5ed69009603: Pull compl…...

2026别错过!降AI率工具深度测评与推荐

2026年真正好用的AI论文降重与改写工具,核心看降重效果、去AI味、格式保留、学术适配四大指标。综合实测,千笔AI、ThouPen、豆包、DeepSeek、Grammarly 是当前最值得推荐的梯队,覆盖从免费到付费、从中文到英文、从文科到理工的全场景需求。 …...