FPGA图像处理之三行缓存

文章目录

- 一、前言

- 二、FPGA实现三行缓存的架构

- 三、Verilog代码实现

- 四、仿真验证

- 五、输入图像数据进行仿真验证

一、前言

在 FPGA 做图像处理时,行缓存是一个非常重要的一个步骤,因为图像输入还有输出都是一行一行进行的,即处理完一行后再处理下一行。行缓存可以存储当前行和前一行的数据以及多行的数据,使得在处理当前行时能够方便地访问周围像素。许多图像处理的算法都需要几行的图像数据进行处理,因此行缓存是非常重要的,本文实现三行缓存,多行缓存的思想也是一致的。

二、FPGA实现三行缓存的架构

由于图像数据一般都是从上到下从左到右一个一个输入进来,因此我们优先考虑使用FIFO,先进先出。按照一般想法,我们只需要三个FIFO,每个FIFO存储一行数据即可实现三行缓存,这里可以节省资源只使用两个FIFO实现,具体实现框框架如下:

开始时,图像数据的第0行写入到FIFO1中,图像数据的第1行写入到FIFO2中。

当第2行数据到来时写入到FIFO2中,同时输出写入的数据作为第二行;同时读出FIFO2中的数据写入到FIFO1中,并输出作为第一行,同时读出FIFO1中的数据输出作为第0行。

同理,当第三行数据来临时写入到FIFO2中,同时输出写入数据作为第二行,再同时读出FIFO2中的数据写入到FIFO1中并输出作为第一行,同时读出FIFO2中的数据输出作为第0行。后面的行以此类推。

三、Verilog代码实现

先看输入接口,输入为像素数据和有效信号,输出为三行数据以及有效信号。

input sys_clk ,input sys_rst ,input [23:0] i_img_data ,input i_img_data_valid ,output [23:0] o_img_data_1line ,output [23:0] o_img_data_2line ,output [23:0] o_img_data_3line ,output o_img_data_valid

再次例化两个FIFO,位宽就为一个像素位宽,深度为一行中最多的像素数量。

img_line_buffer_fifo u0_img_line_buffer_fifo (.clk (sys_clk ), // input wire clk.srst (sys_rst ), // input wire srst.din (fifo1_wr_data ), // input wire [23 : 0] din.wr_en(fifo1_wr_en ), // input wire wr_en.rd_en(rd_en ), // input wire rd_en.dout (fifo1_q ), // output wire [23 : 0] dout.full (), // output wire full.empty() // output wire empty

);img_line_buffer_fifo u1_img_line_buffer_fifo (.clk (sys_clk ), // input wire clk.srst (sys_rst ), // input wire srst.din (fifo2_wr_data ), // input wire [23 : 0] din.wr_en(fifo2_wr_en ), // input wire wr_en.rd_en(rd_en ), // input wire rd_en.dout (fifo2_q ), // output wire [23 : 0] dout.full (), // output wire full.empty() // output wire empty

);

然后根据架构图编写出剩下的代码,编写仿真代码。

四、仿真验证

仿真我们先设置图像宽度为50*50,这样仿真可以跑快一点,然后写入数据流为每次都是0-49循环。就像一幅图像的第0行数据是0-49,第1行的数据也是0-49,每一行的数据都是0-49。按照想法,我们每次输出的数据就是前三行的像素,也就是3行的 0-49数据,仿真代码如下:

`timescale 1ns / 1psmodule tb_img_3line_buffer();reg sys_clk ;

reg sys_rst ;

reg i_img_data_valid ;

reg [23:0] i_img_data ;

reg [12:0] cnt ;

wire [23:0] o_img_data_1line ;

wire [23:0] o_img_data_2line ;

wire [23:0] o_img_data_3line ;

wire o_img_data_valid ;initial beginsys_clk =0;sys_rst = 1;i_img_data_valid = 0;i_img_data = 'd0;#200;sys_rst = 0;

endalways #5 sys_clk = ~sys_clk;always @(posedge sys_clk) beginif(sys_rst == 1'b1)i_img_data_valid <= 1'b0;else if(cnt == 49)i_img_data_valid <= 1'b0;elsei_img_data_valid <= 1'b1;

endalways @(posedge sys_clk) beginif(sys_rst == 1'b1)cnt <= 'd0;else if(cnt == 49)cnt <= 'd0;else if(i_img_data_valid == 1'b1)cnt <= cnt + 1'b1;elsecnt <= cnt;

endalways @(posedge sys_clk) beginif(sys_rst == 1'b1)i_img_data <= 'd0;else if(i_img_data == 49)i_img_data <= 'd0;else if(i_img_data_valid == 1'b1)i_img_data <= i_img_data + 1'b1;elsei_img_data <= i_img_data;

endimg_3line_buffer#(.IMG_WIDTH ( 50 ),.IMG_HEIGHT ( 50 )

)u_img_3line_buffer(.sys_clk ( sys_clk ),.sys_rst ( sys_rst ),.i_img_data ( i_img_data ),.i_img_data_valid ( i_img_data_valid ),.o_img_data_1line ( o_img_data_1line ),.o_img_data_2line ( o_img_data_2line ),.o_img_data_3line ( o_img_data_3line ),.o_img_data_valid ( o_img_data_valid )

);endmodule运行仿真

可以看到写入的每一行数据都是0-49,写入两行后,开始输出数据。

我们可以看到输出的三行数据都是0-49的数据。符合预期。我们修改一下仿真代码,写入2500个数据,对应50*50的图像大小,数据为0-2499,这样第0行的数据就是0-49,第1行的数据就是50-99,第2行的数据就是100-149,第3行的数据就是150-199。输出的数据就应该是(0,50,100),(1,51,101)以此类推,仿真代码如下:

`timescale 1ns / 1psmodule tb_img_3line_buffer();reg sys_clk ;

reg sys_rst ;

reg i_img_data_valid ;

reg [23:0] i_img_data ;

reg [12:0] cnt ;

wire [23:0] o_img_data_1line ;

wire [23:0] o_img_data_2line ;

wire [23:0] o_img_data_3line ;

wire o_img_data_valid ;initial beginsys_clk =0;sys_rst = 1;i_img_data_valid = 0;i_img_data = 'd0;#200;sys_rst = 0;

endalways #5 sys_clk = ~sys_clk;always @(posedge sys_clk) beginif(sys_rst == 1'b1)i_img_data_valid <= 1'b0;else if(cnt == 2499)i_img_data_valid <= 1'b0;elsei_img_data_valid <= 1'b1;

endalways @(posedge sys_clk) beginif(sys_rst == 1'b1)cnt <= 'd0;else if(cnt == 2499)cnt <= 'd0;else if(i_img_data_valid == 1'b1)cnt <= cnt + 1'b1;elsecnt <= cnt;

endalways @(posedge sys_clk) beginif(sys_rst == 1'b1)i_img_data <= 'd0;else if(i_img_data == 2499)i_img_data <= 'd0;else if(i_img_data_valid == 1'b1)i_img_data <= i_img_data + 1'b1;elsei_img_data <= i_img_data;

endimg_3line_buffer#(.IMG_WIDTH ( 50 ),.IMG_HEIGHT ( 50 )

)u_img_3line_buffer(.sys_clk ( sys_clk ),.sys_rst ( sys_rst ),.i_img_data ( i_img_data ),.i_img_data_valid ( i_img_data_valid ),.o_img_data_1line ( o_img_data_1line ),.o_img_data_2line ( o_img_data_2line ),.o_img_data_3line ( o_img_data_3line ),.o_img_data_valid ( o_img_data_valid )

);endmodule运行仿真

验证完成和预期一致,后续一些图像处理算法需要用到这个行缓存。

五、输入图像数据进行仿真验证

现在我们在仿真中输入一张图片,然后通过三行缓存输出,每次只取出第一行的数据写入到新的图片中:

可以看出输出的图像和输入图像一模一样,文件大小也是一模一样,因此三行缓存是没问题的。

相关文章:

FPGA图像处理之三行缓存

文章目录 一、前言二、FPGA实现三行缓存的架构三、Verilog代码实现四、仿真验证五、输入图像数据进行仿真验证 一、前言 在 FPGA 做图像处理时,行缓存是一个非常重要的一个步骤,因为图像输入还有输出都是一行一行进行的,即处理完一行后再处理…...

10月15日,每日信息差

第一、《哈利・波特与魔法石》在中国内地总票房突破 3 亿元,包括 2002 年首映的 5600 万,2020 年重映的 1.923 亿,以及 2024 年重映的 5170 万。 第二、全国铁路实施新货物列车运行图,增开城际班列至 131 列,多式联运…...

4G、5G通信中,“网络侧“含义

在5G通信中,"网络侧"这个术语可以指代不同的网络元素,具体取决于上下文。通常,网络侧可以包括以下两个主要部分: 基站(gNB): 基站是无线接入网(RAN)的一部分&a…...

spring boot核心理解-各种starter

理解 Spring Boot 的 Starter 机制以及如何选择和使用各种 starter,是开发 Spring Boot 应用的重要一环。Spring Boot Starter 是一组方便的依赖组合,用于简化 Spring 项目中的依赖管理。它们可以帮助开发者快速引入所需的库和自动配置,从而加…...

解决海外社媒风控问题的工具——云手机

随着中国企业逐步进入海外市场,海外社交媒体的风控问题严重影响了企业的推广效果与账号运营。这种背景下,云手机作为一种新型技术解决方案,正日益成为企业应对海外社媒风控的重要工具。 由于海外社媒的严格监控,企业经常面临账号流…...

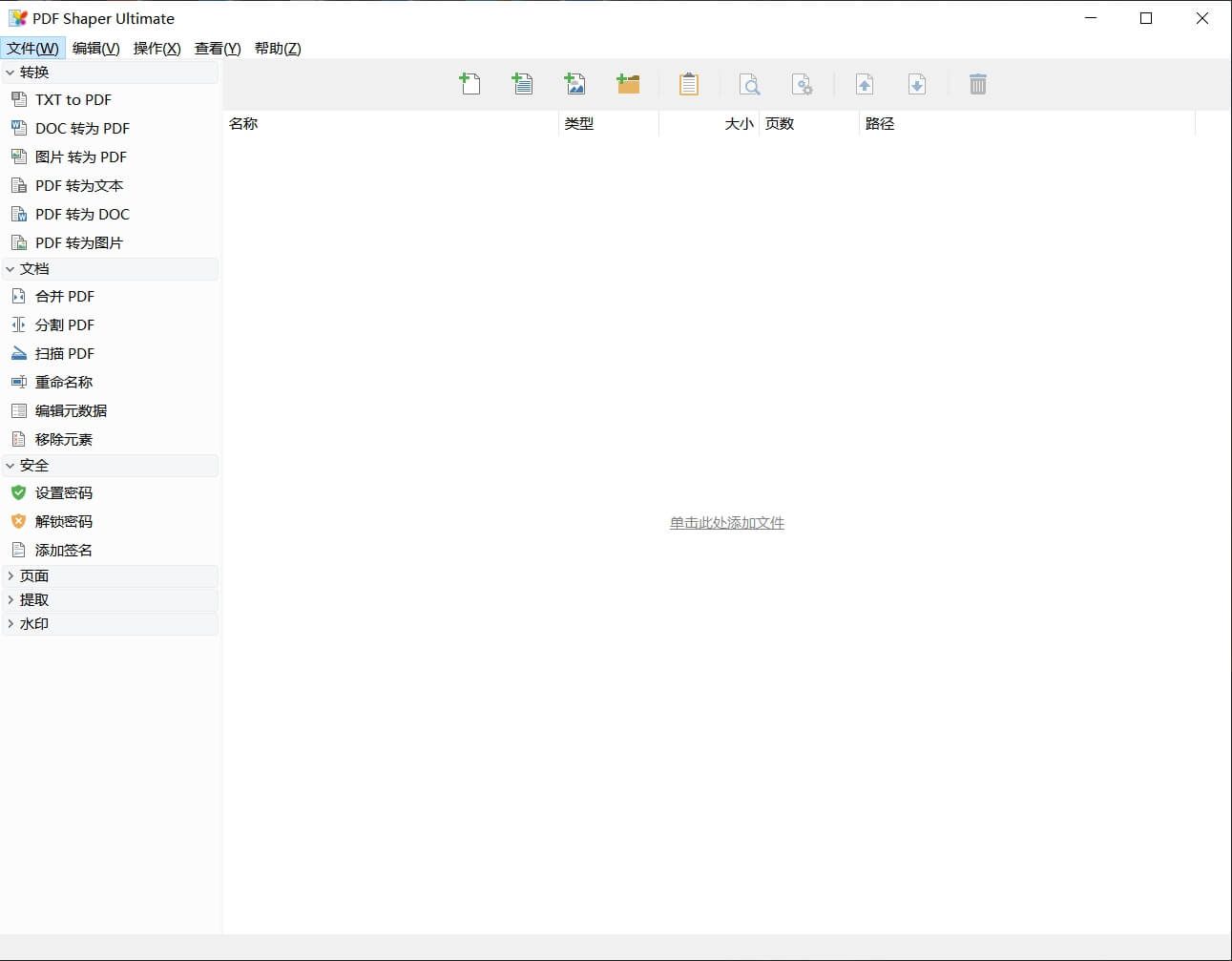

全能PDF工具集 | PDF Shaper Ultimate v14.6 便携版

软件简介 PDF Shaper是一款功能强大的PDF工具集,它提供了一系列用于处理PDF文档的工具。这款软件使用户能够轻松地转换、分割、合并、提取页面以及旋转和加密PDF文件。PDF Shaper的界面简洁直观,使得即使是新手用户也能快速上手。它支持广泛的功能&…...

Maven入门

Maven Maven Wrapper 版本一致性: Maven Wrapper 允许你在项目中指定一个特定的 Maven 版本。这意味着所有开发人员和 CI/CD 环境都将使用相同版本的 Maven,从而避免由于版本不一致导致的问题。 简化设置: 新开发者克隆项目时,…...

Chromium 中window.DOMParser接口说明c++

一、DOMParser DOMParser 可以将存储在字符串中的 XML 或 HTML 源代码解析为一个 DOM Document。 备注: XMLHttpRequest 支持从 URL 可寻址资源解析 XML 和 HTML,在其response 属性中返回Document。 你可以使用XMLSerializer 接口执行相反的操作 - 将…...

linux 安装gitlab

安装环境 CentOS 7.7 (centos6.10会报错)2g内存防火墙关闭 安装步骤: 1 安装gitlab # yum install -y git curl policycoreutils-python openssh-server # 安装依赖 # wget https://mirrors.tuna.tsinghua.edu.cn/gitlab-ce/yum/el7/gitlab-ce-10.2.2-ce…...

java基础(5)继承与多态

目录 编辑 1.前言 2.正文 2.1继承 2.1.1继承概念 2.1.2继承语法 2.1.3子类访问父类 2.1.4super关键字 2.2多态 2.2.1多态概念 2.2.2多态条件 2.2.3重写 2.2.4向上转型与向下转型 2.2.5为什么要使用多态 3.小结 1.前言 哈喽大家好啊,今天继续来为大…...

Flink消费Kafka实时写入Doris

本文模拟实际生产环境,通过FileBeat采集日志信息到Kafka,再通过Flink消费Kafka实时写入Doris。 文章目录 Filebeat采集日志到KafkaFlink消费Kafka实时写入Doris总结 Filebeat采集日志到Kafka 常见的日志采集工具有以下几种:Flume、Logstash和…...

实现Web QQ音乐打开现有新标签页切换音乐

若没有打开播放音乐标签页,则打开新标签页播放所选音乐如果已打开新标签页,则直接切换所选音乐 pageA.vue <script setup lang"ts"> const tab2 ref<any>(null); const router useRouter();interface Track {id: number;name: …...

----时钟结构(通俗版))

从底层结构开始学习FPGA(15)----时钟结构(通俗版)

目录 0、前言 1、IO Bank和Clock Region(时钟区域)是一个东西吗? 2、时钟输入管脚 3、时钟架构 3.1、全局时钟BUFG 3.2、水平时钟BUFH 3.3、IO时钟BUFIO 3.4、区域时钟BUFR/BUFMR 4、总结 《从底层结构开始学习FPGA》目录与传送门 0、前言 我思来想去,总觉…...

MacOS Sublime Text 解决中乱码

1. 安装Package Control 官方安装指南 手动安装 通过以此点击菜单 Sublime Text > Preferences > Browse Packages 打开Packages目录找到Packages的同级目录Installed Packages下载PackageControl.sublime-package并保存到Installed Packages中在菜单 Sublime Text &g…...

Python画笔案例-084 绘制 3D立方体

1、绘制 3D立方体 通过 python 的turtle 库绘制 3D立方体,如下图: 2、实现代码 绘制 3D立方体,以下为实现代码: import turtle import timeviewfactor = 150 xshift = 0 yshift = 0 zshift = 50...

“八股文”面试:助力、阻力还是空谈?

在当今的IT行业,面试程序员时提及“八股文”已成为一种普遍现象。所谓“八股文”,通常指的是一系列固定的、标准化的面试问题及其解答,这些问题往往涵盖了计算机科学和软件工程的基础知识,以及一些流行的技术框架和算法。然而&…...

如何实现弹出式窗口

文章目录 1 概念介绍2 使用方法3 示例代码我们在上一章回中介绍了Sliver综合示例相关的内容,本章回中将介绍PopupMenuButton组件.闲话休提,让我们一起Talk Flutter吧。 1 概念介绍 我们在本章回中介绍的PopupMenuButton组件位于AppBar右侧,通常显示三个圆点图标,点击该图标…...

Lua 函数

Lua 函数 Lua 是一种轻量级的编程语言,广泛用于游戏开发、脚本编写和其他应用程序中。在 Lua 中,函数是一等公民,这意味着它们可以被存储在变量中,作为参数传递给其他函数,以及作为其他函数的返回值。本文将详细介绍 …...

HTML_文本标签

概念: 1、用于包裹:词汇、短语等。 2、通常写在排版标签里面。 3、排版标签更宏观(大段的文字),文本标签更微观(词汇、短语)。 4、文本标签通常都是行内元素。 常用的文本标签 标签名 全称 标签语义em Emphasized 加重(文本)。要着重阅…...

基于SpringBoot+Vue+uniapp的诗词学习系统的详细设计和实现(源码+lw+部署文档+讲解等)

详细视频演示 请联系我获取更详细的演示视频 项目运行截图 技术框架 后端采用SpringBoot框架 Spring Boot 是一个用于快速开发基于 Spring 框架的应用程序的开源框架。它采用约定大于配置的理念,提供了一套默认的配置,让开发者可以更专注于业务逻辑而不…...

计算机毕业设计springboot校园文化社区视频网站 基于SpringBoot的校园文化交流短视频平台 SpringBoot框架下的高校文化分享与视频互动系统

计算机毕业设计springboot校园文化社区视频网站94nso9 (配套有源码 程序 mysql数据库 论文)本套源码可以先看具体功能演示视频领取,文末有联xi 可分享在"互联网校园"理念全面渗透的今天,视频已成为大学生记录生活、传播…...

APScheduler避坑指南:解决定时任务重复执行和时区问题的5种实战方案

APScheduler生产级实战:彻底解决定时任务重复执行与时区混乱的终极方案 凌晨三点,服务器告警铃声突然响起——监控系统显示同一批数据处理任务在短时间内被重复执行了17次。这不是科幻场景,而是某电商平台在使用APScheduler时遇到的真实生产事…...

FLUX.1-dev FP8量化模型:让AI绘画不再依赖高端显卡

FLUX.1-dev FP8量化模型:让AI绘画不再依赖高端显卡 【免费下载链接】flux1-dev 项目地址: https://ai.gitcode.com/hf_mirrors/Comfy-Org/flux1-dev 还在为显卡显存不足而无法体验最新AI绘画技术而烦恼吗?FLUX.1-dev FP8量化模型正是为你量身打造…...

保姆级教程:CLIP-GmP-ViT-L-14图文匹配工具一键部署,小白也能玩转AI识图

保姆级教程:CLIP-GmP-ViT-L-14图文匹配工具一键部署,小白也能玩转AI识图 你是不是经常好奇,AI到底是怎么看懂图片的?给它一张照片和几个文字描述,它怎么知道哪个描述最贴切?今天,我就带你亲手搭…...

Hunyuan-MT-7B应用案例:国际展会AI同传助手系统后端架构设计

Hunyuan-MT-7B应用案例:国际展会AI同传助手系统后端架构设计 1. 项目背景与需求分析 国际展会现场的同声传译一直是技术难题。传统人工翻译成本高昂,且难以覆盖所有语言组合。随着多语言大模型的发展,AI同传系统成为可行的解决方案。 Huny…...

Phi-3-Mini-128K企业级应用:基于MCP协议构建安全可控的AI工具链

Phi-3-Mini-128K企业级应用:基于MCP协议构建安全可控的AI工具链 最近和几个在企业里做技术管理的朋友聊天,大家不约而同地提到了同一个烦恼:看着外面各种AI模型能力越来越强,心里痒痒的,真想引入到自己的业务流程里&a…...

)

Node RED实战:5分钟搞定MQTT消息发布与订阅(附EMQX配置)

Node RED与MQTT实战:从零构建物联网消息系统 1. 为什么选择Node RED与MQTT组合? 物联网开发领域一直存在一个核心挑战:如何快速搭建可靠的消息通信系统而不陷入底层协议实现的泥潭。这正是Node RED与MQTT这对黄金组合的价值所在——它们让开发…...

TAICHI-flet终极排障指南:从新手到高手的完整解决方案

TAICHI-flet终极排障指南:从新手到高手的完整解决方案 【免费下载链接】TAICHI-flet 基于flet的一款windows桌面应用,实现了浏览图片、音乐、小说、漫画、各种资源的功能。 项目地址: https://gitcode.com/GitHub_Trending/ta/TAICHI-flet TAICHI…...

Pixel Fashion Atelier实操手册:批量生成时利用CSV导入多组Enchantment参数

Pixel Fashion Atelier实操手册:批量生成时利用CSV导入多组Enchantment参数 1. 引言:为什么需要批量生成功能 在时尚设计领域,设计师经常需要快速生成多个不同风格的服装设计方案。传统方式需要逐个输入参数、等待生成、再调整参数…...

)

【PAT甲级真题】- PAT Judge (25)

题目来源 PAT Judge (25) 题目描述点击链接自行查看 注意点: 排序:先按总分再按解决题目数再按id 思路简介 思路很简单,直接模拟即可 但是坑倒是很多 主要是要区分编译没过和过了但是得 0 分 方案: 初始化时分数为 -2 编译没…...