Vivado - Aurora 8B/10B IP

目录

1. 简介

2. 设计调试

2.1 Physical Layer

2.2 Link Layer

2.3 Receiver

2.4 IP 接口

2.5 调试过程

2.5.1 Block Design

2.5.2 释放 gt_reset

2.5.3 观察数据

3. 实用技巧

3.1 GT 坐标与布局

3.1.1 选择器件并进行RTL分析

3.1.2 进入平面设计

3.1.3 收发器布局(基础IP)

3.1.4 收发器布局(平面视图)

3.1.5 示例 aurora(zcu106)

3.1.6 示例 aurora(zcu102)

3.1.7 时钟区域与Quad区域

3.2 共享逻辑

3.3 例化模板

3.4 Block Design TCL

4. 总结

1. 简介

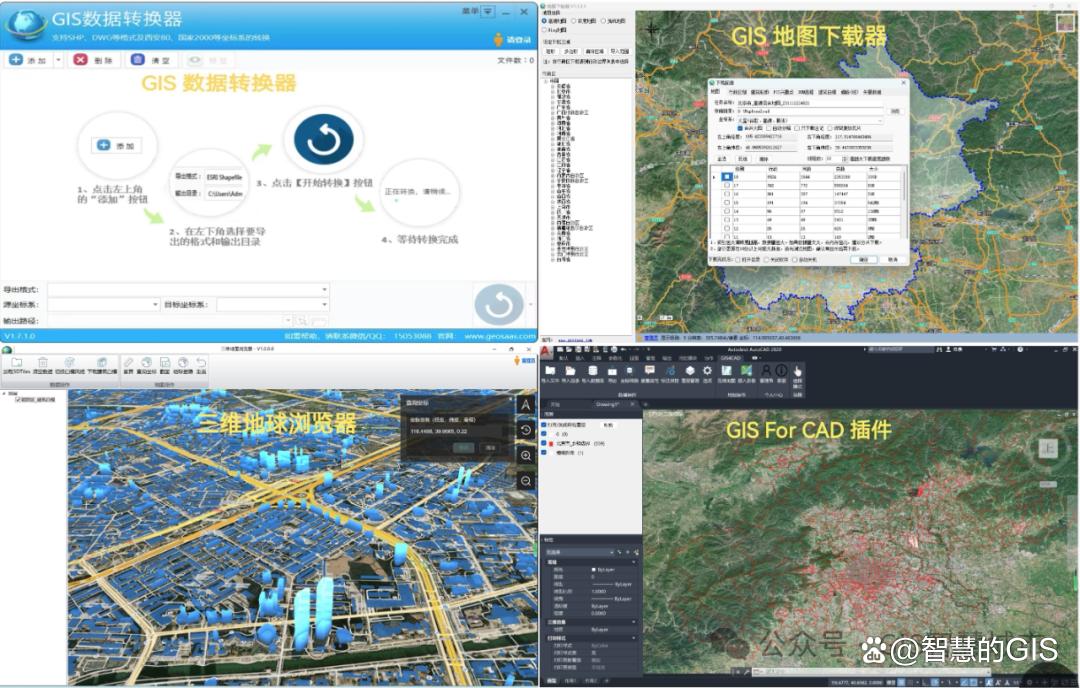

本文介绍在 Block Design 中添加 Aurora 8B/10B IP 并加以调试。

- 使用 Streaming 接口

- 使用 VIO 控制回环方式

- 探究收发器的位置信息

- 共享逻辑和例化模板

- 附带 Block Design 的 TCL 代码

2. 设计调试

2.1 Physical Layer

- INIT clk

由于在 gt_reset 断言时 user_clk 会停止工作,因此需要 init_clk_in 提供时钟信号来确保系统的正常复位过程。

2.2 Link Layer

接口(帧与数据流)

Aurora 8B/10B Core 在连接到 Aurora 通道对象时会自动初始化通道,并以帧或数据流的形式在通道中自由传递数据。

Aurora 帧可以是任意大小,并且可以随时中断。有效数据字节之间的间隙会自动用空闲填充,以保持锁定并防止电磁干扰。流量控制可用于降低传入数据的速率或通过通道发送简短的高优先级消息。

流是单个、无休止的帧。在没有数据的情况下,会传输空闲信号以保持链路处于活动状态。 Aurora 8B/10B内核使用 8B/10B 编码规则检测单位错误和大多数多位错误。过多的位错误、断开连接或设备故障会导致内核重置并尝试重新初始化新通道。

2.3 Receiver

2.4 IP 接口

本示例使用 Block Design 直接连接。

如果还要继续在同一个 Block Design 中添加此 IP,会出现额外端口,用于级联。

重要信号解释:

- channel_up:通道初始化完成,且通道准备好进行数据传输时,生效。

- lane_up:在每个通道成功初始化时进行断言,每个比特代表一个通道。

- user_clk_out:由 Aurora 8B/10B 核心共享的并行时钟(共享逻辑在 IP 中)。

- reset:高电平有效。

- gt_reset:高电平有效。

- loopback:

| Port | Dir | Clock Domain | Description |

|---------------|-----|--------------|----------------------------|

| LOOPBACK[2:0] | In | Async | 000: Normal operation |

| | | | 001: Near-end PCS Loopback |

| | | | 010: Near-end PMA Loopback |

| | | | 011: Reserved |

| | | | 100: Far-end PMA Loopback |

| | | | 101: Reserved |

| | | | 110: Far-end PCS Loopback |《UltraScale Architecture GTH Transceivers User Guide (UG576)》(Table-36)

2.5 调试ZCU106

2.5.1 Block Design

器件:xczu7ev-ffvc1156-2-e

对于 ZCU106 板卡,主要约束为:

set_property PACKAGE_PIN U10 [get_ports GT_DIFF_REFCLK1_0_clk_p]set_property PACKAGE_PIN AH12 [get_ports {CLK_IN_D_0_clk_p[0]}]

set_property IOSTANDARD DIFF_SSTL12 [get_ports {CLK_IN_D_0_clk_p[0]}]set_property IOSTANDARD LVCMOS12 [get_ports ext_reset_in_0]

set_property PACKAGE_PIN AP20 [get_ports ext_reset_in_0]Debug hub 相关约束会自动生成。

2.5.2 释放 gt_reset

通过释放 gt_reset,Aurora IP 将自动建立链接。

2.5.3 观察数据

从 tx_valid 被选中 '1'(数据有效)后,便可从 ILA 中观察到回传的数据了。

由于 tx_valid 是一直为高,回传数据也一直有效,除了收发器周期性发送的控制码期间。

2.6 调试ZCU102

2.6.1 Block Design

Block Design 与 2.5 章节保持一致。不同的是,ZCU102 的时钟输入、复位输入可以使用预先配置的信息,因此只需指定 REFCLK 即可:

set_property PACKAGE_PIN C8 [get_ports GT_DIFF_REFCLK1_0_clk_p]2.6.2 观察数据

3. 实用技巧

3.1 GT 坐标与布局

- 收发器 GTX/GTH/GTY 等位置信息(XxYy)

- 收发器的 Bank 编号怎么确定

- 收发器的 Quad 是指什么

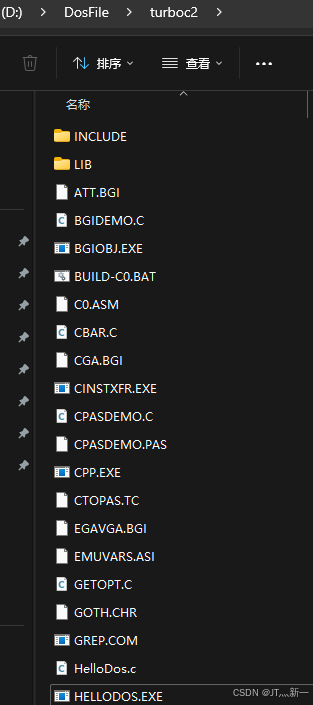

3.1.1 选择器件并进行RTL分析

新建工程时选择,或者在 Project Summary 中选择。

要进行 RTL 分析,需要指定 top module,可以通过创建一个空白 Block Design,然后生成一个空 wraper。

`timescale 1 ps / 1 psmodule design_1_wrapper();design_1 design_1_i();

endmodule然后可以打开 Elaborated Design。

3.1.2 进入平面设计

平面设计,即 Floorplanning 视图。

打开 Elaborated Design 后,可以选择 Floorplanning 视图。

Floorplanning 视图如下:

3.1.3 收发器布局(基础IP)

收发器一般都放置在芯片的边缘,因为其主要功能时与外部设备通讯,这样可以简化 I/O 布线,并减少信号路径的长度,从而降低信号衰减和干扰。

在 Vivado 软件 中,有多种途径可查看到收发器的分布信息,首先演示基础 IP 所展示的信息:

UltraScale FPGAs Transceivers Wizard v1.7

从基础 IP 看到 xczu9eg-ffvb1156-2-e 器件的一些收发器信息:

- 左右两侧各有3个 Quad,12个 Channel

- 每个 Channel 对应有自己的 XxYy 坐标标号

- 每个 Quad 的 Bank 和对应 Pin 的信息

- 在 Physical Resources 中,也可以看到各自资源的位置分布

3.1.4 收发器布局(平面视图)

1)根据资源种类进行筛选

Floorplanning 视图下,通过右侧的 Resource Types 可以筛选视图内容。

2)未启用的 GT 资源

通过筛选 GT transceiver 资源,可以明显观察到有7个 Quad,似乎与基础 IP 描述不符?

放大 Clock Regin X0Y3 这个区域的 Quad 并未启用,故收发器资源有6个可用。

3)公共资源

4)Site Properties

SITE 即不同类型逻辑资源,包括 SLICE/CLBs,这些是基本逻辑元素(BELs)的集合,例如查找表(LUTs)、触发器、多路复用器、以及用于实现快速加法、减法或比较操作的进位逻辑资源。SLICE/CLBs 中包含宽位宽的多路复用器,并有专用的进位链垂直从一个 SLICE 运行到另一个SLICE。

在 Site Properties 中,同样可以看到所有的 Transceivers Wizard 中的信息。

3.1.5 示例 aurora(zcu106)

器件:xczu7ev-ffvc1156-2-e

IP:Aurora 8B10B v11.1

1)需要确认的信息包括:

- Column 位置信息(Column Used)

- Quad 信息(Starting GT Quad)

- Channel信息(Starting GT Lane)

- 参考时钟(GT Refclk Selection)

2)查看原理图

确认如下信息:

- 使用 Channel 0,对应的引脚是 U6、U5

- 参考时钟取自 REFCLK1

在基础 IP 中搜索 Pin 信息:

即可确认位置信息:

- Column 位置信息(Column Used)= right

- Quad 信息(Starting GT Quad)= Quad X0Y3

- Channel信息(Starting GT Lane)= X0Y12

- 参考时钟(GT Refclk Selection)= MGTREFCLK1

3)最终配置如下

3.1.6 示例 aurora(zcu102)

1)原理图

2)GT IP 搜索结果

3)最终配置如下

- Column 位置信息(Column Used)= right

- Quad 信息(Starting GT Quad)= Quad X1Y3

- Channel信息(Starting GT Lane)= X1Y12

- 参考时钟(GT Refclk Selection)= MGTREFCLK0

3.1.7 时钟区域与Quad区域

时钟区域与 GT Quad 区域有各自的位置坐标编码规则,GT Quad 的坐标是跨越时钟区域坐标的,如下图:

- 时钟区域从左到右共4列:X0,X1,X2,X3

- GT Quad 区域只在最左侧和最右侧分布,共2列:Quad_X0,Quad_X1

- Quad_X0 属于时钟区域 X0 中,Quad_X1 属于时钟区域 X3

3.2 共享逻辑

《Aurora 8B/10B LogiCORE IP Product Guide (PG046)》,由于选择共享逻辑选项导致的一些端口变化,增加一些端口。

1)共享逻辑的概念:

Include Shared Logic in Core:将共享逻辑资源包含在 IP 核内部,即所有需要的逻辑资源(如 时钟、复位、缓冲区等)都在 IP 核内部实现。

Include Shared Logic in Example Design:将共享逻辑资源从 IP 核内部移除,并在示例设计中实现。这种方式允许多个 IP 核实例共享同一组逻辑资源。

2)信号变化的原因:

资源共享:当选择共享逻辑时,多个 IP 核实例可能会共享同一组资源。

端口配置:共享逻辑选项会影响到端口的配置。例如,某些时钟和复位信号可能会从 IP 核内部移到外部,以便与其他实例共享。

共享逻辑的连接方法:

3.3 例化模板

通过 IP Sources 可以查看完整的例化模板:

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

aurora_8b10b_0 your_instance_name (.s_axi_tx_tdata (s_axi_tx_tdata ), // input wire [0 : 15] s_axi_tx_tdata.s_axi_tx_tvalid (s_axi_tx_tvalid ), // input wire s_axi_tx_tvalid.s_axi_tx_tready (s_axi_tx_tready ), // output wire s_axi_tx_tready.m_axi_rx_tdata (m_axi_rx_tdata ), // output wire [0 : 15] m_axi_rx_tdata.m_axi_rx_tvalid (m_axi_rx_tvalid ), // output wire m_axi_rx_tvalid.hard_err (hard_err ), // output wire hard_err.soft_err (soft_err ), // output wire soft_err.channel_up (channel_up ), // output wire channel_up.lane_up (lane_up ), // output wire [0 : 0] lane_up.txp (txp ), // output wire [0 : 0] txp.txn (txn ), // output wire [0 : 0] txn.reset (reset ), // input wire reset.gt_reset (gt_reset ), // input wire gt_reset.loopback (loopback ), // input wire [2 : 0] loopback.rxp (rxp ), // input wire [0 : 0] rxp.rxn (rxn ), // input wire [0 : 0] rxn.gt0_drpaddr (gt0_drpaddr ), // input wire [9 : 0] gt0_drpaddr.gt0_drpen (gt0_drpen ), // input wire gt0_drpen.gt0_drpdi (gt0_drpdi ), // input wire [15 : 0] gt0_drpdi.gt0_drprdy (gt0_drprdy ), // output wire gt0_drprdy.gt0_drpdo (gt0_drpdo ), // output wire [15 : 0] gt0_drpdo.gt0_drpwe (gt0_drpwe ), // input wire gt0_drpwe.power_down (power_down ), // input wire power_down.tx_lock (tx_lock ), // output wire tx_lock.tx_resetdone_out (tx_resetdone_out ), // output wire tx_resetdone_out.rx_resetdone_out (rx_resetdone_out ), // output wire rx_resetdone_out.link_reset_out (link_reset_out ), // output wire link_reset_out.init_clk_in (init_clk_in ), // input wire init_clk_in.user_clk_out (user_clk_out ), // output wire user_clk_out.pll_not_locked_out (pll_not_locked_out ), // output wire pll_not_locked_out.sys_reset_out (sys_reset_out ), // output wire sys_reset_out.gt_refclk1_p (gt_refclk1_p ), // input wire gt_refclk1_p.gt_refclk1_n (gt_refclk1_n ), // input wire gt_refclk1_n.sync_clk_out (sync_clk_out ), // output wire sync_clk_out.gt_reset_out (gt_reset_out ), // output wire gt_reset_out.gt_refclk1_out (gt_refclk1_out ), // output wire gt_refclk1_out.gt_powergood (gt_powergood ) // output wire [0 : 0] gt_powergood

);

// INST_TAG_END ------ End INSTANTIATION Template ---------3.4 Block Design TCL

################################################################

# This is a generated script based on design: design_1

#

# Though there are limitations about the generated script,

# the main purpose of this utility is to make learning

# IP Integrator Tcl commands easier.

################################################################namespace eval _tcl {

proc get_script_folder {} {set script_path [file normalize [info script]]set script_folder [file dirname $script_path]return $script_folder

}

}

variable script_folder

set script_folder [_tcl::get_script_folder]################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2022.1

set current_vivado_version [version -short]if { [string first $scripts_vivado_version $current_vivado_version] == -1 } {puts ""catch {common::send_gid_msg -ssname BD::TCL -id 2041 -severity "ERROR" "This script was generated using Vivado <$scripts_vivado_version> and is being run in <$current_vivado_version> of Vivado. Please run the script in Vivado <$scripts_vivado_version> then open the design in Vivado <$current_vivado_version>. Upgrade the design by running \"Tools => Report => Report IP Status...\", then run write_bd_tcl to create an updated script."}return 1

}################################################################

# START

################################################################# To test this script, run the following commands from Vivado Tcl console:

# source design_1_script.tcl# If there is no project opened, this script will create a

# project, but make sure you do not have an existing project

# <./myproj/project_1.xpr> in the current working folder.set list_projs [get_projects -quiet]

if { $list_projs eq "" } {create_project project_1 myproj -part xczu7ev-ffvc1156-2-eset_property BOARD_PART xilinx.com:zcu106:part0:2.6 [current_project]

}# CHANGE DESIGN NAME HERE

variable design_name

set design_name design_1# If you do not already have an existing IP Integrator design open,

# you can create a design using the following command:

# create_bd_design $design_name# Creating design if needed

set errMsg ""

set nRet 0set cur_design [current_bd_design -quiet]

set list_cells [get_bd_cells -quiet]if { ${design_name} eq "" } {# USE CASES:# 1) Design_name not setset errMsg "Please set the variable <design_name> to a non-empty value."set nRet 1} elseif { ${cur_design} ne "" && ${list_cells} eq "" } {# USE CASES:# 2): Current design opened AND is empty AND names same.# 3): Current design opened AND is empty AND names diff; design_name NOT in project.# 4): Current design opened AND is empty AND names diff; design_name exists in project.if { $cur_design ne $design_name } {common::send_gid_msg -ssname BD::TCL -id 2001 -severity "INFO" "Changing value of <design_name> from <$design_name> to <$cur_design> since current design is empty."set design_name [get_property NAME $cur_design]}common::send_gid_msg -ssname BD::TCL -id 2002 -severity "INFO" "Constructing design in IPI design <$cur_design>..."} elseif { ${cur_design} ne "" && $list_cells ne "" && $cur_design eq $design_name } {# USE CASES:# 5) Current design opened AND has components AND same names.set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."set nRet 1

} elseif { [get_files -quiet ${design_name}.bd] ne "" } {# USE CASES: # 6) Current opened design, has components, but diff names, design_name exists in project.# 7) No opened design, design_name exists in project.set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."set nRet 2} else {# USE CASES:# 8) No opened design, design_name not in project.# 9) Current opened design, has components, but diff names, design_name not in project.common::send_gid_msg -ssname BD::TCL -id 2003 -severity "INFO" "Currently there is no design <$design_name> in project, so creating one..."create_bd_design $design_namecommon::send_gid_msg -ssname BD::TCL -id 2004 -severity "INFO" "Making design <$design_name> as current_bd_design."current_bd_design $design_name}common::send_gid_msg -ssname BD::TCL -id 2005 -severity "INFO" "Currently the variable <design_name> is equal to \"$design_name\"."if { $nRet != 0 } {catch {common::send_gid_msg -ssname BD::TCL -id 2006 -severity "ERROR" $errMsg}return $nRet

}set bCheckIPsPassed 1

##################################################################

# CHECK IPs

##################################################################

set bCheckIPs 1

if { $bCheckIPs == 1 } {set list_check_ips "\

xilinx.com:ip:aurora_8b10b:11.1\

xilinx.com:ip:ila:6.2\

xilinx.com:ip:proc_sys_reset:5.0\

xilinx.com:ip:util_ds_buf:2.2\

xilinx.com:ip:vio:3.0\

xilinx.com:ip:xlconstant:1.1\

"set list_ips_missing ""common::send_gid_msg -ssname BD::TCL -id 2011 -severity "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."foreach ip_vlnv $list_check_ips {set ip_obj [get_ipdefs -all $ip_vlnv]if { $ip_obj eq "" } {lappend list_ips_missing $ip_vlnv}}if { $list_ips_missing ne "" } {catch {common::send_gid_msg -ssname BD::TCL -id 2012 -severity "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP(s) to the project." }set bCheckIPsPassed 0}}if { $bCheckIPsPassed != 1 } {common::send_gid_msg -ssname BD::TCL -id 2023 -severity "WARNING" "Will not continue with creation of design due to the error(s) above."return 3

}##################################################################

# DESIGN PROCs

################################################################### Procedure to create entire design; Provide argument to make

# procedure reusable. If parentCell is "", will use root.

proc create_root_design { parentCell } {variable script_foldervariable design_nameif { $parentCell eq "" } {set parentCell [get_bd_cells /]}# Get object for parentCellset parentObj [get_bd_cells $parentCell]if { $parentObj == "" } {catch {common::send_gid_msg -ssname BD::TCL -id 2090 -severity "ERROR" "Unable to find parent cell <$parentCell>!"}return}# Make sure parentObj is hier blkset parentType [get_property TYPE $parentObj]if { $parentType ne "hier" } {catch {common::send_gid_msg -ssname BD::TCL -id 2091 -severity "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}return}# Save current instance; Restore laterset oldCurInst [current_bd_instance .]# Set parent object as currentcurrent_bd_instance $parentObj# Create interface portsset CLK_IN_D_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:interface:diff_clock_rtl:1.0 CLK_IN_D_0 ]set_property -dict [ list \CONFIG.FREQ_HZ {300000000} \] $CLK_IN_D_0set GT_DIFF_REFCLK1_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:interface:diff_clock_rtl:1.0 GT_DIFF_REFCLK1_0 ]set_property -dict [ list \CONFIG.FREQ_HZ {156250000} \] $GT_DIFF_REFCLK1_0set GT_SERIAL_RX_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:display_aurora:GT_Serial_Transceiver_Pins_RX_rtl:1.0 GT_SERIAL_RX_0 ]set GT_SERIAL_TX_0 [ create_bd_intf_port -mode Master -vlnv xilinx.com:display_aurora:GT_Serial_Transceiver_Pins_TX_rtl:1.0 GT_SERIAL_TX_0 ]# Create portsset ext_reset_in_0 [ create_bd_port -dir I -type rst ext_reset_in_0 ]set_property -dict [ list \CONFIG.POLARITY {ACTIVE_HIGH} \] $ext_reset_in_0# Create instance: aurora_8b10b_0, and set propertiesset aurora_8b10b_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:aurora_8b10b:11.1 aurora_8b10b_0 ]set_property -dict [ list \CONFIG.CHANNEL_ENABLE {X0Y12} \CONFIG.C_DRP_IF {false} \CONFIG.C_LINE_RATE {3.125} \CONFIG.C_REFCLK_FREQUENCY {156.25} \CONFIG.C_REFCLK_SOURCE {MGTREFCLK1 of Quad X0Y3} \CONFIG.C_START_LANE {X0Y12} \CONFIG.C_START_QUAD {Quad_X0Y3} \CONFIG.Interface_Mode {Streaming} \CONFIG.SupportLevel {1} \CONFIG.TransceiverControl {false} \] $aurora_8b10b_0# Create instance: ila_1, and set propertiesset ila_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:ila:6.2 ila_1 ]set_property -dict [ list \CONFIG.C_ENABLE_ILA_AXI_MON {false} \CONFIG.C_MONITOR_TYPE {Native} \CONFIG.C_NUM_OF_PROBES {2} \] $ila_1# Create instance: proc_sys_reset_0, and set propertiesset proc_sys_reset_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_0 ]set_property -dict [ list \CONFIG.RESET_BOARD_INTERFACE {Custom} \CONFIG.USE_BOARD_FLOW {true} \] $proc_sys_reset_0# Create instance: util_ds_buf_0, and set propertiesset util_ds_buf_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:util_ds_buf:2.2 util_ds_buf_0 ]# Create instance: util_ds_buf_1, and set propertiesset util_ds_buf_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:util_ds_buf:2.2 util_ds_buf_1 ]set_property -dict [ list \CONFIG.C_BUFGCE_DIV {6} \CONFIG.C_BUF_TYPE {BUFGCE_DIV} \] $util_ds_buf_1# Create instance: vio_0, and set propertiesset vio_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:vio:3.0 vio_0 ]set_property -dict [ list \CONFIG.C_NUM_PROBE_IN {3} \CONFIG.C_NUM_PROBE_OUT {4} \CONFIG.C_PROBE_OUT0_WIDTH {16} \CONFIG.C_PROBE_OUT2_INIT_VAL {0x2} \CONFIG.C_PROBE_OUT2_WIDTH {3} \CONFIG.C_PROBE_OUT3_INIT_VAL {0x1} \CONFIG.C_PROBE_OUT4_INIT_VAL {0x1} \CONFIG.C_PROBE_OUT5_INIT_VAL {0x1} \] $vio_0# Create instance: xlconstant_0, and set propertiesset xlconstant_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_0 ]# Create instance: xlconstant_1, and set propertiesset xlconstant_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_1 ]set_property -dict [ list \CONFIG.CONST_VAL {0} \] $xlconstant_1# Create instance: xlconstant_2, and set propertiesset xlconstant_2 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_2 ]set_property -dict [ list \CONFIG.CONST_VAL {0} \] $xlconstant_2# Create interface connectionsconnect_bd_intf_net -intf_net CLK_IN_D_0_1 [get_bd_intf_ports CLK_IN_D_0] [get_bd_intf_pins util_ds_buf_0/CLK_IN_D]connect_bd_intf_net -intf_net GT_DIFF_REFCLK1_0_1 [get_bd_intf_ports GT_DIFF_REFCLK1_0] [get_bd_intf_pins aurora_8b10b_0/GT_DIFF_REFCLK1]connect_bd_intf_net -intf_net GT_SERIAL_RX_0_1 [get_bd_intf_ports GT_SERIAL_RX_0] [get_bd_intf_pins aurora_8b10b_0/GT_SERIAL_RX]connect_bd_intf_net -intf_net aurora_8b10b_0_GT_SERIAL_TX [get_bd_intf_ports GT_SERIAL_TX_0] [get_bd_intf_pins aurora_8b10b_0/GT_SERIAL_TX]# Create port connectionsconnect_bd_net -net aurora_8b10b_0_channel_up [get_bd_pins aurora_8b10b_0/channel_up] [get_bd_pins vio_0/probe_in1]connect_bd_net -net aurora_8b10b_0_lane_up [get_bd_pins aurora_8b10b_0/lane_up] [get_bd_pins vio_0/probe_in2]connect_bd_net -net aurora_8b10b_0_m_axi_rx_tdata [get_bd_pins aurora_8b10b_0/m_axi_rx_tdata] [get_bd_pins ila_1/probe0]connect_bd_net -net aurora_8b10b_0_m_axi_rx_tvalid [get_bd_pins aurora_8b10b_0/m_axi_rx_tvalid] [get_bd_pins ila_1/probe1]connect_bd_net -net aurora_8b10b_0_s_axi_tx_tready [get_bd_pins aurora_8b10b_0/s_axi_tx_tready] [get_bd_pins vio_0/probe_in0]connect_bd_net -net ext_reset_in_0_1 [get_bd_ports ext_reset_in_0] [get_bd_pins proc_sys_reset_0/ext_reset_in]connect_bd_net -net proc_sys_reset_0_peripheral_reset [get_bd_pins aurora_8b10b_0/reset] [get_bd_pins proc_sys_reset_0/peripheral_reset]connect_bd_net -net util_ds_buf_0_IBUF_OUT [get_bd_pins aurora_8b10b_0/init_clk_in] [get_bd_pins ila_1/clk] [get_bd_pins proc_sys_reset_0/slowest_sync_clk] [get_bd_pins util_ds_buf_1/BUFGCE_O] [get_bd_pins vio_0/clk]connect_bd_net -net util_ds_buf_0_IBUF_OUT1 [get_bd_pins util_ds_buf_0/IBUF_OUT] [get_bd_pins util_ds_buf_1/BUFGCE_I]connect_bd_net -net vio_0_probe_out0 [get_bd_pins aurora_8b10b_0/s_axi_tx_tdata] [get_bd_pins vio_0/probe_out0]connect_bd_net -net vio_0_probe_out1 [get_bd_pins aurora_8b10b_0/s_axi_tx_tvalid] [get_bd_pins vio_0/probe_out1]connect_bd_net -net vio_0_probe_out2 [get_bd_pins aurora_8b10b_0/loopback] [get_bd_pins vio_0/probe_out2]connect_bd_net -net vio_0_probe_out3 [get_bd_pins aurora_8b10b_0/gt_reset] [get_bd_pins vio_0/probe_out3]connect_bd_net -net xlconstant_0_dout [get_bd_pins util_ds_buf_1/BUFGCE_CE] [get_bd_pins xlconstant_0/dout]connect_bd_net -net xlconstant_1_dout [get_bd_pins util_ds_buf_1/BUFGCE_CLR] [get_bd_pins xlconstant_1/dout]connect_bd_net -net xlconstant_2_dout [get_bd_pins aurora_8b10b_0/power_down] [get_bd_pins xlconstant_2/dout]# Create address segments# Restore current instancecurrent_bd_instance $oldCurInstvalidate_bd_designsave_bd_design

}

# End of create_root_design()##################################################################

# MAIN FLOW

##################################################################create_root_design ""4. 总结

理解 IP 重要信号:

- channel_up:通道初始化完成,且通道准备好进行数据传输时,生效。

- lane_up:在每个通道成功初始化时进行断言,每个比特代表一个通道。

- user_clk_out:由 Aurora 8B/10B 核心共享的并行时钟(共享逻辑在 IP 中)。

- reset:高电平有效。

- gt_reset:高电平有效。

- loopback:回环控制

IP 使用非常简单,只需简单配置即可。

使用基础 IP 查找位置信息非常方便。

相关文章:

Vivado - Aurora 8B/10B IP

目录 1. 简介 2. 设计调试 2.1 Physical Layer 2.2 Link Layer 2.3 Receiver 2.4 IP 接口 2.5 调试过程 2.5.1 Block Design 2.5.2 释放 gt_reset 2.5.3 观察数据 3. 实用技巧 3.1 GT 坐标与布局 3.1.1 选择器件并进行RTL分析 3.1.2 进入平面设计 3.1.3 收发器布…...

图(Java语言实现)

一、图的概念 顶点(Vertex):图中的数据元素,我们称之为顶点,图至少有一个顶点(非空有穷集合)。 边(Edge):顶点之间的关系用边表示。 1.图(Graph…...

GPT 生成绘画_Java语言例子_超详细

基于spring ai :简化Java AI开发,提升效率与维护性 过去在使用Java编写AI应用时,主要困境在于缺乏统一的标准化封装,开发者需要针对不同的AI服务提供商查阅各自独立的文档并进行接口对接,这不仅增加了开发的工作量&am…...

华为OD机试 - 小朋友分组最少调整次数 - 贪心算法(Python/JS/C/C++ 2024 E卷 100分)

华为OD机试 2024E卷题库疯狂收录中,刷题点这里 专栏导读 本专栏收录于《华为OD机试真题(Python/JS/C/C)》。 刷的越多,抽中的概率越大,私信哪吒,备注华为OD,加入华为OD刷题交流群,…...

数字农业与遥感监测平台

随着全球人口的增长和气候变化的挑战,农业的可持续发展变得尤为重要。数字农业作为现代农业发展的重要方向,正逐渐成为提高农业生产效率、保障粮食安全的关键手段。遥感技术作为数字农业的重要组成部分,通过监测作物生长状况、土壤湿度、病虫…...

2023年12月中国电子学会青少年软件编程(Python)等级考试试卷(一级)答案 + 解析

一、单选题 1、下列程序运行的结果是?( ) print(hello) print(world) A.helloworld B.hello world C.hello world D.helloworld 正确答案:B 答案解析:本题考察的 Python 编程基础,print 在打印时…...

【优选算法】——双指针(下篇)!

🌈个人主页:秋风起,再归来~ 🔥系列专栏:C刷题算法总结 🔖克心守己,律己则安 目录 1、有效三角形的个数 2、查找总价值为目标值的两个商品 3、三数之和 4、四数之和 5、完结散花 1、有…...

C#中函数重载的说明

一.函数重载的基本概念 C# 中的函数重载是指在同一个类中定义多个同名的函数,但这些函数的参数类型、参数个数、参数顺序等不同,以便适应不同的调用需求,增加代码的兼容性。 二.函数重载的作用 2.1定义多个相类似的函数,减少函…...

图论day56|广度优先搜索理论基础 、bfs与dfs的对比(思维导图)、 99.岛屿数量(卡码网)、100.岛屿的最大面积(卡码网)

图论day56|广度优先搜索理论基础 、bfs与dfs的对比(思维导图)、 99.岛屿数量(卡码网)、100.岛屿的最大面积(卡码网)) 广度优先搜索理论基础bfs与dfs的对比(思维导图)&…...

源码编译方式安装htppd软件

一.源码编译安装httpd软件 1.安装阿帕奇的依赖,安装apr软件,阿帕奇正常运行的环境这个环境就是apr。 2.安装apr-util软件,主要提供针对apr环境的管理工具, 3.安装阿帕奇软件即httpd软件。 如上图所示,就是三个软件的…...

MES制造执行系统原型图动端 Axure原型 交互设计 Axure实战项目

MES制造执行系统原型移动端 Manufacturing Execution System prototype MES制造执行系统原型图移动端是专门为制造执行系统设计的移动端是一个可视化的设计。用于展示和演示该系统在移动设备上的功能和界面。通过原型图,可以清晰地了解制造执行系统在移动端的各个…...

flutter 仿淘宝推荐二级分类效果

先看效果 一开始 用的PageView 做的, 然后重写PageScrollPhysics一顿魔改, 最后发现还是有一些小bug。 后面又想到pageview 能做,listview肯定也能做,最后用ListView加GridView 把功能实现了。 listview 实现pageview 的分页滑动…...

报错 - LangChain AgentExecutor - ‘function‘ object has no attribute ‘get‘

使用 AgentExecutor 调用了使用两个 tool 的agent,报一下错误: 如果 agent 只使用 一个tool,没有报错 File "/Users/xx/miniconda3/envs/env1/lib/python3.11/site-packages/pydantic/_internal/_validators.py", line 44, in sequ…...

【DIY小记】通过降低电压和Process Lasso工具优化CPU超频表现

又到了创作纪念日,秉承着笔耕不辍的理念,笔者还是继续分享一下DIY日常。 在上一篇文章当中,笔者介绍了一些作为新手小白超频CPU和NVIDIA显卡的经验。今天又有了更新,笔者通过降低CPU工作电压,并且结合Process Lasso对…...

3、Docker搭建MQTT及Spring Boot 3.x集成MQTT

一、前言 本篇主要是围绕着两个点,1、Docker 搭建单机版本 MQTT(EMQX),2、Spring Boot 3.x 集成 MQTT(EMQX); 而且这里的 MQTT(EMQX)的搭建也只是一个简单的过程&#x…...

六种定时任务记录

1、java自带的Timer Timer是java中自带的类。 优点:使用简单,缺点是当添加并执行多个任务时,前面任务的执行用时和异常将影响到后面任务。 Timer timer new Timer();timer.schedule(new TimerTask() {int i 0;Overridepublic void run() …...

Dos下编译环境搭建和C运行程序生成

文章目录 前言一、需要准备的Tool二、搭建步骤 前言 因为工作需要,需要搭建个Dos下的编译环境来进行Code App开发,如下记录下搭建过程。 一、需要准备的Tool 编译环境:Win10/win11 编译工具: DOSBox0.74 Turboc2.7z 二、搭建步骤 1.双击压…...

:复杂的SELECT语句)

【MySQL】入门篇—SQL基础:数据查询语言(DQL):复杂的SELECT语句

在实际应用中,复杂的SELECT语句可以帮助我们从多个表中提取相关信息,进行数据分析,生成报告,甚至进行数据挖掘。 掌握复杂的SELECT语句对于数据分析师、数据库管理员和开发者来说是必不可少的技能。 应用场景: 多表查…...

Appium环境搭建、Appium连接真机

文章目录 一、安装Android SDK二、安装Appium-desktop三、安装Appium Inspector 一、安装Android SDK 首先需要安装jdk,这里就不演示安装jdk的过程了 SDK下载地址:Android SDK 下载 1、点击 Android SDK 下载 -> SKD Tools 2、选择对应的版本进行下…...

【X线源】关于滨松MCS2软件的说明

【X线源】关于滨松MCS2软件的说明 1.软件背景2.MCS2界面3.MCS2操作4.常见问题 1.软件背景 滨松为了方便客户将滨松MFX集成进自己的系统,滨松提供了MFX二次开发相关的信息和Demo代码。参考博客说明: 【X线源】关于滨松MFX二次开发demo示例简介 https://…...

【C++:红黑树】4 条规则深度理解红黑树:从原理、变色、旋转到完整实现代码

🔥小叶-duck:个人主页 ❄️个人专栏:《Data-Structure-Learning》《C入门到进阶&自我学习过程记录》 《算法题讲解指南》--优选算法 《算法题讲解指南》--递归、搜索与回溯算法 《算法题讲解指南》--动态规划算法 ✨未择之路࿰…...

)

Sleep-EDF数据库实战:如何用Matlab快速处理睡眠分期标签(附完整代码)

Sleep-EDF数据库实战:如何用Matlab快速处理睡眠分期标签(附完整代码) 睡眠研究是神经科学和临床医学的重要领域,而Sleep-EDF数据库作为公开可用的标准数据集,为科研人员提供了宝贵的多导睡眠图(PSG)记录。但在实际应用…...

如何构建终极智能电池管理系统:DIY爱好者的完整解决方案

如何构建终极智能电池管理系统:DIY爱好者的完整解决方案 【免费下载链接】SmartBMS Open source Smart Battery Management System 项目地址: https://gitcode.com/gh_mirrors/smar/SmartBMS 在当今能源转型的时代,锂电池已成为从电动汽车到家庭储…...

避坑指南:Ubuntu交叉编译工具链安装中的5个常见错误及解决方法

Ubuntu交叉编译工具链安装避坑实战:从环境配置到疑难解析 在嵌入式开发领域,交叉编译工具链的配置往往是项目启动的第一道门槛。许多开发者都有过这样的经历:按照教程一步步操作,却在最后一步arm-linux-gnueabihf-gcc -v验证时遭遇…...

Linux 系统调用实现原理

Linux 系统调用实现原理 系统调用的重要性 作为科技创业者,我深刻理解系统调用在操作系统中的核心地位。系统调用是用户空间与内核空间交互的桥梁,是应用程序访问操作系统服务的唯一途径。深入理解系统调用的实现原理,对于系统性能优化和安全…...

OpenClaw Agent 核心规则体系深度解构

OpenClaw Agent 核心规则体系深度解构OpenClaw Agent 的核心规则,旨在解决一个根本性矛盾:如何赋予一个基于LLM的、具有“黑盒”特性的程序以高系统权限,同时确保其行为安全、可控、可预测且高效。 这套规则体系是工程化、系统化的࿰…...

深入解析MCU Systick:从基础配置到精准延时与系统时间获取实战

1. Systick定时器基础解析 Systick是Cortex-M内核内置的24位递减计数器,堪称MCU的"心跳发生器"。我第一次在STM32项目中使用它时,就像发现了一个隐藏的瑞士军刀——简单却功能强大。这个看似简单的定时器,实际上承担着三大核心功能…...

威联通NAS结合阿里云实现安全远程访问:域名与SSL证书全流程配置

1. 为什么需要为威联通NAS配置域名和SSL证书? 很多朋友买了威联通NAS后都会遇到一个头疼的问题:怎么在外面也能安全地访问家里的NAS?直接暴露IP地址不仅难记,还存在安全隐患。我刚开始用NAS时也踩过不少坑,后来发现用阿…...

TurtleBot3在Gazebo中的多机器人SLAM仿真:ROS2 Humble命名空间实战

TurtleBot3多机SLAM仿真:ROS2 Humble命名空间深度实践 在机器人开发领域,仿真环境的重要性不言而喻。它不仅能大幅降低硬件成本,还能提供可重复、可控的测试条件。ROS2 Humble作为当前长期支持版本,结合Gazebo仿真器和TurtleBot3…...

csvlens作为库使用教程:在Rust项目中集成CSV查看功能

csvlens作为库使用教程:在Rust项目中集成CSV查看功能 【免费下载链接】csvlens Command line csv viewer 项目地址: https://gitcode.com/gh_mirrors/cs/csvlens 想要在你的Rust应用中添加一个功能强大、交互式的CSV数据查看器吗?csvlens不仅是一…...