【DC简介--Part1】

DC简介-Part1

- 1 overview

- 1.1 DC操作步骤

- 1.2 Steps

- 1.2.1 Develop HDL files

- 1.2.2 Specify libraries

- 1.2.3 Read design

- 1.2.4 Define design environment

- 1.2.5 Set design constraints

- 1.2.6 Select compile strategy

- 1.2.7 Synthesize and optimize the design

- 1.2.8 Analyze and resolve design problems

- 1.2.9 Save the design database

- 2 具体前期准备工作

- 2.1 Specify librarys

- 2.1.1 什么是库?

- 2.1.12 进行库(libraries)指定

- 2.2 Read design

- 2.2.1 什么是转换(translation)

- 2.2.2 读入文件进行转换

- 2.2.3 转换后的gtech网表

1 overview

Designer Compiler(DC)就是对应着芯片设计流程中的synthesis(综合)。即:综合就是把行为级的RTL代码在工艺、面积和时序等约束下转换成相对应的门级网表;即对应着将RTL代码编译成实际电路的过程。

综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。

- 转换阶段:综合工具即将高层语言描述的电路–>门级的逻辑实现;对于DC来说,就是使用gtech.db库中的门级单元来组成HDL语言描述的电路,从而构成初始的未优化的电路。

- 优化阶段:综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,同时会根据工程师提供的约束条件对初始电路进行优化,使得电路在满足逻辑功能的前提下,尽可能得往工程师约束的条件靠近(比如说面积最小等);

- 映射阶段:综合工具将优化之后的电路映射到由制造商提供的工艺库上,这里的工艺库就是target_library,最后生成网表文件用于后端设计;

1.1 DC操作步骤

下面是给出DC进行逻辑综合时的基本步骤;

1.2 Steps

1.2.1 Develop HDL files

1.Develop HDL files:即src/ 的module文件;

1.2.2 Specify libraries

Specify libraries:指定库文件,包括搜索路径-search_path、链接库-link library、目标库-target library、符号库-symbol library、综合库-synthetic library.

-

serach_path: 综合工具只会从该指定的路径去寻找各种库文件。

-

link library & target library: Link library 和 target library 统称为 technology library(即工艺库,习惯称之为综合库),technology library 由半导体制造商提供,包含相关 cell 的信息及设计约束标准,其中:

Target library: 在门级优化及映射的时候提供生成网表的 cell,即DC用于创建实际电路的库。

Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是 DC 不用 link library中的 cell 来综合设计。包含target_library,在此基础上再加上IO库文件,IP库文件等

注意 :在 link_library 的设置中必须包含" * “,” * “表示 DC 在引用实例化模块 或者单元电路时首先搜索已经调进DC memory的模块和单元电路,如果在link library 中不包含” * ",DC 就不会使用 DC memory 中已有的模块,因此,会出现无法匹配的模块或单元电路的警告信息(unresolved design reference)。

当 DC 读入设计时,它自动读入由 link library 变量指定的库。当连接设计时,DC 先搜寻其内存中已经有的库,然后在搜寻由 link library 指定的库。 -

Symbol library: 提供 Design Vision GUI 中设计实现的图形符号,如果使用脚本模式而不使用 GUI,可不指定 Symbol library.

-

Synthetic library: 虽然直译为综合库,但是常称为IP库,为Designware library。特殊的IP库需要授权(例如多级流水线乘法器),标准IP库由DC软件商提供,无需指定。

这里只指定搜索路径(search_path)、链接库(link library)、目标库(target library)即可。

1.2.3 Read design

读入设计就是将编写好的HDL代码载入内存。

1.2.4 Define design environment

定义设计环境,定义对象包括工艺参数(温度、电压等)、I/O特性(负载、驱动、扇出);

1.2.5 Set design constraints

设置设计约束,包括设计规则约束(DRC,design rule constraints)和优化约束(optimization constraints),DRC由工艺库决定,在设计编译过程中必须要满足,用于使电路能按照功能要求正常工作。优化约束由工程师指定,为DC要达到的时序和面积优化目标。DC在不违反设计规则约束的前提下,尽可能满足优化约束。

1.2.6 Select compile strategy

选择编译策略。对于层次化设计,DC由top_down和bottom_up两种编译策略。

在top_down策略中,顶层模块和子模块一起编译,所有的环境和约束针对顶层设计,虽然此种策略自动考虑到相关的内部设计,但是此种策略中所有模块需要同时占用内存,硬件资源损耗打,不适合大型设计。

在bottom_up策略中,子模块单独约束,当子模块成功编译后,会被设置为dont_touch属性,不允许之后的编译过程修改,子模块编译完成后再向上编译父模块,直至顶层模块编译完成。由于该策略不需要所有模块同时占用内存,因此适用于大规模设计。

1.2.7 Synthesize and optimize the design

执行综合和优化,可以利用一些选项指导编译和优化过程。

1.2.8 Analyze and resolve design problems

分析及解决设计中存在的问题。DC在编译过程中会产生一系列报告,如时序、面积、约束、功耗等报告,工程师需要通过这些报告进行分析和解决设计中存在的问题。

1.2.9 Save the design database

保存设计数据。DC不会自动保存综合后的设计数据,因此需要手动保存网表、报告等数据文件。

2 具体前期准备工作

2.1 Specify librarys

DC会将我们的设计转换(translation)为一个中间格式——gtech网表;将gtech网表理解为FPGA中RTL Analysis之后得到的RTL级网表,它不与任何具体的FPGA相关,例如RTL级网表可能包含加法器,但是FPGA上只有LUT,并没有加法器。得到gtech网表之后,我们需要根据给定的约束,去选择真实的合适的器件,那么这个时候可以类比于将RTL级网表映射到某一块具体的FPGA上,类似于FPGA开发中的synthesis。

DC运行库中需要的几种库文件:

- 目标库(target_library)

- 链接库(link_library)

- 符号库(symbol_library)

- 综合库(synthetic_library)

2.1.1 什么是库?

- 目标库: 是gtech网表要最终映射(mapping)到的库,库文件有两种格式,有以.lib结尾和.db结尾,.lib是可以阅读的。

下图是具体的一个目标库文件-target_libray: 包含了各个单元cell的行为、引脚、面积、时序信息等,DC会根据用户给定的约束(例如时钟频率和面积等)去选择合适的单元,去掉冗余的单元,最后将优化之后的电路映射(mapping)到目标库(target_library)上。

可以把这个目标库(target_library)理解为一个非常大switch语句,它的变量是各种时序要求等,映射(mapping)就是DC根据时序要求等去选择合适的cell,即选择合适的case

- 链接库(link_library) 是设置模块或单元电路的引用,指定购买的付费IP、存储器、IO等,例如我们购买了Synopsys的某个IP,则需要在这个地方指定。

- 符号库(symbol_library) 定义单元电路Schematic库,在design_vision图形化模式下查看综合图标需要设置,后缀是.sdb

- IP库(synthetic_library) 也称模型库,DC综合时用来将HDL代码转化为相对应的元件时所参考的模型库,比如RTL中的符号“+”,可以通过查找模型库将生成某一类加法器。默认的synthetic library一般有:dw_foundation.sldb. 在design compiler的安装目录下可以找到。

2.1.12 进行库(libraries)指定

set_app_var target_library ../lib/smic18_ss.db //指定目标库 ff和ss代表不同的工艺角set_app_var link_library ../lib/smic18_ss.db //指定链接库

2.2 Read design

specify libraries之后就是read_file,在前文,我们不断提到gtech网表,gtech网表是根据我们的设计转换而来,那我们首先介绍一下什么是转换以及怎么转换?

2.2.1 什么是转换(translation)

首先需要将设计HDL代码导入DC中,DC会使用内部的单元(cell)来替换我们的设计文件,也就是使用gtech.db库中的单元cell来组成一个中间的网表getch网表

经过转换(translation)RTL or gate or behavior ——> gtech

具体转换的过程:

转换的过程中:DC会进行结构级和逻辑级的优化;比如通过公用表达式,进行结构级优化;通过展平,把组合逻辑路径减少两级,变为乘积之和的电路进行逻辑优化;

2.2.2 读入文件进行转换

将设计载入DC中,具体是读入设计文件命令:

read_verilog ../rtl/clock.v

read_verilog ../rtl/register.v

read_verilog ../rtl/cells-lib/dffr.v

read_verilog ../rtl/cells-lib/mux.v

逐条读入时默认指定最后一个为top模块,但建议在任何情况下都要单独指定top模块。

2.2.3 转换后的gtech网表

即将生成的gtech网表保存在unmapped文件夹之下/

在下方得到新的design_gtech_netlist.v来进行对比;

read_verilog ../rtl/cells-lib/dffr_RTL.v current_design dffr_RTLwrite_file -f verilog -hier -o ../unmapped/design_gtech_netlist.v

如果直接在elaborate或者read_file后导出gtech网表,生成的gtech网表会有很多cell不能map到gtech. 比如时序逻辑生成 SEQGEN来表示 \ 如果要生成完全可以map的gtech网表,需要综合compile,这要在设置完约束之后。

在compile前,gtech网表中不仅仅只有与非门、异或门这种门电路符号,还有时序器件符号SEQGEN,如果设计中使用加、减、乘和比较等运算,gtech 会将其提取出来并用以带有OP标识的符号表示,这方便后续进行高级别电路优化;另外,设计中避免不了使用选择逻辑,如不特别声明,DC在这一阶段对选择逻辑用SELECT_OP表示,且在后续的映射阶段并不一定将SELECT_OP映射成多路选择器,而是采用与非门电路来实现其功能,如果想要映射成多路选择器,那么需要在RTL中声明synopsys infer_mux。

未完待续…

[ref]

1.https://blog.csdn.net/qq_23958451/article/details/108189446

2.https://zhuanlan.zhihu.com/p/605629775

相关文章:

【DC简介--Part1】

DC简介-Part1 1 overview1.1 DC操作步骤1.2 Steps1.2.1 Develop HDL files1.2.2 Specify libraries1.2.3 Read design1.2.4 Define design environment1.2.5 Set design constraints1.2.6 Select compile strategy1.2.7 Synthesize and optimize the design1.2.8 Analyze and r…...

Spark写入HDFS数据SUCCESS文件生成控制

Spark写入HDFS数据SUCCESS文件 1、_SUCCESS的控制2、_SUCCESS的实现 1、_SUCCESS的控制 与Hive不同,MapReduce和Spark在执行写入HDFS数据任务时,数据输出目录一般都会有一个名为_SUCCESS的空文件,该文件仅用来表示任务执行成功 但有些时候&a…...

MySQL 服务器简介

通常所说的 MySQL 服务器指的是mysqld程序,当运⾏mysqld后对外提供MySQL 服务,这个专题的内容涵盖了以下关于MySQL 服务器以及相关配置的内容,包括: 服务器⽀持的启动选项。可以在命令⾏和配置⽂件中指定这些选项。 服务器系统变…...

如何使用Python从SACS结构数据文件中提取节点数据信息并导出到EXCEL

在现代工程设计中,结构分析和数据处理是不可或缺的一部分。特别是在海洋工程、桥梁建设等领域,SACS文件被广泛应用。这种文件格式包含了结构模型的各种重要信息,包括节点(JOINT)、构件(ELEMENT)…...

Java网约车项目实战:实现抢单功能详解

在网约车项目中,抢单功能是非常关键的一部分,它决定了司机能否及时响应乘客的订单,提高整个平台的运营效率。本文将详细介绍如何使用Java来实现网约车项目的抢单功能,并提供一个完整的代码示例,以便读者能够直接运行和…...

SSRF服务端请求Gopher伪协议白盒测试

前言 是什么SSRF? 这个简单点说就是 服务端的请求伪造 就是这个如果是个 请求图片的网站 他的目的是请求外部其他网站的 图片 但是 SSRF指的是让他请求本地的图片 再展示出来 请求的是他的服务器上的图片 SSRF(Server-Side Request Forgery:服务器端请求伪造) …...

html+css+js网页设计 美食 家美食1个页面

htmlcssjs网页设计 美食 家美食1个页面 网页作品代码简单,可使用任意HTML辑软件(如:Dreamweaver、HBuilder、Vscode 、Sublime 、Webstorm、Text 、Notepad 等任意html编辑软件进行运行及修改编辑等操作)。 获取源码 1…...

初学stm32---高级定时器输出n个pwm波

目录 高级定时器简介:(F1) 高级定时器框图 重复计数器特性 高级定时器输出指定个数PWM实验原理 高级定时器输出指定个数PWM实验配置步骤 相关HAL库函数介绍 关键结构体介绍 高级定时器简介:(F1) 1.高级定时器 :TIM1/TIM8 2.主要特性&…...

旅游管理系统|Java|SSM|VUE| 前后端分离

【技术栈】 1⃣️:架构: B/S、MVC 2⃣️:系统环境:Windowsh/Mac 3⃣️:开发环境:IDEA、JDK1.8、Maven、Mysql5.7 4⃣️:技术栈:Java、Mysql、SSM、Mybatis-Plus、VUE、jquery,html 5⃣️数据库可…...

imgproxy图像处理的高效与安全

摘要 imgproxy作为一个高效且安全的独立服务器,为图像处理提供了全新的解决方案。它不仅简化了图像调整和转换的过程,还极大地提升了处理速度,确保了整个流程的安全性。通过集成imgproxy,用户可以轻松优化网页上的图像,提高加载速度,改善用户体验。本文将深入探讨imgpro…...

LLM并行计算的论文

LLM并行计算的论文 基础并行计算方法相关 《Gpipe: Efficient Training of Giant Neural Networks using Pipeline Parallelism》:提出了Gpipe这种流水线并行方法,通过将数据批量进一步等分成若干microbatch,并以流水线的方式执行,减少计算中空泡的比例,极大地拓展了模型…...

Linux 搭建 nginx+keepalived 高可用 | Nginx反向代理

注意:本文为 “Linux 搭建 nginxkeepalived (主备双主模式) 高可用 | Nginx反向代理” 相关文章合辑。 KeepalivedNginx实现高可用(HA) xyang0917 于 2016-09-17 00:24:15 发布 keepalived 的 HA 分为抢占模式和非抢占模式,抢占…...

Spring Boot 项目中 Maven 剔除无用 Jar 引用的最佳实践

目录 引言Maven 依赖管理的基础概念 2.1 什么是 Maven 依赖2.2 Maven 的依赖传递机制 无用依赖的常见问题与影响剔除无用 Jar 引用的常见方法 4.1 识别无用依赖4.2 使用 Maven 的 dependency:analyze 插件4.3 配置 scope 以优化依赖范围4.4 使用 exclude 排除传递依赖4.5 分析…...

useWhyDidYouUpdate详解

目录 API Params demo演示 源码 useWhyDidYouUpdate是ahooks库中的一个hook函数,用于帮助开发者排查是哪个属性改变导致了组件的 rerender。 API type IProps Record<string, any>;useWhyDidYouUpdate(componentName: string, props: IProps): void; …...

c++入门——c++输入cin和输出cout的简单使用

c输入cin、输出cout 1 cin2 cout3 cin和cout说明 c在c语言的输入、输出函数的基础上进行了封装。 1 cin c可以理解为控制台,in可以理解为输入。 参考代码: void f(){int a;float b;double c;char d;cin>>a>>b>>c>>d;//这里和…...

Spring Cloud LoadBalancer (负载均衡)

目录 什么是负载均衡 服务端负载均衡 客户端负载均衡 Spring Cloud LoadBalancer快速上手 启动多个product-service实例 测试负载均衡 负载均衡策略 自定义负载均衡策略 什么是负载均衡 负载均衡(Load Balance,简称 LB) , 是高并发, 高可用系统必不可少的关…...

微服务-1 认识微服务

目录 1 认识微服务 1.1 单体架构 1.2 微服务 1.3 SpringCloud 2 服务拆分原则 2.1 什么时候拆 2.2 怎么拆 2.3 服务调用 3. 服务注册与发现 3.1 注册中心原理 3.2 Nacos注册中心 3.3 服务注册 3.3.1 添加依赖 3.3.2 配置Nacos 3.3.3 启动服务实例 …...

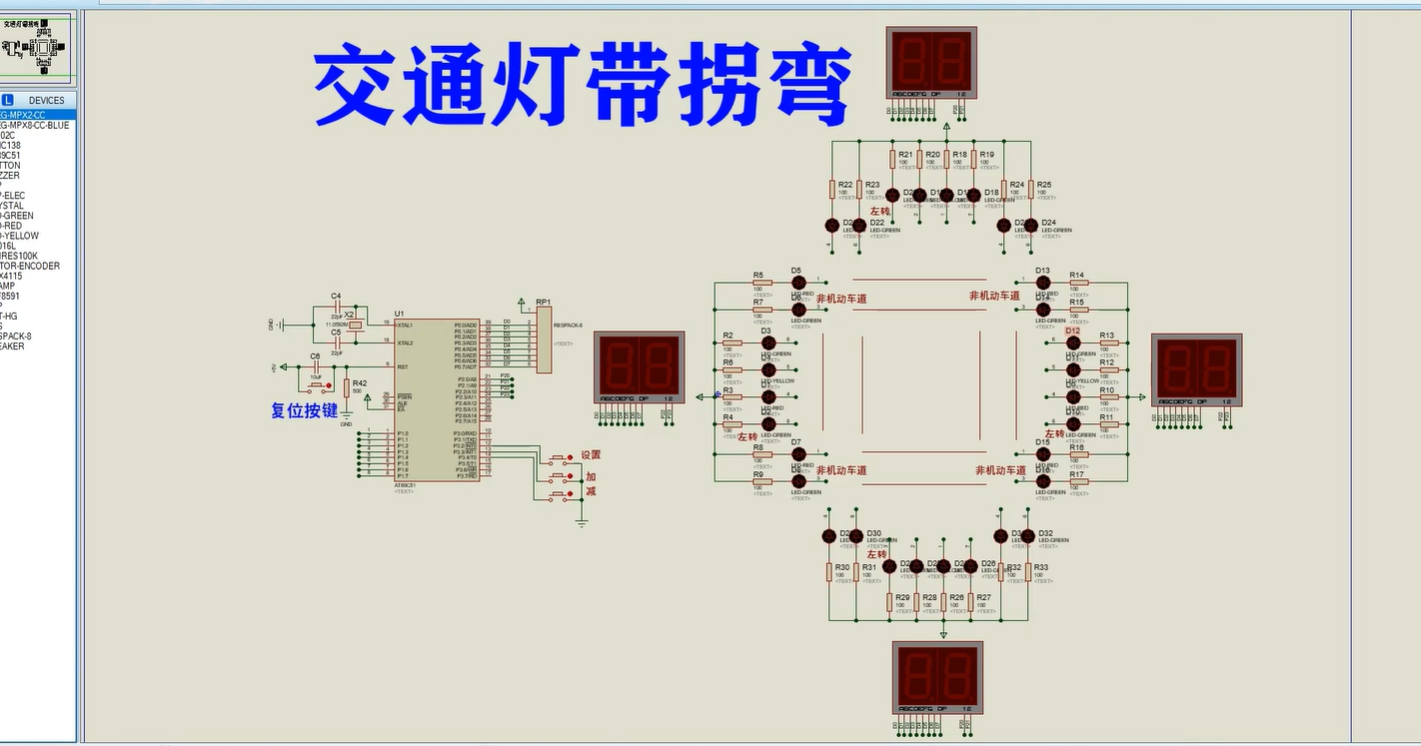

基于51单片机的交通灯带拐弯proteus仿真

地址: https://pan.baidu.com/s/1cgqRHMHp9VJet4vs5LiG5A 提取码:1234 仿真图: 芯片/模块的特点: AT89C52/AT89C51简介: AT89C52/AT89C51是一款经典的8位单片机,是意法半导体(STMicroelectro…...

1229java面经

1,Java中synchronized关键字是否是可重入的? 可重入的定义 可重入是指当一个线程已经获取了某个对象的锁,在该锁没有释放的情况下,如果这个线程再次请求获取这个对象的锁,是可以成功获取的,而不会出现自己把自己锁死的情况。简单…...

MySQL中查看表结构

1. 使用 DESCRIBE 或 DESC 命令 DESCRIBE(或其简写 DESC)是最简单和最直接的方法,可以显示表的列信息。 语法: DESCRIBE table_name; -- 或者 DESC table_name;示例: 假设有一个名为 employees 的表,可以…...

如何通过FCEUX实现NES游戏的完美模拟?超实用指南

如何通过FCEUX实现NES游戏的完美模拟?超实用指南 【免费下载链接】fceux FCEUX, a NES Emulator 项目地址: https://gitcode.com/gh_mirrors/fc/fceux 5个步骤3个技巧,让你快速掌握NES模拟器 核心价值:重温和探索经典游戏的最佳选择 …...

一文搞懂Agent三大核心技术:Function Calling、MCP、A2A,小白也能轻松收藏学习!

本文详细解析了AI Agent的三大核心技术:Function Calling、MCP和A2A。Function Calling使AI能够主动获取外部信息,MCP为工具接入提供了标准化接口,而A2A则实现了多智能体之间的协作。通过这三个技术的演进,AI Agent的能力从点对点…...

)

Microsoft Agent Framework 构建 SubAgent(Multi-Agent)

本文演示如何用 Microsoft Agent Framework 用 Executor Workflow(DAG)模式实现 SubAgent(子代理)架构。通过示例代码(来自项目的 txt)展示并发 Fan‑Out/Fan‑In 的实现、消息路由与聚合策略,…...

TscanCode静态代码扫描工具原理与实践

嵌入式静态代码扫描工具TscanCode深度解析1. 静态代码分析技术概述1.1 静态代码扫描原理静态代码扫描是一种在不实际执行程序的情况下,通过词法分析、语法分析、控制流和数据流分析等技术对源代码进行检测的方法。这种技术能够有效识别代码中潜在的错误和缺陷&#…...

)

Python异步I/O终极调优手册(含strace+py-spy+asyncio debug mode三重追踪链路图)

第一章:Python异步I/O性能瓶颈的本质洞察Python的async/await语法虽大幅简化了异步编程模型,但其底层性能瓶颈并非源于语法糖本身,而根植于事件循环调度机制、GIL对CPU密集型任务的制约,以及I/O等待与协程切换之间的隐式开销。事件…...

【深度解析】Claude Auto Dream:从“短期对话”到“项目级心智模型”的记忆系统升级

摘要 本文从 Anthropic 新增的 Auto Dream(/dream)功能出发,系统解析大模型“跨会话记忆一致性”这一核心难题,剖析 Auto Memory Auto Dream 组合背后的技术逻辑,并给出如何在自己项目里实现“类 Auto Dream 记忆管理…...

LFM2.5-1.2B-Thinking-GGUF应用场景:智能硬件说明书问答机器人落地实践

LFM2.5-1.2B-Thinking-GGUF应用场景:智能硬件说明书问答机器人落地实践 1. 项目背景与需求 在智能硬件领域,产品说明书往往存在以下痛点: 内容专业术语多,普通用户难以理解纸质说明书查找信息效率低不同型号产品差异导致用户混…...

将嵌套循环中的Java对象数组转换为HashMap以优化性能

本文旨在指导开发人员如何通过将嵌套循环转换为Hashmap来优化Java代码的性能,特别是当涉及到对象属性的相等性检查时。通过使用Hashmap的快速搜索特性,可以显著降低时间复杂性,提高代码执行效率。本文将提供详细的步骤和示例代码,…...

告别调参玄学:手把手教你用‘黎卡提方程’为自动驾驶LQR控制器选择Q和R矩阵

自动驾驶轨迹跟踪实战:从黎卡提方程到LQR调参的工程化思考 当你在仿真环境中第一次看到自己设计的LQR控制器让车辆完美跟踪参考轨迹时,那种成就感难以言喻。但更多时候,我们面对的是震荡的超调曲线、缓慢的收敛速度,以及令人抓狂的…...

)

GStreamer性能优化指南:在Jetson TX2上实现4K视频低延迟处理(基于NVMM内存)

GStreamer性能优化指南:在Jetson TX2上实现4K视频低延迟处理(基于NVMM内存) 在嵌入式视觉和实时视频处理领域,NVIDIA Jetson TX2凭借其强大的GPU和专用硬件加速单元,成为工业级应用的理想选择。但要将这块开发板的性能…...