初识verilog HDL

为什么选择用Verilog HDL开发FPGA???

硬件描述语言(Hardware Descriptipon Lagnuage,HDL)通过硬件的方式来产生与之对应的真实的硬件电路,最终实现所设计的预期功能,其设计方法与软件不同,因此也就意味着描述的各个功能之间可以和硬件一样实现真正的并行互动。将这种语言成为硬件描述语言而非硬件语言的原因是:这种语言是用来描述我们设计的硬件所要实现的功能,而不是直接对硬件进行设计。

目前常用的语言是 verilog HDL 和 VHDL。对比而言,

VHDL和Verilog 相比,VHDL语法比Verilog严谨。VHDL语法比Verilog冗长,所以建议学习Verilog做为FPGA开发语言。

Verilog inout端口

module test

(input wire sel ,input wire data_out ,inout wire data_bus ,input wire data_in

);assign data_in = data_bus ;assign data_bus = (sel == 1'b1)?data_out:1'bz; endmoduleVerilog中的系统任务和系统函数

verilog语言中定义了一些任务和函数,用于完成一些特殊功能,它们称为系统任务和系统函数,这些函数大多数只能在TB仿真中使用,使我们更方便验证。

·timescale 1ns/1ns //`timescale 表示时间尺度预编译指令 1ns/1ns 表示 时间单位 时间精度时间单位和时间精度由值1、10和100以及单位s、ms、us、ns、ps、fs组成。

时间单位定义了仿真过程与时间相关量的单位。仿真中使用“#数字” 表示延时 #10 表示延时10ns

主要函数如下:

1、 $display("%b + %b = %d",a,b,c);

`timescale 1ns/1nsmodule tb_test();reg [3:0] a ;reg [3:0] b ;reg [3:0] c ;initialbegin$display("hello");$display("Embedfire");a = 4'd5 ;b = 4'd6 ;c = a + b ;#100;$display("%b + %b = %d",a,b,c);endendmodule2 $write输出信息

`timescale 1ns/1nsmodule tb_test();reg [3:0] a ;reg [3:0] b ;reg [3:0] c ;initialbegin$write("hello") ;$write("Embedfire") ;a = 4'd5 ;b = 4'd6 ;c = a + b ;#100;$write("%b + %b = %d\n",a,b,c);endendmodule3 $strobe输出信息

`timescale 1ns/1nsmodule tb_test();reg [3:0] a ;reg [3:0] b ;reg [3:0] c ;initialbegin$strobe("strobe:%b + %b = %d",a,b,c);a = 4'd5 ;#display("display:%b + %b = %d",a,,b,c);b = 4'd6 ;c = a + b ;endendmodule4 $monitor用于持续监测变量

`timescale 1ns/1nsmodule tb_test();reg [3:0] a ;reg [3:0] b ;reg [3:0] c ;initialbegina = 4'd5 ;#100 ;b = 4'd6 ;#100 ;c = a + b ;endinitialbegin$monitor("%b + %b = %d ",a,b,c) ;endendmodule5 $stop用于暂停仿真,$finish用于仿真结束

`timescale 1ns/1nsmodule tb_test();initialbegin$display("hello") ;$display("Embedfire") ; #100 ;#display("Stop Simulation") ;$stop ;$display("Continue Simulation") ;#100 ;$display("Finish Simulation") ;#finish ; endendmodule6 $time为时间函数,返回64位当前仿真时间;$random用与产生随机函数,返回随机数。

`timescale 1ns/1nsmodule tb_test();reg [3:0] a ;always # 10 a = $random ;initialbegin$monitor("a = %d,time :%d",a,$time) ;endendmodule相关文章:

初识verilog HDL

为什么选择用Verilog HDL开发FPGA??? 硬件描述语言(Hardware Descriptipon Lagnuage,HDL)通过硬件的方式来产生与之对应的真实的硬件电路,最终实现所设计的预期功能,其设计方法与软件…...

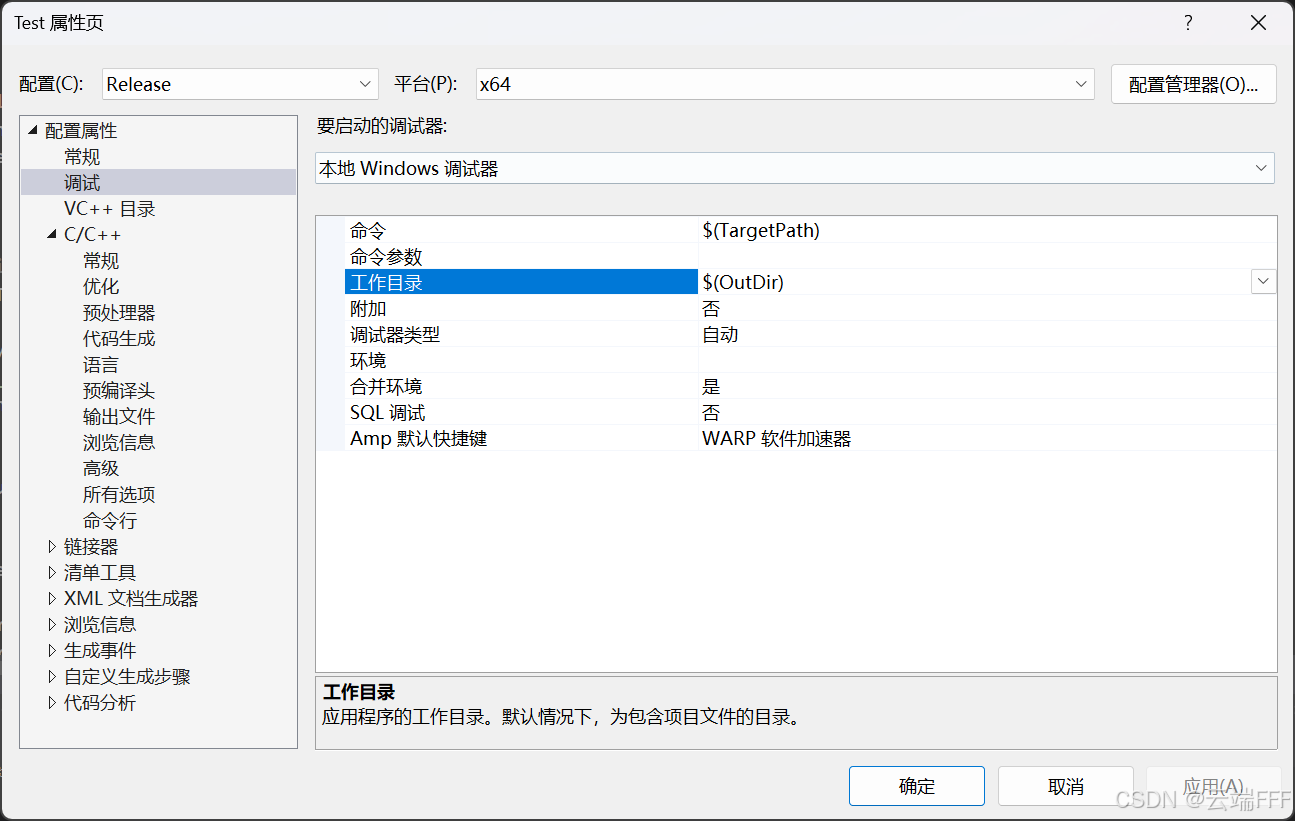

VS2015 + OpenCV + OnnxRuntime-Cpp + YOLOv8 部署

近期有个工作需求是进行 YOLOv8 模型的 C 部署,部署环境如下 系统:WindowsIDE:VS2015语言:COpenCV 4.5.0OnnxRuntime 1.15.1 0. 预训练模型保存为 .onnx 格式 假设已经有使用 ultralytics 库训练并保存为 .pt 格式的 YOLOv8 模型…...

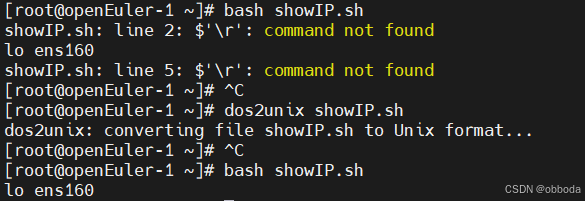

Notepad++上NppFTP插件的安装和使用教程

一、NppFTP插件下载 图示是已经安装好了插件。 在搜索框里面搜NppFTP,一般情况下,自带的下载地址容易下载失败。这里准备了一个下载连接:Release v0.29.10 ashkulz/NppFTP GitHub 这里我下载的是x86版本 下载好后在nodepad的插件里面选择打…...

Kotlin | Android Provider 的实现案例

目标 使用 Android Room 实现持久化库。 代码 Kotlin 代码编写 DemoDatabase,在build生成 DemoDatabase_Impl 疑问 Provider的数据会存在设备吗? 内部存储: 当使用 Room 创建数据库(如 DemoDatabase),数据库文件通常…...

频域自适应空洞卷积FADC详解

定义与原理 在探讨FADC的核心策略之前,我们需要深入了解其定义和工作原理。FADC是一种创新性的卷积技术,旨在克服传统空洞卷积的局限性。其核心思想是从 频谱分析的角度 改进空洞卷积,通过 动态调整膨胀率 来平衡有效带宽和感受野大小。 FADC的工作原理可以从以下几个方面…...

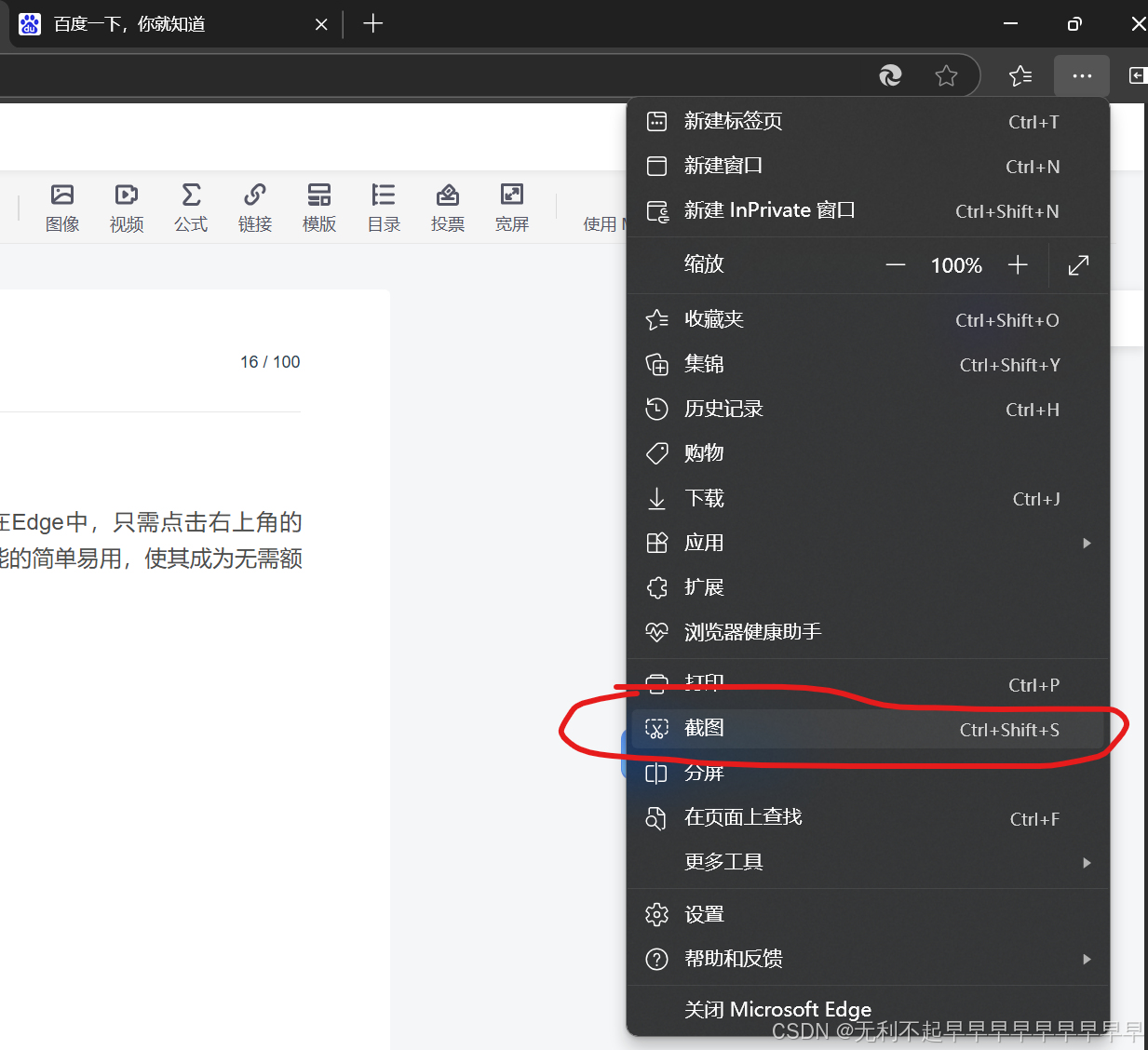

Edge浏览器内置的截长图功能

Edge浏览器内置截图功能 近年来,Edge浏览器不断更新和完善,也提供了长截图功能。在Edge中,只需点击右上角的“...”,然后选择“网页捕获”->“捕获整页”,即可实现长截图。这一功能的简单易用,使其成为…...

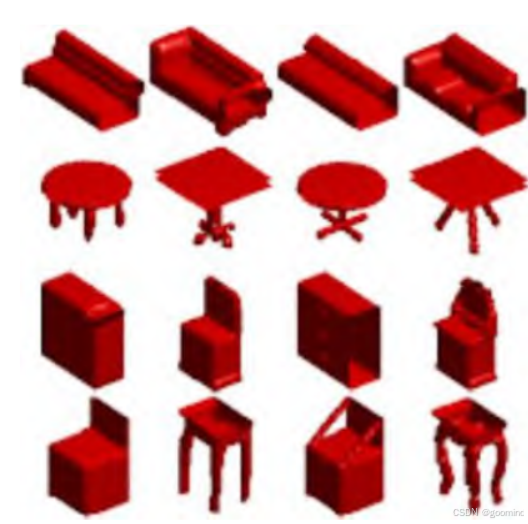

GAN的应用

5、GAN的应用 GANs是一个强大的生成模型,它可以使用随机向量生成逼真的样本。我们既不需要知道明确的真实数据分布,也不需要任何数学假设。这些优点使得GANs被广泛应用于图像处理、计算机视觉、序列数据等领域。上图是基于GANs的实际应用场景对不同G…...

Math Reference Notes: 希腊字母表

希腊字母(Greek alphabet)是古希腊语使用的字母系统,也是西方字母系统的先驱之一,广泛应用于现代数学、物理学、工程学以及各种科学领域。希腊字母有24个字母,它们分为大写和小写两种形式。 1. Alpha (Α, α) 发音&a…...

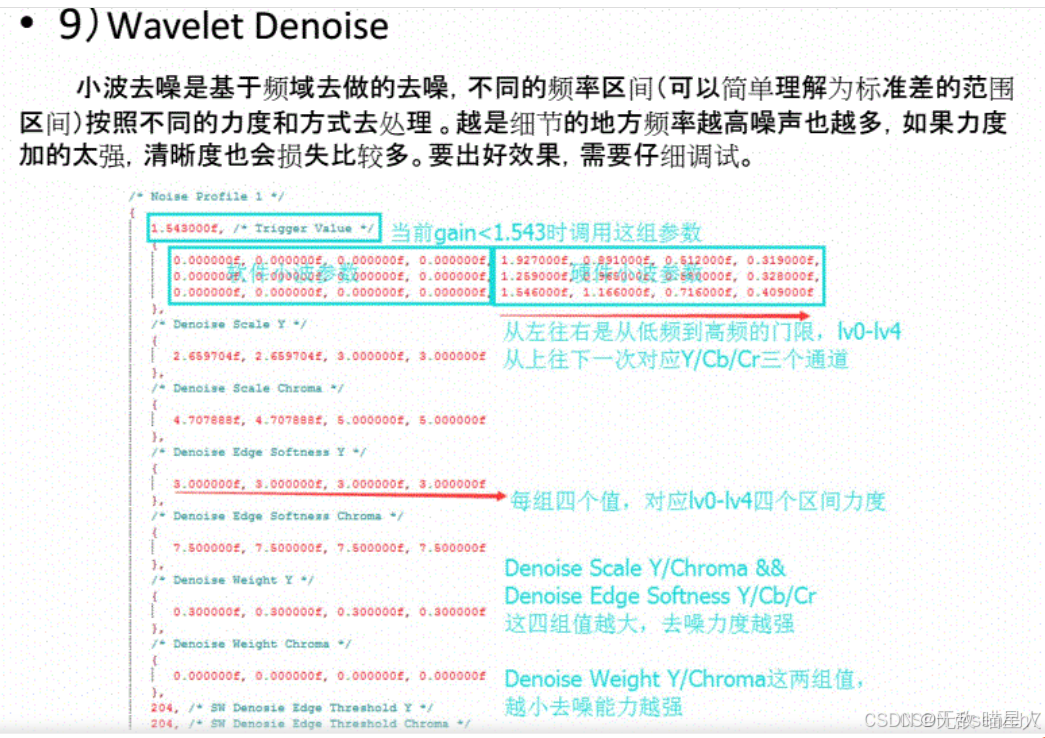

高通,联发科(MTK)等手机平台调优汇总

一、常见手机型号介绍: ISP除了用在安防行业,还有手机市场,以及目前新型的A/VR眼睛,机器3D视觉机器人,医疗内窥镜这些行业。 下面是一些最近几年发布的,,,旗舰SOC型号: 1.联发科:天玑92…...

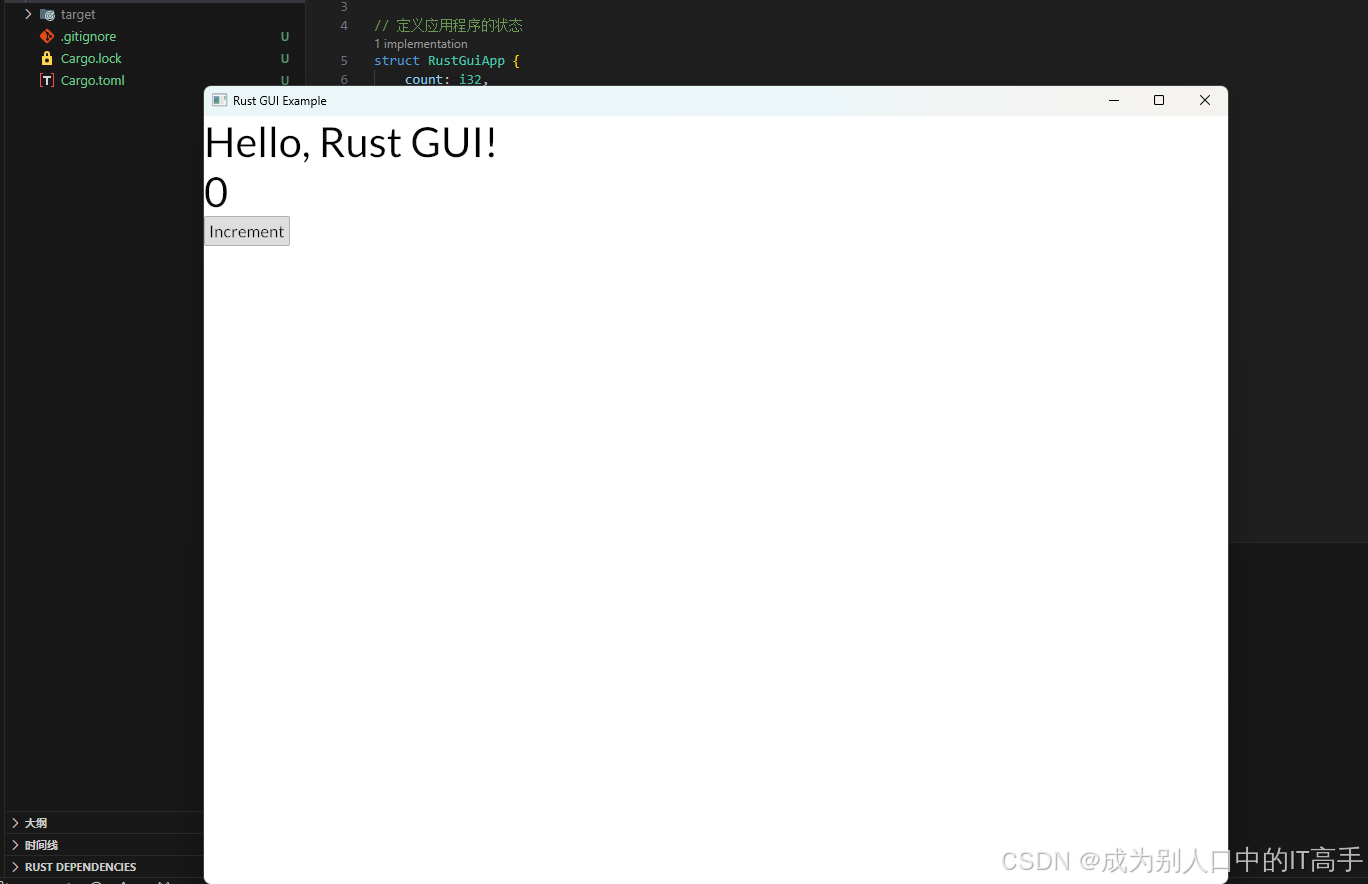

Rust语言使用iced实现简单GUI页面

使用cargo新建一个rust项目 cargo new gui_demo cd gui_demo 编辑Cargo.toml文件 ,添加iced依赖 [package] name "gui_demo" version "0.1.0" edition "2021"[dependencies] iced "0.4.2" 编辑src/main.rs文件: u…...

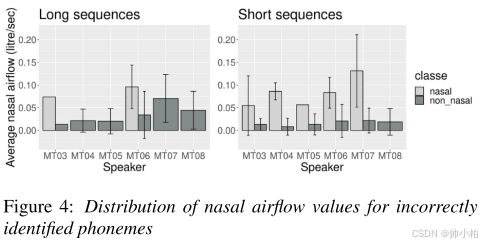

使用wav2vec 2.0进行音位分类任务的研究总结

使用wav2vec 2.0进行音位分类任务的研究总结 原文名称: Using wav2vec 2.0 for phonetic classification tasks: methodological aspects 研究背景 自监督学习在语音中的应用 自监督学习在自动语音识别任务中表现出色,例如说话人识别和验证。变换器模型…...

25/1/11 嵌入式笔记<esp32> 初入esp32

用Arduino平台,学习了点亮led灯。 //定义LED引脚 int led_pin 12;void setup() {//设定引脚为输出模式pinMode(led_pin,OUTPUT):}void loop() {// 点亮LED:digitalWrite(led_pin,HIGH);//延时1sdelay(1000);//熄灭LEDdigitalWrite(led_pin,LOW)://延时…...

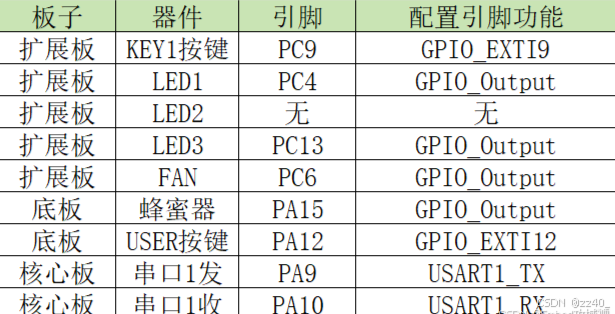

基于SMT32U575RIT单片机-中断练习

任务 查看手册对所有的拓展板上和相对应的底板的引脚对应的端口找到以下结论 通过STM32MX软件对各个引脚进行相应的配置 1.第一种切换模式电脑发送 #include "main.h" #include "icache.h" #include "usart.h" #include "gpio.h"/*…...

在Django的Serializer的列表数据中剔除指定元素

【Python工作随笔】 提问 如何在List序列化方法中剔除不要的元素,例如在成绩中剔除0 class BasicDescriptionSubjectBoxPlotSerializer(serializers.Serializer):语文 serializers.ListField(sourcescore_chinese)数学 serializers.ListField(sourcescore_math…...

我喜欢的数学题

偏向抖机灵性质的,考察理解的,而不是比拼计算量的,可能跟现在岁数大了算不明白了多少有点关系吧。 高高手,别太重计算,给普通孩子留条路。就算将来真的理工治国,也没必要都往人形计算机方面引导。毕竟你未来…...

Redis解决热key问题

当Redis遇到热key问题时,即某个或某些key被频繁访问,可能导致单个Redis节点负载过高,影响整个系统性能。以下是一些常见的解决方案: 1. 缓存预热与复制 缓存预热:在系统启动阶段,将热key对应的value预先加…...

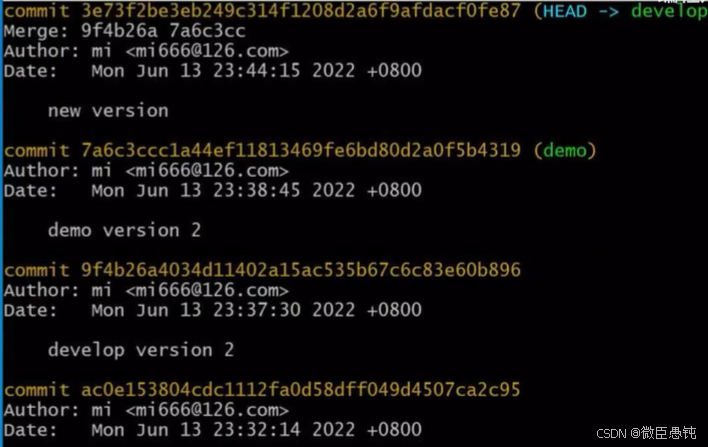

【git】-2 分支管理

目录 一、分支的概念 二、查看、创建、切换分支 1、查看分支-git branch 2、创建分支- git branch 分支名 3、切换分支- git checkout 分支名 三、git指针 -实现分支和版本间的切换 四、普通合并分支 git merge 文件名 五、冲突分支合并 【git】-初始gi…...

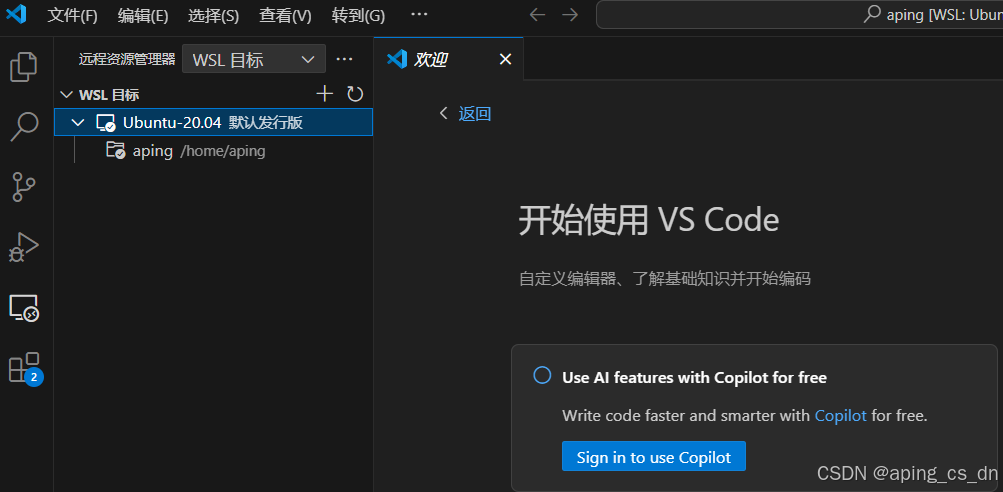

Win11+WLS Ubuntu 鸿蒙开发环境搭建(二)

参考文章 penHarmony南向开发笔记(一)开发环境搭建 OpenHarmony(鸿蒙南向开发)——标准系统移植指南(一) OpenHarmony(鸿蒙南向开发)——小型系统芯片移植指南(二&…...

Meilisearch ASP.Net Core API 功能demo

安装 MeiliSearch 0.15.5 0.15.5demo code using Meilisearch; using System.Data; using System.Text.Json; using System.Text.Json.Serialization;namespace MeiliSearchAPI {public class MeilisearchHelper{public MeilisearchHelper(){DefaultClient…...

程序员独立开发竞品分析:确定网站使用什么建站系统

要确定一个网站使用的建站系统,可以通过以下几种方法尝试分析: 查看页面源代码: 打开网站,右键点击页面并选择“查看页面源代码”。在代码中查找一些常见的建站系统标志,例如: WordPress 的迹象:…...

08-Spring 数据访问 - JDBC 详解

08. Spring 数据访问 - JDBC 详解 8.1 Spring JDBC 概述 Spring JDBC 是 Spring Framework 提供的数据访问抽象层,简化了 JDBC 的使用,消除了样板代码,同时保留了 JDBC 的完整控制能力。 8.1.1 传统 JDBC 的问题 // 传统 JDBC 代码 - 大量样板代码 public List<User&…...

DOL-CHS-MODS:一站式游戏体验优化整合方案

DOL-CHS-MODS:一站式游戏体验优化整合方案 【免费下载链接】DOL-CHS-MODS Degrees of Lewdity 整合 项目地址: https://gitcode.com/gh_mirrors/do/DOL-CHS-MODS 方案价值:为何选择整合方案 DOL-CHS-MODS 提供了一种智能化的游戏资源整合解决方案…...

中小企业AI落地:Qwen3-4B-Instruct-2507轻量部署实战

中小企业AI落地:Qwen3-4B-Instruct-2507轻量部署实战 中小企业想用上大模型,常被几个现实问题卡住:显存不够、部署太重、运维不会、成本太高。Qwen3-4B-Instruct-2507这个模型,就是为这类场景量身打磨的——它不追求参数堆砌&…...

FlowState Lab 日志分析与性能调优实战

FlowState Lab 日志分析与性能调优实战 1. 为什么需要关注模型服务性能 当你把FlowState Lab模型部署上线后,可能会遇到这样的情况:请求量一大,响应就开始变慢,甚至出现超时。这时候就需要关注服务的性能表现。性能调优不是玄学…...

一个防止GPT“降智”的简单方法

GPT客户端容易“降智”?教你一个简单解决办法 正文 最近一直感觉 GPT 手机客户端有点“降智”,回答质量不太稳定。 后来我拿同一账号做了对比,发现用手机浏览器登录网页版时,整体会正常不少,所以来给大家分享一下。 我…...

M9A小助手:重新定义《重返未来:1999》的智能化游戏体验

M9A小助手:重新定义《重返未来:1999》的智能化游戏体验 【免费下载链接】M9A 重返未来:1999 小助手 | Assistant For Reverse: 1999 项目地址: https://gitcode.com/gh_mirrors/m9/M9A M9A小助手是一款专为《重返未来:1999…...

部署到OpenCV项目)

从MATLAB到C++:手把手教你将鱼眼相机标定结果(Scaramuzza模型)部署到OpenCV项目

从MATLAB到C:手把手教你将鱼眼相机标定结果(Scaramuzza模型)部署到OpenCV项目 鱼眼相机因其超广视角在机器人导航、虚拟现实等领域应用广泛。但MATLAB标定结果如何无缝迁移到C工程环境?本文将彻底解决这个痛点,带您完成…...

Ostrakon-VL-8B辅助作业批改实战:识别手写公式与图表

Ostrakon-VL-8B辅助作业批改实战:识别手写公式与图表 每次批改理科作业,是不是都感觉眼睛快看花了?特别是面对几十份甚至上百份的手写作业,那些密密麻麻的公式、歪歪扭扭的电路图,还有各式各样的化学符号,…...

UI-Grid终极样式定制指南:10个LESS变量和主题系统使用技巧

UI-Grid终极样式定制指南:10个LESS变量和主题系统使用技巧 【免费下载链接】ui-grid UI Grid: an Angular Data Grid 项目地址: https://gitcode.com/gh_mirrors/ui/ui-grid UI-Grid作为Angular数据表格的强大解决方案,提供了灵活的样式定制系统。…...

Composio审计日志系统:全面追踪AI工具执行与操作记录

Composio审计日志系统:全面追踪AI工具执行与操作记录 【免费下载链接】composio Composio powers 1000 toolkits, tool search, context management, authentication, and a sandboxed workbench to help you build AI agents that turn intent into action. 项目…...