【FPGA】 MIPS 12条整数指令 【3】

实现乘除

修改框架

EX:实现带符号乘除法和无符号乘除法

HiLo寄存器:用于存放乘法和除法的运算结果。Hi、Lo为32bit寄存器。电路描述与实现RegFile思想一致

仿真

代码

DataMem.v

`include "define.v";

module DataMem(input wire clk,input wire ce,input wire we,input wire [31:0] addr,input wire [31:0] wtData,output reg [31:0] rdData

);reg [31:0] datamem [1023 : 0];always@(*) if(ce == `RamDisable)rdData = `Zero;elserdData = datamem[addr[11 : 2]]; always@(posedge clk)if(ce == `RamEnable && we == `RamWrite)datamem[addr[11 : 2]] = wtData;else ;endmoduledefine.v

`define RstEnable 1'b1

`define RstDisable 1'b0

`define RomEnable 1'b1

`define RomDisable 1'b0

`define Zero 0

`define Valid 1'b1

`define Invalid 1'b0

//I

`define Inst_ori 6'b001101

`define Inst_addi 6'b001000

`define Inst_andi 6'b001100

`define Inst_xori 6'b001110

`define Inst_lui 6'b001111

`define Inst_subi 6'b001001//lw sw

`define Inst_lw 6'b100011

`define Inst_sw 6'b101011//beq bne

`define Inst_beq 6'b000100

`define Inst_bne 6'b000101//R

`define Inst_r 6'b000000

`define Inst_add 6'b100000

`define Inst_sub 6'b100010

`define Inst_and 6'b100100

`define Inst_or 6'b100101

`define Inst_xor 6'b100110

`define Inst_sll 6'b000000

`define Inst_srl 6'b000010

`define Inst_sra 6'b000011`define Inst_jr 6'b001000

//J

`define Inst_j 6'b000010

`define Inst_jal 6'b000011//12

`define Inst_slt 6'b101010

`define Inst_bgtz 6'b000111

`define Inst_bltz 6'b000001

`define Inst_jalr 6'b001001

`define Inst_mult 6'b011000

`define Inst_multu 6'b011001

`define Inst_div 6'b011010

`define Inst_divu 6'b011011

`define Inst_mfhi 6'b010000

`define Inst_mflo 6'b010010

`define Inst_mthi 6'b010001

`define Inst_mtlo 6'b010011//

`define Inst_ll 6'b110000

`define Inst_sc 6'b111000

`define Inst_mfc0 6'b000000

`define Inst_mtc0 6'b000000

`define Inst_eret 6'b011000

`define syscall 6'b001100`define Nop 6'b000000

`define Or 6'b000001

`define Add 6'b000010

`define And 6'b000011

`define Xor 6'b000100

`define Lui 6'b000101

`define Sub 6'b000110

`define Sll 6'b000111

`define Srl 6'b001000

`define Sra 6'b001001

`define J 6'b001010

`define Jal 6'b001011

`define Beq 6'b001100

`define Bne 6'b001101

`define Jr 6'b001110

`define Lw 6'b010000

`define Sw 6'b010001

`define Bgtz 6'b010010

`define Bltz 6'b010011

`define Slt 6'b010100

`define Mult 6'b010101

`define Multu 6'b010110

`define Div 6'b010111

`define Divu 6'b011000//MEM

`define RamWrite 1'b1

`define RamUnWrite 1'b0

`define RamEnable 1'b1

`define RamDisable 1'b0EX.v

`include "define.v"

module EX(input wire rst,//input wire [5:0] op,input wire [5:0] op_i, input wire [31:0] regaData,input wire [31:0] regbData,input wire regcWrite_i,input wire [4:0]regcAddr_i,output reg [31:0] regcData,output wire regcWrite,output wire [4:0] regcAddr,output wire [5:0] op,output wire [31:0] memAddr,output wire [31:0] memData,input wire [31:0] rhi,input wire [31:0] rlo,output reg whi, output reg wlo, output reg [31:0] hiData, output reg [31:0] loData ); assign op = op_i;assign memAddr = regaData;assign memData = regbData;always@(*)if(rst == `RstEnable)regcData = `Zero;elsebegin//case(op)case(op_i)`Or:regcData = regaData | regbData;`Add:regcData = regaData + regbData;`And:regcData = regaData & regbData;`Xor:regcData = regaData ^ regbData;`Lui:regcData = regaData;/*`Lui:regcData = regaData | regbData;*/`Sub:regcData = regaData - regbData;`Sll:regcData = regbData << regaData;`Srl:regcData = regbData >> regaData;`Sra:regcData = ($signed(regbData)) >>> regaData;`J:regcData = `Zero;`Jr:regcData = `Zero;`Jal:regcData = regbData;`Beq:regcData = `Zero;`Bne:regcData = `Zero;`Bltz:regcData = `Zero;`Bgtz:regcData = `Zero;`Slt:regcData = ($signed(regaData)<$signed(regbData))?1'b1:1'b0;`Mult:beginwhi=`Valid;wlo=`Valid;{hiData,loData}=$signed(regaData)*$signed(regbData);end`Multu:beginwhi=`Valid;wlo=`Valid;{hiData,loData}=regaData*regbData;end`Div:beginwhi=`Valid;wlo=`Valid;hiData=$signed(regaData)%$signed(regbData);loData=$signed(regaData)/$signed(regbData);end`Divu:beginwhi=`Valid;wlo=`Valid;hiData=regaData%regbData;loData=regaData/regbData;enddefault:regcData = `Zero;endcaseendassign regcWrite = regcWrite_i;assign regcAddr = regcAddr_i;

endmodule

HiLo.v

`include "define.v"

module HiLo (input wire rst,input wire clk ,input wire [31:0] hiData,input wire [31:0] loData,input wire whi ,input wire wlo ,output reg [31:0] rhi,output reg [31:0] rlo

);reg [31:0]hi,lo;//????always@ (*)if(rst==`RstEnable)beginrhi = `Zero;rlo = `Zero;endelsebeginrhi = hi;rlo = lo;endalways@(posedge clk)if (rst ==`RstDisable && whi==`Valid)hi=hiData;else ;always@(posedge clk)if (rst ==`RstDisable && wlo==`Valid)lo=loData;else ;

endmodule

ID.v

`include "define.v";

module ID (input wire rst, input wire [31:0] pc, //Jinput wire [31:0] inst,input wire [31:0] regaData_i,input wire [31:0] regbData_i,output reg [5:0] op, output reg [31:0] regaData,output reg [31:0] regbData,output reg regaRead,output reg regbRead,output reg regcWrite,output reg [4:0] regaAddr,output reg [4:0] regbAddr, output reg [4:0] regcAddr,output reg [31:0] jAddr, //Joutput reg jCe//J);wire [5:0] inst_op = inst[31:26]; reg [31:0] imm;//Rwire[5:0] func = inst[5:0]; //Jwire [31:0] npc = pc + 4;always@(*)if(rst == `RstEnable)beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;jCe = `Invalid;//JjAddr = `Zero;//Jendelse beginjCe = `Invalid;//JjAddr = `Zero;//Jcase(inst_op)`Inst_ori:beginop = `Or; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_andi:beginop = `And; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_xori:beginop = `Xor; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_addi:beginop = `Add; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_subi:beginop = `Sub; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_lui:beginop = `Lui; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = inst[20:16];imm = {inst[15:0],16'h0};end`Inst_r:case(func)`Inst_add:beginop = `Add; regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_or:beginop = `Or;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sub:beginop = `Sub;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_and:beginop = `And;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_xor:beginop = `Xor;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sll:beginop = `Sll;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_srl:beginop = `Srl;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_sra:beginop = `Sra;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_jr:beginop = `Jr;regaRead = `Valid;//rsregbRead = `Invalid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = 5'b11111;jAddr = regaData;jCe = `Valid;imm = `Zero;end`Inst_jalr:beginop = `Jal;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[15:11]; //jAddr = regaData;jCe = `Valid;imm = npc;end`Inst_slt:beginop = `Slt;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11]; imm = `Zero;end`Inst_mult:beginop = `Mult;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = `Zero;end `Inst_multu:beginop = `Multu;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid; regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = `Zero;end `Inst_div:beginop = `Div;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = `Zero;end `Inst_divu:beginop = `Divu;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = `Zero;end default:beginregaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase//J`Inst_j:beginop = `J;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = `Zero;end `Inst_jal:beginop = `Jal;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = 5'b11111;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = npc;end//J `Inst_beq:beginop = `Beq;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData==regbData)?`Valid:`Invalid; /* if(regaData==regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bne:beginop = `Bne;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData!=regbData)?`Valid:`Invalid; /* if(regaData!=regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bgtz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==0)?`Valid:`Invalid;imm = 32'b0; //end`Inst_bltz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==1)?`Valid:`Invalid; //imm = 32'b0; //end`Inst_lw:beginop = `Lw;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}},inst[15:0]};end`Inst_sw:beginop = `Sw;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = {{16{inst[15]}},inst[15:0]};end default:beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase end/*always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaRead == `Valid)regaData = regaData_i;else regaData = imm;always@(*)if(rst == `RstEnable)regbData = `Zero; else if(regbRead == `Valid)regbData = regbData_i;elseregbData = imm; */

always@(*) if(rst == `RstEnable) regaData = `Zero; else if(op == `Lw || op == `Sw) regaData = regaData_i + imm; else if(regaRead == `Valid) regaData = regaData_i; else regaData = imm; always@(*) if(rst == `RstEnable) regbData = `Zero; else if(regbRead == `Valid) regbData = regbData_i; else regbData = imm;endmoduleIF.v

`include "define.v"

module IF(input wire clk,input wire rst,input wire [31:0] jAddr,//Jinput wire jCe,//Joutput reg ce,

output reg [31:0] pc

);always@(*)if(rst == `RstEnable)ce = `RomDisable;elsece = `RomEnable;

/* always@(posedge clk)if(ce == `RomDisable)pc = `Zero;elsepc = pc + 4;

*/always@(posedge clk)if(ce == `RomDisable)pc = `Zero;else if(jCe == `Valid)//Jpc = jAddr;elsepc = pc + 4;

endmoduleInstMem.v

`include "define.v"

module InstMem(input wire ce,input wire [31:0] addr,output reg [31:0] data

);reg [31:0] instmem [1023 : 0]; always@(*) if(ce == `RomDisable)data = `Zero;elsedata = instmem[addr[11 : 2]]; initialbegininstmem [0] = 32'h34011100; //ori r1,r0,1100h r1--32'h0000 1100instmem [1] = 32'h34020020; //ori r2,r0,0020h r2--32'h0000 0020instmem [2] = 32'h3403ff00; //ori r3,r0,ff00h r3--32'h0000 ff00instmem [3] = 32'h3404ffff; //ori r4,r0,ffffh r4--32'h0000 ffffinstmem [4] = 32'b000000_00001_00010_00000_00000_011001;//multu,r1,r2 22000instmem [5] = 32'b000000_00001_00010_00000_00000_011011;//divu,r1,r2 88instmem [6] = 32'h2005fffc; //addi r5,r0,fffc r5--32'hffff fffcinstmem [7] = 32'h34060002; //ori r6,r0,0002h r6--32'h0000 0002instmem [8] = 32'h3c071234; //lui r7,1234 r7--32'h1234 0000instmem [9] = 32'b000000_00101_00110_00000_00000_011000; //mult r5,r6instmem [10] = 32'b000000_00101_00110_00000_00000_011010; //div r5,r6/*instmem [4] = 32'h2005ffff; //addi r5,r0,ffff r5--32'hffff ffffinstmem [5] =32'b000000_00101_00100_00110_00000_101010; //slt r6,r5,r4instmem [6] =32'b000000_00100_00011_00110_00000_101010; //slt r6,r4,r3

*//* instmem [4] = 32'h3005ffff; //andi r5,r0,ffff r5--32'h0000 0000instmem [5] = 32'h3806ffff; //xori r6,r0,ffff r6--32'h0000 ffffinstmem [6] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffffinstmem [7] = 32'h3c081234; //lui r8,1234 r8--32'h1234 0000instmem [8] = 32'h35095679; //ori r9,r8,5678 r9--32'h1234 5679instmem [9] = 32'h212aa011; //addi r10,r9,a011 r10--32'h1233 f68ainstmem [10] = 32'h306b1111; //andi r11,r3,1111 r10--32'h0000 1100instmem [11] = 32'h254C1111; //subi r12,r10,1111 r12--32'h1234 e579

*/

/*instmem [4] = 32'h00222820; //add r5,r1,r2 r5--32'h0000 1120instmem [5] = 32'h00223025; //or r6,r1,r2 r6--32'h0000 1120instmem [6] = 32'h00223822; //sub r7,r1,r2 r7--32'h0000 10e0instmem [7] = 32'h00224024; //and r8,r1,r2 r8--32'h0000 0000instmem [8] = 32'h00224826; //xor r9,r1,r2 r9--32'h0000 1120instmem [9] =32'h3c0affff; //lui r10,ffff r10--32'hffff 0000instmem [10] = 32'h000a5840; //sll r11,ra,r10 r11--32'hfffe 0000instmem [11] = 32'h000a6042; //srl,r12,ra,r10 r12--32'h7fff 8000instmem [12] = 32'h000a6843; //sra r13,ra,r10 r13--32'hffff 8000*/ /*instmem [4] = 32'h3401001c; //ori r1,r0,1chinstmem [5] = 32'b000000_00001_00000_11111_00000_001001;//jalr r31,r1instmem [6] = 32'h3405ffff; //ori r5,r0,ffffh instmem [7] = 32'b000000_00001_00010_00101_00000_100000;//add,R5,R1,R2 instmem [8] = 32'b000000_11111_00000_00000_00000_001000;//jr r31

*/

/*instmem [4] = 32'b000000_00001_00010_00101_00000_100000;//add,R5,R1,R2 instmem [5] = 32'h3405ffff; //ori r5,r0,ffffh instmem [6] = 32'b000000_00010_00011_00110_00000_100101;//or,R6,R2,R3 instmem [7] = 32'b000111_00101_00000_0000000000000001;//bgtz r5,1instmem [8] = 32'b000000_00001_00010_00110_00000_100101;//or,R6,R1,R2 00001120instmem [9] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffffinstmem [10] = 32'b000000_00011_00100_00110_00000_100101;//or,R6,R3,R4 //instmem [10] = 32'b000001_00111_00000_1111111111111101;//bltz r7,-3 instmem [11] = 32'b000001_00111_00000_1111111111111010;//bltz r7,-6*///(r1)=0000 1100// +0000 0018//addr=0000 1118 // =1000100011000 // =100 0100 0110 // =446H // =46H // =70//mem[70]=(r6)/*instmem[6]=32'b101011_00001_00110_0000_0000_0001_1000; //sw r6,0x18(r1)instmem[7]=32'b100011_00001_00111_0000_0000_0001_1000; //lw r7,0x18(r1)*///(r7)=mem[70]end

endmoduleMEM.v

`include "define.v";

module MEM(input wire rst, input wire [5:0] op,input wire [31:0] regcData,input wire [4:0] regcAddr,input wire regcWr,input wire [31:0] memAddr_i,input wire [31:0] memData, input wire [31:0] rdData,output wire [4:0] regAddr,output wire regWr,output wire [31:0] regData, output wire [31:0] memAddr,output reg [31:0] wtData,output reg memWr, output reg memCe

);assign regAddr = regcAddr; assign regWr = regcWr; assign regData = (op == `Lw) ? rdData : regcData; assign memAddr = memAddr_i;always @(*) if(rst == `RstEnable) begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end elsecase(op) `Lw: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamEnable; end `Sw: begin wtData = memData; memWr = `RamWrite; memCe = `RamEnable; enddefault: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end endcase

endmoduleMIPS.v

`include "define.v";

module MIPS(input wire clk,input wire rst,input wire [31:0] instruction,input wire [31:0] rdData,//lsoutput wire romCe,output wire [31:0] instAddr,output wire [31:0] wtData,//lsoutput wire [31:0] memAddr,//lsoutput wire memCe,//lsoutput wire memWr//ls

);wire [31:0] regaData_regFile, regbData_regFile;wire [31:0] regaData_id, regbData_id; wire [31:0] regcData_ex;//wire [5:0] op; wire [5:0] op_id; //ls wire regaRead, regbRead;wire [4:0] regaAddr, regbAddr;wire regcWrite_id, regcWrite_ex;wire [4:0] regcAddr_id, regcAddr_ex;//Jwire [31:0] jAddr;wire jCe;//lswire [5:0] op_ex;wire[31:0] memAddr_ex,memData_ex;wire [5:0] regAddr_mem;wire [31:0] regData_mem;wire regWr_mem;//wire [31:0] hiData_ex;wire [31:0] loData_ex;wire whi_ex;wire wlo_ex;wire [31:0] rhi_ex;wire [31:0] rlo_ex;IF if0(.clk(clk),.rst(rst),.jAddr(jAddr),//J.jCe(jCe),//J.ce(romCe), .pc(instAddr));ID id0(.rst(rst), .pc(instAddr),//J.inst(instruction),.regaData_i(regaData_regFile),.regbData_i(regbData_regFile),//.op(op),.op(op_id),//ls.regaData(regaData_id),.regbData(regbData_id),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regcWrite(regcWrite_id),.regcAddr(regcAddr_id),.jAddr(jAddr),//J.jCe(jCe)//J);EX ex0(.rst(rst),//.op(op), .op_i(op_id), .regaData(regaData_id),.regbData(regbData_id),.regcWrite_i(regcWrite_id),.regcAddr_i(regcAddr_id),.regcData(regcData_ex),.regcWrite(regcWrite_ex),.regcAddr(regcAddr_ex),.op(op_ex),//ls.memAddr(memAddr_ex),//ls.memData(memData_ex),//ls.rhi(rhi_ex),.rlo(rlo_ex),.whi(whi_ex),.wlo(wlo_ex),.hiData(hiData_ex),.loData(loData_ex) ); HiLo hilo0(.rst(rst),.clk(clk),.rhi(rhi_ex),.rlo(rlo_ex),.whi(whi_ex),.wlo(wlo_ex),.hiData(hiData_ex),.loData(loData_ex) );MEM mem0(.rst(rst), .op(op_ex),.regcData(regcData_ex),.regcAddr(regcAddr_ex),.regcWr(regcWrite_ex),.memAddr_i(memAddr_ex),.memData(memData_ex), .rdData(rdData),.regAddr(regAddr_mem),.regWr(regWr_mem),.regData(regData_mem), .memAddr(memAddr),.wtData(wtData),.memWr(memWr), .memCe(memCe));RegFile regfile0(.clk(clk),.rst(rst),//.we(regcWrite_ex),.we(regWr_mem),//.waddr(regcAddr_ex),.waddr(regAddr_mem),//.wdata(regcData_ex),.wdata(regData_mem),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regaData(regaData_regFile),.regbData(regbData_regFile));endmodule

RegFile.v

`include "define.v"

module RegFile(input wire clk,input wire rst,input wire we,input wire [4:0] waddr,input wire [31:0] wdata,input wire regaRead,input wire regbRead,input wire [4:0] regaAddr,input wire [4:0] regbAddr,output reg [31:0] regaData,output reg [31:0] regbData

);reg [31:0] reg32 [31 : 0]; always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaAddr == `Zero)regaData = `Zero;elseregaData = reg32[regaAddr];always@(*)if(rst == `RstEnable) regbData = `Zero;else if(regbAddr == `Zero)regbData = `Zero;elseregbData = reg32[regbAddr];always@(posedge clk)if(rst != `RstEnable)if((we == `Valid) && (waddr != `Zero))reg32[waddr] = wdata;else ;

endmoduleSoC.v

module SoC(input wire clk,input wire rst

);wire [31:0] instAddr;wire [31:0] instruction;wire romCe;//lswire memCe, memWr; wire [31:0] memAddr;wire [31:0] rdData;wire [31:0] wtData;MIPS mips0(.clk(clk),.rst(rst),.instruction(instruction),.instAddr(instAddr),.romCe(romCe),.rdData(rdData), .wtData(wtData), .memAddr(memAddr), .memCe(memCe), .memWr(memWr) ); InstMem instrom0(.ce(romCe),.addr(instAddr),.data(instruction));//DataMemDataMem datamem0( .ce(memCe), .clk(clk), .we(memWr), .addr(memAddr), .wtData(wtData), .rdData(rdData) );

endmodule

soc_tb.v

`include "define.v"

module soc_tb;reg clk;reg rst;initialbeginclk = 0;rst = `RstEnable;#100rst = `RstDisable;#10000 $stop; endalways #10 clk = ~ clk;SoC soc0(.clk(clk), .rst(rst));

endmodule

相关文章:

【FPGA】 MIPS 12条整数指令 【3】

实现乘除 修改框架 EX:实现带符号乘除法和无符号乘除法 HiLo寄存器:用于存放乘法和除法的运算结果。Hi、Lo为32bit寄存器。电路描述与实现RegFile思想一致 仿真 代码 DataMem.v include "define.v"; module DataMem(input wire clk,input…...

Mac 部署Ollama + OpenWebUI完全指南

文章目录 💻 环境说明🛠️ Ollama安装配置1. 安装[Ollama](https://github.com/ollama/ollama)2. 启动Ollama3. 模型存储位置4. 配置 Ollama 🌐 OpenWebUI部署1. 安装Docker2. 部署[OpenWebUI](https://www.openwebui.com/)(可视化…...

蓝桥杯小白打卡第二天

789. 数的范围 题目描述 给定一个按照升序排列的长度为 n n n 的整数数组,以及 q q q 个查询。 对于每个查询,返回一个元素 k k k 的起始位置和终止位置(位置从 0 0 0 开始计数)。 如果数组中不存在该元素,则返…...

Docker Compose:容器编排的利器

Docker Compose:容器编排的利器 引言 随着容器技术的普及,Docker成为了当今最受欢迎的容器编排工具之一。Docker Compose作为Docker生态系统中的一部分,允许用户以声明式的方式定义和运行多容器Docker应用。本文将深入探讨Docker Compose的基本概念、工作原理、使用场景以…...

springboot项目的单元测试

文章目录 依赖编写单测代码一些注意点 依赖 依赖包含了 JUnit、Mockito、Spring Test 等常用的测试工具 <dependencies><dependency><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-test</artifactId><…...

JVM图文入门

往期推荐 【已解决】redisCache注解失效,没写cacheConfig_com.howbuy.cachemanagement.client.redisclient#incr-CSDN博客 【已解决】OSS配置问题_keyuewenhua.oss-cn-beijing.aliyuncs-CSDN博客 【排坑】云服务器docker部署前后端分离项目域名解析OSS-CSDN博客 微服…...

cursor 开发java项目教程简单上手

1.官网下载 Cursor - The AI Code Editor 下载完后注册账号,可以使用无限邮的方式 注册完之后 设置中文 可以选择设置为中文 Ctrl Shift X 进入设置页面输入chinese 然后重启 更改jdk跟maven仓库设置 ctrlshiftp 打开输入框后输入json,把下面代码…...

优化fm.jiecao.jcvideoplayer_lib中视频横竖屏自动适配原视频方案

fm.jiecao:jiecaovideoplayer:x.x.x 优化fm.jiecao.jcvideoplayer_lib中视频横竖屏自动适配原视频方案: 仅优化关键代码部分,源码: public void startWindowFullscreen() {Log.i(TAG, "startWindowFullscreen " " [" …...

aws(学习笔记第二十七课) 使用aws API Gateway+lambda体验REST API

aws(学习笔记第二十七课) 使用aws API Gatewaylambda体验REST API 学习内容: 使用aws API Gatewaylambda 1. 使用aws API Gatewaylambda 作成概要 使用api gateway定义REST API,之后再接收到了http request之后,redirect到lambda进行执行。…...

物联网的三层架构:感知层、网络层与应用层

物联网(Internet of Things, IoT)作为现代科技的重要组成部分,正在深刻改变我们的生活和工作方式。它将物理世界与数字世界无缝连接,通过智能设备、传感器和网络技术,实现数据的采集、传输和应用。物联网的架构通常分为…...

常用抓包工具tcpdump、Fiddler、Charles、Wireshark 和 Sniffmaster 下载地址

抓包大师官网下载地址 Sniff Master Download - Free TCP and HTTPS Proxy Sniffing Tool, Supports IOS Sniffing Fiddler classic官网下载地址 Download Fiddler Web Debugging Tool for Free by Telerik Fiddler Everywhere官网下载地址 The Ultimate Web Debugging Tool …...

π0开源了且推出自回归版π0-FAST——打造机器人动作专用的高效Tokenizer:比扩散π0的训练速度快5倍但效果相当

前言 过去的半个多月 deepseek火爆全球,我对其的解读也成了整整一个系列 详见《火爆全球的DeepSeek系列模型》,涉及对GRPO、MLA、V3、R1的详尽细致深入的解读 某种意义来讲,deepseek 相当于把大模型的热度 又直接拉起来了——相当于给大模…...

js-对象-JSON

JavaScript自定义对象 JSON 概念: JavaScript Object Notation,JavaScript对象标记法. JSON 是通过JavaScript 对象标记法书写的文本。 由于其语法简单,层次结构鲜明,现多用于作为数据载体,在网络中进行数据传输. json中属性名(k…...

Houdini subuv制作输出阵列图

在游戏开发中经常需要用到sheet阵列图,并用其制作翻页动画。通过Houdini强大的节点组合可以配合输出subuv阵列图供游戏引擎使用。 本文出处:https://zhuanlan.zhihu.com/p/391796978 博主参考学习并写该文。 1.在obj分类下创建font节点以进行测试&#…...

虚幻基础17:动画蓝图

能帮到你的话,就给个赞吧 😘 文章目录 animation blueprint图表(Graph): 编辑动画逻辑。变量(Variables): 管理动画参数。函数(Functions): 自定义…...

路由器及工作原理与常用路由配置命令详解

一、引言 在当今数字化时代,网络已经成为人们生活和工作中不可或缺的一部分。无论是家庭网络中的多台设备同时上网,还是企业网络中各个部门之间的数据传输和资源共享,都离不开网络设备的支持。路由器作为一种关键的网络设备,在网…...

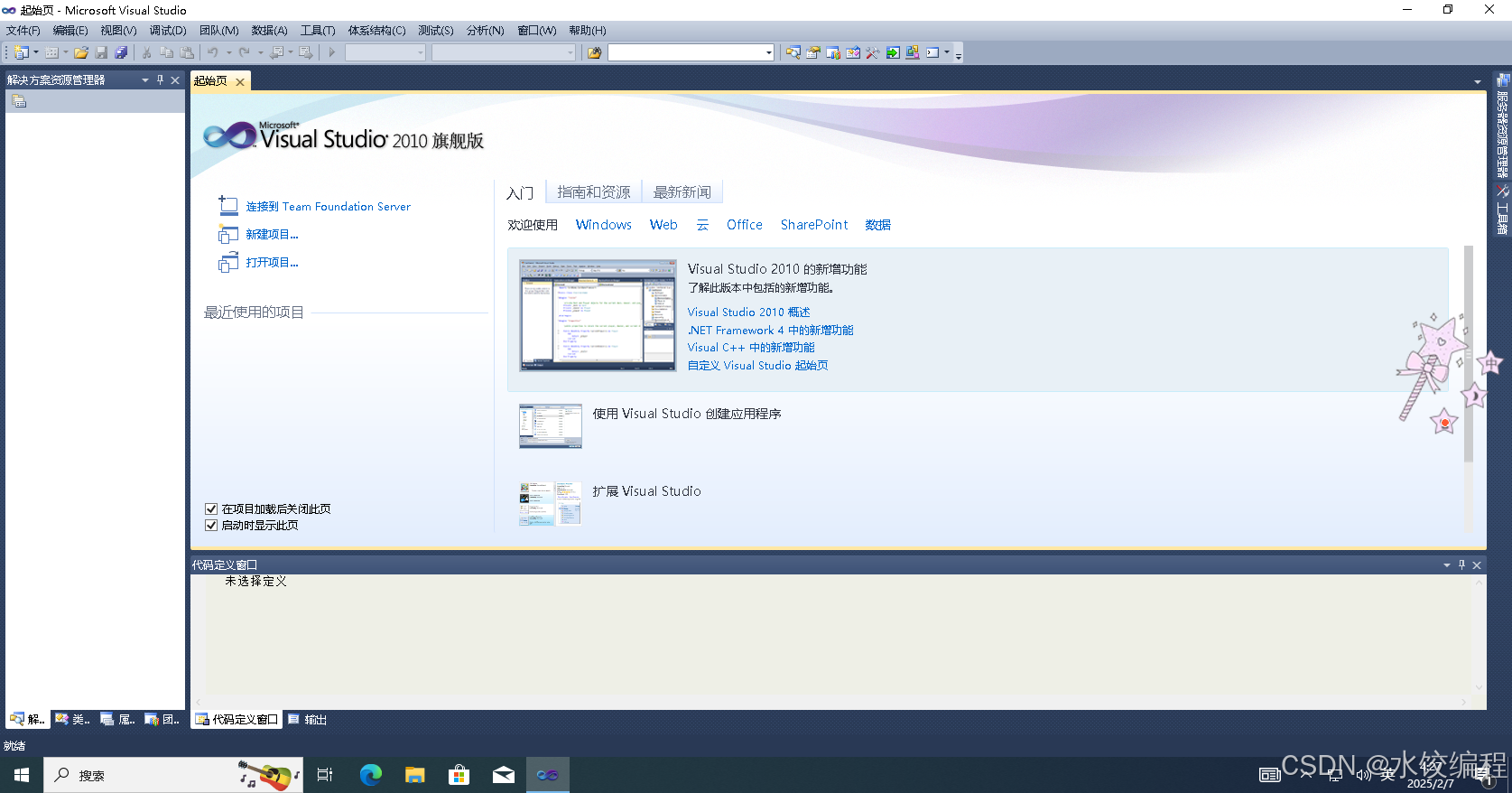

Windows编程:下载与安装 Visual Studio 2010

本节前言 在写作本节的时候,本来呢,我正在写的专栏,是 MFC 专栏。而 VS2010 和 VS2019,正是 MFC 学习与开发中,可以使用的两款软件。然而呢,如果你去学习 Windows API 知识的话,那么࿰…...

R语言 文本分析 天龙八部

起因, 目的: 前面有人对 “倚天屠龙记” 进行分析,我这里只是进行模仿而已。 完整的文件, 已经绑定了,反正读者可以找一下。 案例背景 小说《天龙八部》是金庸先生所著的武侠小说,也是“射雕三部曲”的前传。全书共50章,字数超过一百万字。故事发生在北宋末年,以大理…...

深度学习 Pytorch 建模可视化工具TensorBoard的安装与使用

50 TensorBoard的安装和使用 在深度学习建模过程中,为了能够快速绘制模型基本结构、观察模型评估指标伴随训练过程的动态变化情况,当然也为了能够观察图像数据,我们可以使用TensorBoard工具来进行Pytorch深度学习模型的可视化展示。 Tensor…...

【免费】2007-2019年各省科技支出占一般公共预算支出的比重数据

2007-2019年各省科技支出占一般公共预算支出的比重数据 1、时间:2007-2019年 2、来源:国家统计局、统计年鉴 3、指标:行政区划代码、地区名称、年份、科技支出占一般公共预算支出的比重 4、范围:31省 5、指标解释:…...

ARM TRCCONFIGR寄存器解析与调试追踪实践

1. ARM TRCCONFIGR寄存器深度解析在嵌入式系统开发和处理器调试领域,ARM架构的调试追踪技术一直是工程师们分析程序执行流程、定位性能瓶颈的利器。作为ARMv8/v9架构中调试系统的核心组件,TRCCONFIGR寄存器扮演着追踪配置控制中心的角色。这个64位的系统…...

观察Taotoken用量看板如何精细化管控API调用成本

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 观察Taotoken用量看板如何精细化管控API调用成本 对于依赖大模型API进行开发的项目团队而言,成本控制与预算管理是项目…...

)

libhv实战:手把手教你用C++写一个带自动重连的WebSocket客户端(附避坑指南)

libhv实战:构建高可靠WebSocket客户端的工程化实践 在实时数据采集和监控系统中,WebSocket客户端的稳定性直接决定了业务连续性。当网络出现闪断、服务端重启或负载波动时,简单的连接断开可能导致关键数据丢失。libhv作为高性能网络库&#x…...

Rust命令行工具开发实战:从架构设计到工程化发布

1. 项目概述:为什么是Rust,为什么是命令行工具?最近几年,如果你关注过系统编程或者高性能工具领域,Rust这个词出现的频率会越来越高。它不再是一个“未来之星”,而是实实在在地在重塑我们手中的工具链。我自…...

百度网盘Mac版SVIP破解终极指南:解锁70倍下载速度的完整方案

百度网盘Mac版SVIP破解终极指南:解锁70倍下载速度的完整方案 【免费下载链接】BaiduNetdiskPlugin-macOS For macOS.百度网盘 破解SVIP、下载速度限制~ 项目地址: https://gitcode.com/gh_mirrors/ba/BaiduNetdiskPlugin-macOS 百度网盘Mac版SVIP破解插件是一…...

不只是大小端:用Python脚本自动解析DBC文件中的Motorola和Intel信号

自动化解析DBC信号:Python实战Motorola与Intel字节顺序处理 在汽车电子和工业控制领域,CAN总线通信扮演着至关重要的角色。DBC文件作为描述CAN通信协议的标准化格式,包含了消息、信号以及各种通信参数的完整定义。对于测试工程师和嵌入式开发…...

Cool-Request全局请求头配置终极指南:告别重复配置的API测试新体验

Cool-Request全局请求头配置终极指南:告别重复配置的API测试新体验 【免费下载链接】cool-request IDEA API、Java Method debug tools 项目地址: https://gitcode.com/gh_mirrors/co/cool-request 你是否厌倦了在每个API请求中重复配置相同的认证Token、内容…...

Twitter数据抓取实战:x-twitter-scraper混合架构与生产环境部署指南

1. 项目概述:一个高效、稳定的Twitter数据抓取利器如果你正在寻找一个能绕过官方API限制,稳定、高效地抓取Twitter(现X平台)数据的工具,那么x-twitter-scraper这个开源项目绝对值得你花时间深入研究。它不是一个简单的…...

音频处理中的头部空间标准化:原理、工具与工程实践

1. 项目概述:一个为音频处理而生的“头部空间”工具如果你经常处理音频,尤其是人声干音,那你一定对“头部空间”这个概念不陌生。简单来说,它指的是人声录音中,人声峰值电平与数字满刻度(0 dBFS)…...

Dingo与Go模块:无缝集成现有Go项目的实用技巧

Dingo与Go模块:无缝集成现有Go项目的实用技巧 【免费下载链接】dingo A meta-language for Go that adds Result types, error propagation (?), and pattern matching while maintaining 100% Go ecosystem compatibility 项目地址: https://gitcode.com/gh_mi…...