FPGA调试笔记

XILINX SSTL属性电平报错

错误如下:

[DRC BIVRU-1] Bank IO standard Vref utilization: Bank 33 contains ports that use a reference voltage. In order to use such standards in a bank that is not configured to use INTERNAL_VREF, the bank's VREF pin must be used to supply the appropriate voltage. Example port: pe_spi_sdi[0] (SSTL18_I). However, the following VREF sites are occupied and can't be used to supply the necessary voltage: site IOB_X1Y87 (occupied by port pe_spi_sdi[1]), site IOB_X1Y61 (occupied by port spi_rx_data). Free up VREF sites or create an appropriate INTERNAL_VREF constraint.

错误核心问题

-

Bank 33 中的某些引脚(如

pe_spi_sdi[0])使用了需要参考电压的 SSTL18_I 标准(一种差分信号标准)。 -

但该 Bank 未启用内部参考电压(INTERNAL_VREF),因此必须通过 FPGA 的 专用 VREF 引脚 从外部提供参考电压。

-

而当前设计中,Bank 33 的 两个可用 VREF 引脚 已经被其他信号占用:

-

IOB_X1Y87被pe_spi_sdi[1]占用 -

IOB_X1Y61被spi_rx_data占用

-

-

结果:没有空闲的 VREF 引脚 为

pe_spi_sdi[0]提供参考电压,导致 DRC 报错。 -

根本原因

-

SSTL18_I 等高速信号标准需要参考电压(如 SSTL18_I 需要 0.9V 的 VREF)。

-

FPGA Bank 的 VREF 配置有两种方式:

-

内部 VREF(INTERNAL_VREF):通过 FPGA 内部电路生成(需在约束中启用)。

-

外部 VREF:通过专用引脚从外部电源输入(需硬件连接)。

-

-

你的设计选择了 外部 VREF,但所有可用的 VREF 引脚已被其他信号占用,导致冲突。

-

解决方法

方案 1:启用内部 VREF(推荐)

直接在约束文件中(如 XDC)添加以下命令,让 Bank 33 使用内部生成的参考电压:

tcl

复制

set_property INTERNAL_VREF 0.9 [get_iobanks 33]

优点:无需修改硬件或引脚分配,简单快捷。

注意:需确认 FPGA 型号支持内部 VREF,且电压值(0.9V)符合 SSTL18_I 标准要求。

方案 2:释放被占用的 VREF 引脚

将占用 VREF 引脚的信号(如

pe_spi_sdi[1]和spi_rx_data)移到非 VREF 引脚:tcl

复制

set_property PACKAGE_PIN "新引脚位置" [get_ports pe_spi_sdi[1]] set_property PACKAGE_PIN "新引脚位置" [get_ports spi_rx_data]

优点:保留外部 VREF 的灵活性。

缺点:需重新布局引脚,可能影响其他信号完整性。

方案 3:更换 IO 标准

如果设计允许,将

pe_spi_sdi[0]的 IO 标准改为 不需要 VREF 的类型(如 LVCMOS18):set_property IOSTANDARD LVCMOS18 [get_ports pe_spi_sdi*]

注意:需确保新标准与硬件电路兼容(如电平匹配)。

如何选择?

-

如果 硬件已设计为外部 VREF → 选 方案 2(修改引脚分配)。

-

如果 硬件未严格限定 VREF 来源 → 选 方案 1(内部 VREF,最简单)。

-

如果信号可改为普通电平标准 → 选 方案 3。

约束$tco_max和$trce_dly_max说明

对于系统时钟而言,时钟来自源端,数据来自目的端,这样数据和时钟会有延时。

约束时需要告诉FPGA数据返回最大延时和最小延时时间;

原时序如下图所示:

输入信号 $input_ports 相对于时钟 $input_clock 的 最大延迟 不能超过 $tco_max + $trce_dly_max,否则可能无法正确采样。”

-

输入延迟约束示例

(1) 最大输入延迟(Setup 检查)

set_input_delay -clock clk_100m -max [expr $Tco_max + $Trce_dly_max] [get_ports data_in]; # 计算:3ns + 2ns = 5ns

含义:

数据从外部芯片发出后,最晚5ns到达 FPGA 引脚。

由于采样点在5ns(半周期),工具会确保:

5ns(输入延迟) + Tsu(FPGA建立时间) < 5ns(采样点)

→ 实际要求Tsu < 0(显然不合理,需调整约束!)(2) 修正约束(考虑采样点在周期中心)

正确的约束应使 最大输入延迟 < 半周期(即

本人理解:时钟在上升沿采样,理论上100MHz的时钟中间采样,数据有效时间是5ns,如果delay时间大于等于5ns,那么没有建立时间,所以无法采集。特殊情况下我们可以特殊处理延时一个时钟周期或者半个时钟周期之后确定有效数据到FPGA时钟沿5ns以内。再做约束。<5ns),否则数据可能错过建立时间。

若实际Tco_max + Trce_dly_max = 5ns,则需 提前时钟采样边沿 或 降低输入延迟: -

最小输入延迟(Hold 检查)

set_input_delay -clock clk_100m -min [expr $Tco_min + $Trce_dly_min] [get_ports data_in]; # 计算:1ns + 1ns = 2ns

含义:

数据最早2ns到达 FPGA 引脚。工具会确保2ns(输入延迟) > Th(FPGA保持时间) -

关键点总结

-

采样点对齐:

100MHz 中心采样 → 数据应在5ns处稳定。 -

最大延迟:

Tco_max + Trce_dly_max必须 < 半周期 - Tsu。 -

最小延迟:

Tco_min + Trce_dly_min必须 > Th。 -

内部终端电阻(Internal Termination)

- Xilinx FPGA(如UltraScale+/7系列)的部分IO标准支持内部可编程终端电阻(如DCI,Digitally Controlled Impedance)。

- 这里A7和K7系列不支持内部中断电阻匹配命令;

-

若需在PCB上添加外部串行电阻(如信号线串联电阻),Xilinx工具无法直接“指令化”添加物理电阻,但可通过约束优化信号完整性:

-

替代方案

-

(1)使用DCI阻抗匹配

在单端信号(如DDR3的SSTL)中,通过IO标准激活DCI,自动匹配驱动阻抗和终端阻抗:set_property IOSTANDARD SSTL15 [get_ports {your_port}]-

DCI会在IO bank启用时自动调整阻抗(需参考Bank电压和标准)。

-

-

(2)调整驱动强度(DRIVE)

间接影响信号完整性(类似串联电阻效果):set_property DRIVE 8 [get_ports {your_port}] ; # 可选值:4, 8, 12, 16 (mA) - 这里的关系是:降低驱动强度(如设置

DRIVE 8mA)可等效增大驱动阻抗(R_drv↑),从而减少与传输线的阻抗失配。但FPGA的驱动阻抗通常非线性,无法精确替代物理电阻。 -

(3)减缓压摆率(减少高频噪声):

set_property SLEW SLOW [get_ports {your_port}] -

注意:此方法无法替代物理电阻的阻抗匹配功能,仅适用于短走线或低速信号。

-

(4)外部电阻

若需要精确的串行电阻(如源端匹配),必须在PCB设计时手动添加。

相关文章:

FPGA调试笔记

XILINX SSTL属性电平报错 错误如下: [DRC BIVRU-1] Bank IO standard Vref utilization: Bank 33 contains ports that use a reference voltage. In order to use such standards in a bank that is not configured to use INTERNAL_VREF, the banks VREF pin mu…...

基于Java(SSM)+Mysql实现移动大厅业务办理(增删改查)

基于 SSM 框架的移动业务大厅 数据库需要自行创建! 一、 整体基本实现情况 对本学期的 Java 作业 1 的 SOSO 移动大厅进行改进, 基于 SSM、JSP、Maven、Tomcat、MySQL 等实现。 二、 实现详情 1、 工程结构图 2、 工程结构各部分实现 (…...

音视频 ColorSpace色彩空间详解

前言 基于前篇介绍YUV格式,本文继续介绍另一个重要概念颜色空间,又叫色彩空间;主要用于在音视频开发中的色彩空间转换。 色彩空间Color Space 色彩空间由色彩模型和色域共同定义。当色彩模型与特定的描述相关联以后,就称为色彩空间。 色彩模型Color Model 色彩模型Col…...

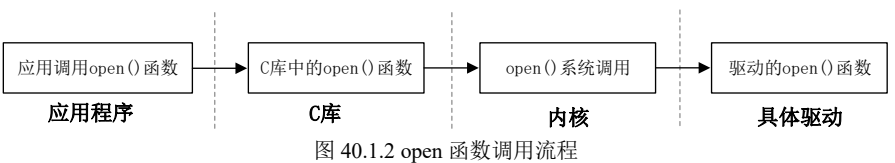

【字符设备驱动开发–IMX6ULL】(一)简介

【字符设备驱动开发–IMX6ULL】(一)简介 一、Linux驱动与裸机开发区别 1.裸机驱动开发回顾 1、底层,跟寄存器打交道,有些MCU提供了库。 spi.c:主机驱动(换成任何一个设备之后只需要调用此文件里面的…...

45 55跳跃游戏解题记录

先是55跳跃游戏,暴力解法会怎样?会超出时间限制,而且有很多细节要注意: func canJump(nums []int) bool {// 处理空数组情况,当nums只剩一个元素时,nums[i:]导致越界。if len(nums) 0 {return false}// 如…...

C++_STL之list篇

一、list的介绍 std::list是C标准模板库(STL)中的一个双向链表容器。与vector和deque不同,list不支持随机访问,但它在任何位置插入和删除元素都非常高效。 1.基本特性 (1)双向链表结构:每个元素都包含指向前驱和后继的指针 (2)非连续存储&…...

Go中的逃逸分析

什么是逃逸? 逃逸是指一个变量本来应该分配在栈(stack)上,但由于某些原因,最终被分配到了堆(heap)上。 类比: 栈就像一个临时的快餐盒,用来存放短期使用的数据。堆就像…...

Spring 声明式事务 万字详解(通俗易懂)

目录 Δ前言 一、声明式事务快速入门 1.为什么需要声明式事务? 2.定义: 3.应用实例: 二、声明式事务的传播机制 1.引出问题: 2.传播机制分类: 3.应用实例: 三、声明式事务的隔离机制 1.四种隔离级别&…...

MySQL 当中的锁

MySQL 当中的锁 文章目录 MySQL 当中的锁MySQL 中有哪些主要类型的锁?请简要说明MySQL 的全局锁有什么用?MySQL 的表级锁有哪些?作用是什么?元数据锁(MetaData Lock,MDL)意向锁(Inte…...

fyrox 2D和3D游戏的制作

目录 fyrox介绍 1. 核心特性 1.1 高性能渲染 1.2 跨平台支持 1.3 物理引擎集成 1.4 脚本系统 1.5 场景管理 2. 架构设计 2.1 渲染器 2.2 资源管理器 2.3 输入系统 2.4 音频引擎 2.5 网络模块 3. 使用场景 3.1 2D游戏 3.2 3D游戏 3.3 模拟与教育应用 4. 在游戏…...

[Linux]基础IO

基础IO C文件IO相关操作磁盘文件与内存文件inode(index node)硬链接与软连接硬链接软连接总结 动静态库静态库动态库总结 C文件IO相关操作 当前路径:进程运行的时候,所处的路径叫做当前路径 打开文件的时候,一定是进…...

力扣刷题-热题100题-第27题(c++、python)

21. 合并两个有序链表 - 力扣(LeetCode)https://leetcode.cn/problems/merge-two-sorted-lists/description/?envTypestudy-plan-v2&envIdtop-100-liked 常规法 创建一个新链表,遍历list1与list2,将新链表指向list1与list2…...

Vue3 其它API Teleport 传送门

Vue3 其它API Teleport 传送门 在定义一个模态框时,父组件的filter属性会影响子组件的position属性,导致模态框定位错误使用Teleport解决这个问题把模态框代码传送到body标签下...

windows下安装sublime

sublime4 alpha 4098 版本 下载 可以根据待破解的版本选择下载 https://www.sublimetext.com/dev crack alpha4098 的licence 在----- BEGIN LICENSE ----- TwitterInc 200 User License EA7E-890007 1D77F72E 390CDD93 4DCBA022 FAF60790 61AA12C0 A37081C5 D0316412 4584D…...

golang 的strconv包常用方法

目录 1. 字符串与整数的转换 2. 字符串与浮点数的转换 3. 布尔值的转换 4. 字符串的转义 5. 补充:rune 类型的使用 方法功能详解 代码示例: 1. 字符串与整数的转换 方法名称功能描述示例Atoi将字符串转换为十进制整数。strconv.Atoi("123&q…...

ComplexE的代码注释

目录 dataloader.pymodel.pyrun.py 先安装软件,配置环境,搞了一周。再看代码写注释搞了一周。中间隔了一周。再安装环境跑代码又一周。最后结果是没结果。自己电脑内存带不动。还不想配电脑,又不会用GPU服务器。哭死哭死。心态崩了。直接发吧…...

vector<int> 的用法

vector<int> 是 C 标准模板库(STL)中的一个容器,用于存储动态大小的整数序列。以下是它的主要用法: 基本操作 1. 创建和初始化 #include <vector> using namespace std;vector<int> v1; // 空vector vector<int>…...

Java高级JVM知识点记录,内存结构,垃圾回收,类文件结构,类加载器

JVM是Java高级部分,深入理解程序的运行及原理,面试中也问的比较多。 JVM是Java程序运行的虚拟机环境,实现了“一次编写,到处运行”。它负责将字节码解释或编译为机器码,管理内存和资源,并提供运行时环境&a…...

名言警句1

1、嫉妒是欲望的衍生,而欲望则是成长的驱动,说到底每个人都是为了成长,为了不居人后,在成长的过程中,我们可以让欲望枝繁叶茂,但不能让嫉妒开花结果 2、人生无法奢求更多,我们有健康的身体&…...

【STL】queue

q u e u e queue queue 是一种容器适配器,设计为先进先出( F i r s t I n F i r s t O u t , F I F O First\ In\ First\ Out,\ FIFO First In First Out, FIFO)的数据结构,有两个出口,将元素推入队列的操作称为 p u …...

QXmpp入门

QXmpp 是一个基于 Qt 的 XMPP (Jabber) 协议实现库,用于开发即时通讯(IM)、聊天应用和实时协作系统。它支持客户端和服务端开发,提供完整的 XMPP 核心功能扩展。 1. 核心功能 XMPP 核心协议支持 支持 RFC 6120 (XMPP Core) 和 RFC 6121 (XMPP IM) 基础功能:认证、在线状态…...

使用cursor为代码添加注释

1. add-comments.md英文 You are tasked with adding comments to a piece of code to make it more understandable for AI systems or human developers. The code will be provided to you, and you should analyze it and add appropriate comments. To add comments to …...

20250330-傅里叶级数专题之离散时间傅里叶变换(4/6)

4. 傅里叶级数专题之离散时间傅里叶变换 20250328-傅里叶级数专题之数学基础(0/6)-CSDN博客20250330-傅里叶级数专题之傅里叶级数(1/6)-CSDN博客20250330-傅里叶级数专题之傅里叶变换(2/6)-CSDN博客20250330-傅里叶级数专题之离散傅里叶级数(3/6)-CSDN博客20250330-傅里叶级数专…...

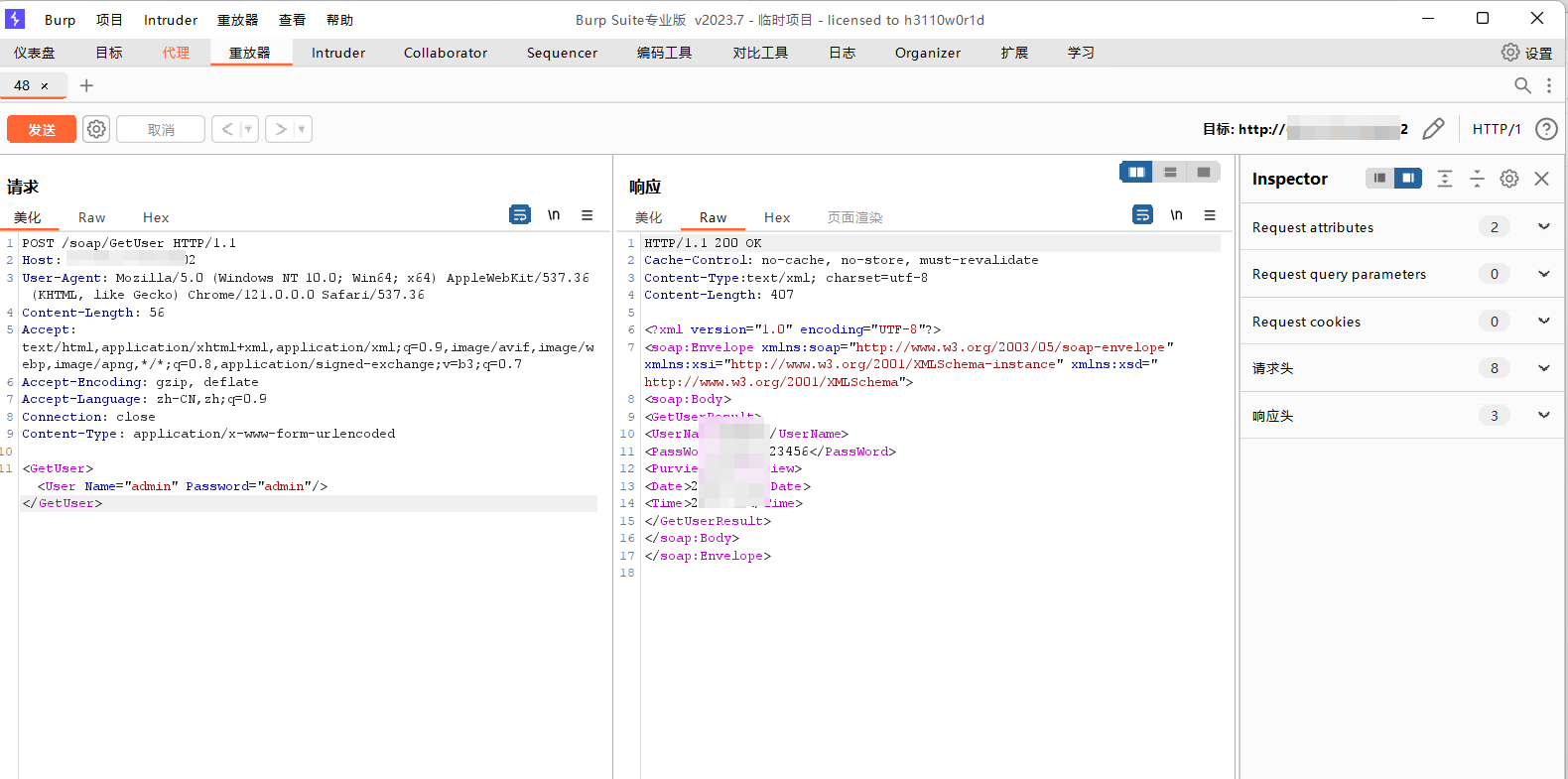

漏洞挖掘---迅饶科技X2Modbus网关-GetUser信息泄露漏洞

一、迅饶科技 X2Modbus 网关 迅饶科技 X2Modbus 网关是功能强大的协议转换利器。“X” 代表多种不同通信协议,能将近 200 种协议同时转为 Modbus RTU 和 TCP 服务器 。支持 PC、手机端等访问监控,可解决组态软件连接不常见控制设备难题,广泛…...

Java进阶——位运算

位运算直接操作二进制位,在处理底层数据、加密算法、图像处理等领域具有高效性能和效率。本文将深入探讨Java中的位运算。 本文目录 一、位运算简介1. 与运算2. 或运算异或运算取反运算左移运算右移运算无符号右移运算 二、位运算的实际应用1. 权限管理2. 交换两个变…...

golang strings包常用方法

方法名称功能描述示例strings.Join将字符串切片中的元素连接成一个字符串,使用指定的分隔符。strings.Join([]string{"hello", "world"}, " ")strings.HasPrefix检查字符串是否以指定的前缀开头。strings.HasPrefix("hello"…...

网络安全之前端学习(css篇2)

那么今天我们继续来学习css,预计这一章跟完后,下一章就是终章。然后就会开始js的学习。那么话不多说,我们开始吧。 字体属性 之前讲到了css可以改变字体属性,那么这里来详细讲一讲。 1.1字体颜色 之前讲到了对于字体改变颜色食…...

PS底纹教程

1.ctrlshiftU 去色 2.新建纯色层 颜色中性灰;转换为智能对象 3.纯色层打开滤镜(滤镜库); 素描下找到半调图案,数值调成大小5对比1; 再新建一层,素描下找到撕边,对比拉到1&#x…...

NX/UG二次开发—CAM获取加工操作的最低Z深度值的方法

网上已经有些大佬给出了解决方案,但是基本有两种,一种内部函数,另外一种就是导出程序的刀轨文件找坐标计算。使用内部函数进行操作,可以自己学习,不做解释。下面只是针对第二种进行说明,参考胡君老师的教程…...

解决pyinstaller GUI打包时无法打包图片问题

当我们的python GuI在开发时。经常会用到图片作为背景,但是在打包后再启动GUI后却发现:原先调试时好端端的背景图片竟然不翼而飞或者直接报错。这说明图片没有被pyinstaller一起打包…… 要解决这个问题很简单,就是更改图片的存储方式。 tk…...