Xilinx系列FPGA实现HDMI2.1视频收发,支持8K@60Hz分辨率,提供2套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 我已有的4K/8K视频处理解决方案

- 我已有的FPGA图像处理方案

- 3、详细设计方案

- 设计框图

- 硬件设计架构

- 本HDMI2.1性能参数

- 8K视频输入源

- Video PHY Controller

- HDMI 2.1 Receiver Subsystem

- 8K HDMI 解码后的视频流走向

- 8K HDMI 解码后的音频流走向

- HDMI 2.1 Transmitter Subsystem

- 视频输出显示

- vivado逻辑工程源码架构

- vitis软件工程源码架构

- 4、工程源码1详解-->ZU7EV,HDMI2.1输入转输出版本

- 5、工程源码2详解-->ZU19EG,HDMI2.1输入转输出版本

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证并演示

- 准备工作

- HDMI2.1视频收发演示

- 8、福利:工程源码获取

Xilinx系列FPGA实现HDMI2.1视频收发,支持8K@60Hz分辨率,提供2套工程源码和技术支持

1、前言

Xilinx系列FPGA实现8K视频收发现状:

目前Xilinx系列FPGA实现提供了多种8K视频收发方案;对于纯FPGA而言,需要用到GT高速接口资源实现编解码,但要求UltraScale+及其以上系列FPGA,以HDMI2.1为例,Xilinx官方提供了基于Video PHY Controller为核心的一整套HDMI2.1收发方案,此外,还可以直接使用GT高速接口IP核配置为GT-HDMI编解码模式,或者配置为DP编解码模式;对于Zynq-UltraScale+系列FPGA而言,既可以使用PL端的GT高速接资源做8K视频收发,也可以使用PS端的DP外设做8K视频收发;本博主擅长Xilinx-UltraScale+系列FPGA实现HDMI2.1视频收发方案设计,本设计采用基于Video PHY Controller为核心的一整套HDMI2.1收发方案,最高支持3840x2160@120Hz或者7680×4320@60Hz;

工程概述

本设计基于Xilinx系列FPGA的GT告诉接口实现HDMI2.1工程解决方案,最高支持3840x2160@120Hz或者7680×4320@60Hz;基于目前市场主流需求,本设计共设计了HDMI2.1接收发送工程,最高支持3840x2160@120Hz或者7680×4320@60Hz;

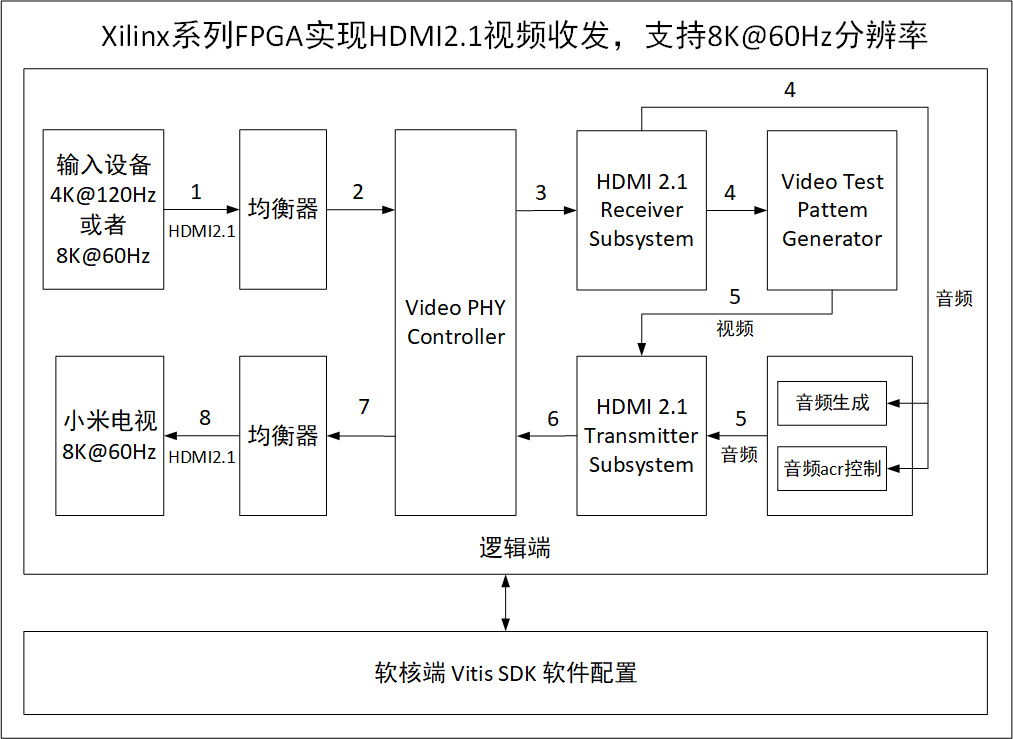

使用Xilinx-UltraScale+系列FPGA 的GT高速接口资源做3840x2160@120Hz或者7680×4320@60Hz的HDMI2.1视频收发实验;8K视频输入源使用专用视频发生器或者机顶盒,将输入设备分辨率设置为3840x2160@120Hz或者7680×4320@60Hz,然后用HDMI2.1线缆连接至FPGA开发板的HDMI2.1输入接口;然后经过FPGA开发板板载的NB7NQ621M或者其他同等功能的重定时器芯片实现恢复和重定时高速信号;然后输入差分视频信号直接连到FPGA的GT高速BANK上;然后调用Xilinx官方的Video PHY Controller IP核接收HDMI2.1输入视频并做串并转换工作,将原来高速串行信号解串为4路40bit的AXI4-Stream并行数据;然后调用Xilinx官方的HDMI 2.1 Receiver Subsystem IP核做8K超清视频的解码工作,同时解码出AXI4-Stream流的音频流和视频流;解码后的AXI4-Stream视频流进入Xilinx官方的TPG IP核,该IP在没有外部AXI4-Stream视频流进入时输出彩条视频,否则输出外部AXI4-Stream视频;同时解码后的AXI4-Stream音频流进入Xilinx官方的音频模块;至此,HDMI2.1的接收解码工作已经完成,此时可以对解码后的视频进行个性化处理了,比如缓存、缩放、卷积之类的,本工程做回环输出操作;然后Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核做8K音视频的编码工作,可同时编码视频流和音频流,并输出4路AXI4-Stream流和DDC控制信号;4路AXI4-Stream流进入前面调用的Video PHY Controller IP核做8K视频并串转化工作,将原4路20bit的AXI4-Stream并行数据串化为高速串行信号,输出的差分视频数据信号直接从FPGA的GT高速BANK输出,差分时钟信号直接从FPGA的LVDS高速BANK输出,HDMI2.1高速差分信号再进入FPGA开发板板载的NB7NQ621M或其他同等功能的驱动芯片,以增强高速信号的输出驱动能力;最后使用HDMI2.1线缆连接至显示器即可输出显示3840x2160@120Hz或者7680×4320@60Hz视频;

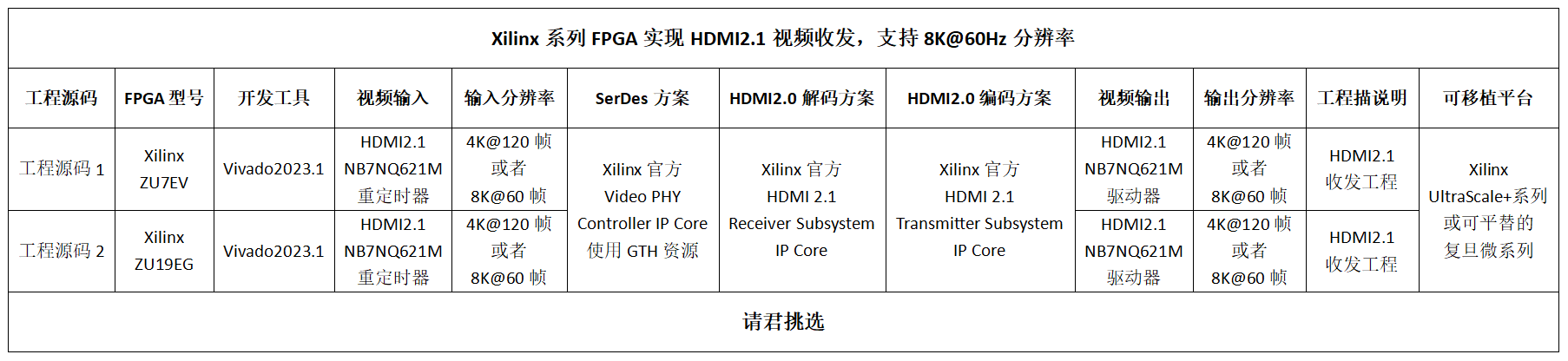

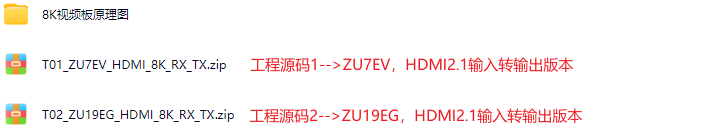

上述IP和IC需要SDK或者vitis配置,所以需要调用MicroBlaze或者Zynq软核;针对目前市面上主流的项目需求,本博客共设计了2套工程源码,详情如下:

现对上述2套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx-Zynq UltraScale+ xczu7ev-ffvc1156-2-i;8K视频输入源使用专用视频发生器或者机顶盒,将输入设备分辨率设置为3840x2160@120Hz或者7680×4320@60Hz,然后用HDMI2.1线缆连接至FPGA开发板的HDMI2.1输入接口;然后经过FPGA开发板板载的NB7NQ621M或者其他同等功能的重定时器芯片实现恢复和重定时高速信号;然后输入差分视频信号直接连到FPGA的GT高速BANK上;然后调用Xilinx官方的Video PHY Controller IP核接收HDMI2.1输入视频并做串并转换工作,将原来高速串行信号解串为4路40bit的AXI4-Stream并行数据;然后调用Xilinx官方的HDMI 2.1 Receiver Subsystem IP核做8K超清视频的解码工作,同时解码出AXI4-Stream流的音频流和视频流;解码后的AXI4-Stream视频流进入Xilinx官方的TPG IP核,该IP在没有外部AXI4-Stream视频流进入时输出彩条视频,否则输出外部AXI4-Stream视频;同时解码后的AXI4-Stream音频流进入Xilinx官方的音频模块;至此,HDMI2.1的接收解码工作已经完成,此时可以对解码后的视频进行个性化处理了,比如缓存、缩放、卷积之类的,本工程做回环输出操作;然后Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核做8K音视频的编码工作,可同时编码视频流和音频流,并输出4路AXI4-Stream流和DDC控制信号;4路AXI4-Stream流进入前面调用的Video PHY Controller IP核做8K视频并串转化工作,将原4路20bit的AXI4-Stream并行数据串化为高速串行信号,输出的差分视频数据信号直接从FPGA的GT高速BANK输出,差分时钟信号直接从FPGA的LVDS高速BANK输出,HDMI2.1高速差分信号再进入FPGA开发板板载的NB7NQ621M或其他同等功能的驱动芯片,以增强高速信号的输出驱动能力;最后使用HDMI2.1线缆连接至显示器即可输出显示3840x2160@120Hz或者7680×4320@60Hz视频;本设计使用UltraScale-GTH高速接口,适用于Xilinx-UltraScale+系列FPGA实现HDMI2.1视频收发应用;

工程源码2

开发板FPGA型号为Xilinx-Zynq UltraScale+ xczu19eg-ffvc1760-2-i;8K视频输入源使用专用视频发生器或者机顶盒,将输入设备分辨率设置为3840x2160@120Hz或者7680×4320@60Hz,然后用HDMI2.1线缆连接至FPGA开发板的HDMI2.1输入接口;然后经过FPGA开发板板载的NB7NQ621M或者其他同等功能的重定时器芯片实现恢复和重定时高速信号;然后输入差分视频信号直接连到FPGA的GT高速BANK上;然后调用Xilinx官方的Video PHY Controller IP核接收HDMI2.1输入视频并做串并转换工作,将原来高速串行信号解串为4路40bit的AXI4-Stream并行数据;然后调用Xilinx官方的HDMI 2.1 Receiver Subsystem IP核做8K超清视频的解码工作,同时解码出AXI4-Stream流的音频流和视频流;解码后的AXI4-Stream视频流进入Xilinx官方的TPG IP核,该IP在没有外部AXI4-Stream视频流进入时输出彩条视频,否则输出外部AXI4-Stream视频;同时解码后的AXI4-Stream音频流进入Xilinx官方的音频模块;至此,HDMI2.1的接收解码工作已经完成,此时可以对解码后的视频进行个性化处理了,比如缓存、缩放、卷积之类的,本工程做回环输出操作;然后Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核做8K音视频的编码工作,可同时编码视频流和音频流,并输出4路AXI4-Stream流和DDC控制信号;4路AXI4-Stream流进入前面调用的Video PHY Controller IP核做8K视频并串转化工作,将原4路20bit的AXI4-Stream并行数据串化为高速串行信号,输出的差分视频数据信号直接从FPGA的GT高速BANK输出,差分时钟信号直接从FPGA的LVDS高速BANK输出,HDMI2.1高速差分信号再进入FPGA开发板板载的NB7NQ621M或其他同等功能的驱动芯片,以增强高速信号的输出驱动能力;最后使用HDMI2.1线缆连接至显示器即可输出显示3840x2160@120Hz或者7680×4320@60Hz视频;本设计使用UltraScale-GTH高速接口,适用于Xilinx-UltraScale+系列FPGA实现HDMI2.1视频收发应用;

本博客详细描述了Xilinx系列FPGA实现HDMI2.1视频收发的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网以及其他开源免费获取渠道等等),若大佬们觉得有所冒犯,请私信批评教育;部分模块源码转载自上述网络,版权归原作者所有,如有侵权请联系我们删除;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我已有的4K/8K视频处理解决方案

我的主页有FPGA 4K/8K视频处专栏,该专栏有4K/8K视频处理,包括简单的4K/8K视频收发、4K/8K视频缩放、4K/8K视频拼接等等;以下是专栏地址:

点击直接前往

我已有的FPGA图像处理方案

我的主页目前有FPGA图像处理专栏,改专栏收录了我目前手里已有的FPGA图像处理方案,包括图像缩放、图像识别、图像拼接、图像融合、图像去雾、图像叠加、图像旋转、图像增强、图像字符叠加等等;以下是专栏地址:

点击直接前往

3、详细设计方案

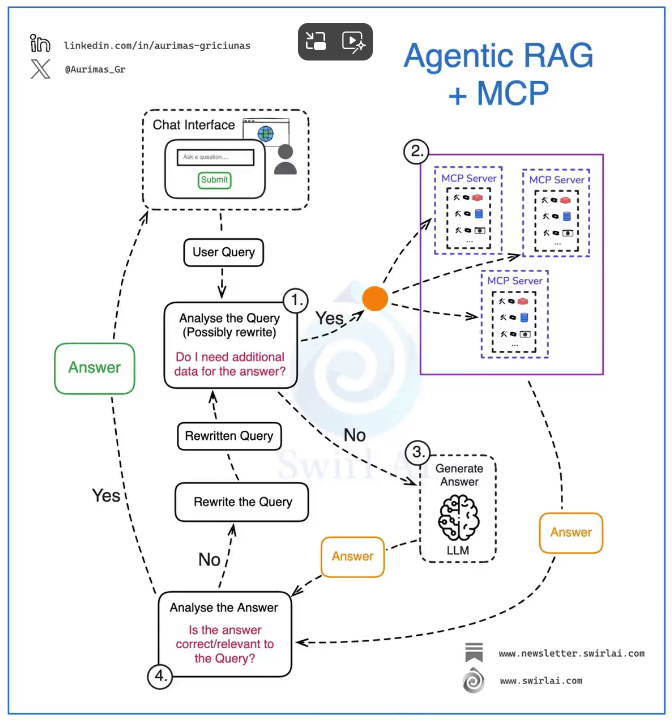

设计框图

本设计使用的是Xilinx官方推荐的方案,该方案大致如下:

具体到本设计的工程详细设计方案框图如下:

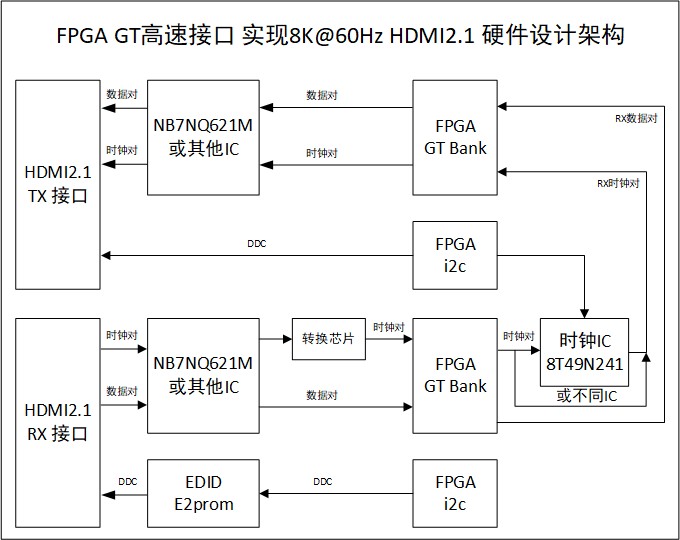

硬件设计架构

8K HDMI2.1 硬件设计架构如下:

本博主提供FPGA HDMI2.1视频收发的参考原理图,为PDF版本,里面包含了详细的电路设计,可节省你的硬件开发时间,如下:

本HDMI2.1性能参数

Xilinx官方提供的HDMI2.1物理层架构包括GT控制器和收发子系统,总体而言性能很不错,具体如下:

1、包括HDMI 源端 (TX) 子系统和 HDMI 宿端 (RX) 子系统;

2、基于AXI4-Stream的 1、2 或 4 像素视频接口(即一个像素时钟传输几个像素);

3、内嵌自动视频时序生成;

4、独立的 PHY 和控制层有助于用户高度灵活地在接收与发送之间共享GT高速接口;

5、3840x2160@120Hz或者7680×4320@60Hz;

6、视频编码支持 RGB 4:4:4, YUV4:4:4, YUV 4:2:2 和 YUV 4:2:0;

7、视频深色支持(每像素 24、30、36 及 48 位);

8、支持HDR;

9、音频支持达 32 信道(包含 HBR 音频);

10、支持HDCP(HDCP1.4, HDCP2.2/2.3);

11、支持信息帧;

12、数据显示通道 (DDC);

13、支持热插拔/EDID(电平极性可选);

8K视频输入源

我用到的8K视频输入源为腾讯极光盒子6Pro,极光盒子输出分辨率设置为3840x2160@60Hz;如下:

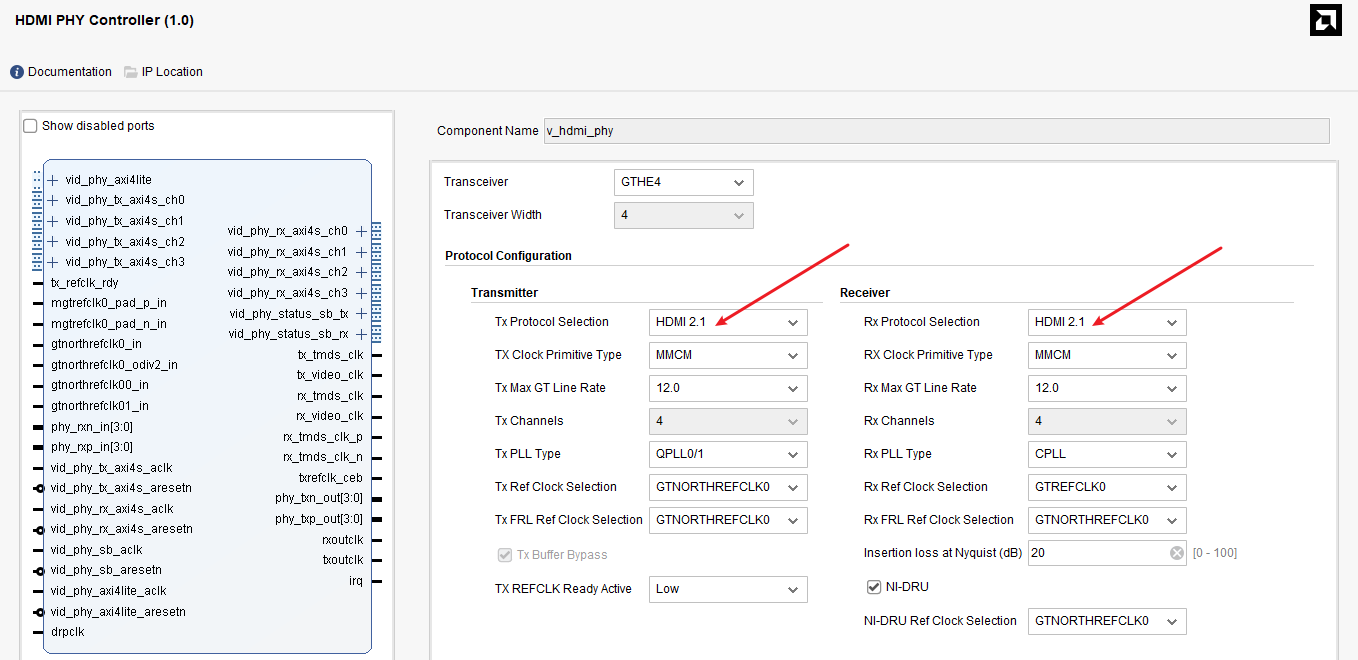

Video PHY Controller

Video PHY Controller可做HDMI2.1视频的接收和发送的解串与串化;对于HDMI2.1视频接收而言,可将原来高速串行信号解串为4路40bit的AXI4-Stream并行数据;然后调用Xilinx官方的HDMI 2.1 Receiver Subsystem IP核做8K超清视频的解码工作,同时解码出AXI4-Stream流的音频流和视频流;对于HDMI2.1视频发送而言,可将原4路40bit的AXI4-Stream并行数据串化为高速串行信号,输出的差分视频数据信号直接从FPGA的GT高速BANK输出,差分时钟信号直接从FPGA的LVDS高速BANK输出;以HDMI2.1收发模式为例,Video PHY Controller配置如下:

该IP需要在Vitis SDK中做进一步详细配置,详情参考Vitis SDK C语言软件代码;

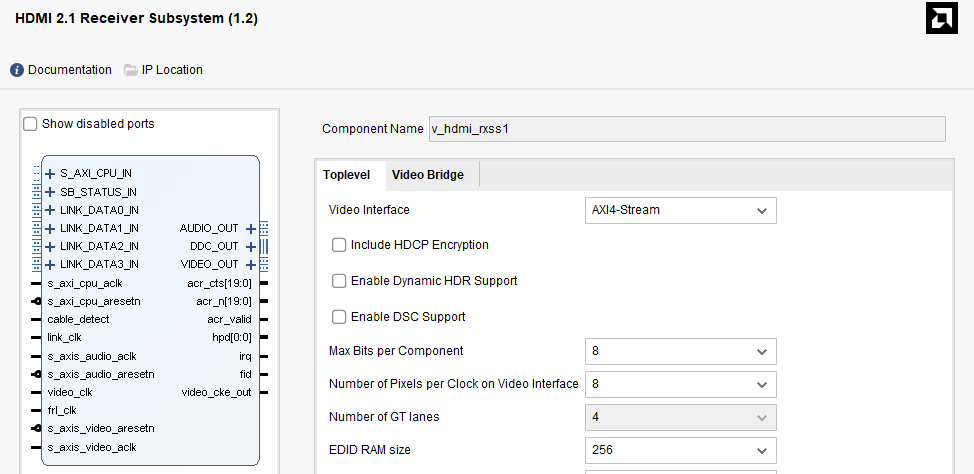

HDMI 2.1 Receiver Subsystem

Xilinx官方的HDMI 2.1 Receiver Subsystem IP核主要实现8K超清视频的解码工作,同时解码出AXI4-Stream流的音频流和视频流;HDMI 2.1 Receiver Subsystemr配置如下:

该IP需要在Vitis SDK中做进一步详细配置,详情参考Vitis SDK C语言软件代码;

值得注意的是,该IP使用的GT高速接口PLL类型一般选择CPLL;

8K HDMI 解码后的视频流走向

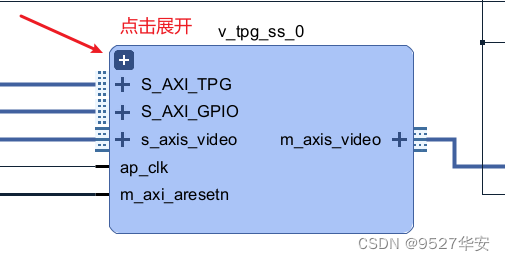

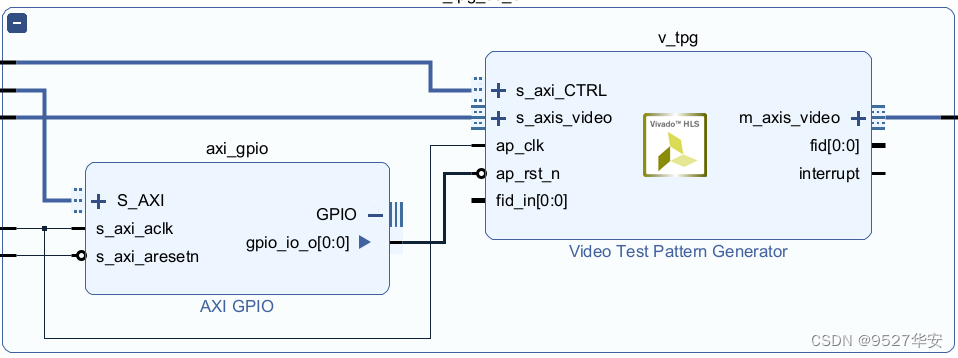

解码后的AXI4-Stream视频流进入Xilinx官方的TPG IP核,该IP在没有外部AXI4-Stream视频流进入时输出彩条视频,否则输出外部AXI4-Stream视频;同时解码后的AXI4-Stream音频流进入Xilinx官方的音频模块;TPG配合AXI-GPIO复位使用,IP组进行了封装,如下:

展开后以及TPG配置如下:

该IP需要在Vitis SDK中做进一步详细配置,详情参考Vitis SDK C语言软件代码;

8K HDMI 解码后的音频流走向

HDMI 2.1 Receiver Subsystem同时解码出AXI4-Stream格式的视频流和音频流,音频流输入Xilinx官方的音频生成模块(aud_pat_gen.v)和音频acr控制模块(hdmi_acr_ctrl.v),解码后的AXI4-Stream音频流进入这两个模块进行处理;两个模块进行了封装,如下:

展开后如下:

这两个模块需要在Vitis SDK中做进一步详细配置,详情参考Vitis SDK C语言软件代码;

HDMI 2.1 Transmitter Subsystem

调用Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核做8K音视频的编码工作,同时编码8K视频流和音频流并输出4路AXI4-Stream流和DDC控制信号;HDMI 2.1 Transmitter Subsystem配置如下:

该IP需要在Vitis SDK中做进一步详细配置,详情参考Vitis SDK C语言软件代码;

值得注意的是,该IP使用的GT高速接口PLL类型要根据TX端输入的参考时钟而定,具体要结合你的原理图设计考虑,并非固定配置,详情可咨询博主;

视频输出显示

视频输出显示需要支持3840x2160@120Hz或者7680×4320@60Hz,一般情况下,1千块以内的显示器是不支持的,我是用的是家里的电视机,品牌为小米电视大师 82” 至尊纪念版,你可以查询一下你的电视是否支持3840x2160@120Hz或者7680×4320@60Hz,此外,使用的HDMI线缆也必须支持3840x2160@120Hz或者7680×4320@60Hz,在保证显示线缆和显示器OK的情况下再做输出测试,可以解决很大部分调试排查时间;

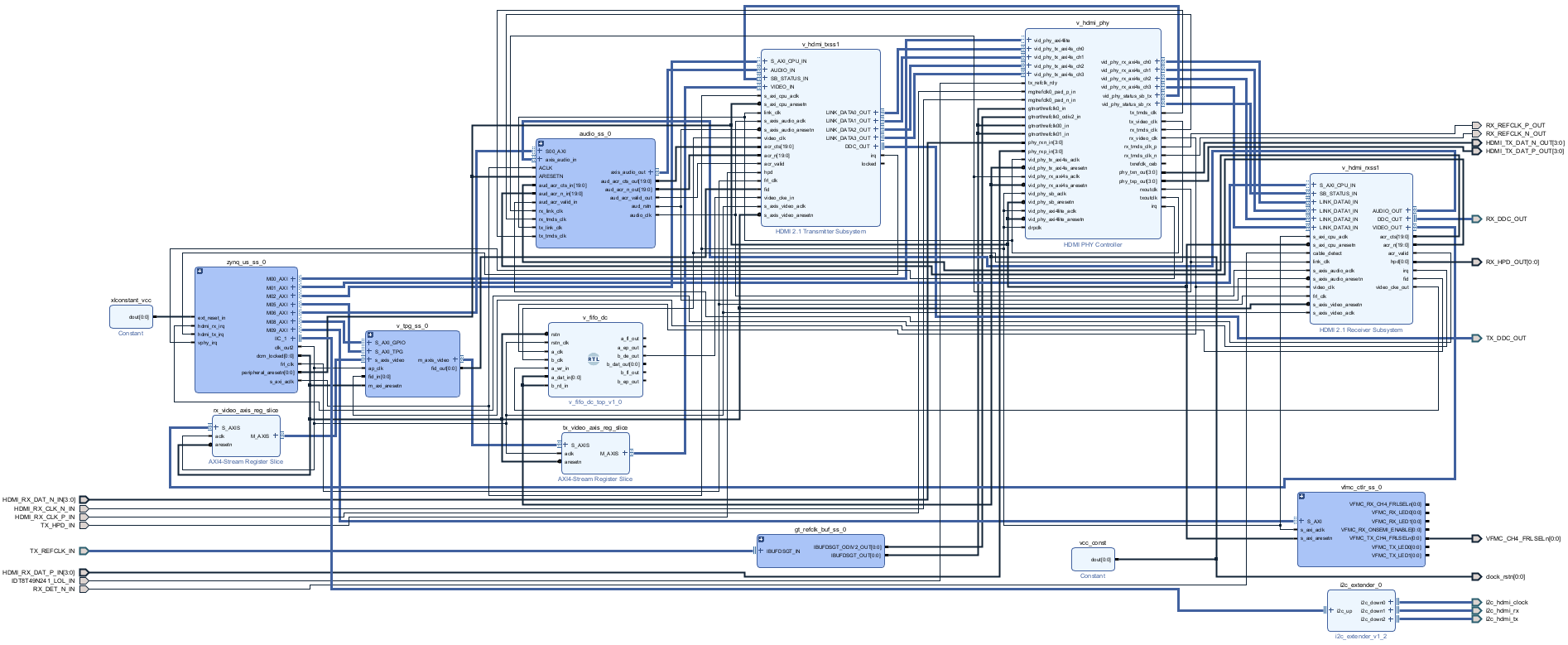

vivado逻辑工程源码架构

工程源码架构包括vivado Block Design逻辑设计和vitis SDK软件设计;

以工程源码1为例,Block Design逻辑设计架构截图如下:

以工程源码1为例,综合后的源码架构如下:

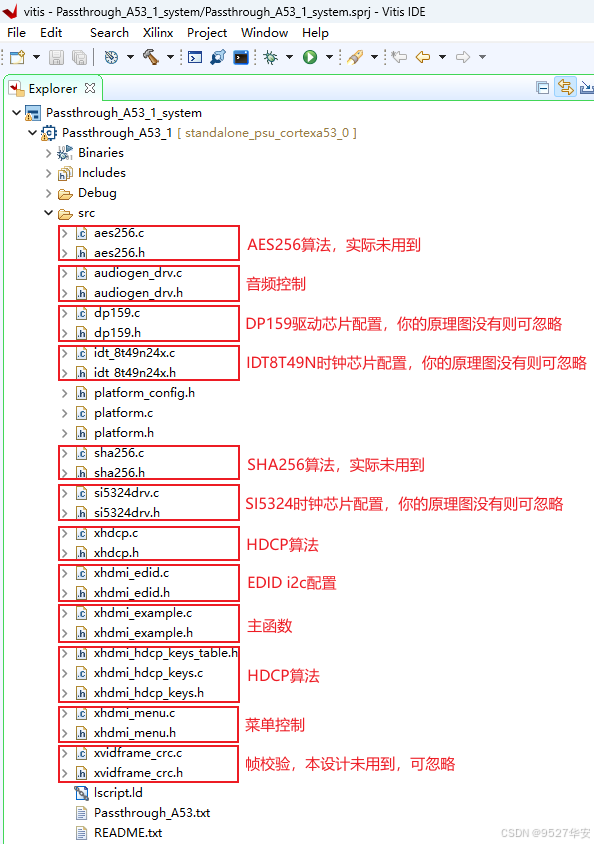

vitis软件工程源码架构

Vitis软件代码如下:

!!!注意

!!!注意

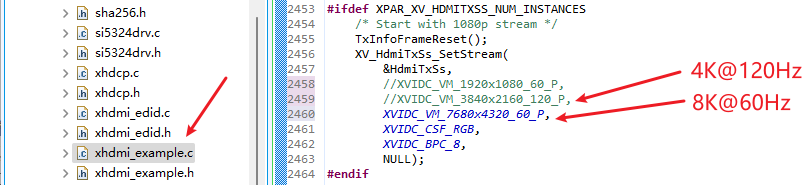

代码为了兼容不同板卡的外围IC,所以代码显得冗余复杂,图中标记的为必须使用到的代码,大多数保持默认即可;3840x2160@120Hz或者7680×4320@60Hz选择如下:

4、工程源码1详解–>ZU7EV,HDMI2.1输入转输出版本

开发板FPGA型号:Xilinx-Zynq UltraScale+ xczu7ev-ffvc1156-2-i;

FPGA开发环境:Vivado2023.1;

输入:机顶盒,HDMI2.1,分辨率3840x2160@120Hz;

输出:小米电视,HDMI2.1,分辨率3840x2160@120Hz;

HDMI2.1物理层方案:Xilinx官方的Video PHY Controller IP核,使用UltraScale-GTH高速接口;

HDMI2.1协议层解码方案:Xilinx官方的HDMI 2.1 Receiver Subsystem IP核;

HDMI2.1协议层编码方案:Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Xilinx系列FPGA实现HDMI2.1视频收发设计能力,以便能够移植和设计自己的项目;

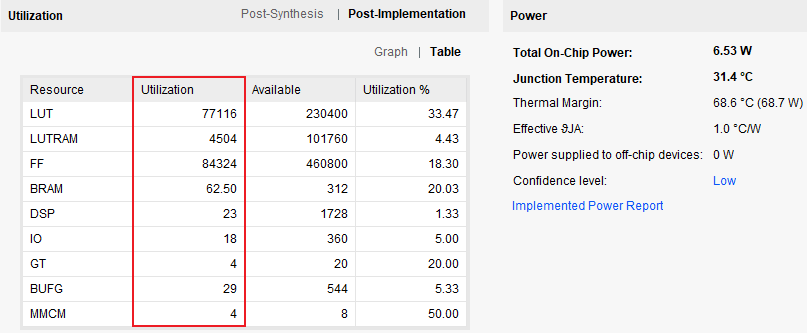

工程的资源消耗和功耗如下:

5、工程源码2详解–>ZU19EG,HDMI2.1输入转输出版本

开发板FPGA型号:Xilinx-Zynq UltraScale+ xczu19eg-ffvc1760-2-i;

FPGA开发环境:Vivado2023.1;

输入:机顶盒,HDMI2.1,分辨率3840x2160@120Hz;

输出:小米电视,HDMI2.1,分辨率3840x2160@120Hz;

HDMI2.1物理层方案:Xilinx官方的Video PHY Controller IP核,使用UltraScale-GTH高速接口;

HDMI2.1协议层解码方案:Xilinx官方的HDMI 2.1 Receiver Subsystem IP核;

HDMI2.1协议层编码方案:Xilinx官方的HDMI 2.1 Transmitter Subsystem IP核;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Xilinx系列FPGA实现HDMI2.1视频收发设计能力,以便能够移植和设计自己的项目;

工程的资源消耗和功耗如下:

6、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证并演示

准备工作

FPGA开发板,推荐使用本博的开发板;

8K输入设备;

8K HDMI显示器或者电视;

HDMI线;

以工程源码1为例,开发板连接如下:

HDMI2.1视频收发演示

手里暂时没有8K输入设备,用4K输入暂做演示,HDMI2.1可向下兼容HDMI2.0,收发演示如下:

HDMI2.1-8K-收发

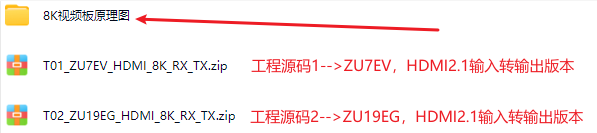

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Xilinx系列FPGA实现HDMI2.1视频收发,支持8K@60Hz分辨率,提供2套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目我已有的4K/8K视频处理解决方案我已有的FPGA图像处理方案 3、详细设计方案设计框图硬件设计架构本HDMI2.1性能参数8K视频输入源Video PHY ControllerHDMI 2.1 Receive…...

如何把网页文章转为pdf保存

fnF12调出右边网页端的控制台 在下面输入代码 1、转CSDN上的文章 (function(){ use strict;var articleBox $("div.article_content");articleBox.removeAttr("style");var head_str ""; var foot_str ""; var olde…...

开源可视化大屏go-view前后端安装

一、后端安装 下载代码 git clone https://gitee.com/MTrun/go-view-serve修改配置 cd go-view-serve/ # 修改application-dev.yml的数据库文件地址 vi ./src/main/resources/application-dev.ymlapplication-dev.yml spring:datasource:driver-class-name: org.sqlite.JDB…...

eventEmitter实现

没有做任何异常处理,简单模拟实现 事件对象的每一个事件都对应一个数组 /*__events {"事件1":[cb1,cb2],"事件2":[cb3,cb4],"事件3":[...],"事件4":[...],};*/class E{__events {};constructor(){}//注册监听回调on(type , callbac…...

自然语言处理|如何用少样本技术提升低资源语言处理?

一、引言 在全球化的背景下,自然语言处理(NLP)技术取得了显著进展,为人们的生活和工作提供了便利。然而,大多数 NLP 研究和应用集中在少数高资源语言上,如英语和中文。据统计,全球存在超过 700…...

系统安全——文件监控-FileMonitor

namespace FileSystemWatcherDemo {public partial class Form1 : Form{ public Form1(){InitializeComponent();UsingFileSystemWatcher();} /// <summary>/// 使用FileSystemWatcher方法/// </summary>void UsingFileSystemWatcher(){//6.2//FileSystemWa…...

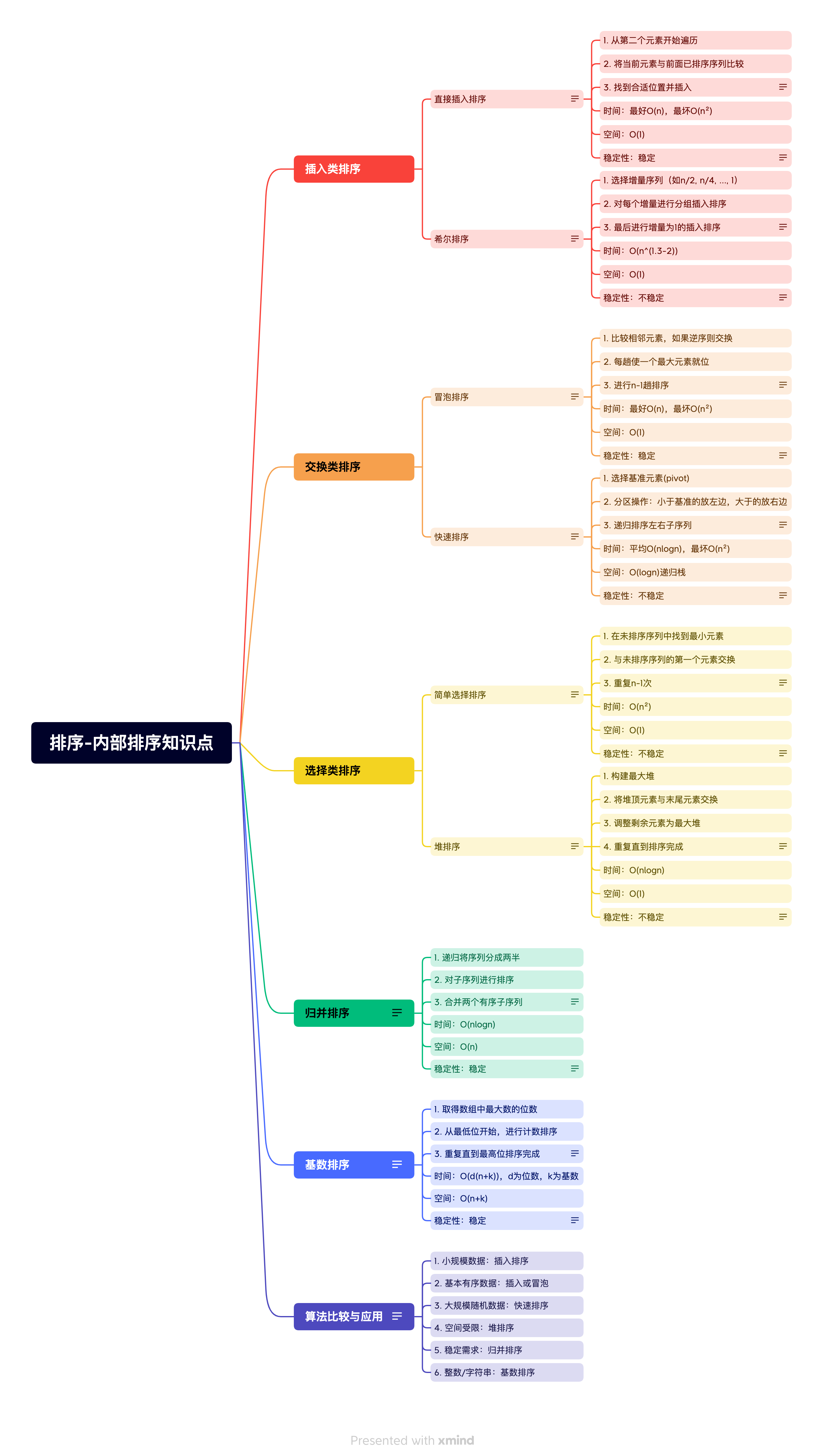

07-01-自考数据结构(20331)- 排序-内部排序知识点

内部排序算法是数据结构核心内容,主要包括插入类(直接插入、希尔)、交换类(冒泡、快速)、选择类(简单选择、堆)、归并和基数五大类排序方法。 知识拓扑 知识点介绍 直接插入排序 定义:将每个待排序元素插入到已排序序列的适当位置 算法步骤: 从第二个元素开始遍历…...

)

Unity:平滑输入(Input.GetAxis)

目录 1.为什么需要Input.GetAxis? 2. Input.GetAxis的基本功能 3. Input.GetAxis的工作原理 4. 常用参数和设置 5. 代码示例:用GetAxis控制角色移动 6. 与Input.GetAxisRaw的区别 7.如何优化GetAxis? 1.为什么需要Input.GetAxis&…...

【AI学习】MCP的简单快速理解

最近,AI界最火热的恐怕就是MCP了。作为一个新的知识点,学习的开始,先摘录一些信息,从发展历程、通俗介绍到具体案例,这样可以快速理解MCP。 MCP发展历程 来自i陆三金 Anthropic 开发者关系负责人 Alex Albert&#…...

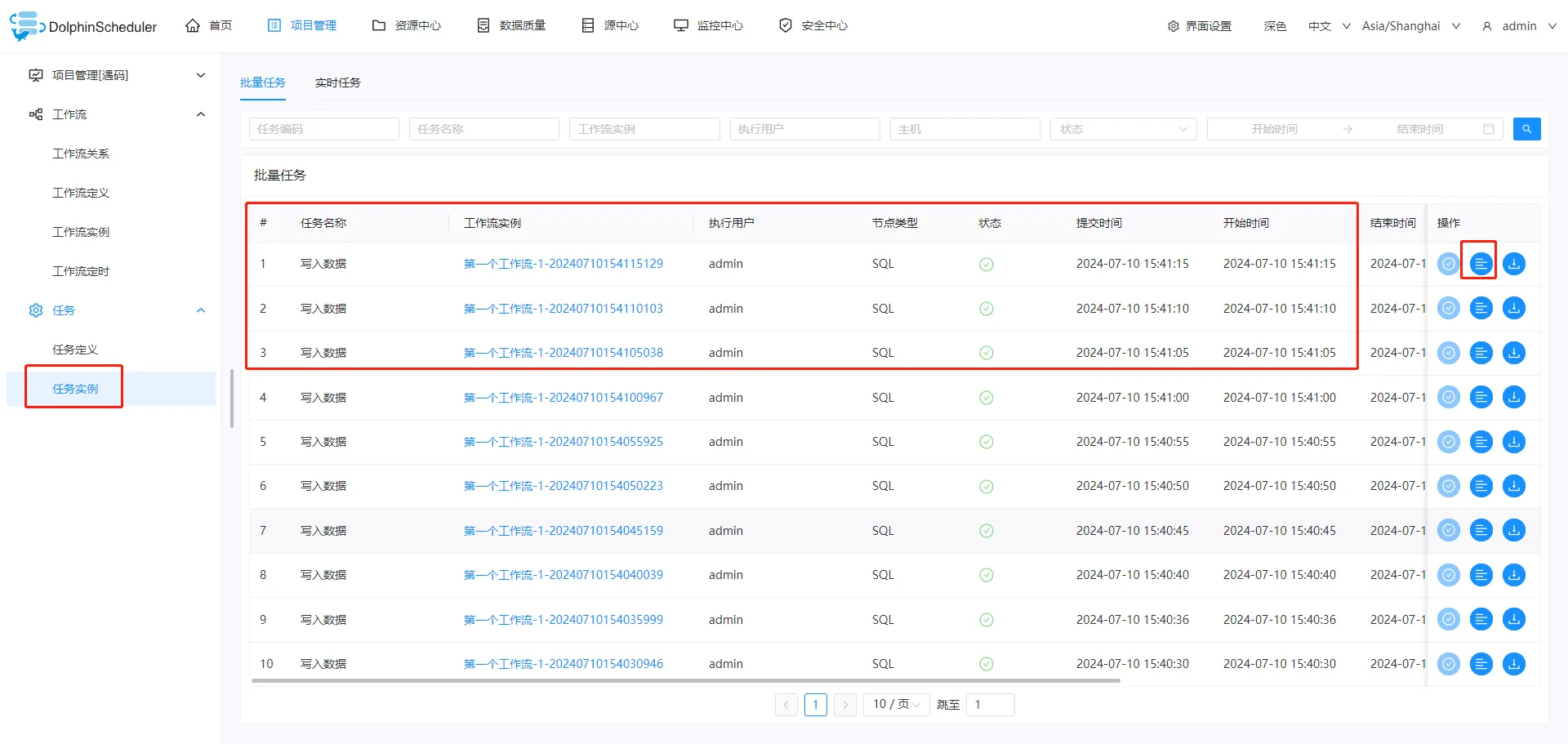

单机快速部署开源、免费的分布式任务调度系统——DolphinScheduler

看了DolphinScheduler的介绍,不知道有没有引起你的兴趣,有没有想要上手体验一番呢。本文则主要为大家介绍DolphinScheduler的单机部署方式,方便大家快速体验。 环境准备 需要Java环境,这是一个老生常谈的问题,关于Ja…...

Vue3命名规范指南

在 Vue 3 中,遵循一致的命名规范可以提高代码的可读性和维护性。以下是常见的命名规范和实践建议: 1. 组件命名 PascalCase(大驼峰式) 单文件组件(.vue 文件)和组件引用时推荐使用 PascalCase,便…...

【大模型系列篇】大模型基建工程:基于 FastAPI 自动构建 SSE MCP 服务器

今天我们将使用FastAPI来构建 MCP 服务器,Anthropic 推出的这个MCP 协议,目的是让 AI 代理和你的应用程序之间的对话变得更顺畅、更清晰。FastAPI 基于 Starlette 和 Uvicorn,采用异步编程模型,可轻松处理高并发请求,尤…...

springcloud configClient获取configServer信息失败导致启动configClient注入失败报错解决

目录 一、问题现象 二、解决方案 三、运行结果 四、代码地址 一、问题现象 springcloud configClient获取configServer信息失败导致启动configClient注入失败 报错堆栈信息 org.springframework.beans.factory.BeanCreationException: Error creating bean with name scop…...

HarmonyOS-ArkUI Rcp模块类关系梳理

前言 本文重点解决的是,按照官网学习路径学习Tcp模块内容时,越看越混乱的问题。仿照官网案例,书写代码时,产生的各种疑惑。比如,类与类之间的关系,各种配置信息究竟有多少,为什么越写越混乱。那…...

26考研——线性表_ 线性表的链式表示_双循环链表(2)

408答疑 文章目录 三、 线性表的链式表示双循环链表单链表与双链表的比较单链表的特点双链表的特点 双链表上基本操作的实现双链表的插入操作双链表的删除操作 双链表的代码实操定义结点创建一个结点带头结点的双链表初始化创建双链表打印双链表查找结点插入结点在指定节点后插…...

大模型如何引爆餐饮与电商行业变革

大模型如何引爆餐饮与电商行业变革? 一、时代背景:大模型重构产业逻辑的底层动力 1. 技术跃迁催生效率革命 2025年,大模型技术迎来"普惠临界点"。李开复在中关村论坛指出,大模型推理成本每年降低10倍,使得…...

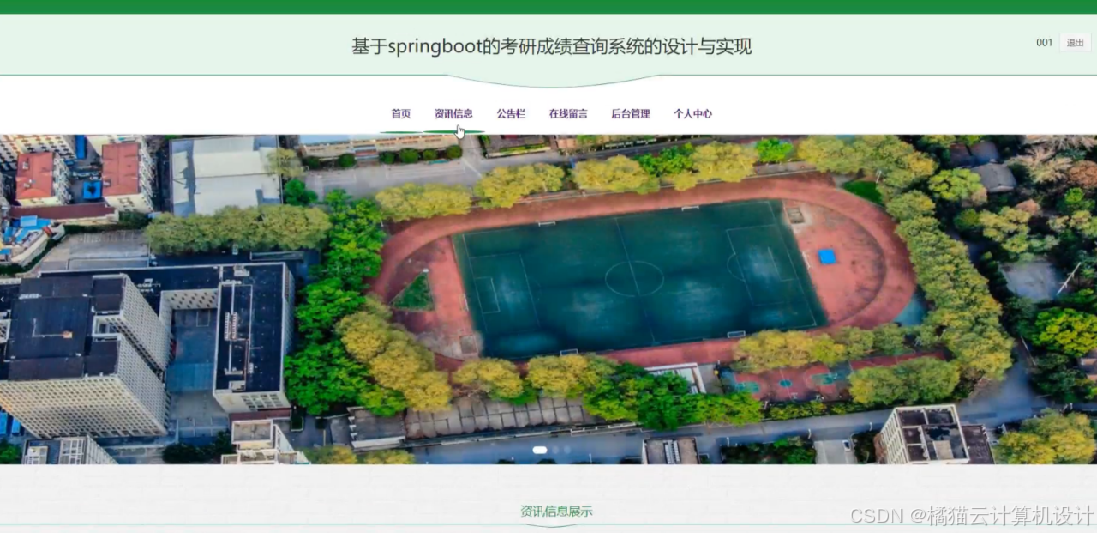

基于springboot的考研成绩查询系统(源码+lw+部署文档+讲解),源码可白嫖!

摘要 这些年随着Internet的迅速发展,我们国家和世界都已经进入了互联网大数据时代,计算机网络已经成为了整个社会以及经济发展的巨大动能,考研成绩查询管理事务现在已经成为社会关注的重要内容,因此运用互联网技术来提高考研成绩…...

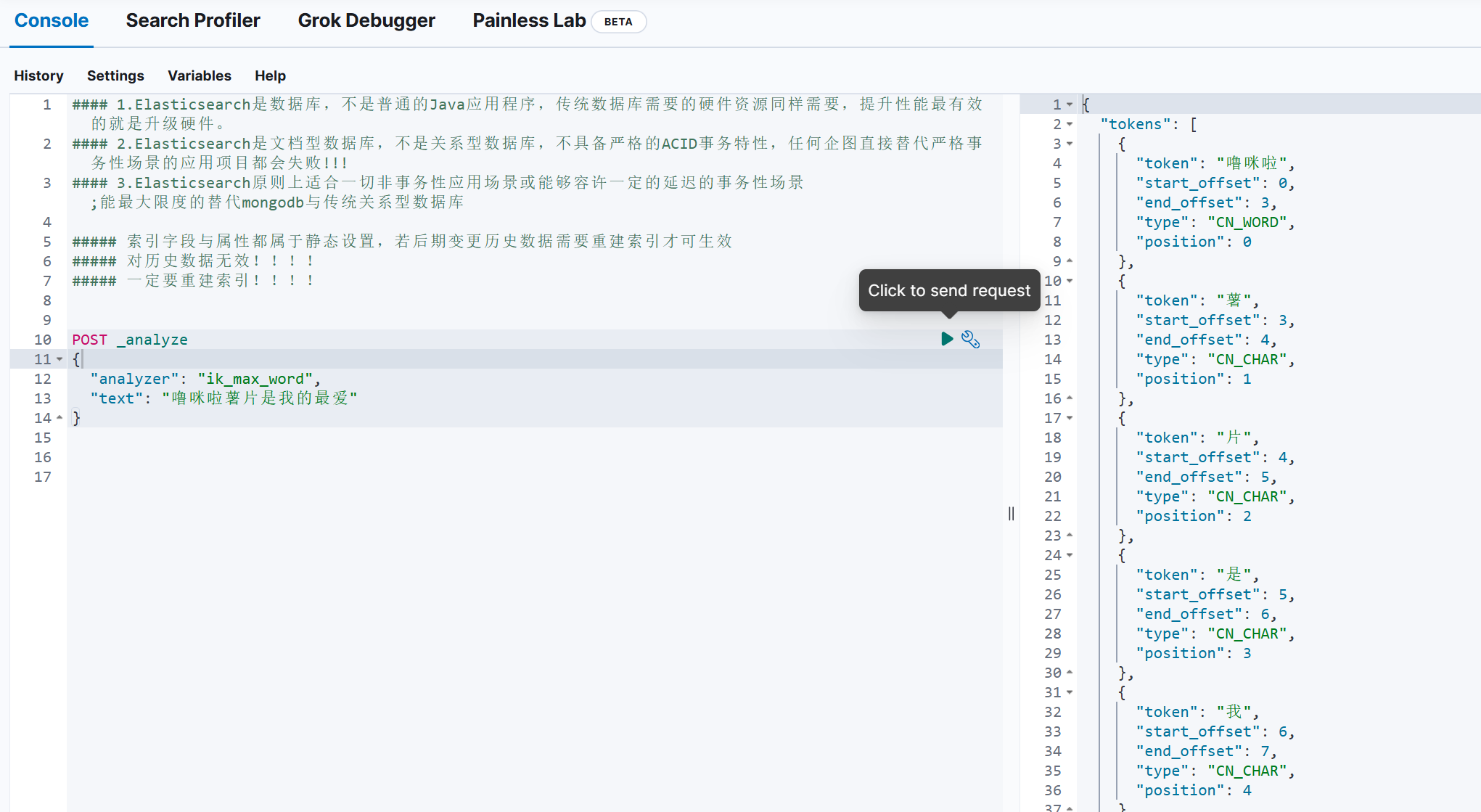

es自定义ik分词器中文词库实现热更新

基于web地址的方式实现ik分词热更新。 操作系统:win 11 es version:8.6.2 ik version:8.6.2 1、创建web服务,并提供ik查询词库接口 编写分词http url代码,返回自定义分词内容分词词库数据来自业务需求,存…...

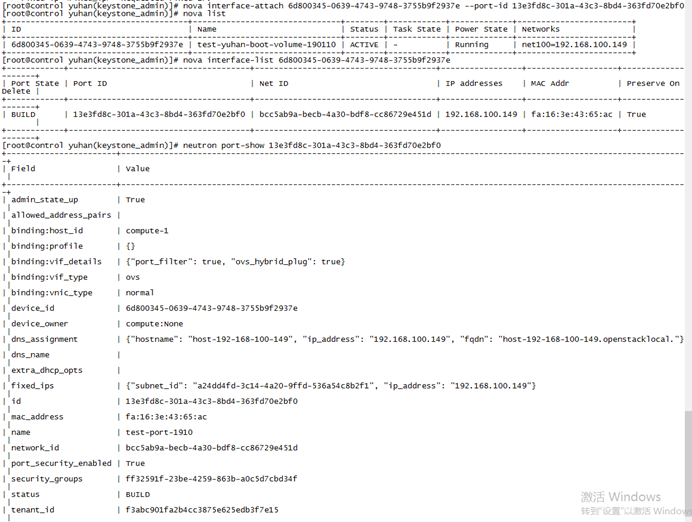

OpenStack 卷虚拟机跨租户迁移方案

目标:迁移租户A的卷虚机到租户B 场景:使用卷虚拟机,租户a和b使用相同网络 租户A的操作: 1.记录虚拟机的ip地址,Mac信息, nova interface-list neutron port-show 2.对虚拟机进行关机操作,将…...

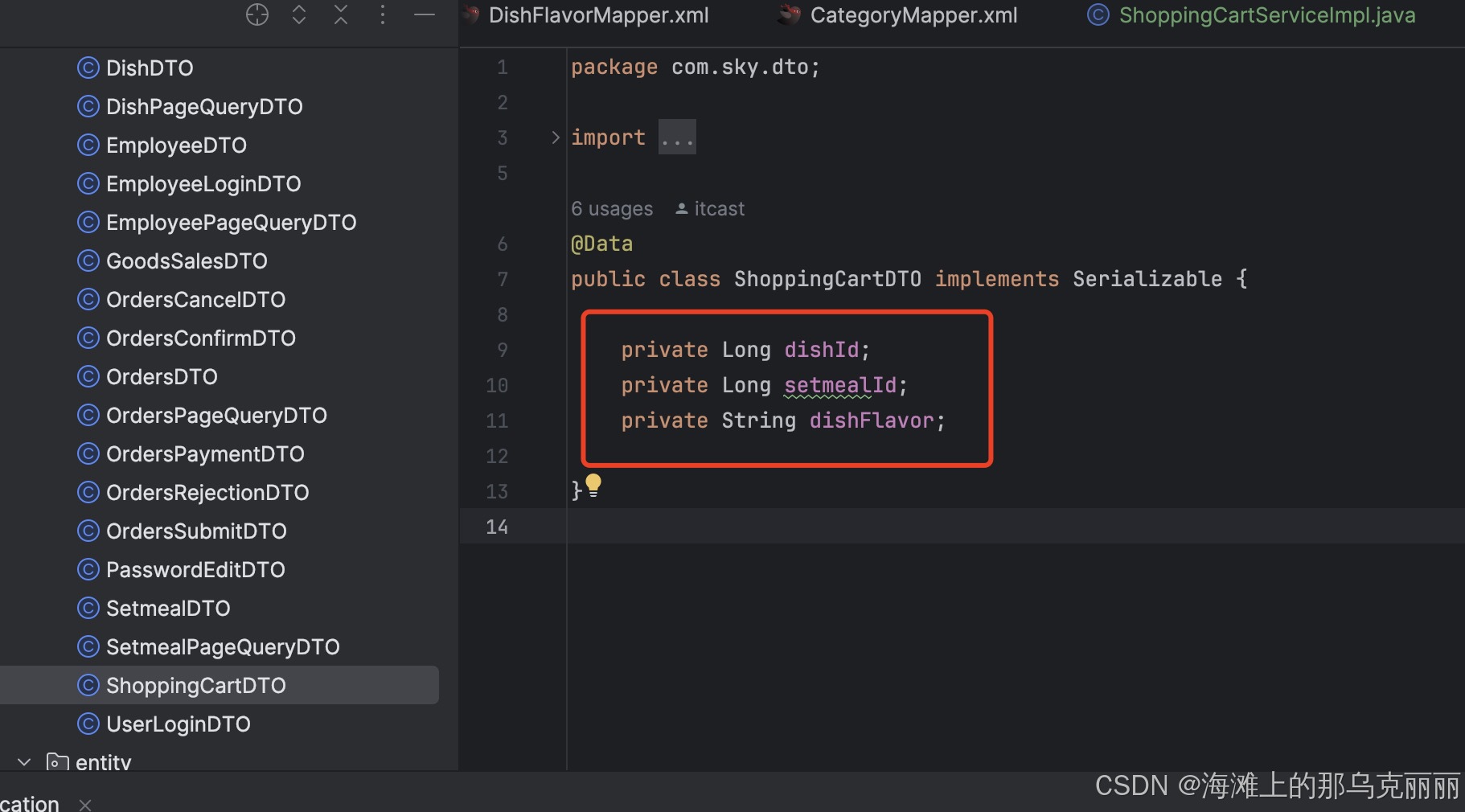

添加购物车功能

业务需求: 用户提交三个字段,服务端根据提交的字段判断是菜品还是套餐,根据菜品或者套餐添加购物车表中。 代码实现 RestController Slf4j RequestMapping("/user/shoppingCart") public class ShoppingCartController {Autowired…...

Logo语言的系统监控

Logo语言的系统监控 引言 在信息技术飞速发展的时代,系统监控成为了确保计算机系统和网络平稳运行的重要手段。系统监控不仅可以实时跟踪系统的性能、资源使用情况和安全风险等,还能够在出现问题时及时发出警报,从而避免潜在的故障和损失。…...

Scheme语言的算法

Scheme语言的算法探索 引言 Scheme是一种以表达式为基础的编程语言,属于Lisp家族,因其简洁、灵活的语法而受到广泛关注。Scheme不仅适合教学,还被用于实际应用开发和研究。本文将深入探讨Scheme语言的算法,包括其基本特性、常用…...

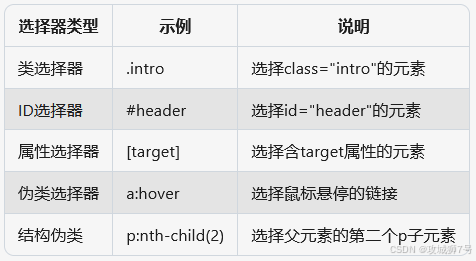

Python爬虫第2节-网页基础和爬虫基本原理

目录 一、网页基础 1.1 网页的组成 1.2 网页的结构 1.3 节点树及节点间的关系 1.4 选择器 二、爬虫的基本原理 2.1 爬虫概述 2.2 能抓怎样的数据 2.3 JavaScript 渲染页面 一、网页基础 使用浏览器访问网站时,我们会看到各式各样的页面。你是否思考过&…...

阿里巴巴langengine二次开发大模型平台

阿里巴巴LangEngine开源了!支撑亿级网关规模的高可用Java原生AI应用开发框架 - Leepy - 博客园 阿里国际AI应用搭建平台建设之路(上) - 框架篇 基于java二次开发 目前Spring ai、spring ai alibaba 都是java版本的二次基础能力 重要的是前端工作流 如何与 服务端的…...

深度学习中的 Batch 机制:从理论到实践的全方位解析

一、Batch 的起源与核心概念 1.1 批量的中文译名解析 Batch 在深度学习领域标准翻译为"批量"或"批次",指代一次性输入神经网络进行处理的样本集合。这一概念源自统计学中的批量处理思想,在计算机视觉先驱者Yann LeCun于1989年提出…...

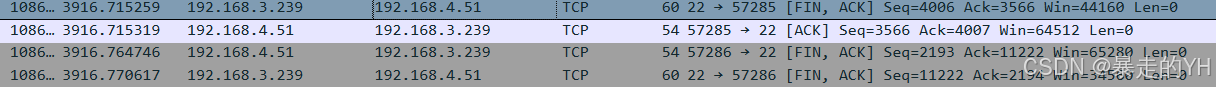

【网络协议】三次握手与四次挥手

例如我们使用MobaXterm登录服务器的时候,基于TCP协议的之间是如何进行通信的? 使用工具:wireshark抓取传输层TCP协议 三次握手 mobaxterm:登录服务器触发三次握手 wireshark过滤分析 ip.addr 192.168.3.239 192.168.3.239登录…...

请求被中止: 未能创建 SSL/TLS 安全通道。

需要安装vs2019社区办,下载VisualStudioSetup.exe后,报无法从"https://aka,ms/vs/16/release/channel"下载通道清单错误,接着打开%temp%目录下的最新日志,发现日志里报: [27d4:000f][2025-04-04T21:15:43] …...

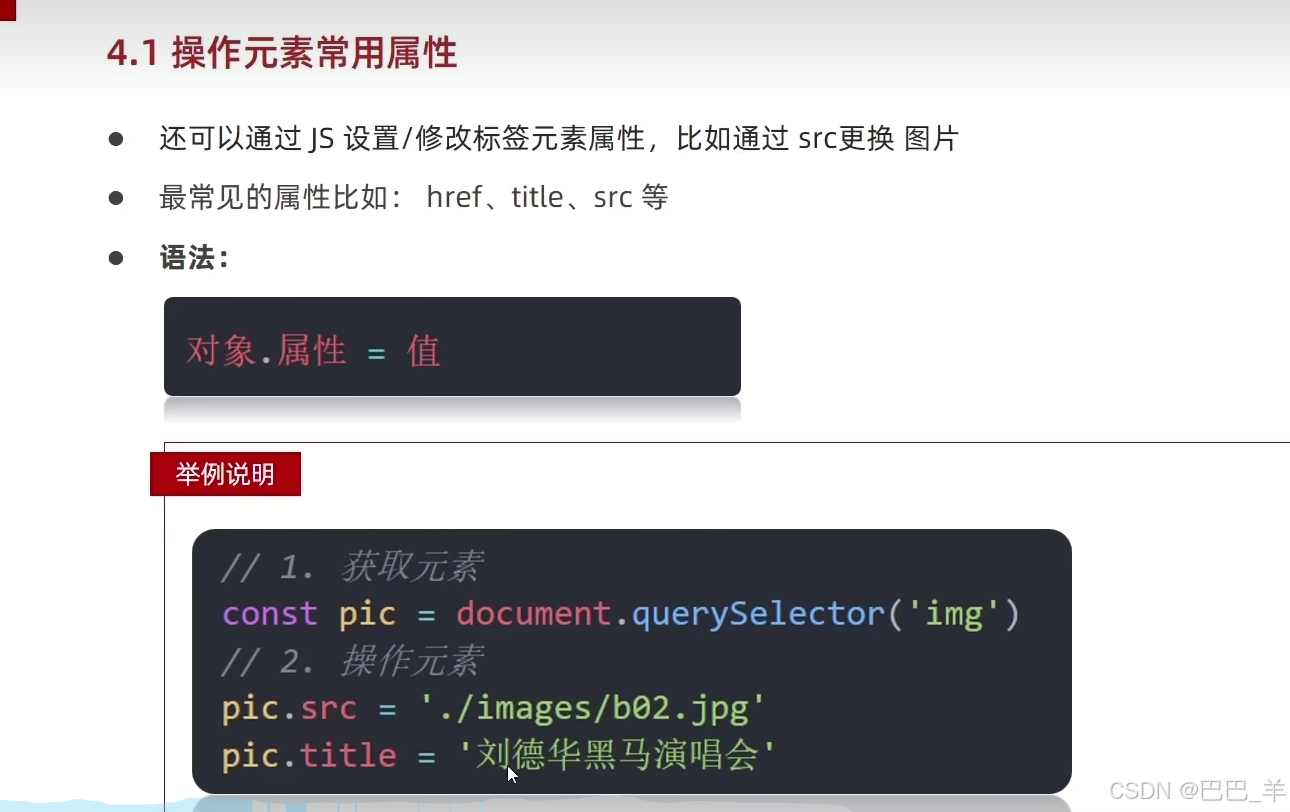

JS API

const变量优先 即对象、数组等引用类型数据可以用const声明 API作用和分类 DOM (ducument object model) 操作网页内容即HTML标签的 树状模型 HTML中标签 JS中对象 最大对象 document 其次大 html 以此类推 获取DOM对象 CSS 中 使用选择器 JS 中 选多个 时代的眼泪 修…...

“一路有你”公益行携手《东方星动》走进湖南岳阳岑川镇中心小学

2025年4月2日,“一路有你”公益行携手《东方星动》走进湖南岳阳岑川镇,一场充满爱与温暖的捐赠仪式在岑川镇中心小学隆重举行。这是一场跨越千里的爱心捐赠,也是一场别开生面的国防教育,更是一场赋能提质的文化盛宴。 岑川镇地处湘…...

vue组件开发:什么是VUE组件?

什么是VUE组件 在我们实际开发过程中你也许会发现有很多代码是重复的,它们可能是一个按钮、一个表单、一个列表等等,其中最为显著的应该是列表。 以CSDN的首页为例: 上述截图中的文章列表可能会在多处出现,比如此截图是精选博客…...