【FPGA基础学习】状态机思想实现流水灯

目录

- 一、用状态机实现LED流水灯

- 1.状态机思想简介

- 1. 1基本概念

- 1.2.核心要素

- 1.3分类与模型

- 2.LED流水灯

- 二、CPLD与FPGA

- 1.技术区别

- 2.应用场景

- 3.设计选择建议

- 三、HDLbits组合逻辑题目

一、用状态机实现LED流水灯

1.状态机思想简介

1. 1基本概念

状态机(Finite State Machine, FSM)是一种用于描述系统行为及其状态转换的数学模型。它将系统抽象为有限个状态,并通过事件触发实现状态间的迁移,同时可能伴随特定的动作。其核心思想是“基于状态的逻辑控制”,适用于具有明确阶段性和条件依赖性的系统

1.2.核心要素

现态(Current State):系统当前所处的状态。

事件(Event):触发状态迁移的条件(如用户输入、传感器信号等)

动作(Action):状态迁移时执行的操作(如开启设备、发送数据等)

次态(Next State):事件触发后系统将进入的新状态

1.3分类与模型

Moore型:输出仅由当前状态决定(如交通信号灯的红绿灯切换)

Mealy型:输出由当前状态和输入共同决定(如网络协议中的应答机制)

确定型(DFA):每个状态对同一事件有唯一迁移路径

非确定型(NFA):同一事件可能触发多个迁移路径,需额外逻辑处理

2.LED流水灯

核心代码如下:

module led_flow(input clk, // 50MHz时钟input rst_n, // 复位信号(低有效)output reg [7:0] led

);// 状态定义(8个状态)localparam [2:0] S0=0, S1=1, S2=2, S3=3, S4=4, S5=5, S6=6, S7=7;reg [2:0] state;reg [24:0] cnt;wire en = (cnt == 25'd24_999_999); // 分频使能// 分频计数器always @(posedge clk or negedge rst_n) beginif (!rst_n) cnt <= 0;else if (en) cnt <= 0;else cnt <= cnt + 1;end// 状态机主逻辑always @(posedge clk or negedge rst_n) beginif (!rst_n) beginstate <= S0;led <= 8'b00000001; // 初始状态S0点亮LED0endelse if (en) begincase(state)S0: begin led <= 8'b00000010; state <= S1; end //S0→S1(第2个LED亮)S1: begin led <= 8'b00000100; state <= S2; end //S1→S2(第3个LED亮)S2: begin led <= 8'b00001000; state <= S3; end //S2→S3(第4个LED亮)S3: begin led <= 8'b00010000; state <= S4; end //S3→S4(第5个LED亮)S4: begin led <= 8'b00100000; state <= S5; end //S4→S5(第6个LED亮)S5: begin led <= 8'b01000000; state <= S6; end //S5→S6(第7个LED亮)S6: begin led <= 8'b10000000; state <= S7; end //S6→S7(第8个LED亮)S7: begin led <= 8'b00000001; state <= S0; end //S7→S0(第1个LED亮,循环)default: state <= S0; // 默认回到初始状态endcaseendend

endmodule

仿真文件编写:

`timescale 1ns / 1ps

module led_flow_tb;// 输入信号reg clk; // 50MHz时钟reg rst_n; // 复位信号(低有效)// 输出信号wire [7:0] led; // LED输出// 实例化被测模块led_flow uut (.clk(clk),.rst_n(rst_n),.led(led));// 1. 生成50MHz时钟initial beginclk = 0;forever #10 clk = ~clk; // 周期20ns(50MHz)end// 2. 控制复位信号initial beginrst_n = 0; // 初始复位有效#100; // 保持100ns复位rst_n = 1; // 释放复位#2000000000; // 仿真运行2秒(覆盖多个状态循环)$finish; // 结束仿真end// 3. 监视信号变化initial begin$monitor("Time=%tns | State=%d | LED=%b", $time, uut.state, led);end

endmodule

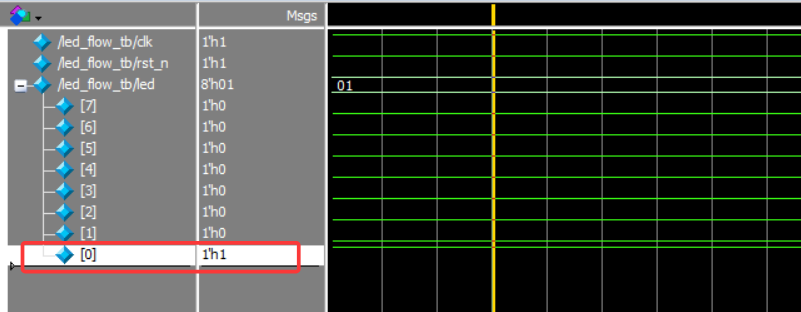

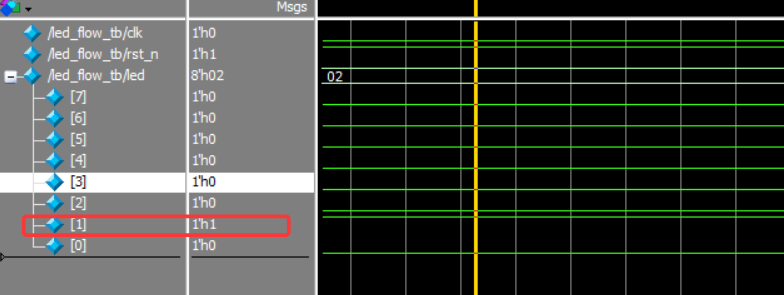

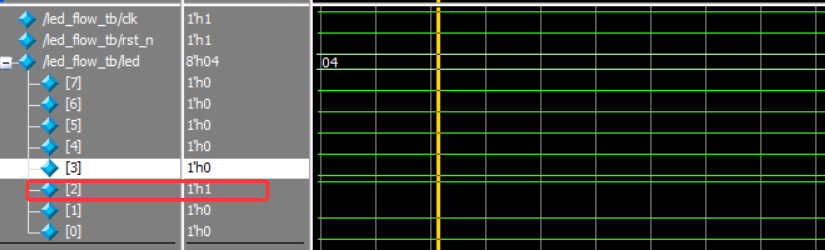

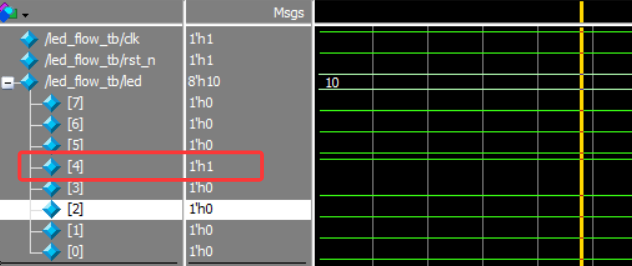

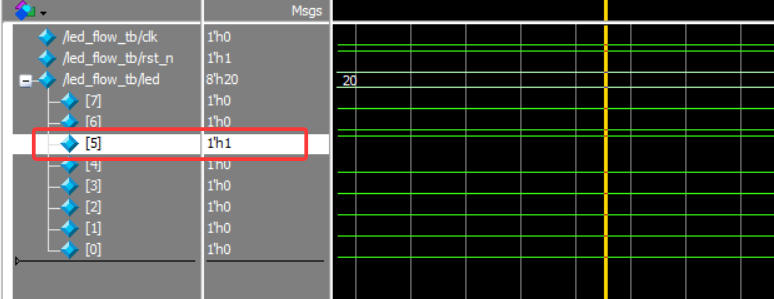

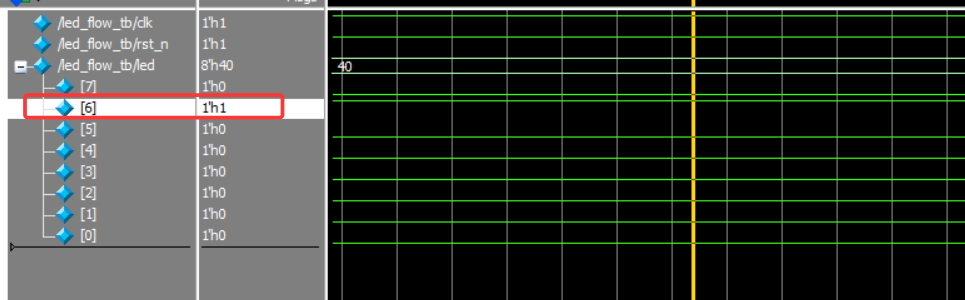

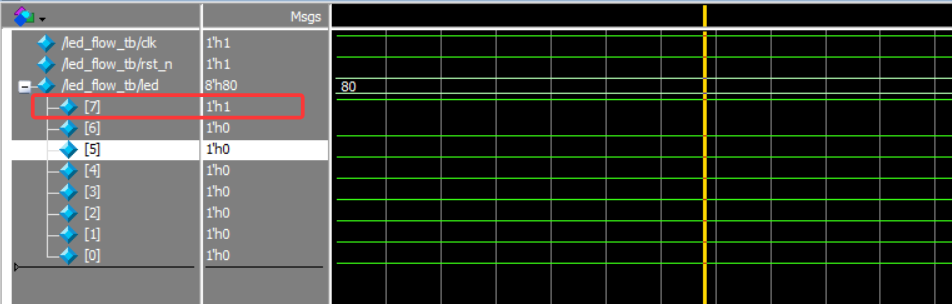

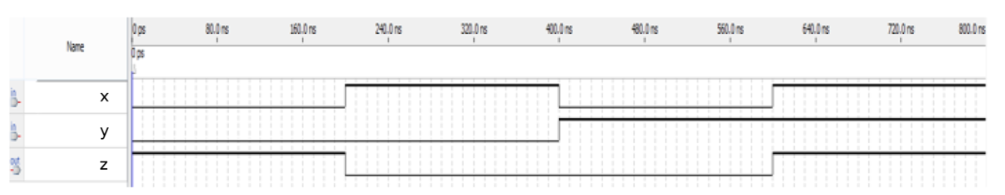

仿真:

因为我流水灯的周期太长了,没有办法显示全,所以调整分频

wire en = (cnt == 25'd4_999_999); // 分频使能

可以看到仿真结果符合预期

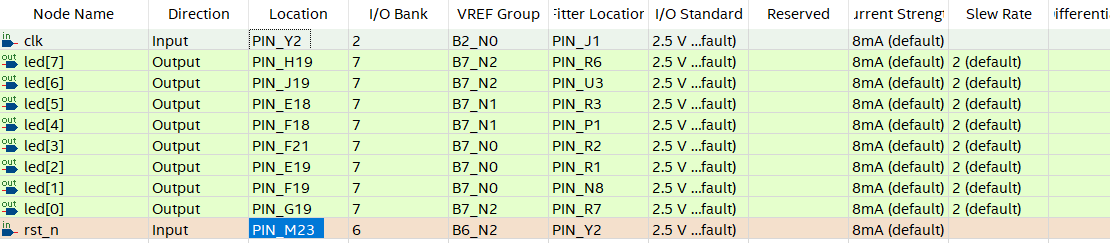

引脚绑定:

实现效果:

led 流水灯状态机思想

二、CPLD与FPGA

1.技术区别

| 特性 | CPLD | FPGA |

|---|---|---|

| 架构 | 基于乘积项(Product Term)结构,逻辑块较大 | 基于查找表(LUT)结构,逻辑单元粒度小 |

| 资源规模 | 较小(通常<10万门) | 较大(可达数百万门) |

| 时序特性 | 延时均匀,可预测性强 | 延时依赖布局布线,需时序约束优化**7 |

| 编程方式 | 非易失性(EEPROM/Flash),无需外部配置 | 易失性(SRAM),需外部存储器加载配置 |

| 功耗 | 静态功耗低,适合低功耗场景 | 动态功耗高,适合高性能计算 |

| 重构灵活性 | 配置固定,不支持动态重构 | 支持实时动态重构 |

2.应用场景

-

CPLD:

- 控制密集型系统:如接口转换(UART转SPI)、简单状态机、工业控制逻辑

- 低功耗场景:电池供电设备,需长期稳定运行

- 快速原型验证:中小规模逻辑的快速实现

-

FPGA:

-

数据密集型系统:图像处理、高速通信(如PCIe)、数字信号处理(DSP)

-

复杂算法加速:深度学习推理、加密解密算法

-

可重构计算:航天电子设备需在轨更新功能

-

3.设计选择建议

-

若需简单逻辑控制且对成本敏感,选CPLD

-

若需高性能并行处理或动态重构,选FPGA

三、HDLbits组合逻辑题目

HDLBits(点击进入练习) 是一个专注于 Verilog硬件描述语言(HDL)学习和实践 的在线平台,由多伦多大学开发,旨在通过小型电路设计习题帮助用户:夯实Verilog基础、理解数字电路设计思想(例如状态机设计、时序约束优化等关键概念)、衔接实际项目(平台题目与FPGA开发中的常见模块,如FIFO、接口控制器,高度相关)

题目1:简单电路B

module top_module ( input x, input y, output z );assign z = ~(x ^ y);

endmodule

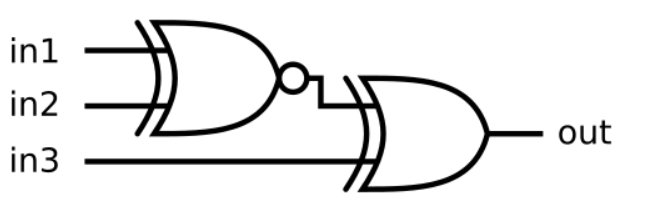

题目2:Two gates

module top_module (input in1,input in2,input in3,output out);assign out=(~(in1^in2))^in3;

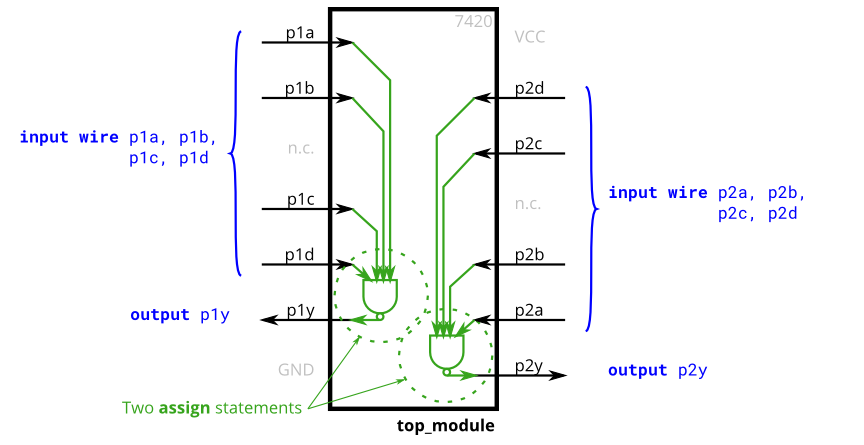

endmodule题目3:7420chip

module top_module ( input p1a, p1b, p1c, p1d,output p1y,input p2a, p2b, p2c, p2d,output p2y );assign p1y=~(p1a&p1b&p1c&p1d);assign p2y=~(p2a&p2b&p2c&p2d);

endmodule

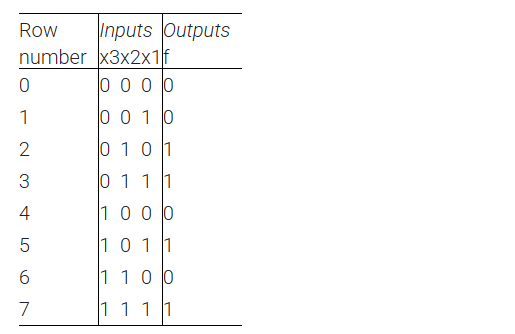

题目4:真值表

module top_module( input x3,input x2,input x1, // three inputsoutput f // one output

);wire and1 = (~x3 & x2 & ~x1);wire and2 = (~x3 & x2 & x1);wire and3 = (x3 & ~x2 & x1);wire and4 = (x3 & x2 & x1);assign f = and1 | and2 | and3 | and4;

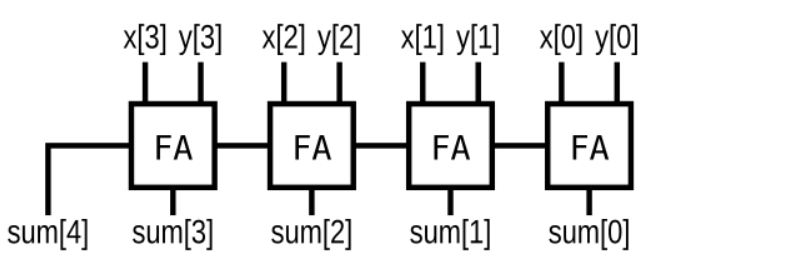

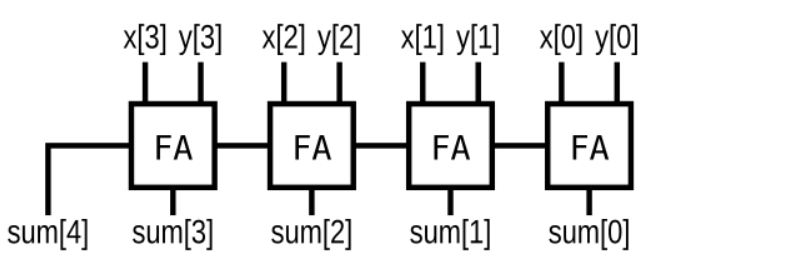

endmodule题目5:加法器

module top_module (input [3:0] x, input [3:0] y, output [4:0] sum);assign sum = x + y;

endmodule参考链接:

百度词条CPLD与FPGA

CPLD与FPGA的用途及其区别

百度百科状态机

聊一聊状态机

相关文章:

【FPGA基础学习】状态机思想实现流水灯

目录 一、用状态机实现LED流水灯1.状态机思想简介1. 1基本概念1.2.核心要素1.3分类与模型 2.LED流水灯 二、CPLD与FPGA1.技术区别2.应用场景3.设计选择建议 三、HDLbits组合逻辑题目 一、用状态机实现LED流水灯 1.状态机思想简介 1. 1基本概念 状态机(Finite …...

HTML表单属性2

HTML5针对<input>添加了许多属性: autofocus属性 页面加载时自动聚焦到输入字段 <form action"action_page.php" >名字: <input type"text" name"fnam" autofocus><br>姓氏:<in…...

图片尺寸修改软件下载

【图片尺寸调整工具v1.0:高效便捷的图像处理助手】 图片尺寸调整工具v1.0是一款专为简化图像处理流程设计的轻量级软件,兼顾高效批量处理与个性化单图调整需求。该工具以"零学习成本"为核心设计理念,通过简洁直观的交互界面&#…...

202521 | 远程调用 | 注册中心

远程调用 1. 核心方案全景图 #mermaid-svg-f3oyP1p2P8a2lAuW {font-family:"trebuchet ms",verdana,arial,sans-serif;font-size:16px;fill:#333;}#mermaid-svg-f3oyP1p2P8a2lAuW .error-icon{fill:#552222;}#mermaid-svg-f3oyP1p2P8a2lAuW .error-text{fill:#55222…...

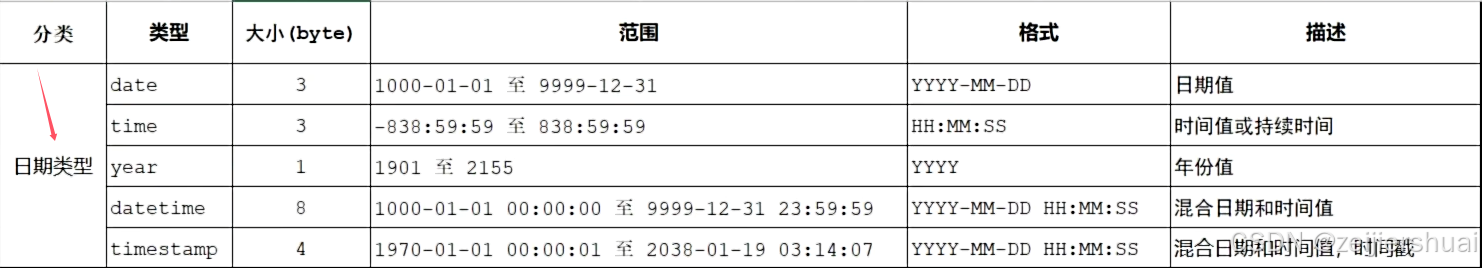

MySQL-SQL-DDL语句、表结构创建语句语法、表约束、表数据类型,表结构-查询SQL、修改SQL、删除SQL

一.SQL SQL:一门操作关系型数据库的编程语言,定义操作所有关系型数据库的统一标准 二. DDL-数据库 1. 查询所有数据库 命令:show databases; 2. 查询当前数据库 命令:select database(); 3. 创建数据库 命令:create da…...

网络钓鱼攻击的威胁和执法部门的作用(第一部分)

在当今的数字世界中,网络犯罪分子不断开发新技术来利用个人、企业和政府机构。 最普遍和最具破坏性的网络犯罪形式之一是网络钓鱼——一种社会工程手段,用于欺骗人们提供敏感信息,例如登录凭据、财务数据和个人详细信息。 随着网络钓鱼攻击…...

鸿蒙版(ArkTs) 贪吃蛇,包含无敌模式 最高分 暂停和继续功能

鸿蒙版(ArkTs) 贪吃蛇,包含无敌模式 最高分 暂停和继续功能; 效果图如下: 代码如下: // 所有import语句必须放在文件开头 import router from ohos.router; import promptAction from ohos.promptAction; // Add this import at the top wit…...

适配器模式)

设计模式简述(十三)适配器模式

适配器模式 描述基本使用使用关于适配器关联不兼容类的方式如果原有抽象层是抽象类若原有抽象是接口使用 描述 适配器模式常用于系统已经上限稳定运行,但现有需求需要将两个不匹配的类放到一起工作时使用。 也就是说这是一个迭代阶段使用的模式。 这种模式&#x…...

4月6日随笔

一觉起来十点多 其实六点和九点分别醒过一次。 起来之后点了个侍卫草推荐的猪排饭,真的巨好吃,猪排很脆,溏心蛋也很香 但是因为酒店十二点半要退房,就匆匆吃完了猪排和一半米饭就走了 今天下午在科技楼写了一会作业,…...

Spring Boot 3.4.3 和 Spring Security 6.4.2 实现基于内存和 MySQL 的用户认证

在 Web 应用开发中,用户认证是保障系统安全的基础需求。Spring Boot 3.4.3 结合 Spring Security 6.4.2 提供了强大的安全框架支持,可以轻松实现基于内存或数据库的用户认证功能。本文将详细介绍如何在 Spring Boot 3.4.3 中集成 Spring Security 6.4.2&…...

多款CANFD芯片单粒子效应对比分析

一、引言 随着航天、工业自动化等领域的快速发展,通信芯片在各种复杂环境下的可靠性变得至关重要。单粒子效应(Single Event Effect,SEE)是空间辐射环境中影响半导体器件性能的重要因素之一。CANFD(Controller Area Network with…...

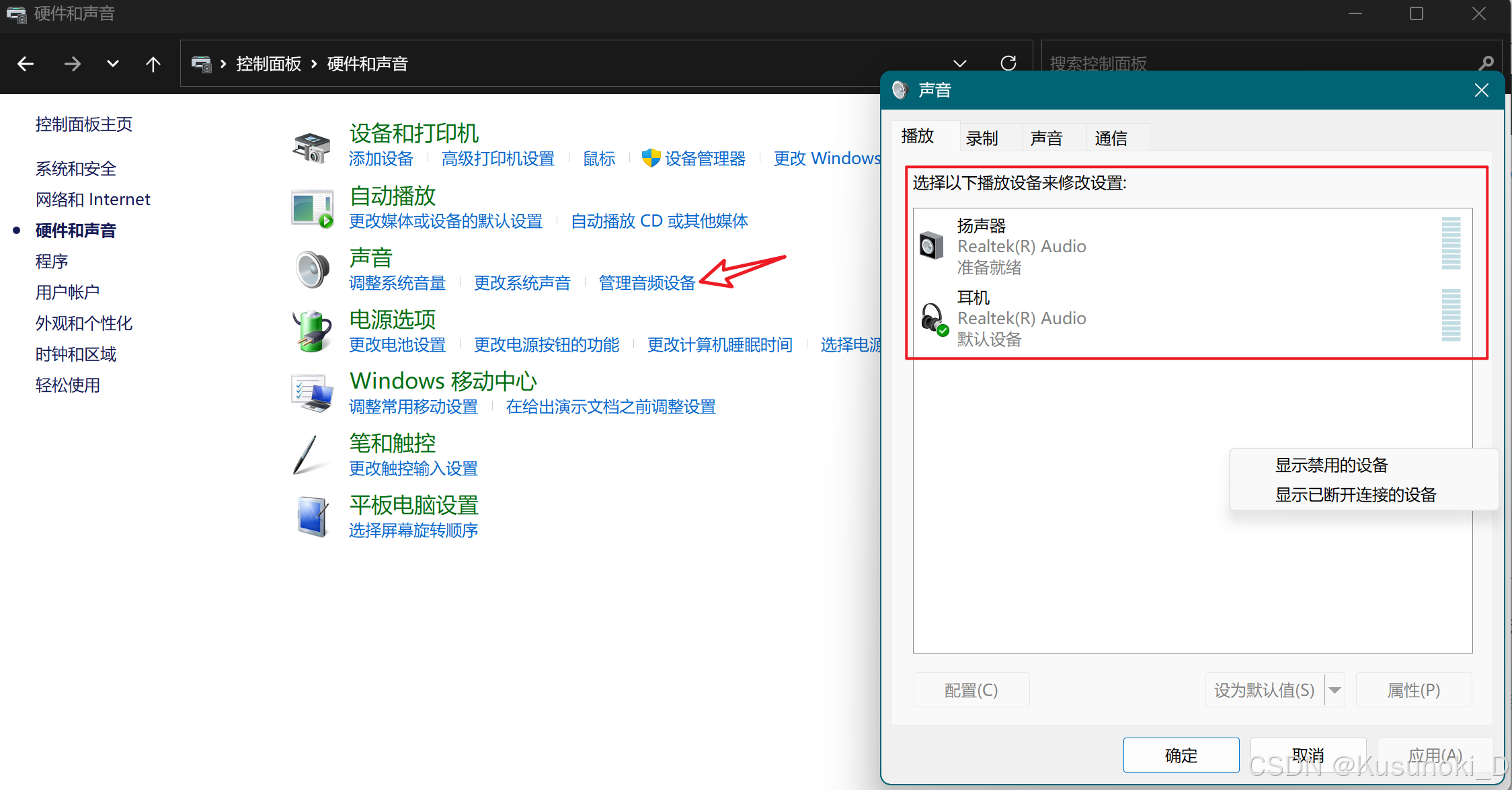

解决Win11耳机没有声音的问题

方法一:更新驱动程序(有效) 进入 “设置”(快捷键:WinX),点击 “Windows 更新” → “高级选项” 点击 “可选更新” ,然后点击 “驱动程序更新” 【注】:更新后可能会出…...

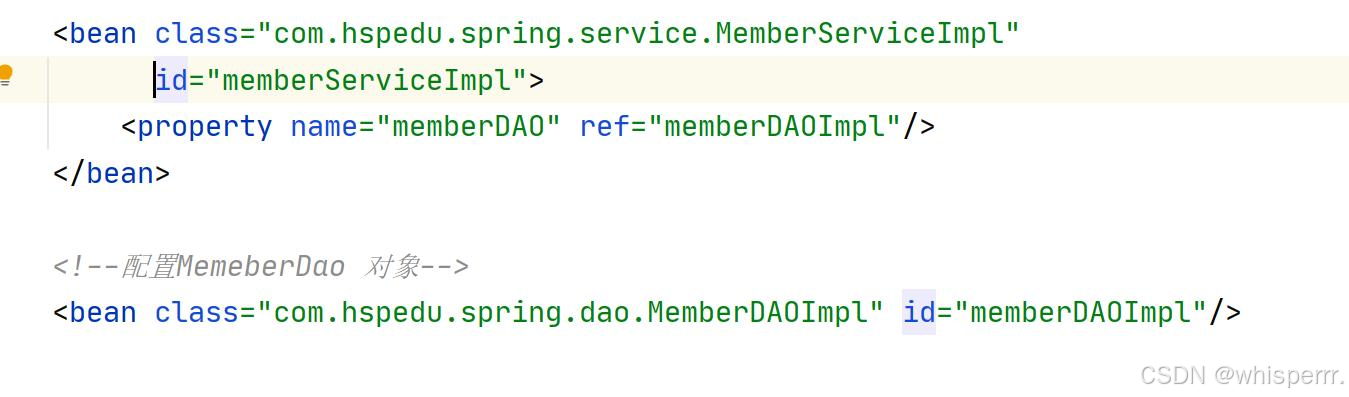

【spring02】Spring 管理 Bean-IOC,基于 XML 配置 bean

文章目录 🌍一. bean 创建顺序🌍二. bean 对象的单例和多例❄️1. 机制❄️2. 使用细节 🌍三. bean 的生命周期🌍四. 配置 bean 的后置处理器 【这个比较难】🌍五. 通过属性文件给 bean 注入值🌍六. 基于 X…...

内网渗透(杂项集合) --- 中的多协议与漏洞利用技术(杂项知识点 重点) 持续更新

目录 1. NetBIOS 名称的网络协议在局域网中内网渗透中起到什么作用 2. 使用 UDP 端口耗尽技术强制所有 DNS 查找失败,这个技术如何应用在局域网内网渗透测试中 3. 在本地创建一个 HTTP 服务来伪造 WPAD 服务器 什么是 WPAD 服务器?这个服务器是干嘛的…...

el-tabs添加按钮增加点击禁止样式

前置文章 一、vue使用element-ui自定义样式思路分享【实操】 二、vue3&ts&el-tabs多个tab表单校验 现状确认 点击添加按钮,没有点击样式,用户感知不明显没有限制最大的tab添加数量,可以无限添加 调整目标&代码编写 调整目标…...

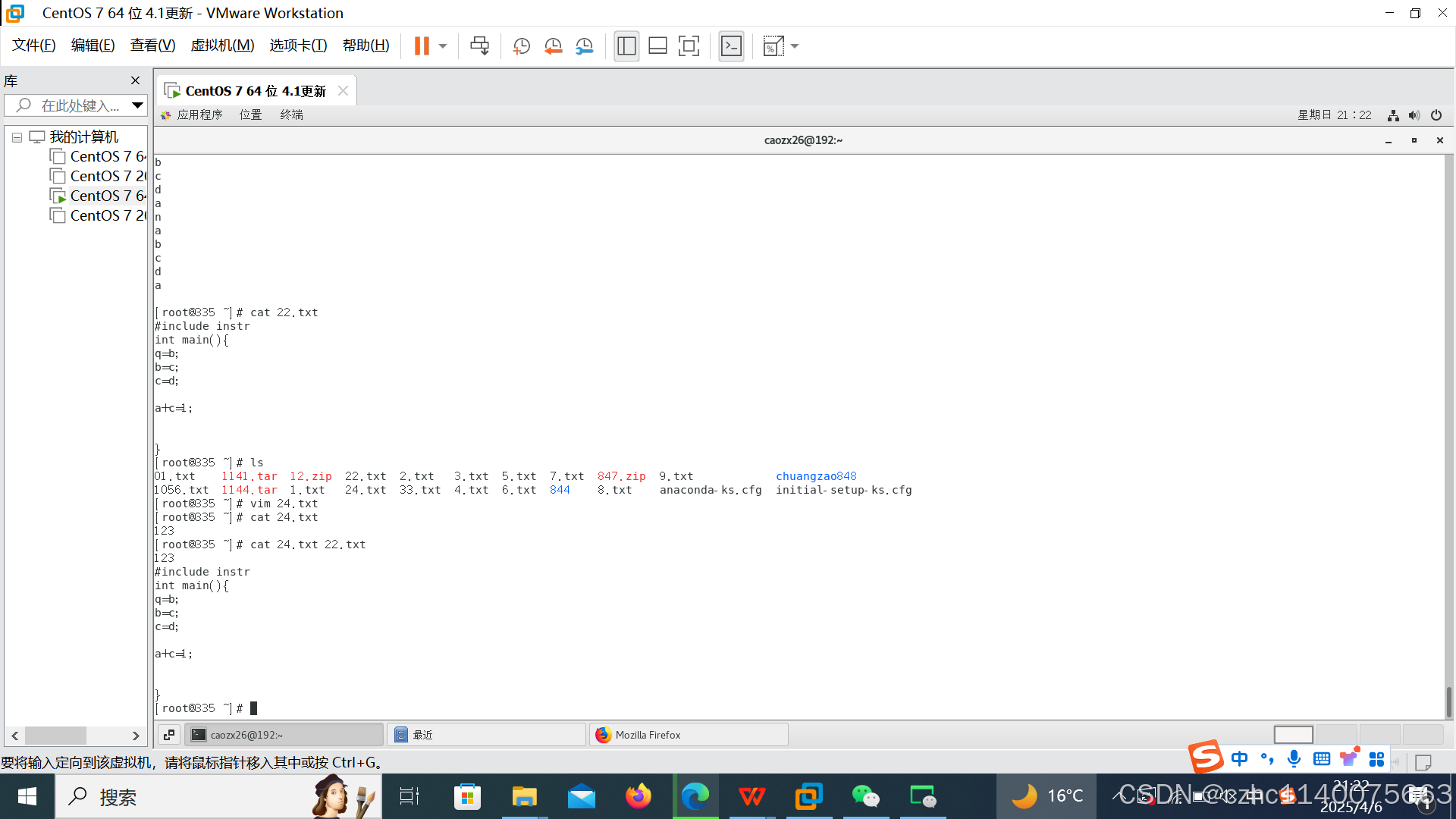

LINUX 5 vim cat zip unzip

dd u撤销 ctrlr取消撤销 q!刚才的操作不做保存 刚才是编辑模式 现在是可视化模式 多行注释...

PDFBox渲染生成pdf文档

使用PDFBox可以渲染生成pdf文档,并且自定义程度高,只是比较麻烦,pdf的内容位置都需要手动设置x(横向)和y(纵向)绝对位置,但是每个企业的单据都是不一样的,一般来说都会设…...

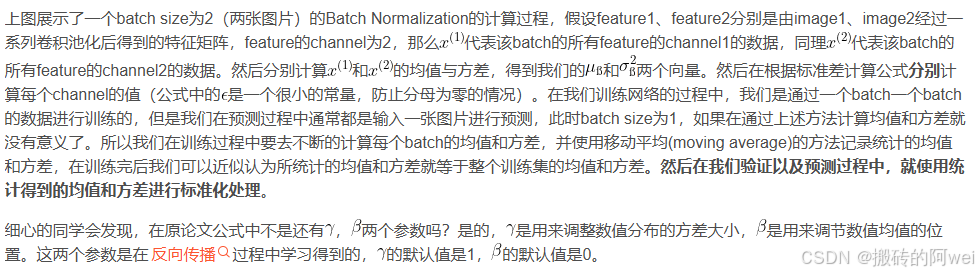

Batch Normalization:深度学习训练的加速引擎

引言 在深度学习的发展历程中,训练深度神经网络一直是一项极具挑战性的任务。随着网络层数的增加,梯度消失、梯度爆炸以及训练过程中的内部协变量偏移(Internal Covariate Shift)问题愈发严重,极大地影响了模型的收敛…...

低空经济基础设施建设方向与展望

随着科技的不断进步,低空经济正逐渐成为推动国家经济发展的新引擎。低空经济,指的是在低空范围内进行的各种经济活动,包括但不限于无人机物流、空中交通管理、低空旅游、农业监测等。本文将探讨低空经济基础设施建设的方向与未来展望。 1. 低…...

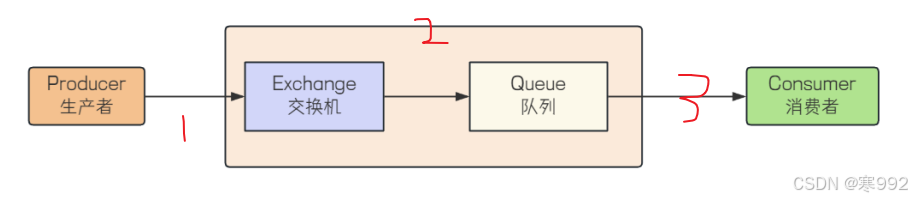

如何保证RabbitMQ消息的可靠传输?

在这个图中,消息可能丢失的场景是1,2,3 1.在生产者将消息发送给RabbitMQ的时候,消息到底有没有正确的到达服务器呢,RabbitMQ提供了两种解决方案: a. 通过事务机制实现(比较消耗性能࿰…...

)

Kotlin语言进阶:协程、Flow、Channel详解(二)

Kotlin语言进阶:协程、Flow、Channel详解(二) 一、Flow基础 1.1 什么是Flow Flow是Kotlin提供的用于处理异步数据流的解决方案,它建立在协程之上,具有以下特点: 冷流特性:只有在收集时才会开始发射数据背压处理:自动处理生产者和消费者速度不匹配的问题组合操作:提…...

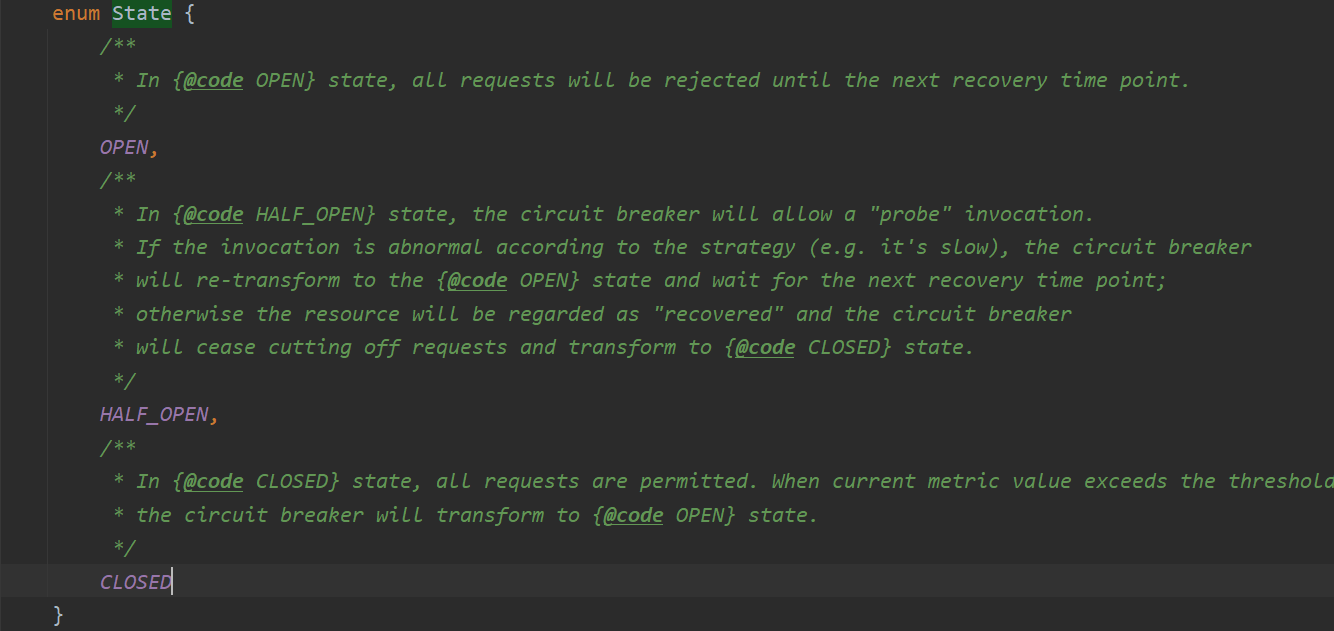

Sentinel核心源码分析(上)

文章目录 前言一、客户端与Spring Boot整合二、SphU.entry2.1、构建责任链2.2、调用责任链2.2.1、NodeSelectorSlot2.2.2、ClusterBuilderSlot2.2.3、LogSlot2.2.4、StatisticSlot2.2.5、AuthoritySlot2.2.6、SystemSlot2.2.7、FlowSlot2.2.7.1、selectNodeByRequesterAndStrat…...

Systemd安全加密备份系统与智能通知

实训背景 你是一家金融科技公司的系统架构师,需为敏感数据设计一套安全备份系统,满足以下需求: 加密存储:自动解密插入的LUKS加密USB设备,挂载到安全目录。备份验证:备份完成后校验文件完整性,…...

6.0 使用Qt+ OpenCV+Python加载图片

本例作为python图像处理的入门课程1,使用Qt+ OpenCV+Python加载图片。 主要有如下几个地方需要注意: 1. OpenCV 默认使用 BGR 格式,而 Qt 使用 RGB。显示前需要转换:cv2.cvtColor(img, cv2.COLOR_BGR2RGB),一般使用某个QLabel控件进行显示。 pic = cv2.cvtColor(pic, cv2.C…...

)

深度学习篇---网络分析(1)

文章目录 前言1. ImprovedResBlock(改进的残差块)结构组成卷积层1卷积层2跳跃连接(Downsample) 前向传播流程主路径跳跃路径残差连接 2. EnhancedCNN(主模型)2.1 初始特征提取层功能参数变化 2.2 残差块堆叠…...

【Mac 从 0 到 1 保姆级配置教程 11】- Mac 基础配置 Finder、触控板、常用快捷键等

文章目录 前言配置 Finder1. 把我们的家目录请出来2. 显示文件扩展名3. 展示隐藏文件4. 显示路径栏和状态栏5. 固定文件夹到工具栏 基础快捷键1. Finder 导航快捷键2. 文件操作快捷键3. 视图和显示快捷键4. 搜索和选择快捷键5. 实用技巧6. 关于文件创建 配置触控板1. 右键设置2…...

C++Primer - 动态内存管理

欢迎阅读我的 【CPrimer】专栏 专栏简介:本专栏主要面向C初学者,解释C的一些基本概念和基础语言特性,涉及C标准库的用法,面向对象特性,泛型特性高级用法。通过使用标准库中定义的抽象设施,使你更加适应高级…...

DeepSeek本地部署(Ollama)

1. Ollama 安装 Ollama 官网地址: https://ollama.com/安装包网盘地址: https://pan.baidu.com 2. Deepseek 部署 根据自己电脑配置和应用需求选择不同模型,配置不足会导致运行时候卡顿。 版本安装指令模型大小硬盘(存储)显卡…...

Amodal3R ,南洋理工推出的 3D 生成模型

Amodal3R 是一款先进的条件式 3D 生成模型,能够从部分可见的 2D 物体图像中推断并重建完整的 3D 结构与外观。该模型建立在基础的 3D 生成模型 TRELLIS 之上,通过引入掩码加权多头交叉注意力机制与遮挡感知注意力层,利用遮挡先验知识优化重建…...

第二期:深入理解 Spring Web MVC [特殊字符](核心注解 + 进阶开发)

前言: 欢迎来到 Spring Web MVC 深入学习 的第二期!在第一期中,我们介绍了 Spring Web MVC 的基础知识,学习了如何 搭建开发环境、配置 Spring MVC、编写第一个应用,并初步了解了 控制器、视图解析、请求处理流程 等核…...