AD9253 LVDS 高速ADC驱动开发

1、查阅AD9253器件手册

2、查阅Xilinx xapp524手册

3、该款ADC工作在125Msps下,14bit - 2Lane - 1frame 模式。

对应:data clock时钟为500M DDR mode。data line rate:1Gbps。frame clock:1/4 data clock

具体内容:下文的参考博客写的很清楚,我就不详细写了。参考博客clock align模块不完整,本文新增这个模块。

`timescale 1ns / 1psmodule bit_clk_align(input i_clk_p,input i_clk_n,input i_clk_200m,input i_reset,output o_bitclk_align_done,output o_bitclk_Monclk,output o_bitclk_Refclk);//------------------ variable declare ------------------

localparam PHASE_ADJ_FAILED = 1; // 0: OK 1:FAILEDwire s_BitClk_MonClkOut;

wire s_BitClk_RefClkOut;

wire s_bitclk;

wire s_idelayctrl_rdy;

wire s_bitclk_align_ena;

wire s_IntBitClk;

wire [07:00]s_bitclk_para;

wire [04:00]s_cntvalueout;

reg r_idelay_ce = 1;

reg r_idelay_inc = 1;reg [3:0]r_clk_div_reset = 4'hf; // high active

wire s_clk_div_reset;

reg r_phase_adj_status = 0;

reg r_bitclk_align_done = 0;

reg [03:00] r_adj_cnt = 0;

reg [03:00] r_bitclk_align_state = 0;

reg [01:00] s_iserdesout_dly_cnt = 0;//------------------ main body of code ------------------

assign o_bitclk_Monclk = s_BitClk_MonClkOut;

assign o_bitclk_Refclk = s_BitClk_RefClkOut;// generate iserdes reset

always@(posedge s_BitClk_RefClkOut)beginr_clk_div_reset <= r_clk_div_reset >> 1;

end

assign s_clk_div_reset = (|r_clk_div_reset);//

// state: adjust local clock phase align to input clk

//

assign s_bitclk_align_ena = s_idelayctrl_rdy && (~i_reset);

always@(posedge s_BitClk_RefClkOut)begincase(r_bitclk_align_state)0:beginr_idelay_ce <= 0;r_idelay_inc <= 0;r_phase_adj_status <= 0;r_bitclk_align_done <= 0;if(s_bitclk_align_ena)beginr_bitclk_align_state <= 1;endend1:begin//wait iserdes Q8~Q1 output stablelyr_idelay_ce <= 0;r_idelay_inc <= 0;if(s_iserdesout_dly_cnt >= 2)begins_iserdesout_dly_cnt <= 0;r_bitclk_align_state <= r_bitclk_align_state + 1;endelse begins_iserdesout_dly_cnt <= s_iserdesout_dly_cnt + 1;endend2:begin// search first patarn// 8'h00 - rising clk align// 8'hff - falling clk alignif(s_bitclk_para == 8'h00)beginr_bitclk_align_state <= 3;endelse beginif(s_cntvalueout == 31)begin// phase adjust flow failedr_idelay_ce <= 0;r_idelay_inc <= 0;r_phase_adj_status <= PHASE_ADJ_FAILED;endelse beginr_idelay_ce <= 1;r_idelay_inc <= 1;r_bitclk_align_state <= 1;endendend3:begin// find datain: riding edgeif(s_bitclk_para != 8'h00)beginr_bitclk_align_state <= 5;endelse beginif(s_cntvalueout == 31)begin// phase adjust flow failedr_idelay_ce <= 0;r_idelay_inc <= 0;r_phase_adj_status <= PHASE_ADJ_FAILED;endelse beginr_idelay_ce <= 1;r_idelay_inc <= 1;r_bitclk_align_state <= 4;endendend4:begin//wait iserdes Q8~Q1 output stablelyr_idelay_ce <= 0;r_idelay_inc <= 0;if(s_iserdesout_dly_cnt >= 2)begins_iserdesout_dly_cnt <= 0;r_bitclk_align_state <= 3;endelse begins_iserdesout_dly_cnt <= s_iserdesout_dly_cnt + 1;endend5:begin// adjust s_cntvalueout: -1r_idelay_ce <= 1;r_idelay_inc <= 0;r_bitclk_align_state <= 6;end6:beginr_idelay_ce <= 0;r_idelay_inc <= 0;r_bitclk_align_done <= 1;r_bitclk_align_state <= 6;enddefault:r_bitclk_align_state = 0;endcase

endassign o_bitclk_align_done = r_bitclk_align_done;//

//

//

IBUFDS #(.IOSTANDARD("LVDS_25") // Specify the input I/O standard) IBUFDS_inst (.O(s_bitclk), // Buffer output.I(i_clk_p), // Diff_p buffer input (connect directly to top-level port).IB(i_clk_n) // Diff_n buffer input (connect directly to top-level port));(* IODELAY_GROUP = "bitclk_group" *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRLIDELAYCTRL IDELAYCTRL_inst (.RDY(s_idelayctrl_rdy), // 1-bit output: Ready output.REFCLK(i_clk_200m), // 1-bit input: Reference clock input.RST(1'b0) // 1-bit input: Active high reset input);IDELAYE2 #(.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE).DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN).HIGH_PERFORMANCE_MODE("TRUE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE").IDELAY_TYPE("VARIABLE"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE.IDELAY_VALUE(0), // Input delay tap setting (0-31).PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0)..SIGNAL_PATTERN("CLOCK") // DATA, CLOCK input signal)IDELAYE2_inst (.CNTVALUEOUT(s_cntvalueout), // 5-bit output: Counter value output.DATAOUT(s_IntBitClk), // 1-bit output: Delayed data output.C(s_BitClk_RefClkOut), // 1-bit input: Clock input.CE(r_idelay_ce), // 1-bit input: Active high enable increment/decrement input.CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input.CNTVALUEIN(5'd0), // 5-bit input: Counter value input.DATAIN(1'b0), // 1-bit input: Internal delay data input.IDATAIN(s_bitclk), // 1-bit input: Data input from the I/O.INC(r_idelay_inc), // 1-bit input: Increment / Decrement tap delay input.LD(0), // 1-bit input: Load IDELAY_VALUE input.LDPIPEEN(1'b0), // 1-bit input: Enable PIPELINE register to load data input.REGRST(0) // 1-bit input: Active-high reset tap-delay input);BUFIO BUFIO_inst (.O(s_BitClk_MonClkOut), // 1-bit output: Clock output (connect to I/O clock loads)..I(s_IntBitClk) // 1-bit input: Clock input (connect to an IBUF or BUFMR).);BUFR #(.BUFR_DIVIDE("4"), // Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8" .SIM_DEVICE("7SERIES") // Must be set to "7SERIES" )BUFR_inst (.O(s_BitClk_RefClkOut), // 1-bit output: Clock output port.CE(1), // 1-bit input: Active high, clock enable (Divided modes only).CLR(0), // 1-bit input: Active high, asynchronous clear (Divided modes only).I(s_IntBitClk) // 1-bit input: Clock buffer input driven by an IBUF, MMCM or local interconnect);ISERDESE2 #(.DATA_RATE ("SDR"), // DDR, SDR

// .DATA_RATE ("DDR"), // DDR, SDR.DATA_WIDTH (8), // Parallel data width (2-8,10,14).DYN_CLKDIV_INV_EN ("FALSE"), // Enable DYNCLKDIVINVSEL inversion (FALSE, TRUE).DYN_CLK_INV_EN ("FALSE"), // Enable DYNCLKINVSEL inversion (FALSE, TRUE)// INIT_Q1 - INIT_Q4: Initial value on the Q outputs (0/1).INIT_Q1 (1'b0),.INIT_Q2 (1'b0),.INIT_Q3 (1'b0),.INIT_Q4 (1'b0),.INTERFACE_TYPE ("NETWORKING"), // MEMORY, MEMORY_DDR3, MEMORY_QDR, NETWORKING, OVERSAMPLE// .IOBDELAY ("IBUF"), // NONE, BOTH, IBUF, IFD.IOBDELAY ("NONE"), // NONE, BOTH, IBUF, IFD.NUM_CE (1), // Number of clock enables (1,2).OFB_USED ("FALSE"), // Select OFB path (FALSE, TRUE).SERDES_MODE ("MASTER"), // MASTER, SLAVE// SRVAL_Q1 - SRVAL_Q4: Q output values when SR is used (0/1).SRVAL_Q1 (1'b0),.SRVAL_Q2 (1'b0),.SRVAL_Q3 (1'b0),.SRVAL_Q4 (1'b0)

)

ISERDESE2_inst1(.O (), // 1-bit output: Combinatorial output// Q1 - Q8: 1-bit (each) output: Registered data outputs.Q1 (s_bitclk_para[0]),.Q2 (s_bitclk_para[1]),.Q3 (s_bitclk_para[2]),.Q4 (s_bitclk_para[3]),.Q5 (s_bitclk_para[4]),.Q6 (s_bitclk_para[5]),.Q7 (s_bitclk_para[6]),.Q8 (s_bitclk_para[7]),// SHIFTOUT1, SHIFTOUT2: 1-bit (each) output: Data width expansion output ports.SHIFTOUT1 (),.SHIFTOUT2 (),.BITSLIP (0), // 1-bit input: The BITSLIP pin performs a Bitslip operation synchronous to// CLKDIV when asserted (active High). Subsequently, the data seen on the Q1// to Q8 output ports will shift, as in a barrel-shifter operation, one// position every time Bitslip is invoked (DDR operation is different from// SDR).// CE1, CE2: 1-bit (each) input: Data register clock enable inputs.CE1 (1'b1),.CE2 (1'b0),.CLKDIVP (1'b0), // 1-bit input: TBD// Clocks: 1-bit (each) input: ISERDESE2 clock input ports.CLK (s_BitClk_MonClkOut), // 1-bit input: High-speed clock.CLKB (0), // 1-bit input: High-speed secondary clock.CLKDIV (s_BitClk_RefClkOut), // 1-bit input: Divided clock.OCLK (1'b0), // 1-bit input: High speed output clock used when INTERFACE_TYPE="MEMORY"// Dynamic Clock Inversions: 1-bit (each) input: Dynamic clock inversion pins to switch clock polarity.DYNCLKDIVSEL (1'b0), // 1-bit input: Dynamic CLKDIV inversion.DYNCLKSEL (1'b0), // 1-bit input: Dynamic CLK/CLKB inversion// Input Data: 1-bit (each) input: ISERDESE2 data input ports.D (s_bitclk), // 1-bit input: Data input

// .DDLY (s_IntBitClk), // 1-bit input: Serial data from IDELAYE2.DDLY (0), // 1-bit input: Serial data from IDELAYE2.OFB (1'b0), // 1-bit input: Data feedback from OSERDESE2.OCLKB (1'b0), // 1-bit input: High speed negative edge output clock

// .RST (i_reset), // 1-bit input: Active high asynchronous reset.RST (s_clk_div_reset ), // 1-bit input: Active high asynchronous reset// SHIFTIN1, SHIFTIN2: 1-bit (each) input: Data width expansion input ports.SHIFTIN1 (1'b0),.SHIFTIN2 (1'b0)

);// note:ISERDES/OSERDES需要复位,才会生效。

// 虽然支持异步复位,但是推荐用CLKDIV这个时钟来进行同步复位,或采用异步复位同步释放。

// 即.RST (i_reset), // 1-bit input: Active high asynchronous reset

// i_reset可以替换为由s_BitClk_RefClkOut来内部逻辑产生s_clk_div_reset 。endmodule补充知识:

- OSERDES2原语

- ISERDES2原语

参考博客:

LVDS接口程序设计框架及仿真_lvds接口仿真-CSDN博客

xilinx原语详解及仿真——OSERDESE2 - 知乎 (zhihu.com)

相关文章:

AD9253 LVDS 高速ADC驱动开发

1、查阅AD9253器件手册 2、查阅Xilinx xapp524手册 3、该款ADC工作在125Msps下,14bit - 2Lane - 1frame 模式。 对应:data clock时钟为500M DDR mode。data line rate:1Gbps。frame clock:1/4 data clock 具体内容:…...

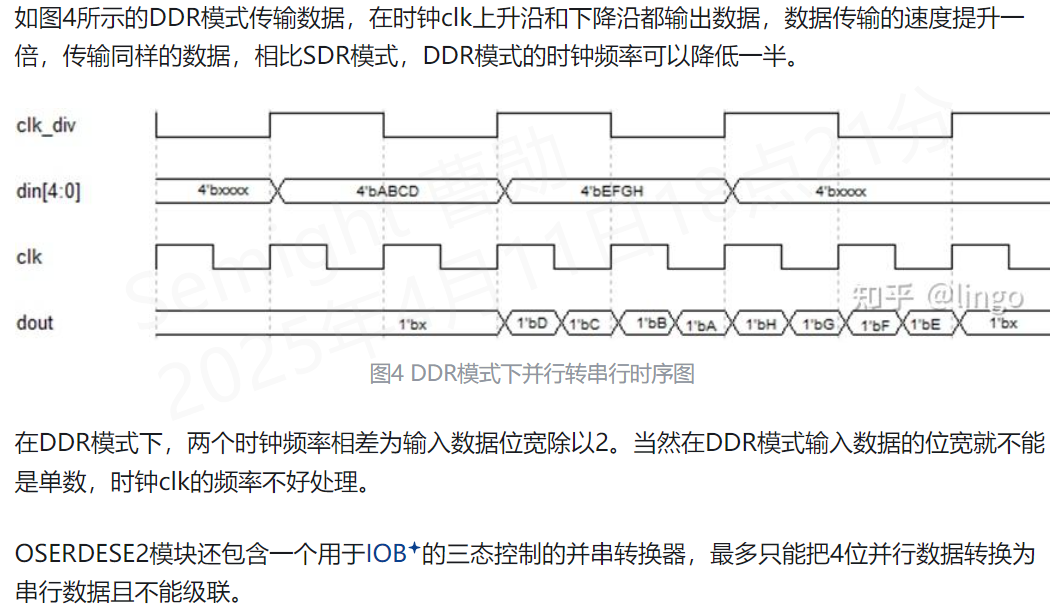

pycharm2024.3.5版本配置conda踩坑

配置解释器是conda时,死活选不到自己的环境 看了很多,都是说要选scripts下的conda.exe 都没用 主要坑在于这是新版的pycharm 是配置condabin 下的 conda.bat 参考:PyCharm配置PyTorch环境(完美解决找不到Conda可执行文件python.exe问题) …...

【异常处理】Clion IDE中cmake时头文件找不到 头文件飘红

如图所示是我的clion项目目录 我自定义的data_structure.h和func_declaration.h在unit_test.c中无法检索到 cmakelists.txt配置文件如下所示: cmake_minimum_required(VERSION 3.30) project(noc C) #设置头文件的目录 include_directories(${CMAKE_SOURCE_DIR}/…...

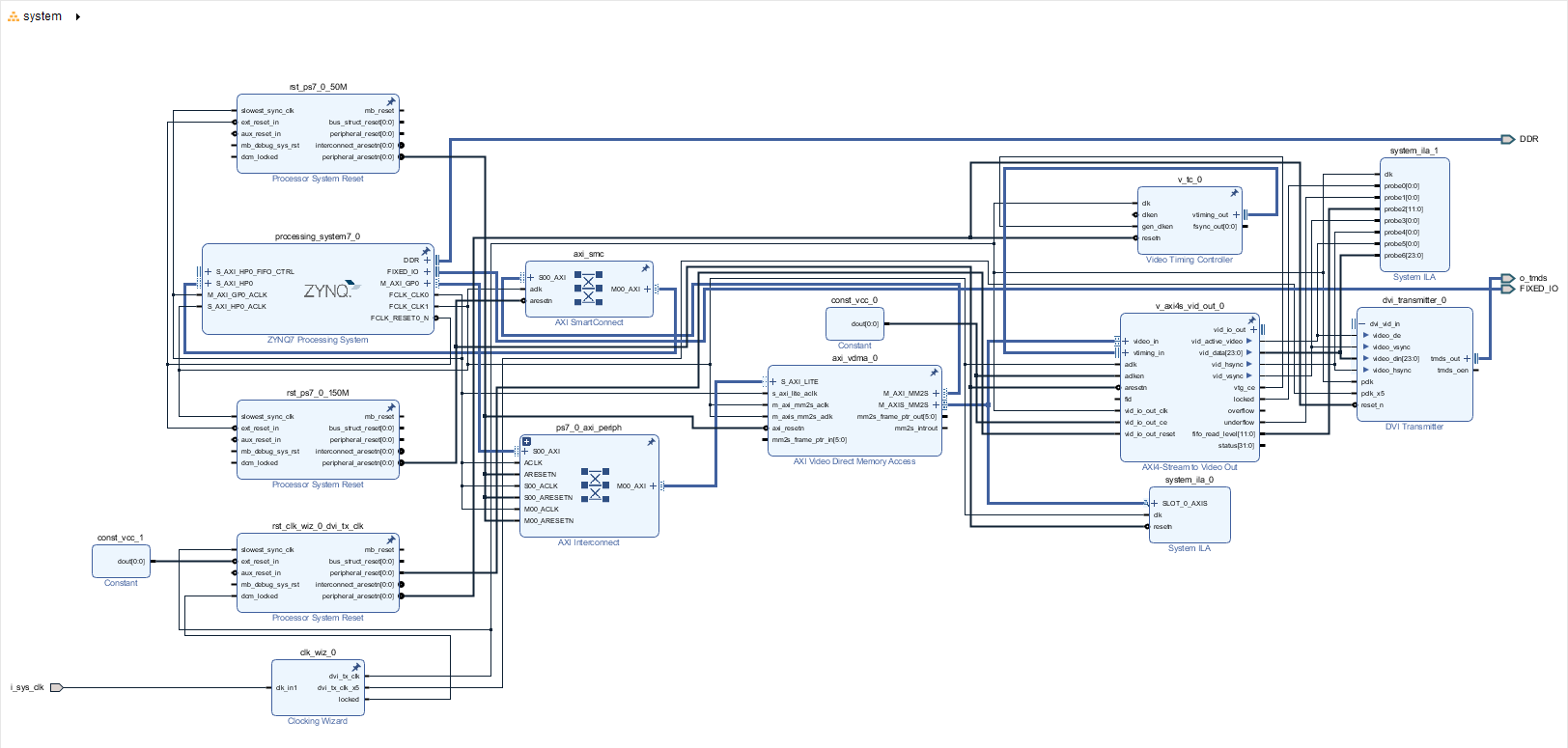

14 - VDMA彩条显示实验

文章目录 1 实验任务2 系统框图3 硬件设计4 软件设计 1 实验任务 本实验任务是PS端写彩条数据至DDR3内存中,然后通过PL端的VDMA IP核将彩条数据通过HDMI接口输出显示。 2 系统框图 本实验是用HDMI接口固定输出1080P的彩条图,所以: rgb2lc…...

:touch)

每天学一个 Linux 命令(13):touch

Linux 文件管理命令:touch touch 是 Linux 中一个简单但高频使用的命令,主要用于创建空文件或修改文件的时间戳(访问时间、修改时间)。它是文件管理和脚本操作的实用工具。 1. 命令作用 创建空文件:快速生成一个或多个空白文件。更新时间戳:修改文件的访问时间(Access …...

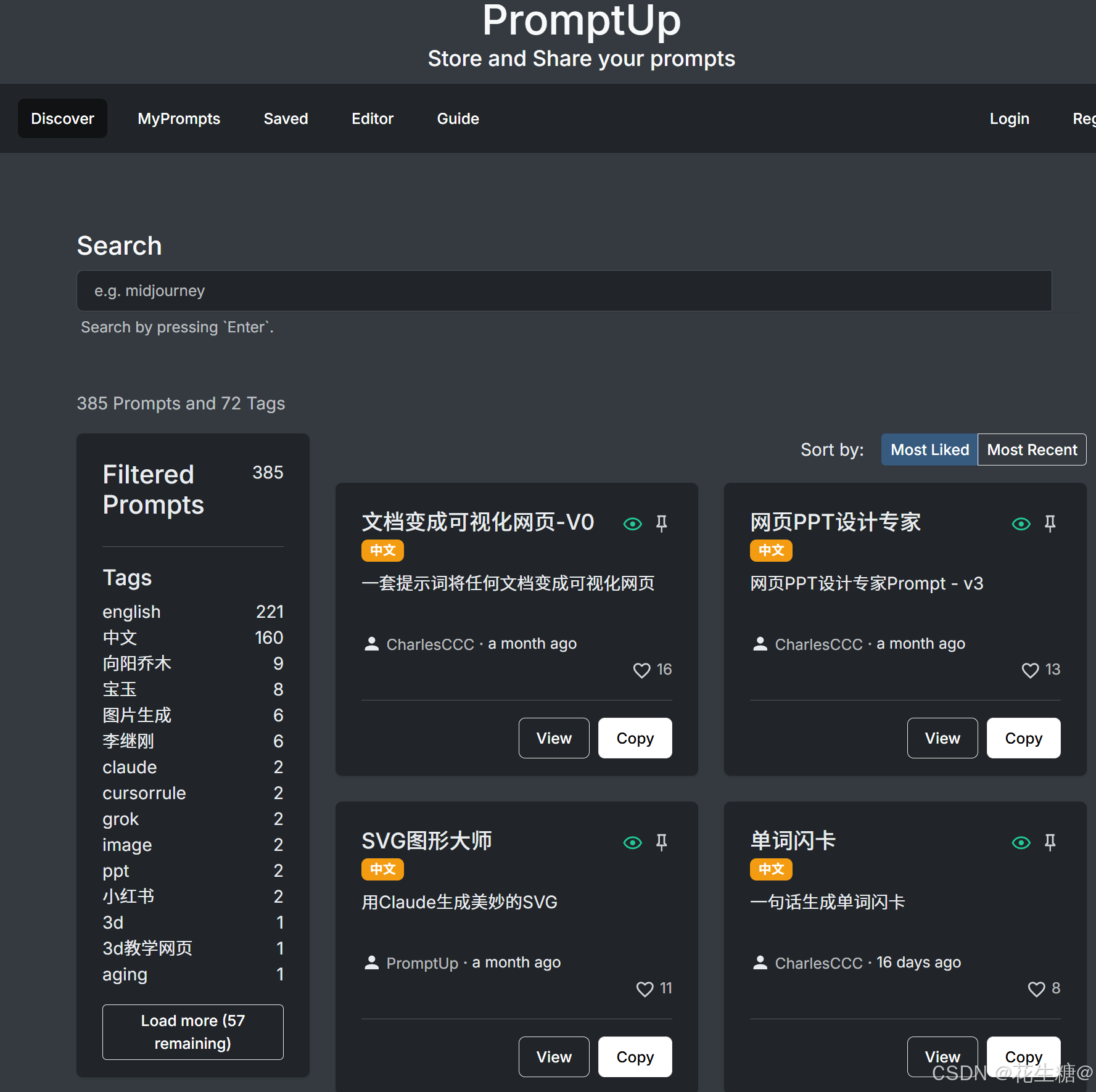

PromptUp 网站介绍:AI助力,轻松创作

1. 网站定位与核心功能 promptup.net 可能是一个面向 创作者、设计师、营销人员及艺术爱好者 的AI辅助创作平台,主打 零门槛、智能化的内容生成与优化。其核心功能可能包括: AI艺术创作:通过输入关键词、选择主题或拖放模板,快速生成风格多样的数字艺术作品(如插画、海报…...

高级java每日一道面试题-2025年3月26日-微服务篇[Nacos篇]-在Spring Cloud项目中如何集成Nacos?

如果有遗漏,评论区告诉我进行补充 面试官: 在Spring Cloud项目中如何集成Nacos? 我回答: 在Spring Cloud项目中集成Nacos,可以充分利用Nacos作为服务注册与发现中心以及配置管理中心的功能。以下是详细的步骤和说明,帮助你完成这一集成过程…...

平台的整体概览与未来发展)

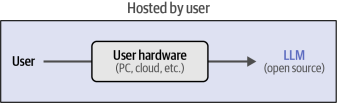

AI 大语言模型 (LLM) 平台的整体概览与未来发展

📋 分析报告:AI 大语言模型 (LLM) 平台的整体概览与未来发展 自动生成的结构化分析报告 💻 整体概述:AI LLM 平台的市场现状与发展动力 随着人工智能技术的飞速发展,大语言模型(Large Language Models, L…...

Java中的Map vs Python字典:核心对比与使用指南

一、核心概念 1. 基本定义 Python字典(dict) :动态类型键值对集合,语法简洁,支持快速查找。Java Map:接口,常用实现类如 HashMap、LinkedHashMap,需声明键值类型(泛型&…...

人工智能100问☞第3问:深度学习的核心原理是什么?

目录 一、通俗解释 二、专业解析 三、权威参考 深度学习的核心原理是通过构建多层神经网络结构,逐层自动提取并组合数据特征,利用反向传播算法优化参数,从而实现对复杂数据的高层次抽象和精准预测。 一、通俗解释 深度学习的核心原理,就像是教计算机像婴儿…...

金能电力:配电房为什么离不开绝缘胶板

在当今电力系统日益复杂、对供电稳定性与安全性要求极高的时代,每一个细节都关乎着电力供应的顺畅以及工作人员的生命安全。而配电房里常常被大家忽视的绝缘垫,实则起着至关重要的 “守护” 作用。今天,金能电力就来给大家详细讲讲配电房为什…...

Python 深度学习实战 第1章 什么是深度学习代码示例

第1章:什么是深度学习 内容概要 第1章介绍了深度学习的背景、发展历史及其在人工智能(AI)和机器学习(ML)中的地位。本章探讨了深度学习的定义、其与其他机器学习方法的关系,以及深度学习在近年来取得的成…...

【模块化拆解与多视角信息1】基础信息:隐藏的筛选规则——那些简历上没说出口的暗号

写在最前 作为一个中古程序猿,我有很多自己想做的事情,比如埋头苦干手搓一个低代码数据库设计平台(目前只针对写java的朋友),比如很喜欢帮身边的朋友看看简历,讲讲面试技巧,毕竟工作这么多年,也做到过高管,有很多面人经历,意见还算有用,大家基本都能拿到想要的offe…...

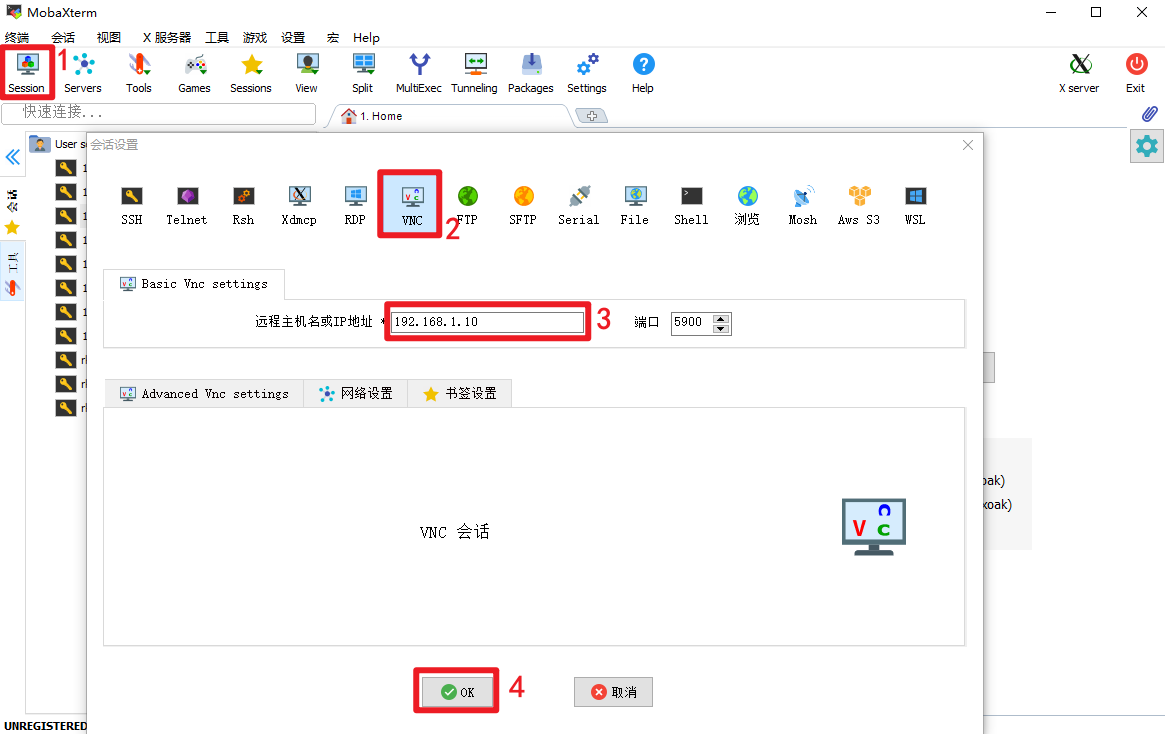

【HD-RK3576-PI】VNC 远程桌面连接

在当今数字化时代,高效便捷的操作方式是技术爱好者与专业人士的共同追求。对于使用 HD-RK3576-PI微型单板计算机的用户而言,当面临没有显示屏的场景时,如何实现远程操作桌面系统呢?别担心,VNC 远程桌面连接将为你解决这…...

Vue.js 中 v-if 的使用及其原理

在 Vue.js 的开发过程中,条件渲染是一项极为常见的需求。v-if指令作为 Vue.js 实现条件渲染的关键手段,能够根据表达式的真假来决定是否渲染某一块 DOM 元素。它在优化页面展示逻辑、提升用户体验等方面发挥着重要作用。接下来,我们就深入探讨…...

电梯广告江湖的终局:分众 “吃掉” 新潮,是救赎还是迷途?

文 / 大力财经 作者 / 魏力 导言:商业世界的底层运行法则,从来都是能量流动的自然映射。宇宙第一性原理和运行法则是,能量大的吸引能量小的。电梯里的战争与和平,从对抗到合并,成为中国商业竞争史中关于博弈与进化的…...

第十六届蓝桥杯大赛软件赛省赛 C/C++ 大学B组

由于官方没有公布题目的数据, 所以代码仅供参考 1. 移动距离 题目链接:P12130 [蓝桥杯 2025 省 B] 移动距离 - 洛谷 【问题描述】 小明初始在二维平面的原点,他想前往坐标 (233, 666)。在移动过程中,他 只能采用以下两种移动方式…...

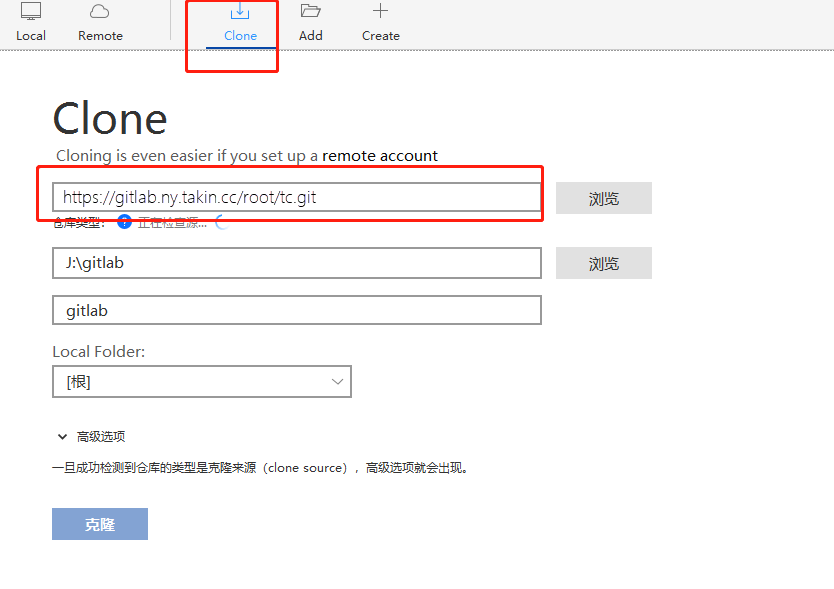

如何在 CentOS 7 系统上以容器方式部署 GitLab,使用 ZeroNews 通过互联网访问 GitLab 私有仓库,进行代码版本发布与更新

第 1 步: 部署 GitLab 容器 在开始部署 GitLab 容器之前,您需要创建本地目录来存储 GitLab 数据、配置和日志: #创建本地目录 mkdir -p /opt/docker/gitlab/data mkdir -p /opt/docker/gitlab/config mkdir -p /opt/docker/gitlab/log#gi…...

第1章 对大型语言模型的介绍

人类正处在一个关键转折点。自2012年起,基于深度神经网络的人工智能系统研发进入快速通道,将这一技术推向了新高度:至2019年底,首个能够撰写与人类文章真假难辨的软件系统问世,这个名为GPT-2(生成型预训练变…...

Quartus II的IP核调用及仿真测试

目录 第一章 什么是IP核?第二章 什么是LPM?第一节 设置LPM_COUNTER模块参数第二节 仿真 第三章 什么是PLL?第一节 设置ALTPLL(嵌入式锁相环)模块参数第二节 仿真 第四章 什么是RAM?第一节 RAM_1PORT的调用第…...

JDK(Java Development Kit)从发布至今所有主要版本 的详细差异、新增特性及关键更新的总结,按时间顺序排列

以下是 JDK(Java Development Kit)从发布至今所有主要版本 的详细差异、新增特性及关键更新的总结,按时间顺序排列: 1. JDK 1.0 (1996) 发布年份:1996年1月23日关键特性: Java首次正式发布。核心语言特性…...

Vue 3 和 Vue 2 的区别及优点

Vue.js 是一个流行的 JavaScript 框架,广泛用于构建用户界面和单页应用。自 Vue 3 发布以来,很多开发者开始探索 Vue 3 相较于 Vue 2 的新特性和优势。Vue 3 引入了许多改进,优化了性能、增强了功能、提升了开发体验。本文将详细介绍 Vue 2 和…...

Linux 入门五:Makefile—— 从手动编译到工程自动化的蜕变

一、概述:Makefile—— 工程编译的 “智能指挥官” 1. 为什么需要 Makefile? 手动编译的痛点:当工程包含数十个源文件时,每次修改都需重复输入冗长的编译命令(如gcc file1.c file2.c -o app),…...

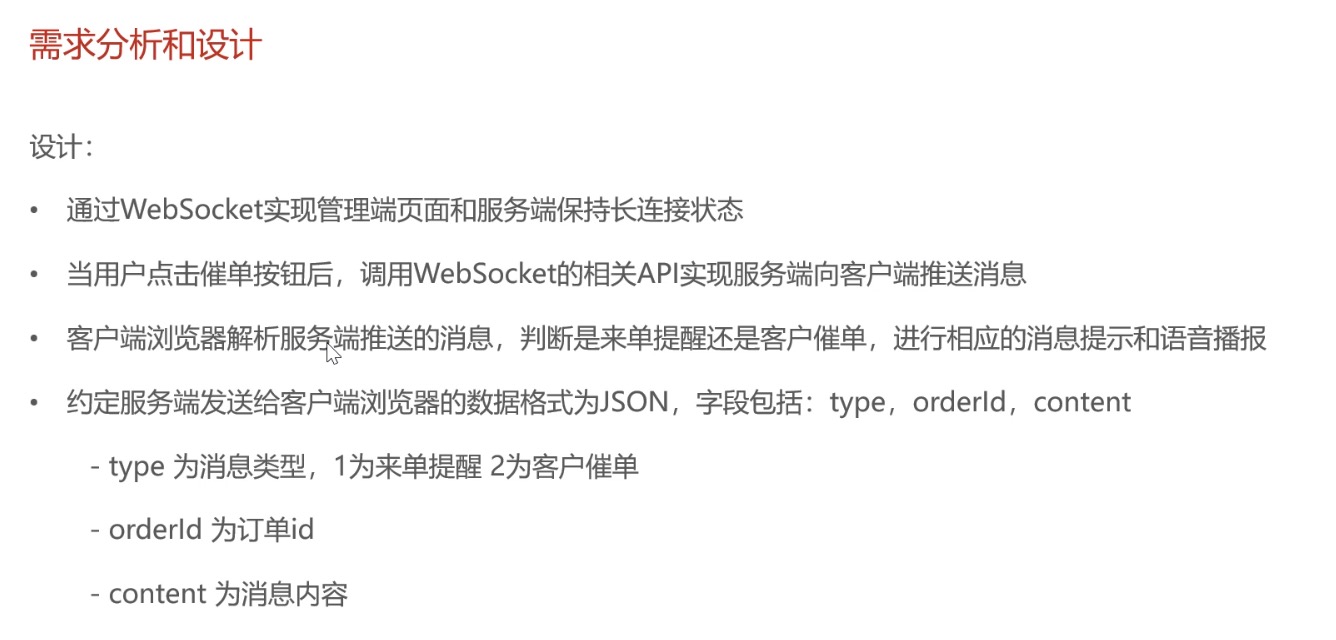

通过websocket给服务端发送订单催单提醒消息

controller层 GetMapping("/reminder/{id}")public Result Remainder(PathVariable("id") Long id){orderService.remainder(id);return Result.success();} 实现类 Overridepublic void remainder(Long id) {Orders ordersDB orderMapper.getById(id);…...

【NumPy科学计算:高性能数组操作核心指南】

目录 前言:技术背景与价值当前技术痛点解决方案概述目标读者说明 一、技术原理剖析核心概念图解关键技术模块技术选型对比 二、实战演示环境配置要求核心代码实现运行结果验证 三、性能对比测试方法论量化数据对比结果分析 四、最佳实践推荐方案 ✅常见错误 ❌调试技…...

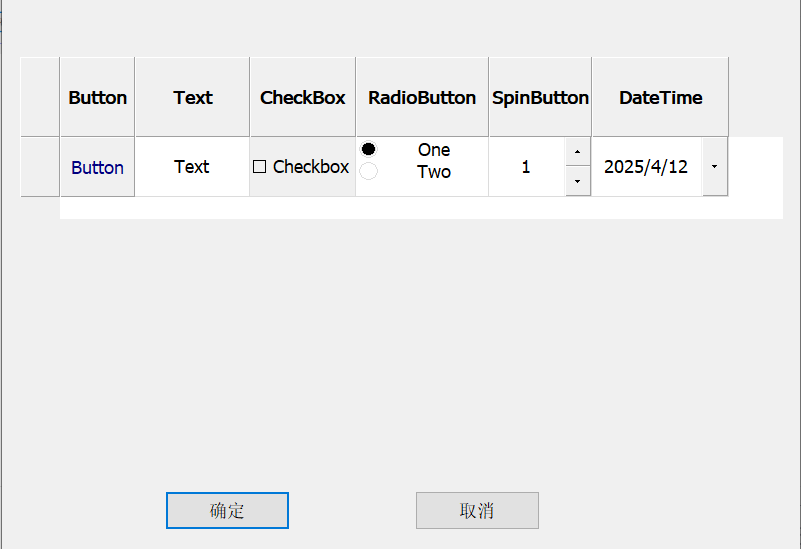

c++ 表格控件 UltimateGrid 控件实例

控件区域: 使用效果: 代码如下: void MyUGCtrl::OnSetup() { m_nButtonIndex AddCellType(&m_button); SetNumberCols(6); AppendRow(); CUGCell cell; int rows, cols; int row 0; // 头部 int nHeaderRow -1; …...

从单机版到超级APP:MCP如何解锁AI的超能力

MCP:AI界的“万能充电宝”——让AI从此告别“语言不通”的尴尬! 开篇:AI咖啡馆的尴尬日常 想象一下这样的场景: 一位AI助手在咖啡馆里手忙脚乱——它想帮用户点杯咖啡,但需要先写代码调用天气API(“今天下…...

【算法】 欧拉函数与欧拉降幂 python

欧拉函数 欧拉函数 ϕ ( n ) \phi(n) ϕ(n) 表示小于等于 n 的正整数中与 n 互质的数的个数。即: ϕ ( n ) ∣ { k ∈ Z ∣ 1 ≤ k ≤ n , gcd ( k , n ) 1 } ∣ \phi(n) \left| \{ k \in \mathbb{Z}^ \mid 1 \leq k \leq n, \gcd(k, n) 1 \} \right| ϕ(n)…...

【Python] pip制作离线包

制作离线安装包是一种非常实用的方法,尤其是在网络环境受限或需要在多台机器上部署相同环境时。以下是详细的步骤,帮助您创建一个包含所有依赖项的离线安装包,并在后续环境中复用。 步骤 1:准备工具和环境 确保您有一台可以访问互…...

什么是回表?哪些数据库存在回表?

目录 一、什么是回表1. 回表的核心流程2. 示例说明3. 回表的性能问题4. 总结 二、哪些数据库会有回表1. MySQL(InnoDB)2. Oracle3. 其他数据库(如 SQL Server、PostgreSQL)4. 总结 三、非聚集索引与聚集索引的区别及产生原因1. 聚…...