7系列 之 I/O标准和终端技术

背景

《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、LVTTL (Low Voltage TTL)

- 2、LVCMOS (Low Voltage CMOS)

- 3、LVDCI (Low-Voltage Digitally Controlled Impedance)

- 3.1、LVDCI

- 3.2、LVDCI_DV2

- 3.3、HSLVDCI (High-Speed LVDCI)

- 4、HSTL (High-Speed Transceiver Logic)

- 4.1、HSTL Class I(1.2V, 1.5V, or 1.8V)

- 4.2、HSTL Class II

- 4.3、Differential HSTL Class I

- 4.4、Differential HSTL Class II

- 5、SSTL (Stub-Series Terminated Logic)

- 5.1、SSTL18、SSTL15、SSTL135、SSTL12

- 5.2、SSTL18, SSTL15, SSTL135, SSTL12

- 5.3、Differential SSTL18, SSTL15, SSTL135, SSTL12

- 5.4、SSTL18, SSTL15, SSTL135, or SSTL12 (T_DCI) Termination

- 6、HSUL_12 (High Speed Unterminated Logic)

- 6.1、HSUL_12

- 6.2、Differential HSUL_12

- 7、MOBILE_DDR (Low Power DDR)

- 8、LVDS 和 LVDS_25(Low Voltage Differential Signaling)

- 9、RSDS (Reduced Swing Differential Signaling)

- 10、Mini-LVDS (Mini Low Voltage Differential Signaling)

- 11、PPDS (Point-to-Point Differential Signaling)

- 12、TMDS (Transition Minimized Differential Signaling)

- 13、BLVDS (Bus LVDS)

- 14、参考文献

前言

本文对应的是《ug471_7Series_SelectIO.pdf》的第 1 章 < Supported I/O Standards and Terminations > 部分,是对7系列的所支持的不同I/O标准的一个概述与介绍。

1、LVTTL (Low Voltage TTL)

LVTTL标准 仅 在 HR I/O Bank 中可用。

LVTTL 是一种适用于 3.3V 应用的通用 EIA/JESD 标准,采用单端 CMOS 输入缓冲器和推挽输出缓冲器。该标准要求 3.3V 输出源电压(VCCO),但不要求使用参考电压(VREF)或终端电压(VTT)。该标准由 JEDEC(JESD 8C.01)定义。

LVTTL(Low-Voltage Transistor-Transistor Logic)是一种低电压的晶体三极管逻辑标准。它是TTL(Transistor-Transistor Logic)标准的变体,它采用更低的供电电压,通常为3.3伏(V)。低电平和高电平的电压阈值会根据具体的器件和规范而有所不同,但通常低电平范围接近0伏至0.8伏,高电平范围接近2.2伏至3.3伏。

它使用单端CMOS输入缓冲器和推挽输出缓冲器来支持LVTTL的输入与输出的。进一步说输入信号会转换成CMOS逻辑电平,对于输出信号是通过推挽输出缓冲器将输入逻辑信号转换成推或拉的输出电平,这样能够提供足够的输出电流以驱动外部负载。

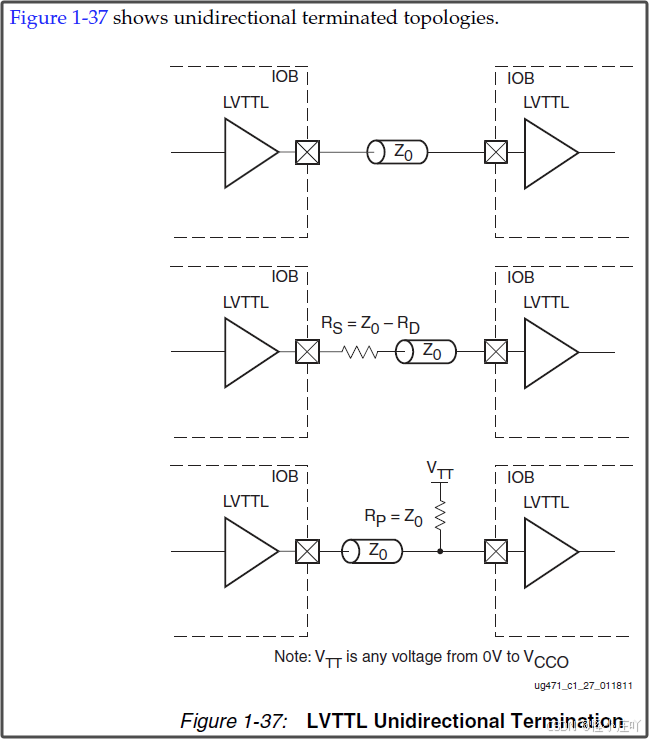

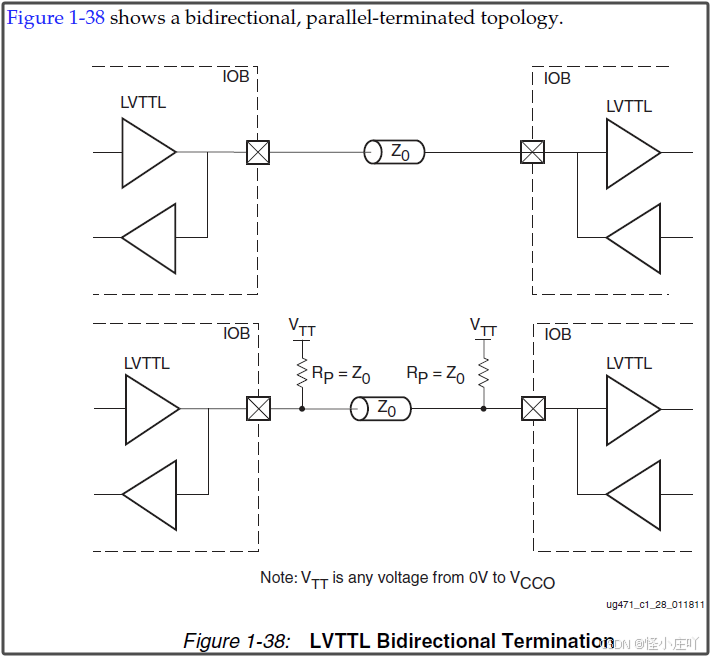

图 1-37 和图 1-38 展示了单向和双向 LVTTL 终端技术的示例电路。这两张图展示了源端串联和并联终止拓扑的示例。

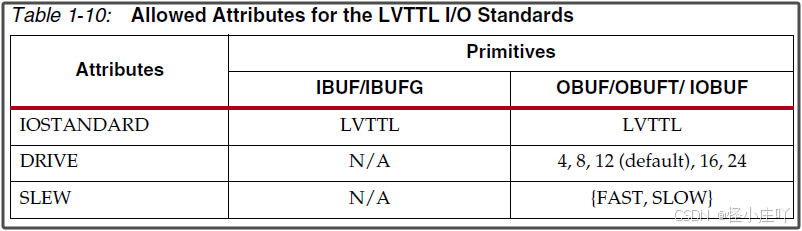

表1-10 详细列出了可应用于 LVTTL I/O 标准的允许属性。

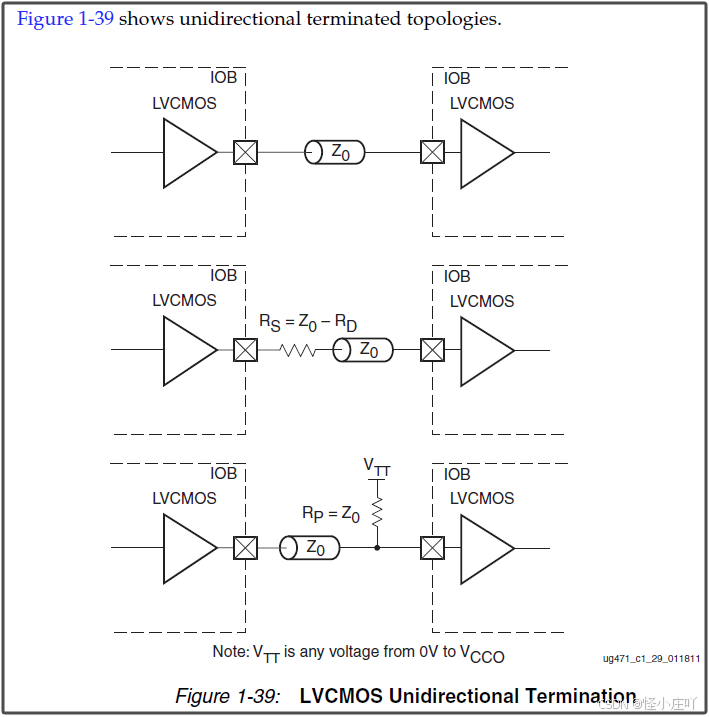

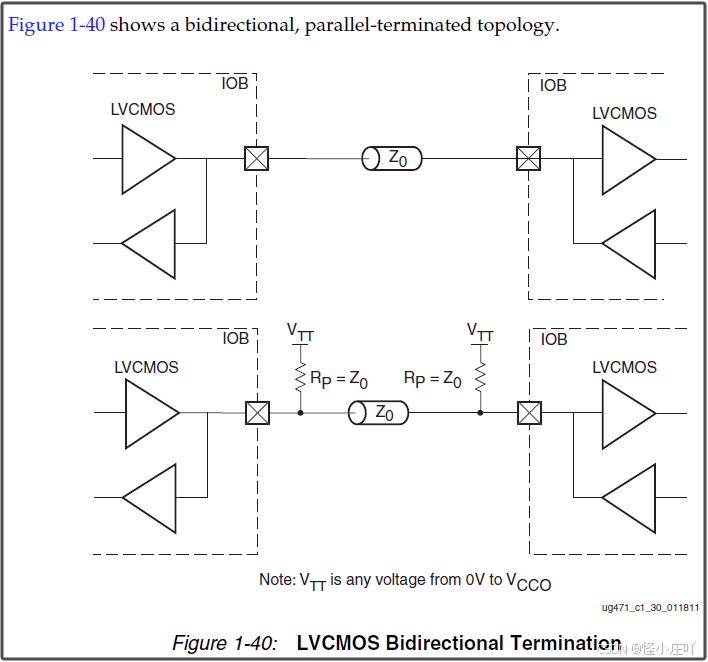

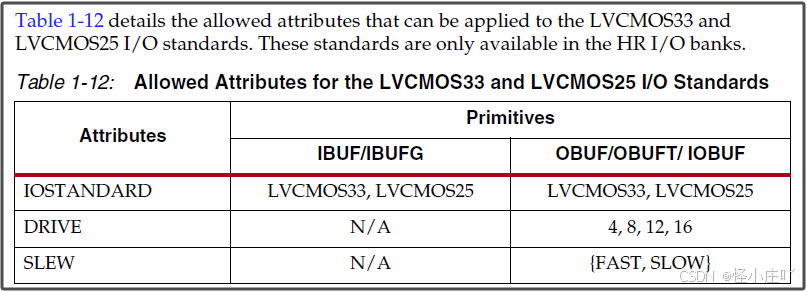

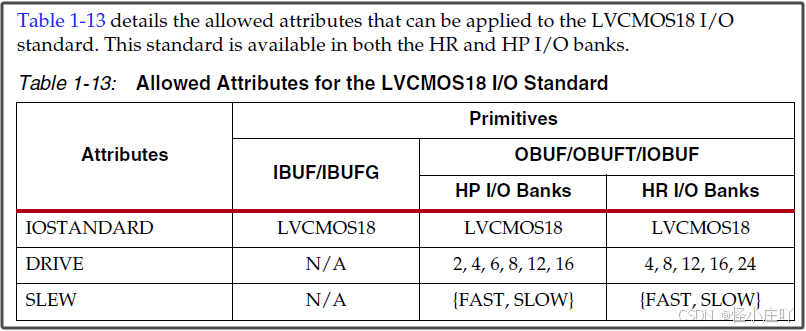

2、LVCMOS (Low Voltage CMOS)

该LVCMOS 标准在 HR I/O Bank 和 HP I/O Bank 中均可用。

LVCMOS 是一种广泛应用的基于 CMOS 晶体管的开关标准,由 JEDEC(JESD 8C.01 标准)定义。

LVCMOS通常指的是以3.3伏(V)或者更低的电压供电的CMOS电路。

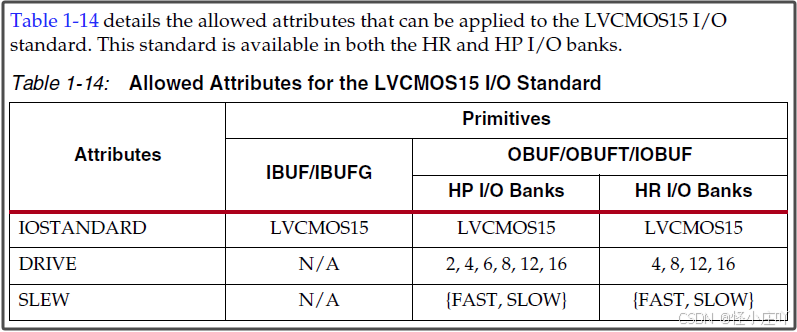

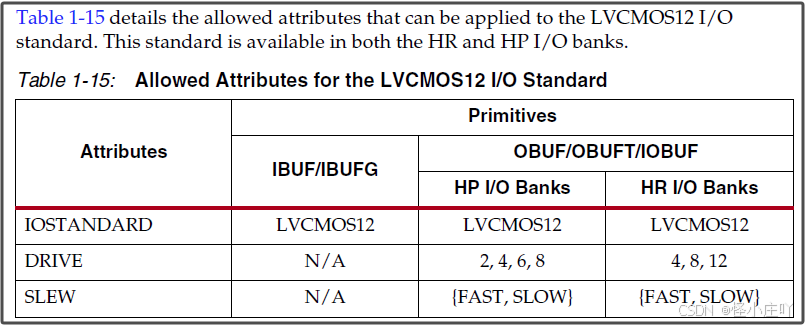

7 系列 FPGA 支持的 LVCMOS 标准包括:LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25 和 LVCMOS33。

3、LVDCI (Low-Voltage Digitally Controlled Impedance)

LVDCI的三个相关标准:LVDCI、LVDCI_DV2和HSLVDCI,仅 在 HP I/O Bank 中可用。

这种电平标准信号是对输出信号的阻抗进行控制和调整,使得输出信号具有受控和稳定的阻抗特性,以适应特定的传输线或系统要求,进而提高信号的传输质量和完整性。这里也就用到了Xilinx的DCI调节器。DCI是具有可控输出阻抗的驱动器,用于驱动信号进入特定的传输线或电路。

3.1、LVDCI

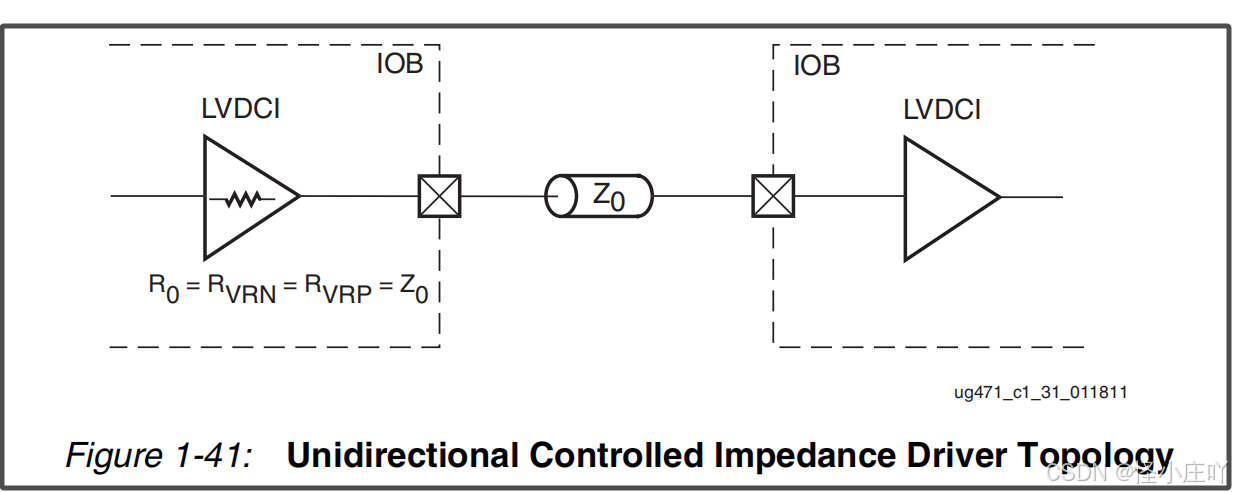

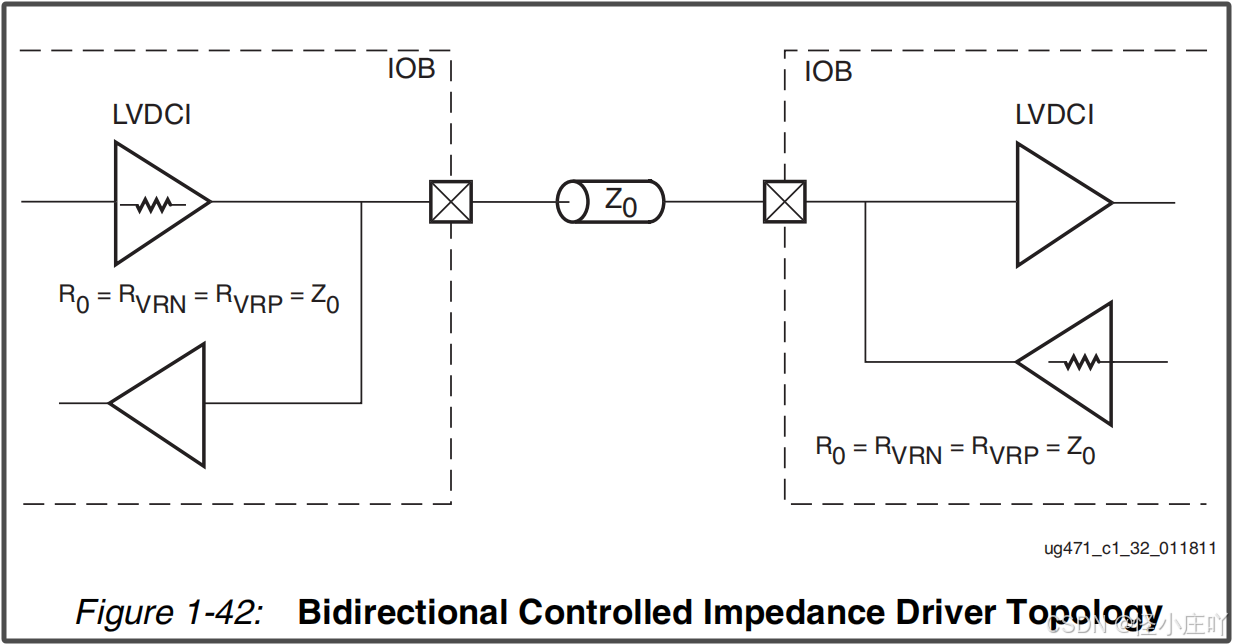

Using these I/O buffers configures the outputs as controlled impedance drivers.

LVDCI的接收器与 LVCMOS 接收器相同。某些I/O标准(如LVCMOS)必须具备与驱动线路(driven line)特性阻抗匹配的驱动阻抗。

7 系列器件的 HP I/O bank 提供了受控阻抗输出驱动器,无需外部源端接电阻,即可实现串联端接。阻抗通过外部公共参考电阻来设置,该电阻阻值等于走线特性阻抗(trace characteristic impedance),Z₀。

支持受控阻抗驱动器(controlled impedance driver)的 DCI I/O 标准包括:LVDCI_15 和 LVDCI_18。

图 1-41 和图 1-42 展示了受控阻抗驱动器的单向和双向拓扑示例电路。

3.2、LVDCI_DV2

LVDCI_DV2的意思是一半阻抗的DCI驱动器可以为驱动器提供具有参考电阻一半阻抗的特性。通过增加参考电阻的阻抗,可以降低静态功耗并改善电路性能。

具有半阻抗(源端接)的受控阻抗驱动器还能提供阻抗为参考电阻一半的驱动器。这使得参考电阻的阻值可以增大至原来的两倍,而且通过VRN/VRP降低静态功耗。

支持半阻抗可控阻抗驱动器的I/O标准有:LVDCI_DV2_15和LVDCI_DV2_18。

当使用半阻抗驱动器时,为使驱动阻抗与特性阻抗Z₀匹配,参考电阻R的阻值必须为Z₀的2倍。

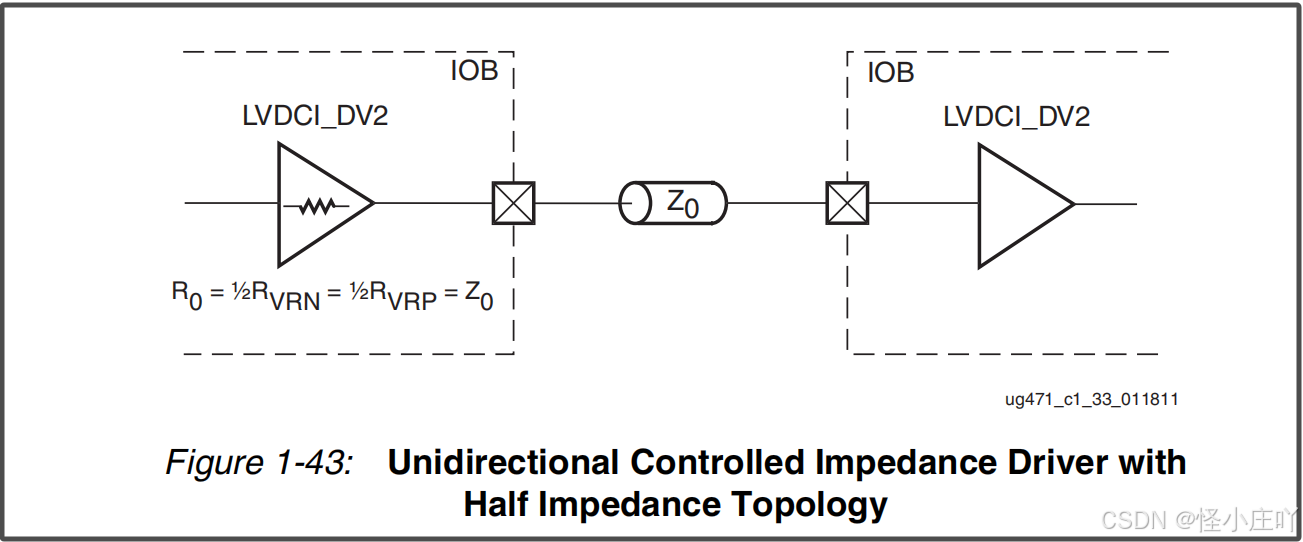

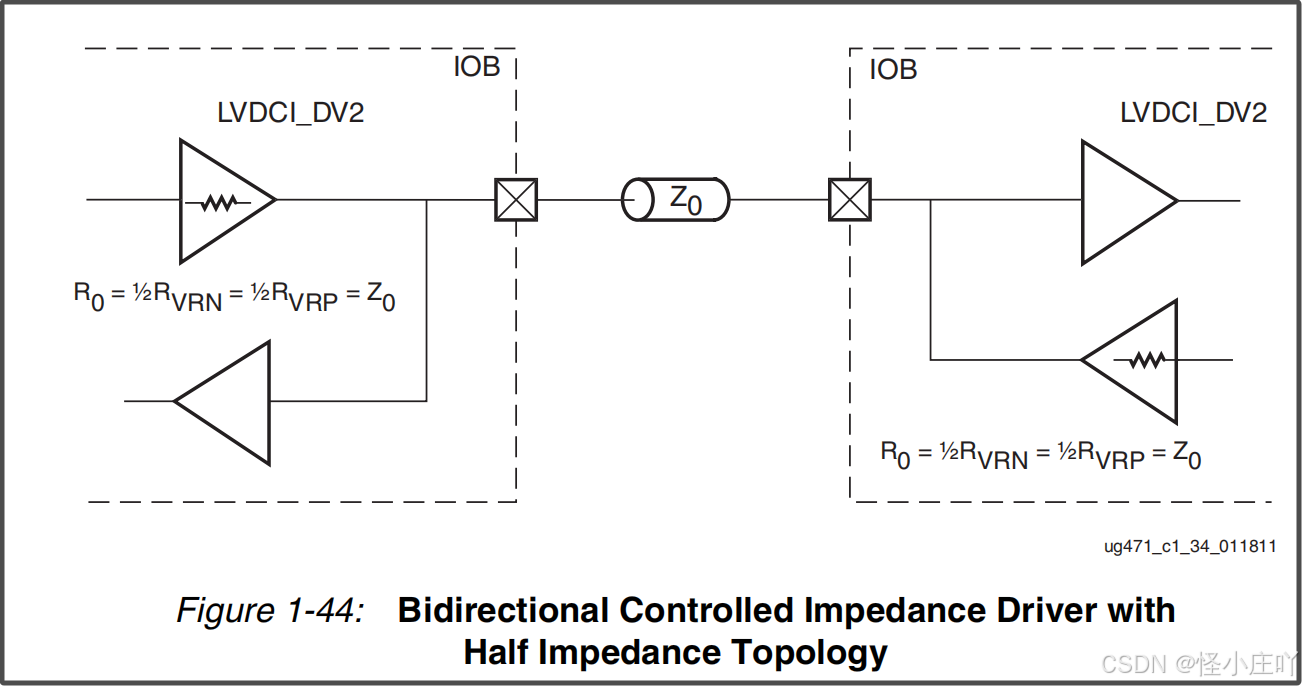

图1-43和图1-44展示了半阻抗可控驱动器的单向拓扑结构。

对于LVDCI驱动器而言,没有可选择的电流驱动强度设置。当驱动器的阻抗为VRN/VRP参考电阻阻值的一半时,会在属性名称中添加“DV2”来表示这一情况。

3.3、HSLVDCI (High-Speed LVDCI)

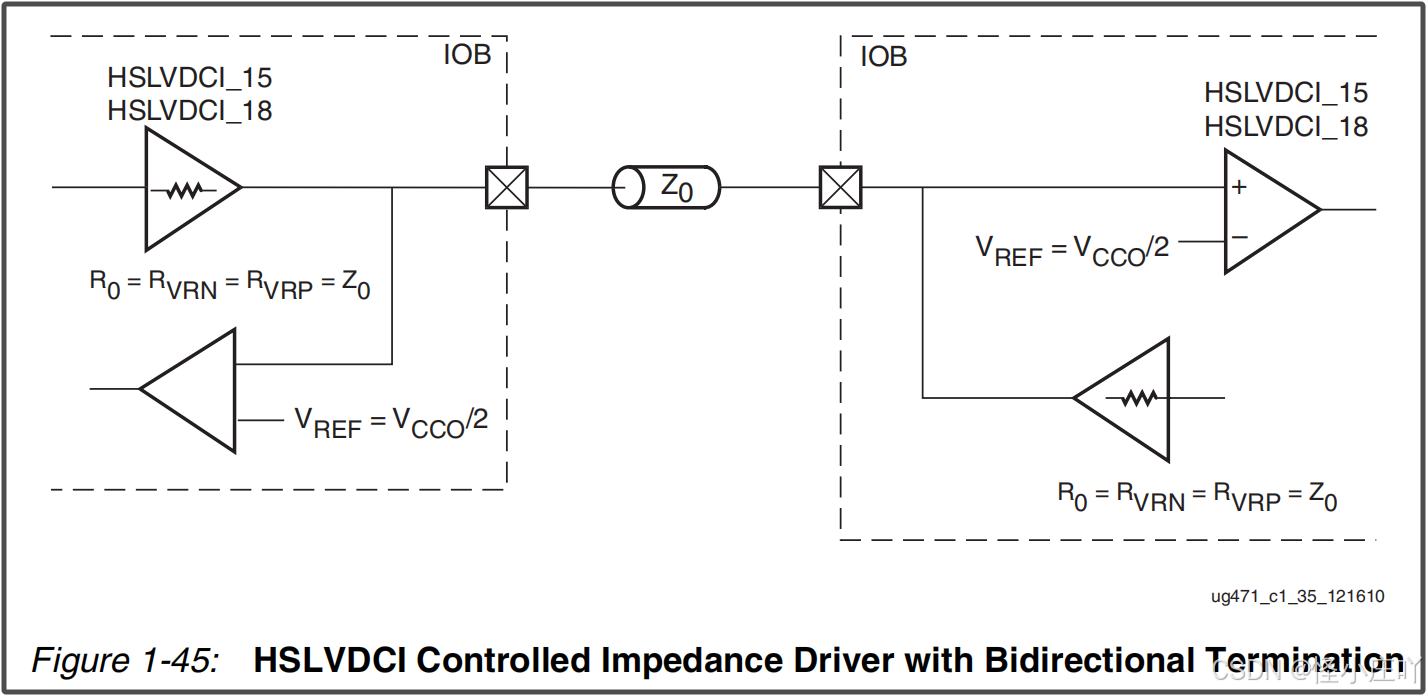

HSLVDCI标准旨在用于双向应用。

其驱动器与 LVDCI 的驱动器相同,而输入则与 HSTL和 SSTL的输入相同。

通过使用以 VREF 为参考的输入,与使用单端 LVCMOS 类型接收器相比,HSLVDCI 能让接收器具有更高的输入灵敏度。

支持采用以 VREF 为参考输入的可控阻抗驱动器的 DCI I/O 标准有:HSLVDCI_15 和 HSLVDCI_18。

图 1-45 展示了一个 HSLVDCI 受控阻抗驱动器双向端接技术的示例电路。

4、HSTL (High-Speed Transceiver Logic)

HSTL标准是遵照JESD8-6协议的通用高速总线标准。

HSTL标准有四种不同的类型:HSTL class-I、HSTL class-II、Differential HSTL Class I和Differential HSTL Class II。

其中,差分版本可支持高速存储器接口的时钟设计。

7 series FPGA I/O supports class-I for the 1.2V version of HSTL (in HP banks),and class-I and II for the 1.5V and 1.8V versions, including the differential versions. The differential versions of the standard require a differential amplifier input buffer and a push-pull output buffer. The HP I/O banks also support DCI versions.

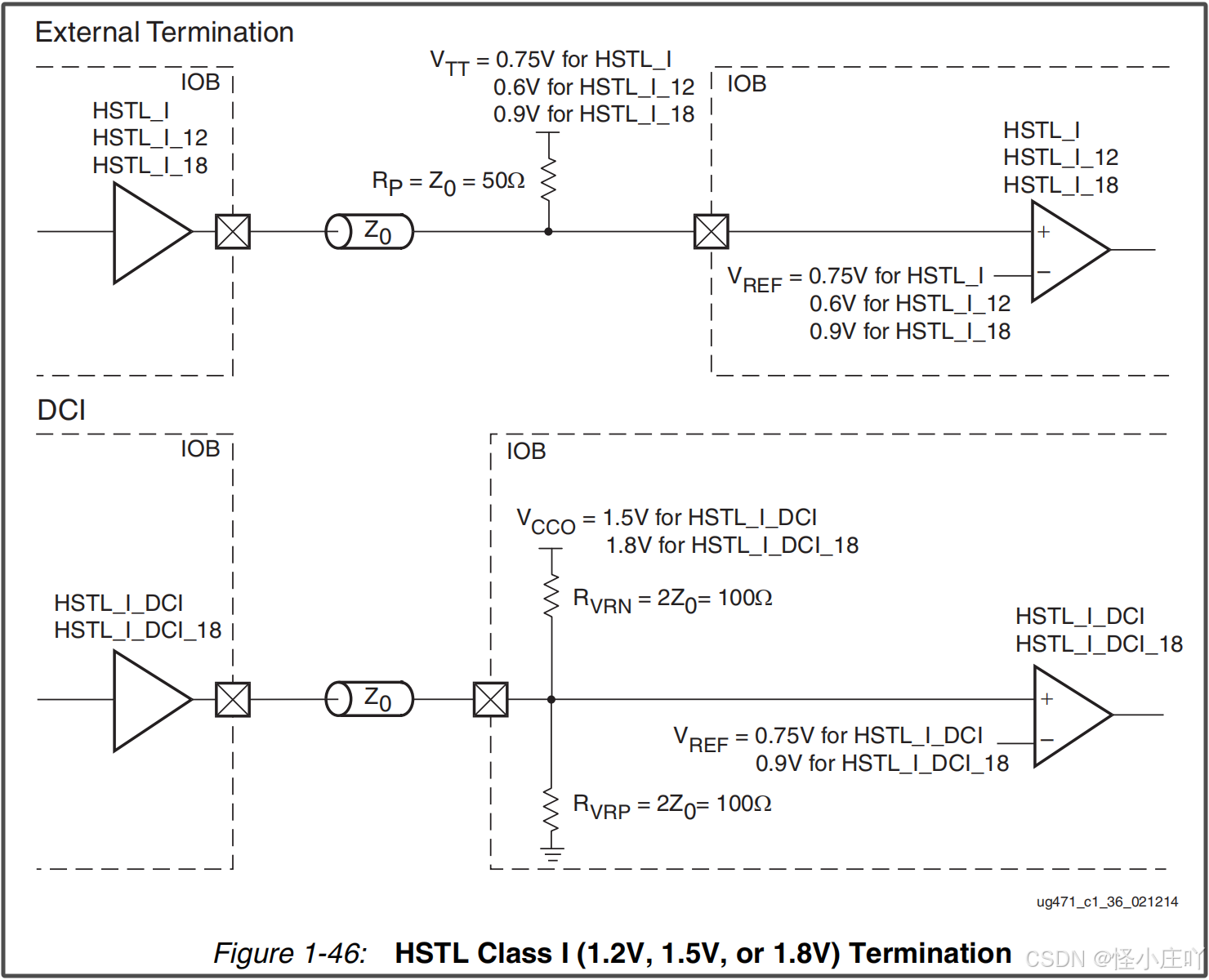

4.1、HSTL Class I(1.2V, 1.5V, or 1.8V)

- 1、HSTL_ I 和 HSTL_ I_18

HSTL_ I和HSTL_ I_18标准 在 HR I/O Bank 和 HP I/O Bank 中均可用。

HSTL_I 和 HSTL_I_18 使用电源电压VCCO的一半(VCCO/2)作为并联端接电压(VTT),专用于单向链路(unidirectional links),支持电压为1.5V/1.8V。

- 2、HSTL_I_12

HSTL_I_12标准 仅在 HP I/O Bank 中可用。

HSTL_I_12使用电源电压VCCO的一半(即VCCO/2)作为并联端接电压(VTT),用于单向链路,支持1.2V。

- 3、HSTL_ I_DCI 和 HSTL_ I_DCI_18

HSTL_ I_DCI和HSTL_ I_DCI_18标准 仅在 HP I/O Bank 中可用。

HSTL_I_DCI和HSTL_I_DCI_18提供由VCCO供电的片上分压戴维南端接,形成等效为VCCO/2的并联端接电压(VTT,VTT = VCCO/2),专用于单向链路,带有DCI支持1.5V/1.8V。

图 1-46 展示了 1.2V、1.5V 或 1.8V 版本的 HSTL Class I标准的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.2V、1.5V 或 1.8V),且不可互换。仅 HP I/O Bank 支持 DCI 标准。

4.2、HSTL Class II

- 1、HSTL_ II 和 HSTL_ II_18

HSTL_ II和HSTL_ II_18标准 在 HR I/O Bank 和 HP I/O Bank 中均可用。

HSTL_II和HSTL_II_18采用VCCO/2作为并联端接电压(VTT),专用于双向链路(bidirectional links)。

- 2、HSTL_ II_DCI 和 HSTL_ II_DCI_18

HSTL_ II_DCI 和 HSTL_ II_DCI_18标准 在 HP I/O Bank 中可用。

HSTL_II_DCI和HSTL_II_DCI_18提供由VCCO供电的片上分压戴维南端接,形成等效为VCCO/2的端接电压,专用于双向链路。

- 3、HSTL_ II_T_DCI 和 HSTL_ II_T_DCI_18

HSTL_ II_T_DCI 和 HSTL_ II_T_DCI_18标准 在 HP I/O Bank 中可用。

HSTL_ II_T_DCI 和 HSTL_ II_T_DCI_18提供由VCCO供电的片上分压戴维南端接。当驱动器处于三态时,会在接收器端形成等效为VCCO/2的端接电压。当驱动器不处于三态时,这两种标准不进行端接。

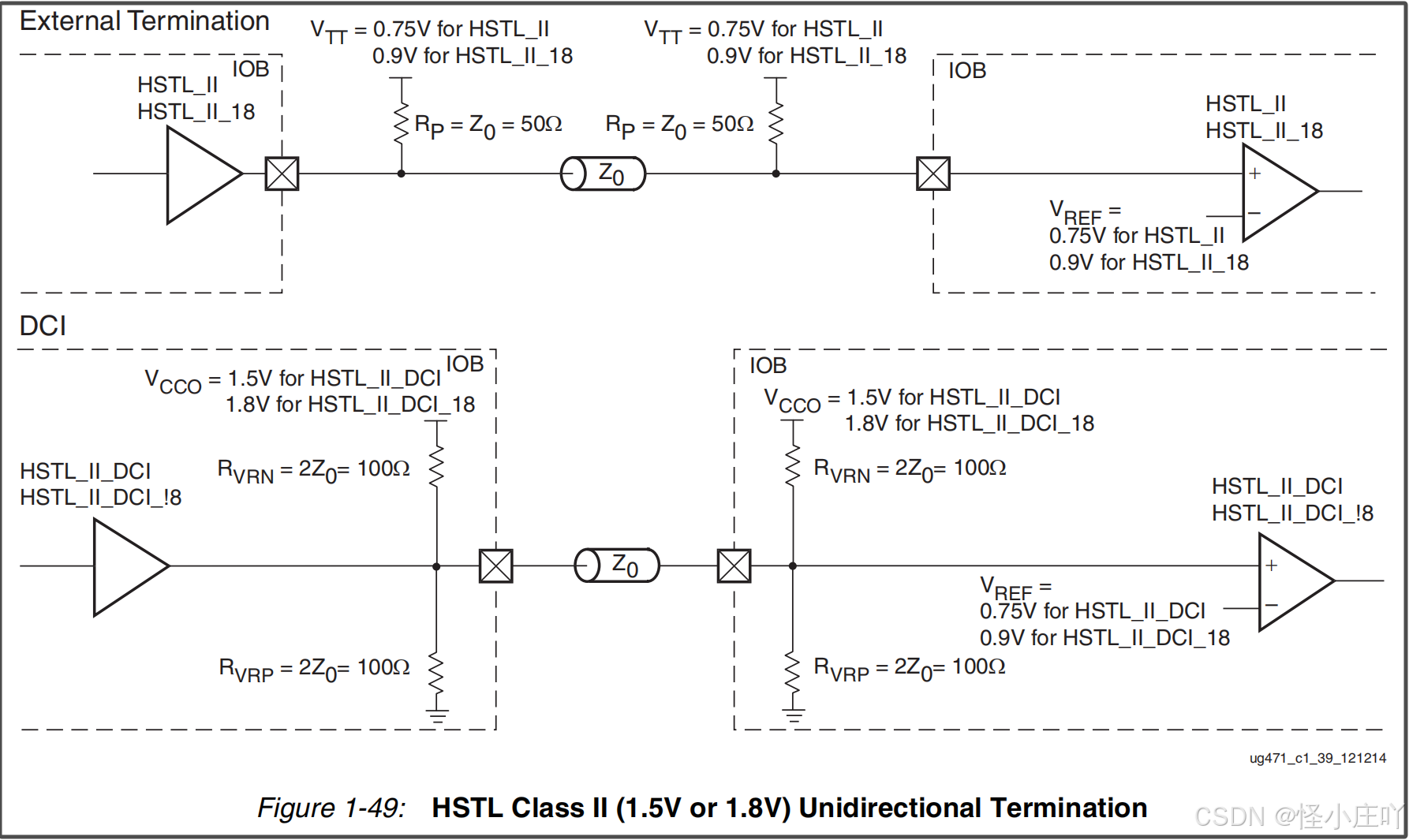

图 1-49 展示了适用于 HSTL Class II 类(1.5V 或 1.8V)的单向端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。HP I/O Bank 支持 DCI 标准。内部分压端接电阻始终存在,与驱动器是否处于三态无关。

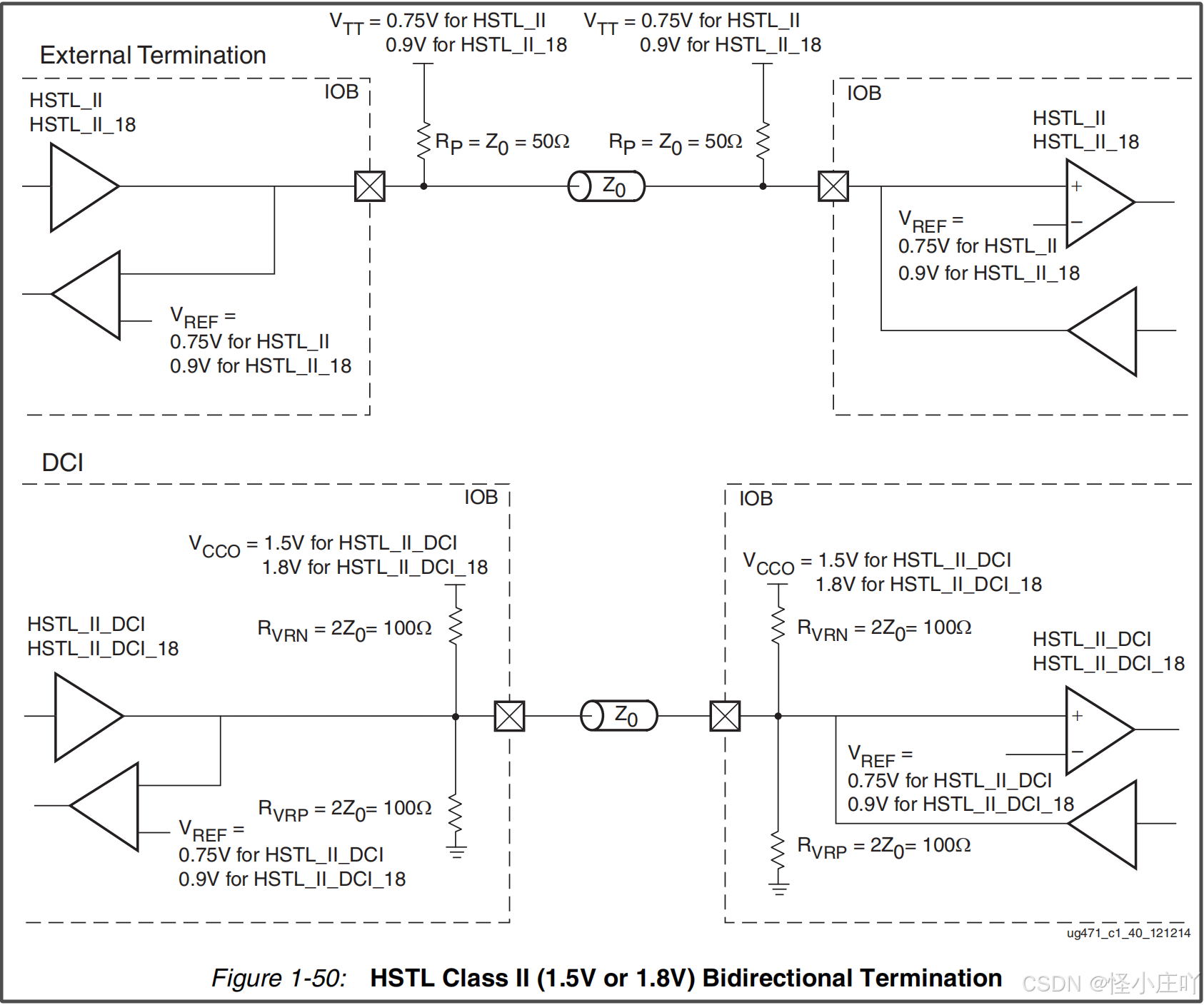

图 1-50 展示了适用于 HSTL II 类(1.5V 或 1.8V)的双向端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。HP I/O Bank 支持 DCI 标准。内部分压端接电阻始终存在,与驱动器是否处于三态无关。

- 4、HSTL_II_T_DCI (1.5V or 1.8V) Split-Thevenin Termination (3-state)

- 4、HSTL_II_T_DCI (1.5V or 1.8V) Split-Thevenin Termination (3-state)

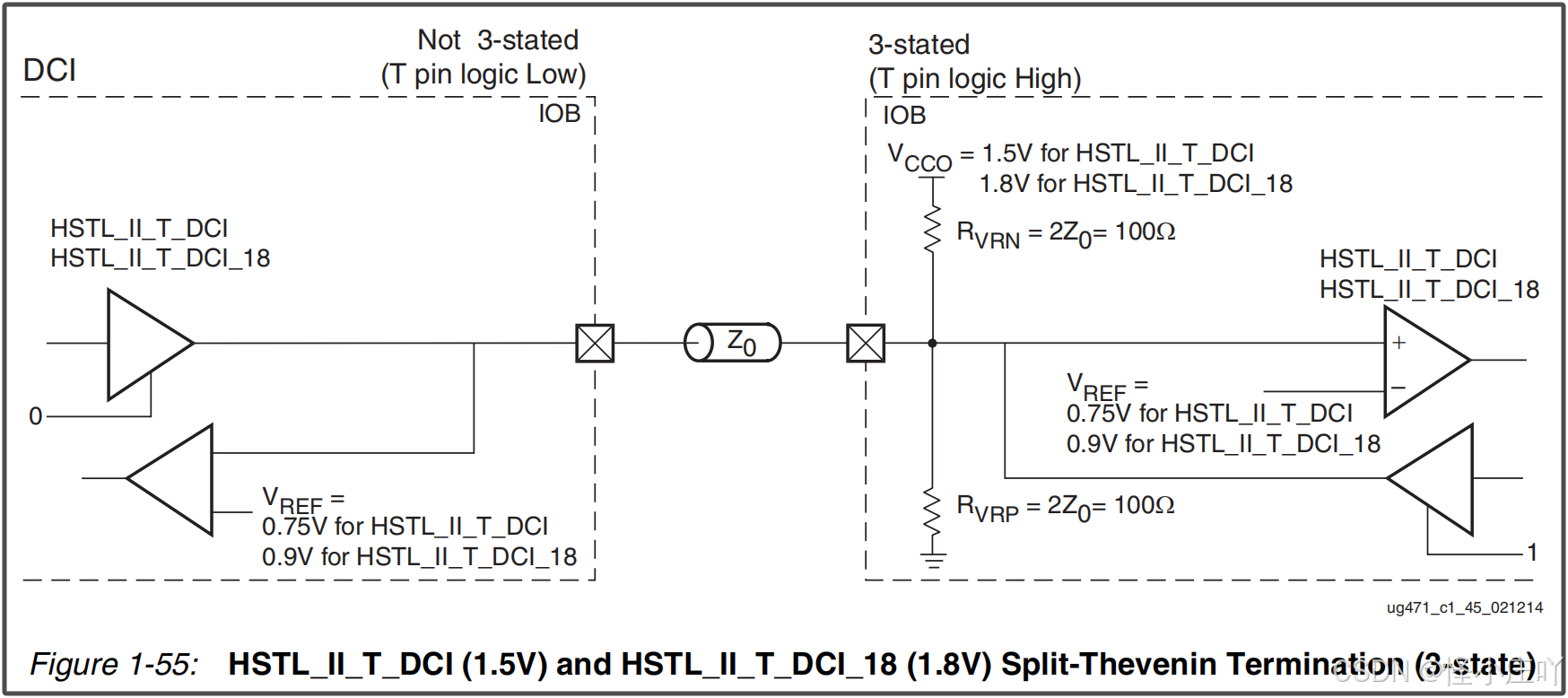

图1-55,展示了HSTL_II_T_DCI(1.5V )和HSTL_II_T_DCI_18(1.8V )的片上分压戴维南端接技术。在这种双向场景中,当处于三态时,端接在接收器端启用,而不在驱动器端启用。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V或1.8V),且不可互换。仅 HP I/O Bank 支持T_DCI标准。内部分压端接电阻仅在输出缓冲器处于三态时存在。

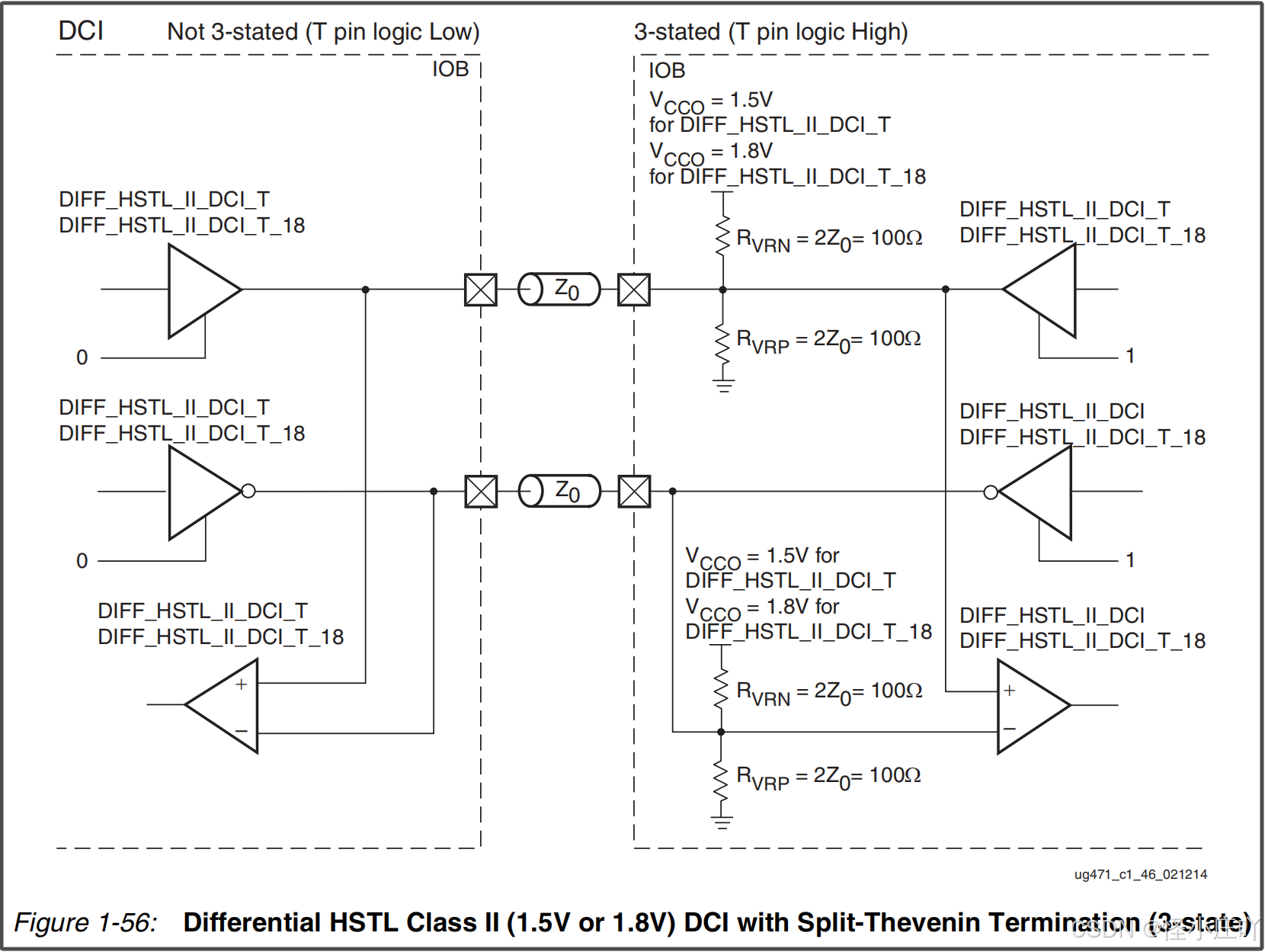

图1-56展示了采用片上分压戴维南端接的差分HSTL II类(1.5V或1.8V)端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V或1.8V),且不可互换。仅 HP I/O Bank 支持T_DCI标准。内部分压端接电阻仅在输出缓冲器处于三态时存在。

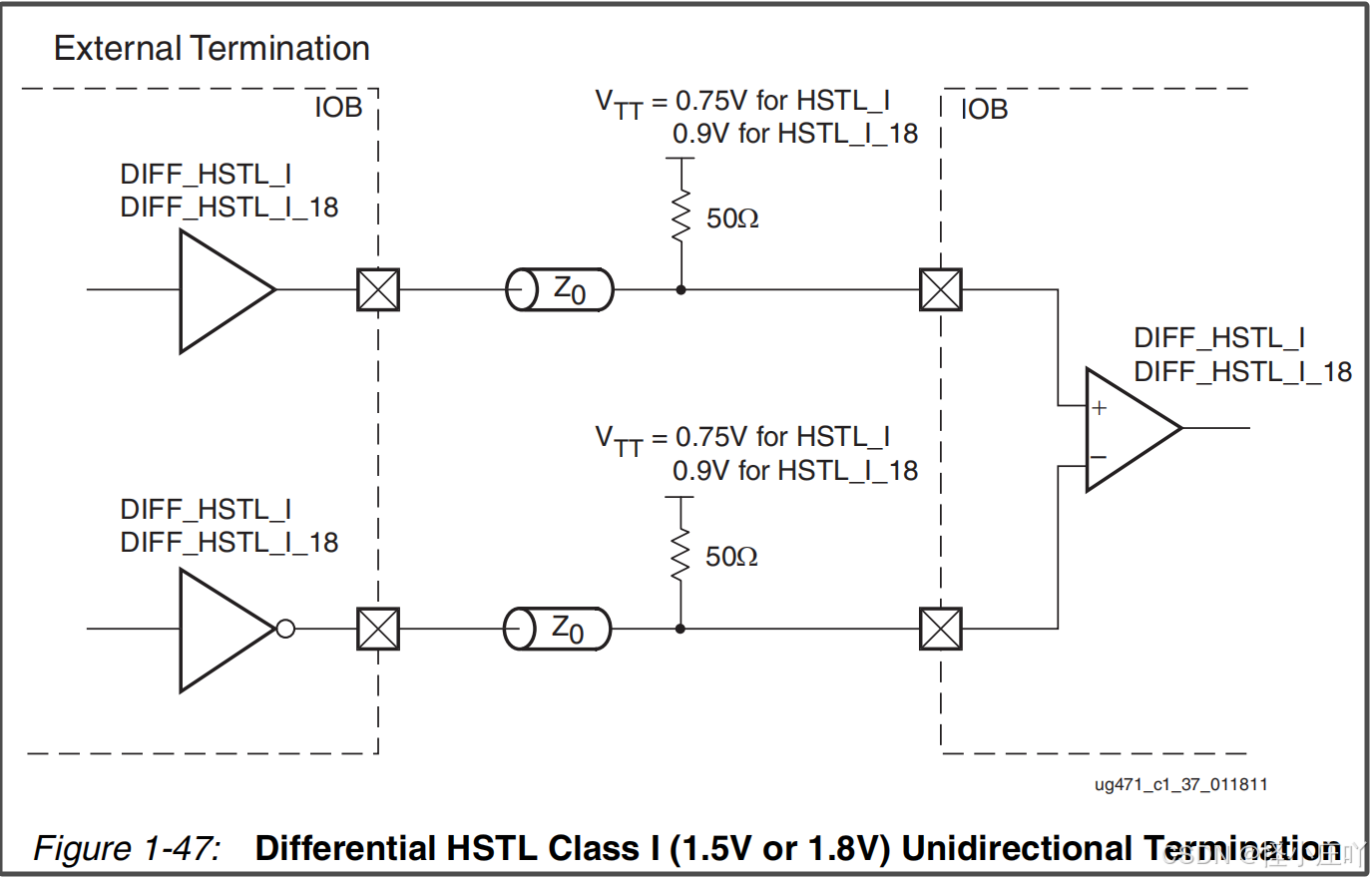

4.3、Differential HSTL Class I

- 1、DIFF_HSTL_I 和 DIFF_HSTL_I_18

DIFF_HSTL_I 和 DIFF_HSTL_I_18标准 在 HR I/O Bank 和 HP I/O Bank 中均可用。

差分HSTL Class-I将互补单端HSTL_I型驱动器与差分接收器配对,专用于单向通信链路。

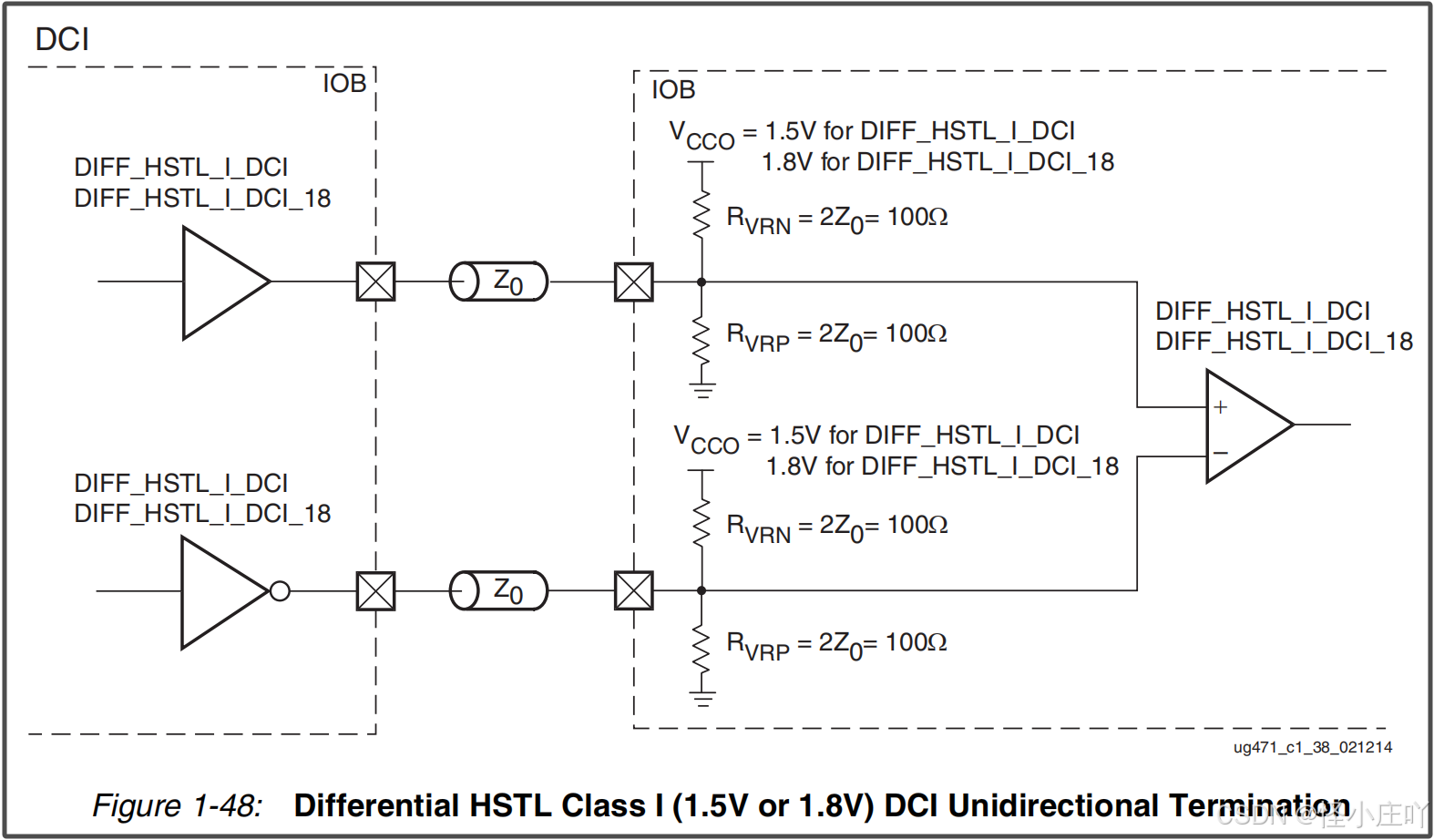

- 2、DIFF_HSTL_I_DCI 和 DIFF_HSTL_I_DCI_18

DIFF_HSTL_I_DCI 和 DIFF_HSTL_I_DCI_18标准 在 HP I/O Bank 中可用。

差分HSTL Class-I将互补单端HSTL_I型驱动器与差分接收器配对,包含片上分压式戴维南端接,专用于单向通信链路

图 1-47 展示了具有单向端接的差分 HSTL I 类(1.5V 或 1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。

图1-48展示了一个示例电路,说明了具有单向DCI端接的差分HSTL I类(1.5V或1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V或1.8V),且不可互换。仅HP I/O bank支持这些DCI标准。

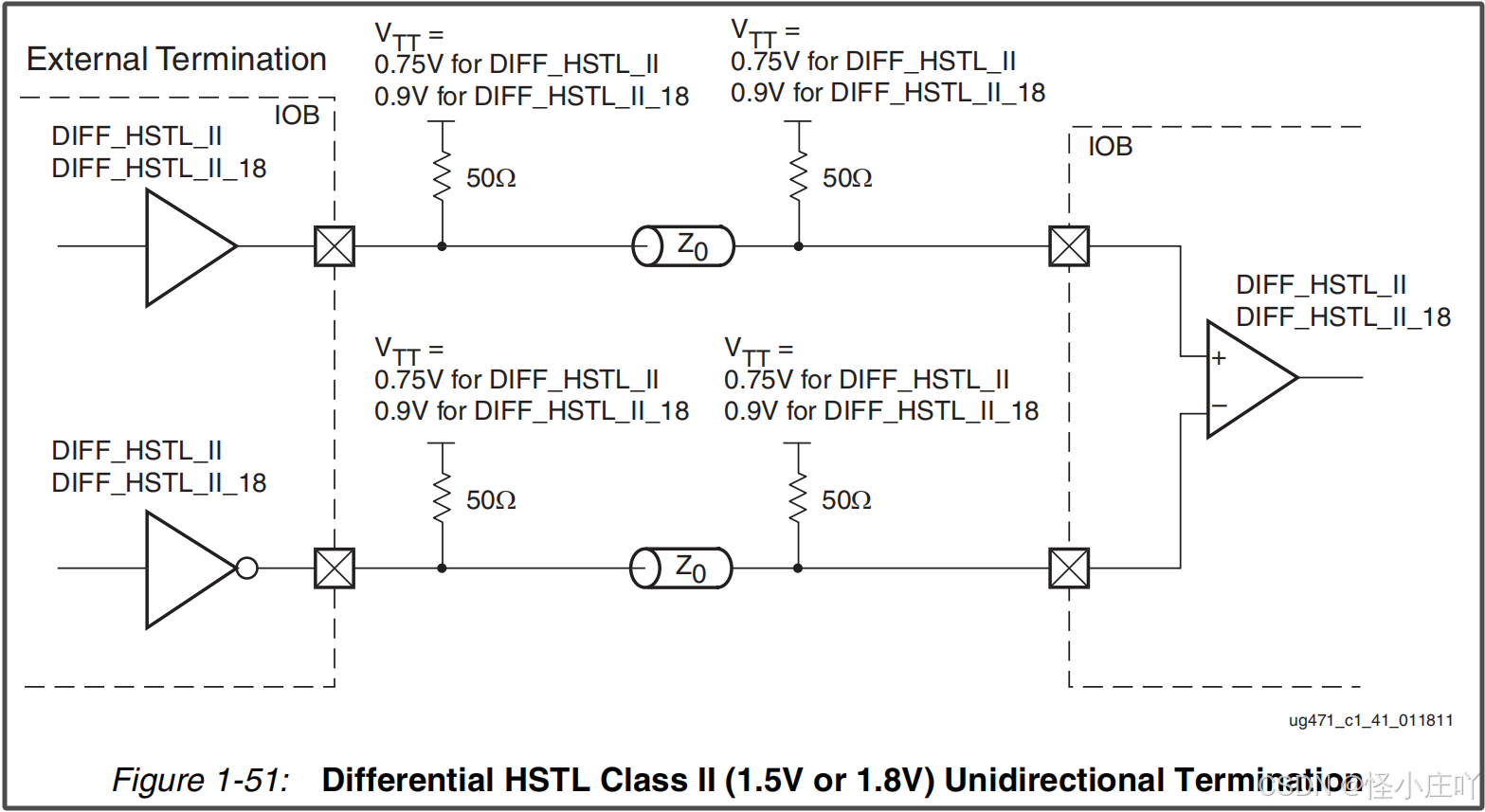

4.4、Differential HSTL Class II

- 1、DIFF_HSTL_ II 和 DIFF_HSTL_II_18

DIFF_HSTL_ II 和 DIFF_HSTL_II_18标准 在 HR I/O Bank 和 HP I/O Bank 中均可用。

差分HSTL Class-II将互补单端HSTL_II型驱动器与差分接收器配对。该标准适用于双向链路,也可用于存储器接口设计中的差分时钟和 DQS(数据选通)信号。

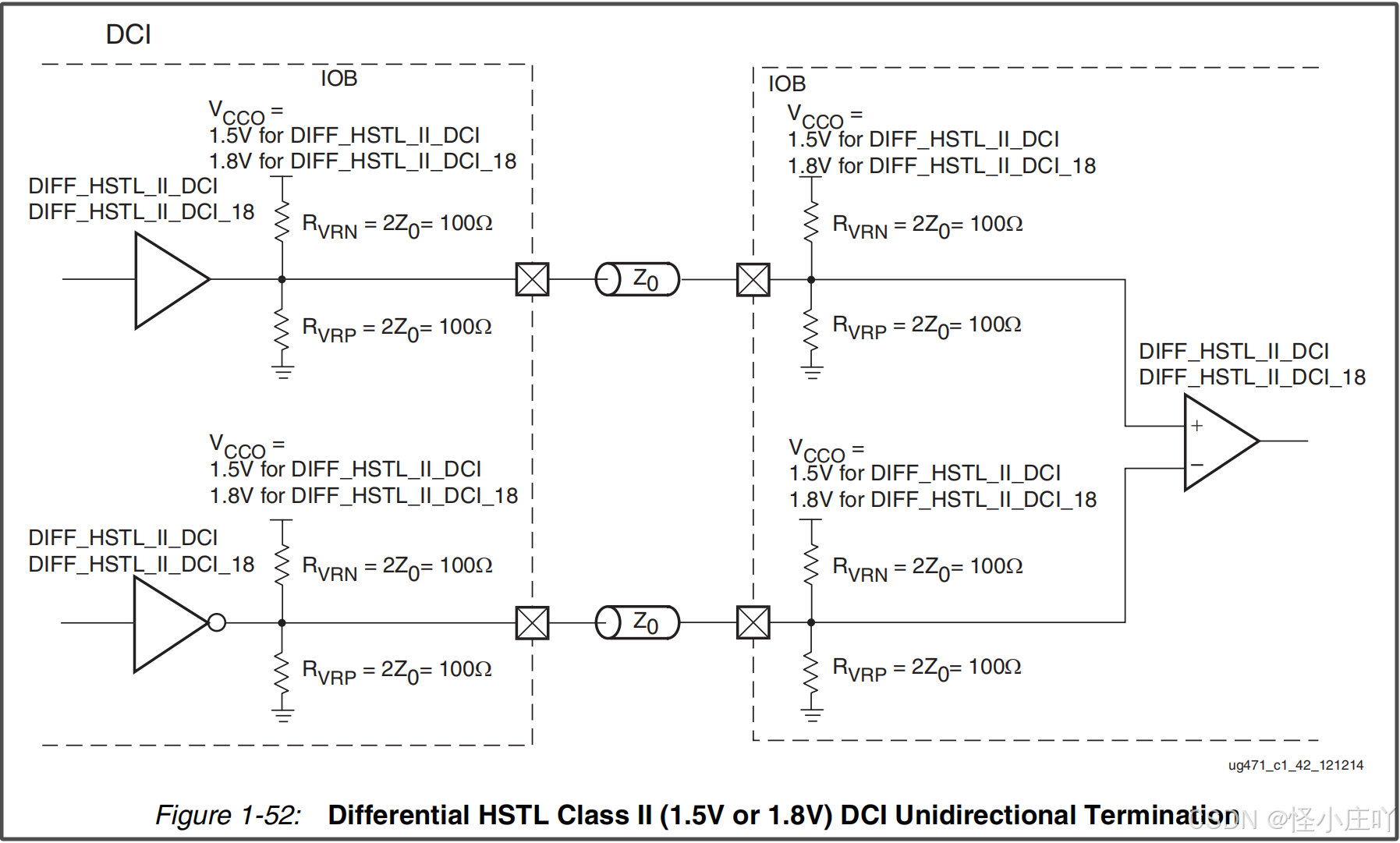

- 2、DIFF_HSTL_II_DCI 和 DIFF_HSTL_II_DCI_18

该DIFF_HSTL_II_DCI 和 DIFF_HSTL_II_DCI_18标准 仅在 HP I/O Bank 中可用。

差分HSTL Class-II将互补单端HSTL_II型驱动器与差分接收器配对,包括片上分压戴维南端接,专用于双向链路,同时支持存储器接口设计中的差分时钟和 DQS(数据选通)信号。

- 3、DIFF_HSTL_II_T_DCI 和 DIFF_HSTL_II_T_DCI_18

该DIFF_HSTL_II_T_DCI 和 DIFF_HSTL_II_T_DCI_18标准 仅在 HP I/O Bank 中可用。

此类标准与DIFF_HSTL_II_DCI及DIFF_HSTL_II_DCI_18标准几乎完全相同,区别仅在于端接仅在驱动器处于三态时存在。

图 1-51 展示了具有单向端接的差分 HSTL II 类(1.5V 或 1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。

图 1-52 展示了具有单向 DCI 端接的差分 HSTL II 类(1.5V 或 1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。仅 HP I/O Bank 支持 DCI 标准。内部分压端接电阻始终存在,与驱动器是否处于三态无关。

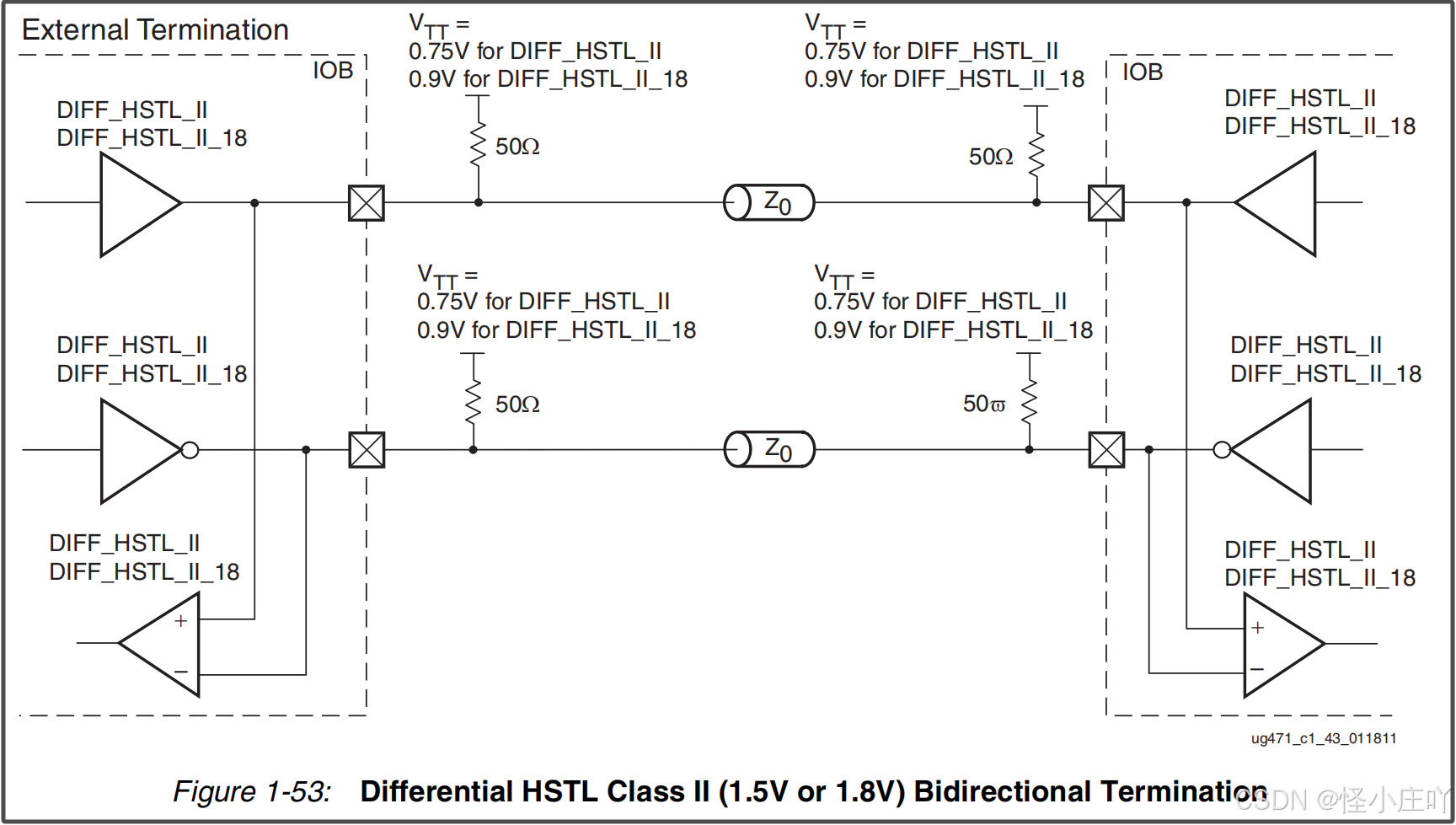

图 1-53 展示了具有双向端接的差分 HSTL II 类(1.5V 或 1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。

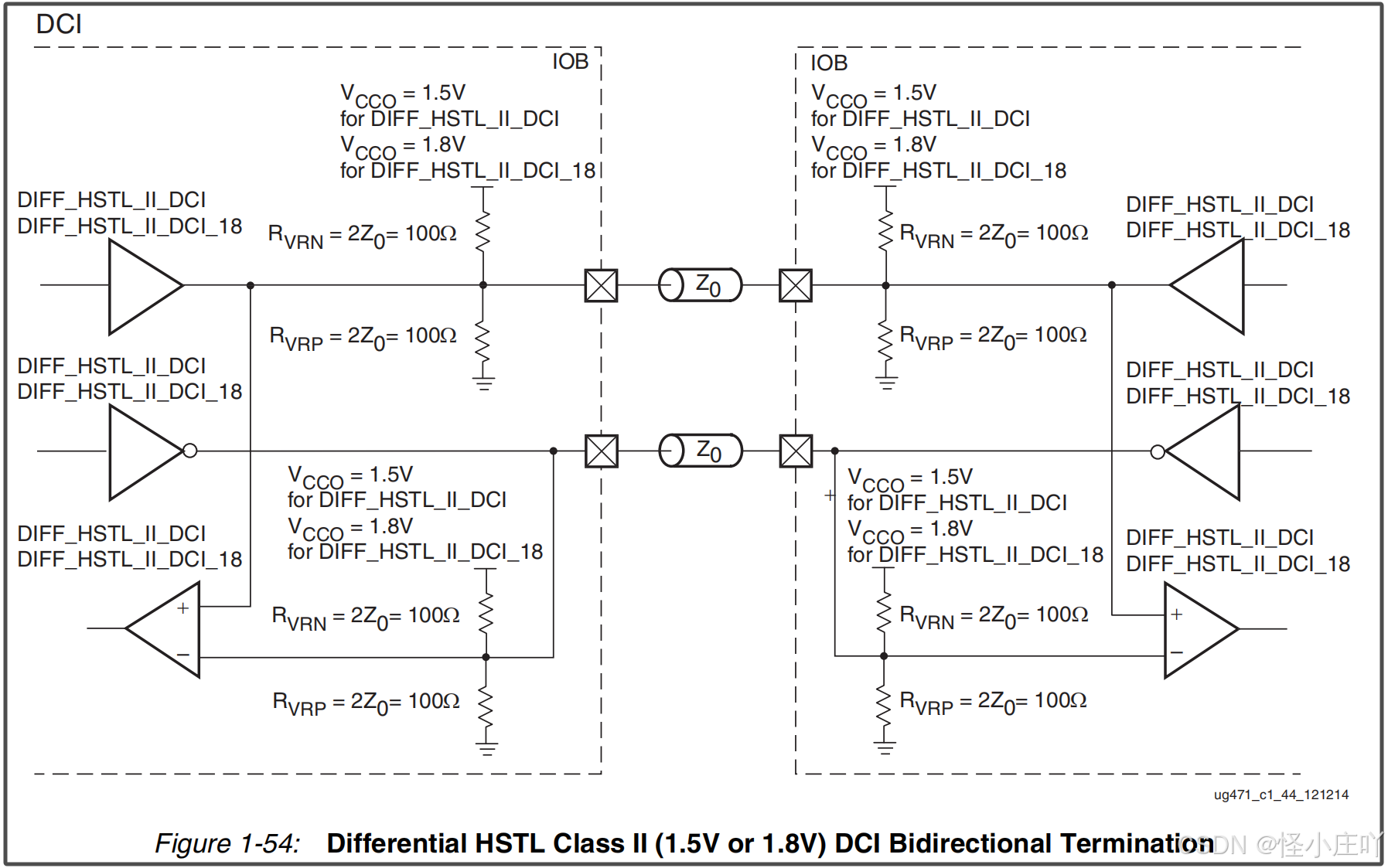

图 1-54 展示了具有双向 DCI 端接的差分 HSTL II 类(1.5V 或 1.8V)的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.5V 或 1.8V),且不可互换。仅 HP I/O Bank 支持 DCI 标准。内部分压端接电阻始终存在,与驱动器是否处于三态无关。

5、SSTL (Stub-Series Terminated Logic)

The Stub-Series Terminated Logic (SSTL) for 1.8V (SSTL18), 1.5V (SSTL15), and 1.35V (SSTL135) are I/O standards used for general purpose memory buses.

SSTL标准同时支持单端(single-ended signaling)和差分(differential signaling)标准。差分版本采用真差分放大器输入缓冲器(true differential amplifier input buffer)和互补推挽输出缓冲器(complementary push-pull output buffers)。

The 3-state DCI (T_DCI) versions of these standards are the preferred I/O standards to use for memory interfaces implemented in the HP I/O banks.

5.1、SSTL18、SSTL15、SSTL135、SSTL12

SSTL18 用于DDR2 SDRAM存储器接口,由 JEDEC标准中的JESD8-15定义。

SSTL15 用于DDR3 SDRAM存储器接口,由 JEDEC标准中的JESD79-3E定义(未明确命名,有大致定义)。

SSTL135 用于 DDR3L SDRAM 内存接口,由 JEDEC标准中的JESD79-3-1定义(未明确命名,有大致定义)。

SSTL12 支持美光(Micron)的下一代 RLDRAM3 内存。

SSTL18 class-I 和 SSTL18 class-II 在 HR I/O Bank 和 HP I/O Bank 中均可用。

对于SSTL15,full-strength driver(SSTL15)在 HR I/O Bank 和 HP I/O Bank 中均可用;reduced-strength driver ( SSTL15_R )仅在 HR I/O Bank 中均可用。

对于SSTL135,full-strength driver(SSTL135)在 HR I/O Bank 和 HP I/O Bank 中均可用;reduced-strength driver( SSTL135_R )仅在 HR I/O Bank 中均可用。

SSTL12仅在 HP I/O Bank 中可用。

SSTL18 Class I 驱动器仅适用于单向拓扑(不支持双向),SSTL18 Class II 驱动器则可同时用于双向和单向信号传输。

SSTL15 和 SSTL15_R 驱动器均支持双向和单向信号传输。

SSTL135 和 SSTL135_R 驱动器都支持双向和单向信号传输。

对于某些拓扑结构中(如短距离点对点接口):

SSTL18 Class I 驱动器可减少过冲,提升信号完整性。

SSTL15_R 驱动器可减少过冲,改善信号完整性。

SSTL135_R 驱动器可以减少过冲并提高信号完整性。

对于SSTL18 Class I、SSTL15_R、SSTL135_R、SSTL12 :

1、HP Bank 提供DCI和T_DCI选项,用于调谐内部并联分段终端电阻(tuned internal parallel split-termination resistors)。其中,SSTL18 Class I、SSTL15_R、SSTL135_R ,T_DCI选项 仅适用于双向信号(不适用 input-only 或 output-only );SSTL135_R ,DCI 选项不适用于双向信号(适用于input 或 output only);SSTL12 ,DCI 选项不适用于双向信号(仅适用于单向输入或输出),而 T_DCI 选项仅适用于双向信号(不适用于 input-only 或 output-only )。

2、HR Bank 为未调谐内部并联分压端接电阻(untuned internal parallel split-termination resistors)提供IN_TERM选项。

尽管任何新设计的最佳驱动和端接方案均需通过细致的信号完整性分析才能确定,但初始考虑因素包括:

1、HP I/O bank:在7系列FPGA的双向引脚(DQ和DQS)上使用SSTL18_II_T_DCI / SSTL15_T_DCI / SSTL135_T_DCI / SSTL12_T_DCI,在单向引脚(所有其他引脚)上使用SSTL18_II / SSTL15 / SSTL135 / SSTL12。双向信号在存储器件端使用 on-die termination(ODT),单向信号采用外部并联端接电阻至VTT=VCCO/2。 对于SSTL12,若双向信号在存储设备端支持ODT,则使用 ODT;若不支持 ODT,则使用连接外部并联端接电阻到 VTT = VCCO/2 。

2、HR I/O bank:7系列FPGA引脚的双向信号(DQ/DQS)和单向信号(所有其他引脚)均采用SSTL18_II / SSTL15 / SSTL12,并在双向引脚上结合IN_TERM(内部端接)属性。双向信号在存储器件端使用ODT,单向信号采用外部并联端接电阻至VTT=VCCO/2。

5.2、SSTL18, SSTL15, SSTL135, SSTL12

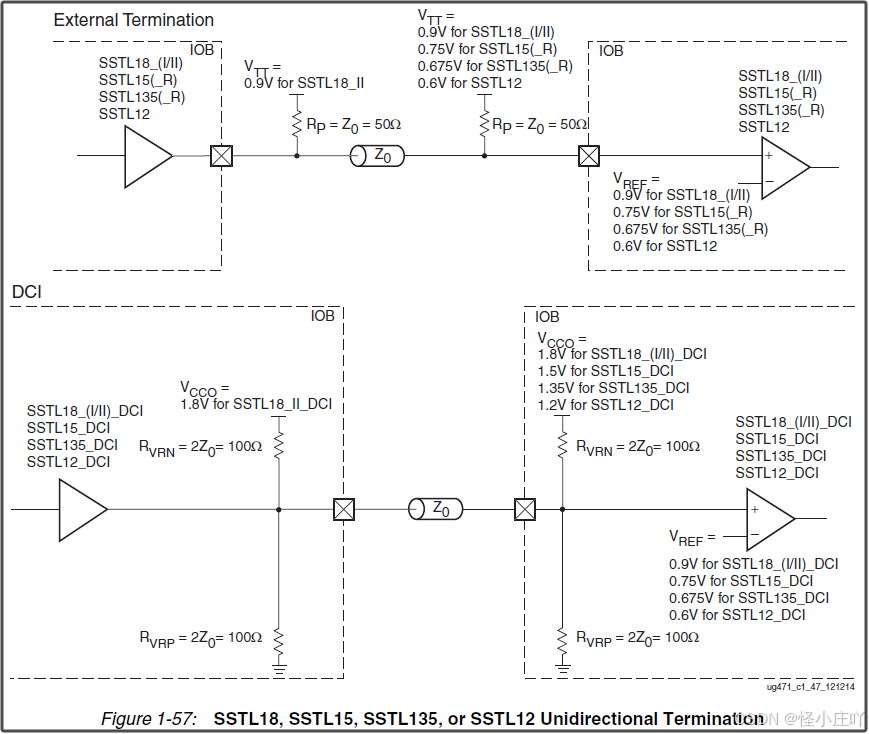

图1-57,展示了一个用于SSTL18、SSTL15、SSTL135或SSTL12的单向端接示例电路。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.8V、1.5V、1.35V或1.2V),且不可互换。图1-57还显示,SSTL18_II_DCI 仅在输出引脚上存在内部分压端接电阻。

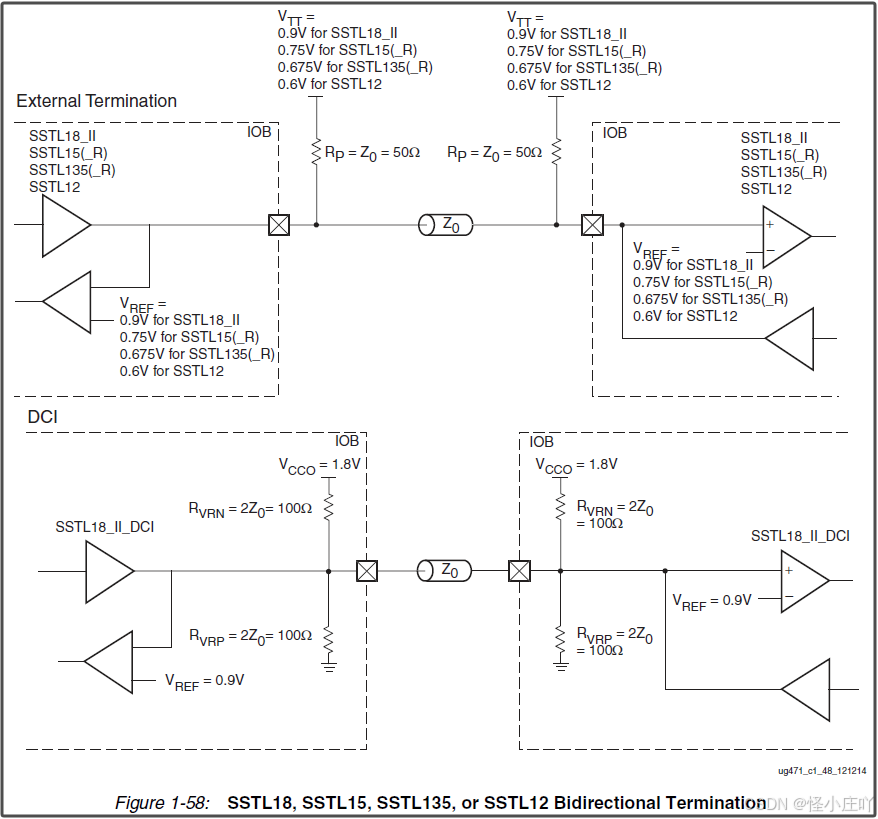

图 1-58 展示了用于 SSTL18、SSTL15、SSTL135 或 SSTL12 的双向端接示例。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.8V、1.5V、1.35V 或 1.2V),且不可互换。SSTL18 Class I 标准不支持双向信号,此外,SSTL18_II_DCI 是唯一支持双向信号的 DCI 标准。SSTL18_I、SSTL15、SSTL135 和 SSTL12 的 DCI 版本仅适用于单向信号。对于需要 DCI 端接的 SSTL15、SSTL135 和 SSTL12 双向信号,需使用 T_DCI 标准。SSTL18_II_DCI 的内部分压端接电阻始终存在,无论驱动器是否处于三态。

5.3、Differential SSTL18, SSTL15, SSTL135, SSTL12

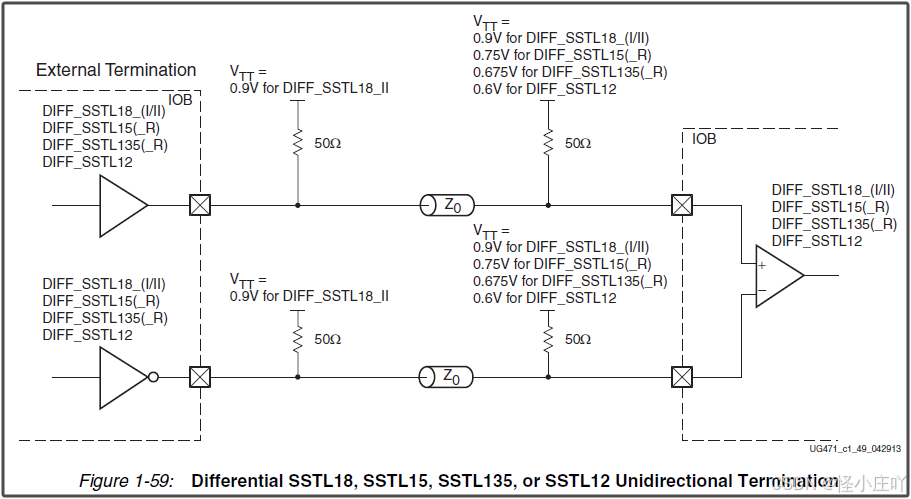

图1-59 展示了单向端接的差分SSTL18、SSTL15、SSTL135或SSTL12的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.8V、1.5V、1.35V或1.2V),且不可互换。

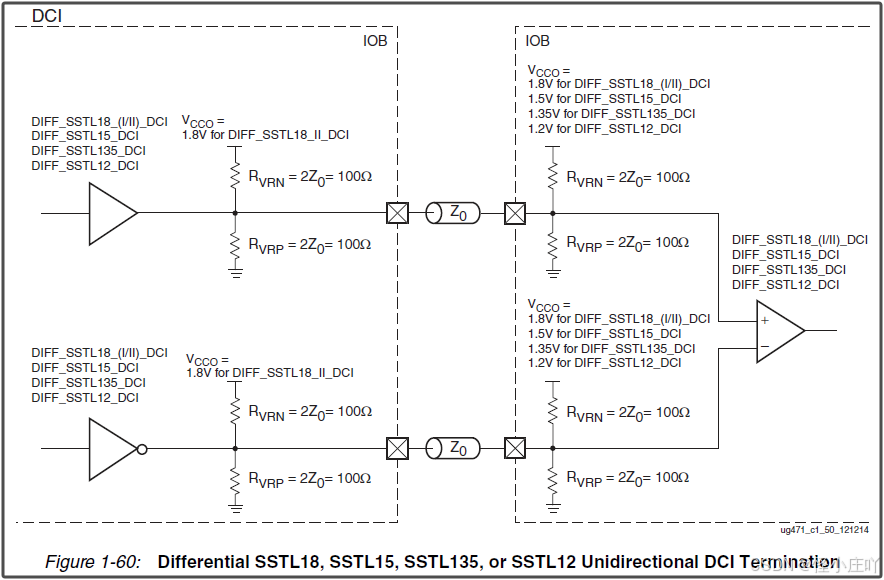

图1-60 展示了单向DCI端接的差分SSTL18、SSTL15、SSTL135或SSTL12的端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.8V、1.5V、1.35V或1.2V),且不可互换。且SSTL18_II_DCI仅在输出引脚上时存在内部分压端接电阻。

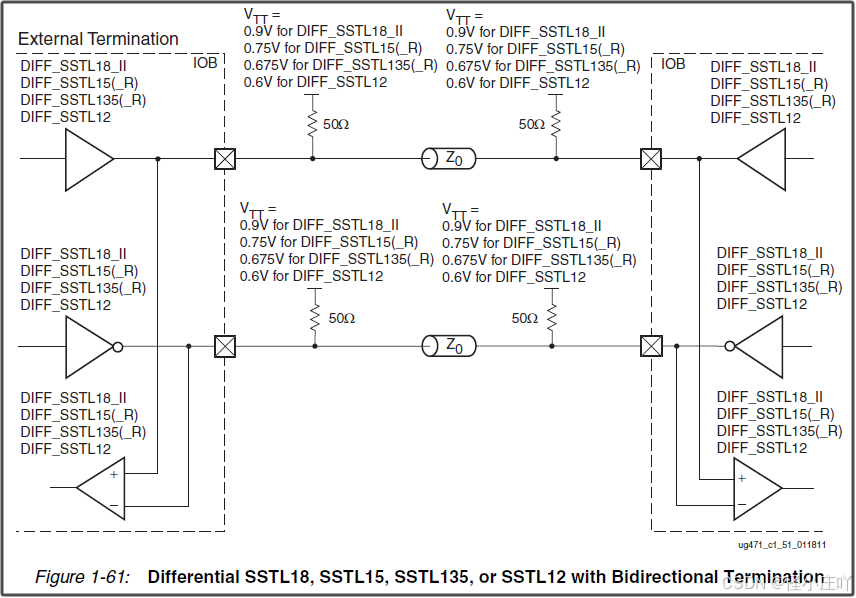

图1-61,展示了差分SSTL18、SSTL15、SSTL135或SSTL12的双向端接技术。在具体电路中,所有驱动器和接收器必须处于相同的电压电平(1.8V、1.5V、1.35V或1.2V),且不可互换。Differential SSTL18 class-I 标准不支持双向应用。

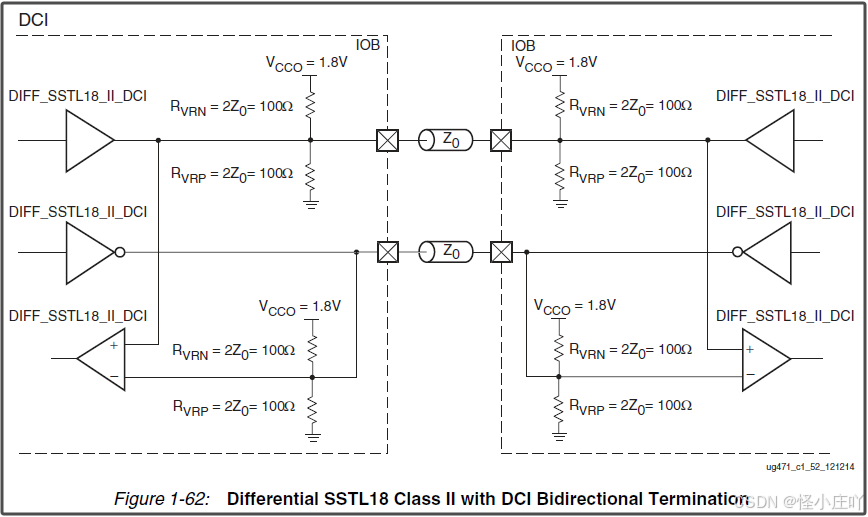

图1-62,展示了差分SSTL18采用双向DCI端接的端接技术。DIFF_SSTL18_II_DCI是唯一支持双向信号的DCI标准。DIFF_SSTL18_I、DIFF_SSTL15、DIFF_SSTL135 和 DIFF_SSTL12的DCI版本仅适用于单向信号。对于需要DCI端接的DIFF_SSTL15、DIFF_SSTL135 和 DIFF_SSTL12双向信号,需使用T_DCI标准。

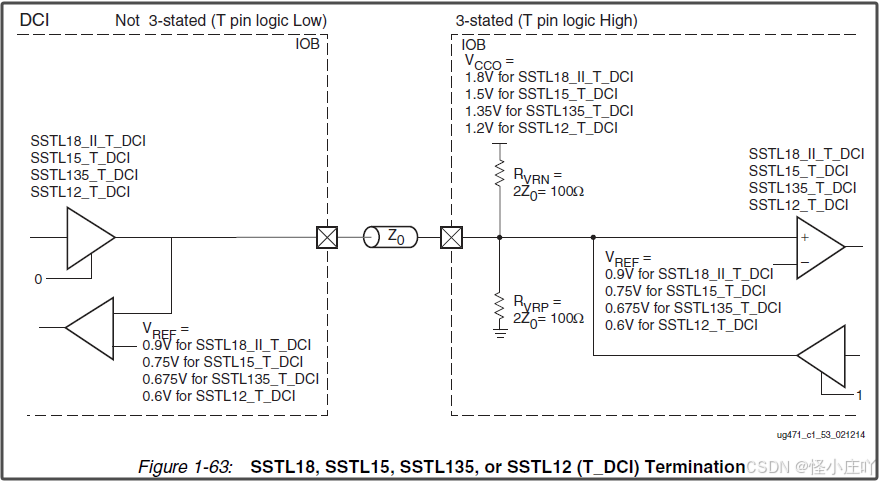

5.4、SSTL18, SSTL15, SSTL135, or SSTL12 (T_DCI) Termination

图1-63展示了片上分压戴维南端接的SSTL18、SSTL15、SSTL135或SSTL12(T_DCI)端接技术。在此双向I/O标准中,当处于三态时,内部分压端接在接收器上启用,而不是在驱动器上。

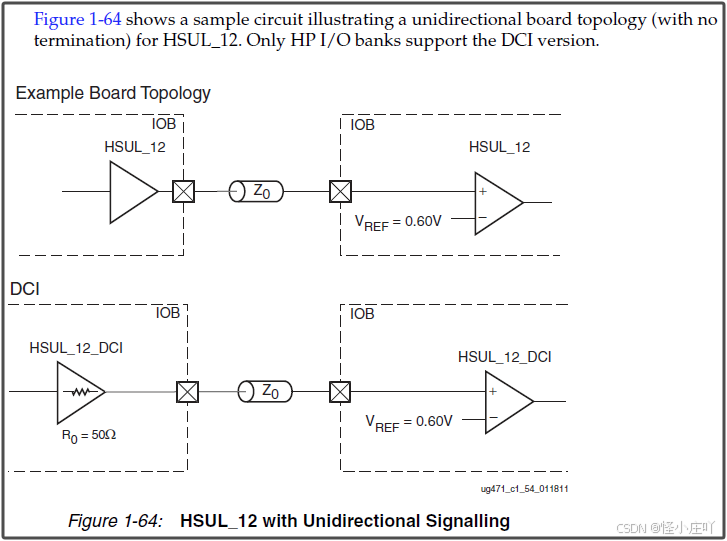

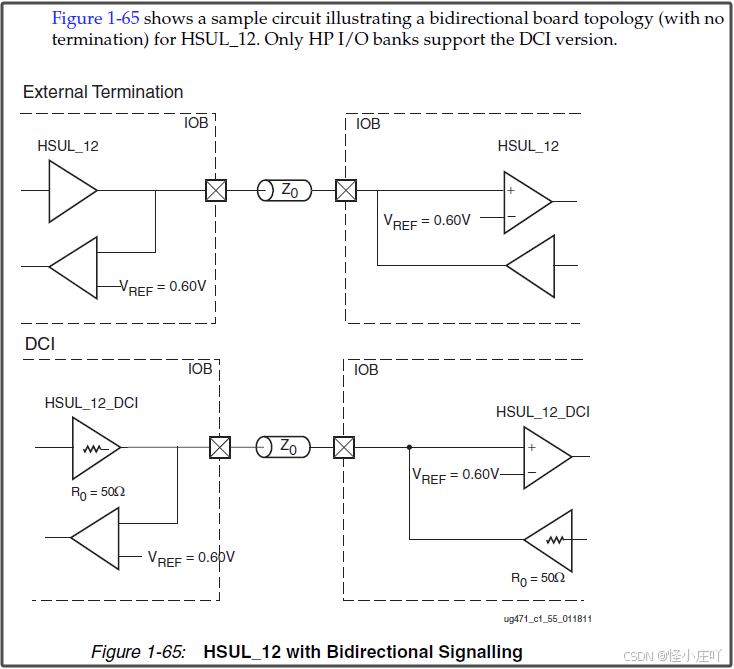

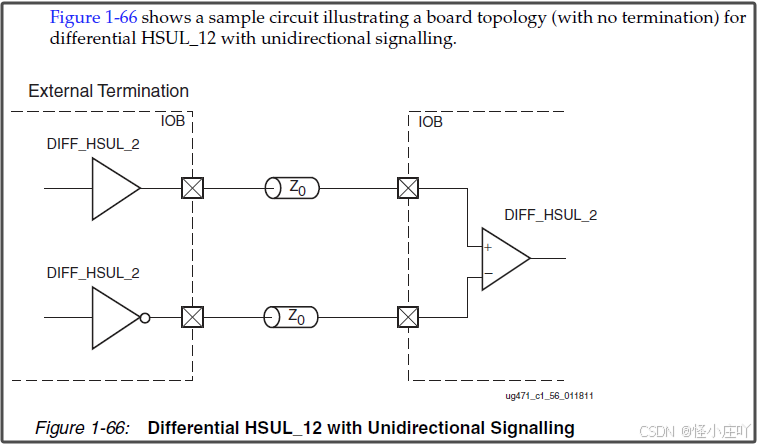

6、HSUL_12 (High Speed Unterminated Logic)

HSUL_12 标准适用于 LPDDR2 内存总线,由 JEDEC 标准中的 JESD8-22 定义。7 系列 FPGA 支持该标准的单端信号和差分信号。与 SSTL 类似,该标准还需要差分放大器输入缓冲器和推挽输出缓冲器。

**HSUL_12 和 DIFF_HSUL_12 在 HR I/O Bank 和 HP I/O Bank 中均可用 **

**HSUL_DCI_12 和 DIFF_HSUL_12_DCI 仅在 HP I/O Bank 中均可用 **

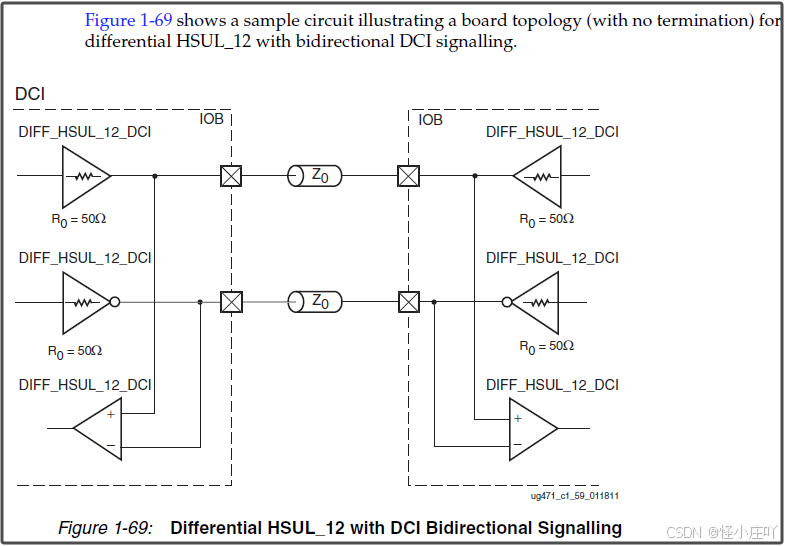

DCI 提供了一种调谐输出阻抗驱动器,可将输出阻抗与 VRP 和 VRN 引脚上的参考电阻相匹配。驱动器和接收器均不配备分压端接电阻。差分(DIFF_)版本在输出端使用互补单端驱动器,在输入端使用差分接收器。

6.1、HSUL_12

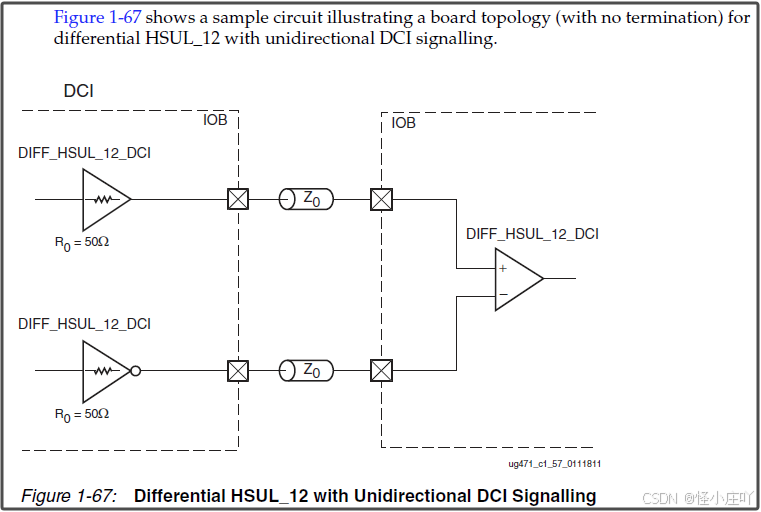

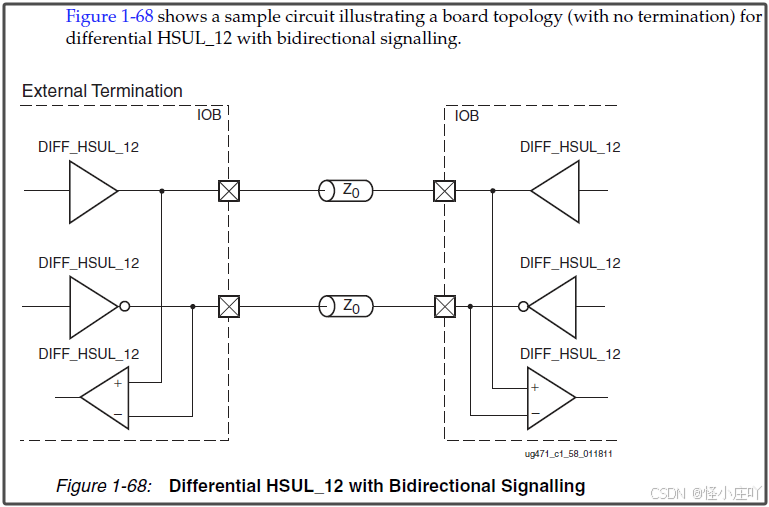

6.2、Differential HSUL_12

7、MOBILE_DDR (Low Power DDR)

**MOBILE_DDR 仅在 HR I/O Bank 中可用 **

MOBILE_DDR 标准适用于 LPDDR 和 Mobile DDR 内存总线,由 JEDEC I/O 标准中的 JESD209A 定义。这是一种 1.8V 单端 I/O 标准,无需 VREF 和 VTT 电源。7 系列 FPGA 支持该标准的单端信号和差分输出,其中差分输出用于驱动 CK/CK# 引脚。

差分(DIFF_)版本在输出端使用互补单端驱动器,在输入端使用差分接收器。

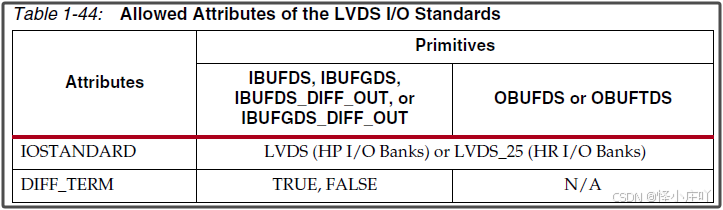

8、LVDS 和 LVDS_25(Low Voltage Differential Signaling)

Low-voltage differential signaling (LVDS) is a powerful high-speed interface in many system applications. 7 series FPGA I/Os are designed to comply with the EIA/TIA electrical specifications for LVDS to make system and board design easier. With the use of an LVDS current-mode driver in the IOBs and the optional internal differential termination feature, the need for external source termination in point-to-point applications is eliminated. 7 series devices provide the most flexible solution for doing an LVDS design in an FPGA.

**LVDS I/O standard 在 HR I/O Bank 中均可用 **。当选中内部差分端接(DIFF_TERM=TRUE)时,对于输出和输入,要求为 VCCO 提供 1.8V 的电源。

**LVDS_25 I/O standard 在 HP I/O Bank 中均可用 **。当选中内部差分端接(DIFF_TERM=TRUE)时,对于输出和输入,要求为 VCCO 提供 2.5V 的电源。

The 7 series FPGA LVDS transmitter does not require any external termination.

对原语属性的设置要求:

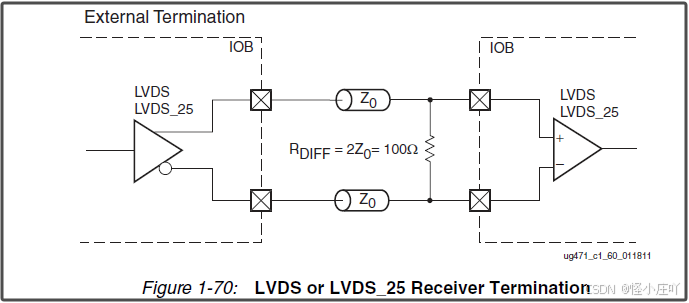

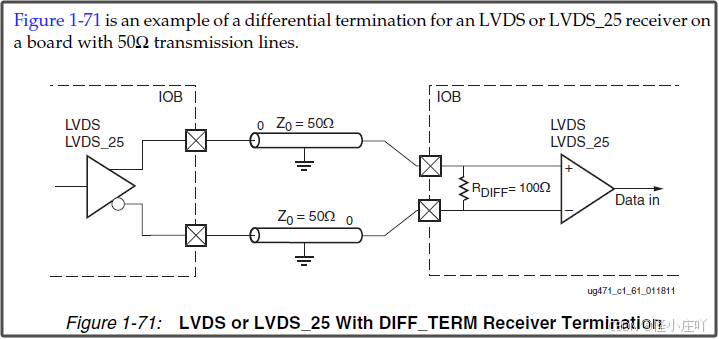

Figure 1-70 is an example of differential termination for an LVDS or LVDS_25 receiver on a board with 50Ω transmission lines.

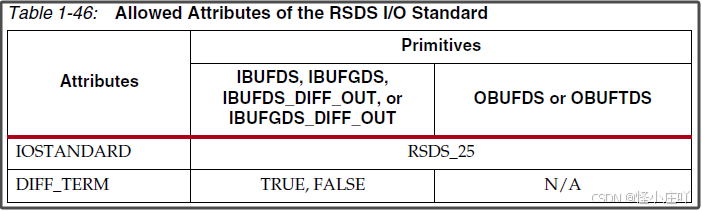

9、RSDS (Reduced Swing Differential Signaling)

**RSDS I/O standard 在 HR I/O Bank 中可用 **。

Reduced-swing differential signaling (RSDS) is similar to an LVDS high-speed interface using differential signaling. RSDS has a similar implementation to LVDS_25 in 7 series FPGAs and is only intended for point-to-point applications. RSDS is only available in HR I/O banks and requires a VCCO voltage level of 2.5V. The IOSTANDARD is called RSDS_25.

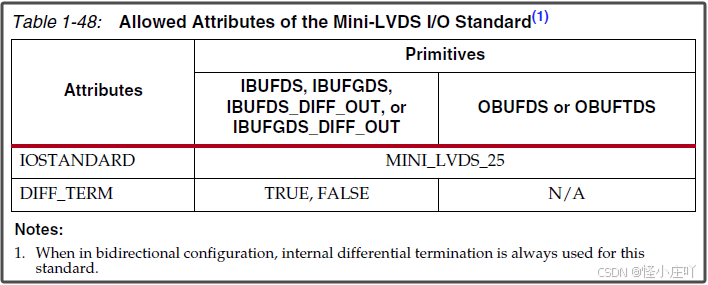

10、Mini-LVDS (Mini Low Voltage Differential Signaling)

**MINI_LVDS_25 standard 在 HR I/O Bank 中可用 **。

Mini-LVDS is a serial, intra-flat panel differential I/O standard that serves as an interface between the timing control function and an LCD source driver. Mini-LVDS inputs require a parallel-termination resistor, either by using a discrete resistor on the PCB, or by using the 7 series FPGAs DIFF_TERM attribute to enable internal termination. Mini-LVDS is only available in HR I/O banks and requires a VCCO voltage level of 2.5V. The IOSTANDARD is called MINI_LVDS_25.

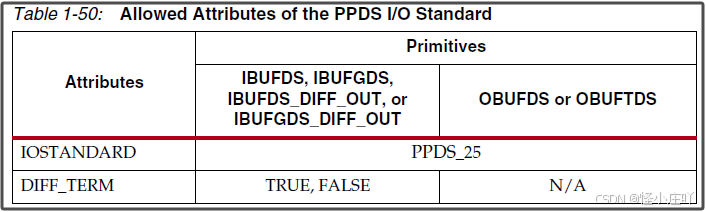

11、PPDS (Point-to-Point Differential Signaling)

**PPDS_25 standard 在 HR I/O Bank 中可用。 **

PPDS is a differential I/O standard for next-generation LCD interface row and column drivers. PPDS inputs require a parallel-termination resistor, either through the use of a discrete resistor on the PCB, or by using the 7 series FPGAs DIFF_TERM attribute to enable internal termination. PPDS is only available in HR I/O banks and requires a VCCO voltage level of 2.5V. The IOSTANDARD is called PPDS_25.

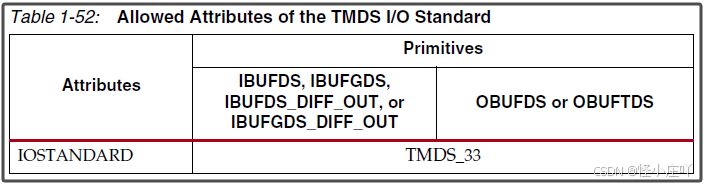

12、TMDS (Transition Minimized Differential Signaling)

**TMDS_33 standard 在 HR I/O Bank 中可用 **。

TMDS is a differential I/O standard for transmitting high-speed serial data used by the DVI and HDMI video interfaces. The TMDS standard requires external 50Ω pull-up resistors to 3.3V on the inputs. TMDS inputs do not require differential input termination resistors. TMDS is only available in HR I/O banks and requires a VCCO voltage level of 3.3V. The IOSTANDARD is called TMDS_33.

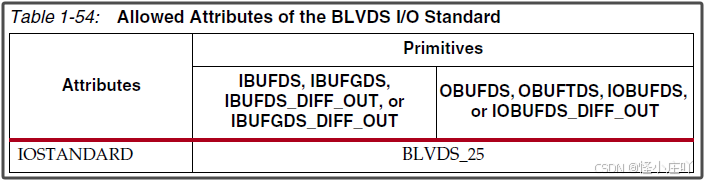

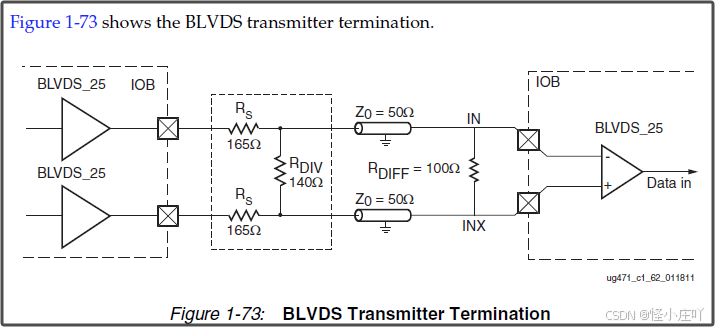

13、BLVDS (Bus LVDS)

**BLVDS_25 standard 在 HR I/O Bank 中可用 **。

Since LVDS is intended for point-to-point applications, BLVDS is not an EIA/TIA standard implementation and requires careful adaptation of I/O and PCB layout design rules. The primitive supplied in the software library for bidirectional LVDS does not use the 7 series FPGA LVDS current-mode driver, instead, it uses complementary single-ended differential drivers. Therefore, source termination is required. BLVDS is only available in HR I/O banks and requires a VCCO voltage level of 2.5V. The IOSTANDARD is called BLVDS_25.

14、参考文献

1、《ug471_7Series_SelectIO.pdf》

相关文章:

7系列 之 I/O标准和终端技术

背景 《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。 第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。 第 2 章《SelectIO Logic Resource…...

github 上的 CI/CD 的尝试

效果 步骤 新建仓库设置仓库的 page 新建一个 vite 的项目,改一下 vite.config.js 中的 base 工作流 在项目的根目录下新建一个 .github/workflows/ci.yml 文件,然后编辑一下内容 name: Build & Deploy Vue 3 Appon:push:branches: [main]permi…...

Scala和Go差异

Scala和Go(又称Golang)是两种现代编程语言,各自具有独特的特性和设计哲学。 尽管它们都可以用于构建高性能、可扩展的应用程序,但在许多方面存在显著差异。 Scala和Go的详细比较,涵盖它们的异同点: 1. 语…...

yup 使用 3 - 利用 meta 实现表单字段与表格列的统一结构配置(适配 React Table)

yup 使用 3 - 利用 meta 实现表单字段与表格列的统一结构配置(适配 React Table) Categories: Tools Last edited time: May 11, 2025 7:45 PM Status: Done Tags: form validation, schema design, yup 本文介绍如何通过 Yup 的 meta() 字段࿰…...

类初始化方法

一、类初始化方法 成员初始化列表 class Point {int x, y; public:Point(int a, int b) : x(a), y(b) {} };就地初始化(C11) 声明时初始化。 class Widget {int size 10; // 类内成员初始化vector<int> data{1,2,3}; };特殊情况:静…...

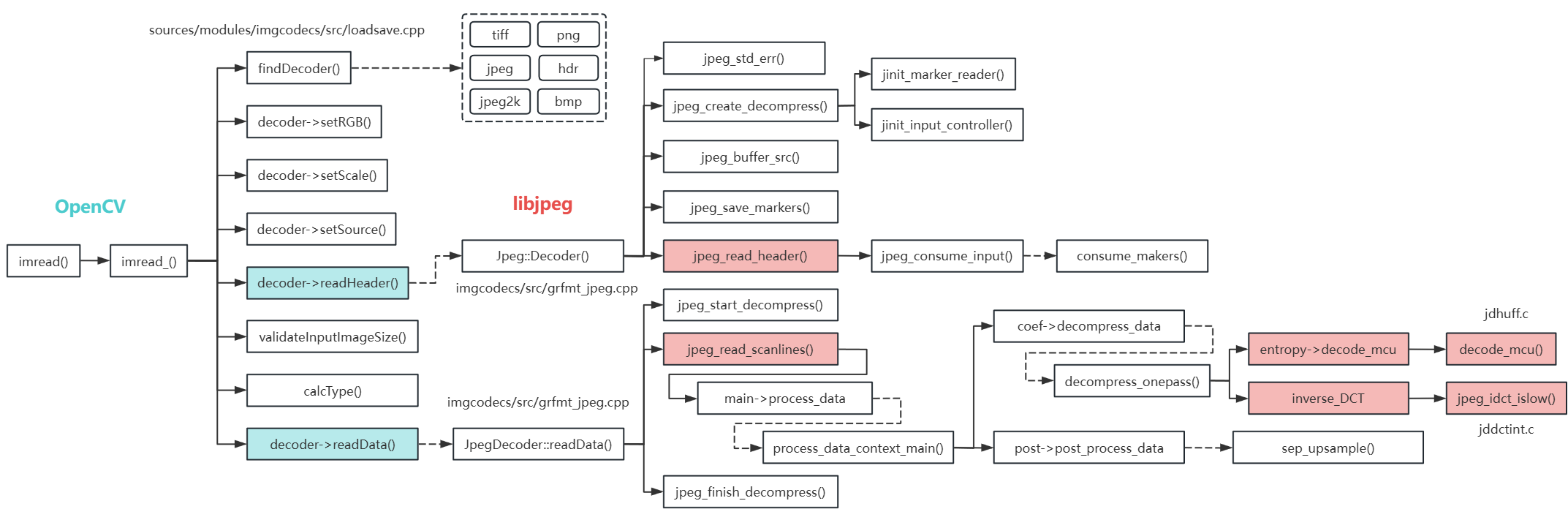

【OpenCV】imread函数的简单分析

目录 1.imread()1.1 imread()1.2 imread_()1.2.1 查找解码器(findDecoder)1.2.2 读取数据头(JpegDecoder-->readHeader)1.2.2.1 初始化错误信息(jpeg_std_error)1.2.2.2 创建jpeg解压缩对象(…...

【Linux实践系列】:进程间通信:万字详解共享内存实现通信

🔥 本文专栏:Linux Linux实践项目 🌸作者主页:努力努力再努力wz 💪 今日博客励志语录: 人生就像一场马拉松,重要的不是起点,而是坚持到终点的勇气 ★★★ 本文前置知识: …...

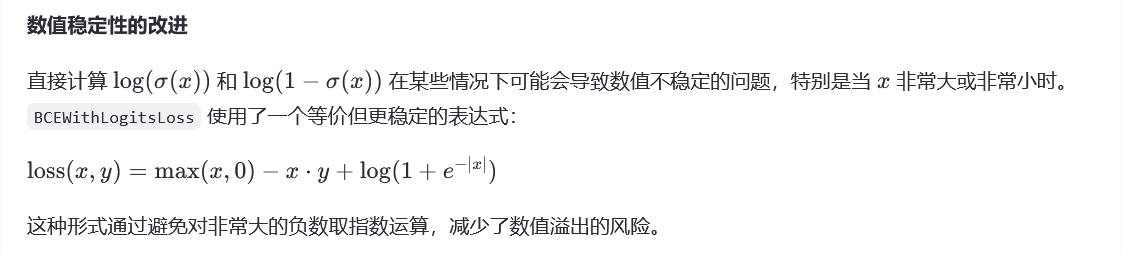

【笔记】BCEWithLogitsLoss

工作原理 BCEWithLogitsLoss 是 PyTorch 中的一个损失函数,用于二分类问题。 它结合了 Sigmoid 激活函数和二元交叉熵(Binary Cross Entropy, BCE)损失在一个类中。 这不仅简化了代码,而且通过数值稳定性优化提高了模型训练的效…...

Oracle SYSTEM/UNDO表空间损坏的处理思路

Oracle SYSTEM/UNDO表空间损坏是比较棘手的故障,通常会导致数据库异常宕机进而无法打开数据库。数据库的打开故障处理起来相对比较麻烦,读者可以参考本书第5章进一步了解该类故障的处理过程。如果数据库没有备份,通常需要设置官方不推荐的隐含…...

为什么 cout<<“中文你好“ 能正常输出中文

一, 简答: 受python3字符串模型影响得出的下文C字符串模型结论 是错的!C的字符串和python2的字符串模型类似,也就是普通的字符串是ASCII字符串和字节串两种语义,类似重载或多态,有时候解释为整数,有时候是字节串。Uni…...

Leetcode 3547. Maximum Sum of Edge Values in a Graph

Leetcode 3547. Maximum Sum of Edge Values in a Graph 1. 解题思路2. 代码实现 题目链接:3547. Maximum Sum of Edge Values in a Graph 1. 解题思路 这一题主要是在问题的分析上面。由题意易知,事实上给定的图必然只可能存在三种可能的结构&#x…...

关于Go语言的开发环境的搭建

1.Go开发环境的搭建 其实对于GO语言的这个开发环境的搭建的过程,类似于java的开发环境搭建,我们都是需要去安装这个开发工具包的,也就是俗称的这个SDK,他是对于我们的程序进行编译的,不然我们写的这个代码也是跑不起来…...

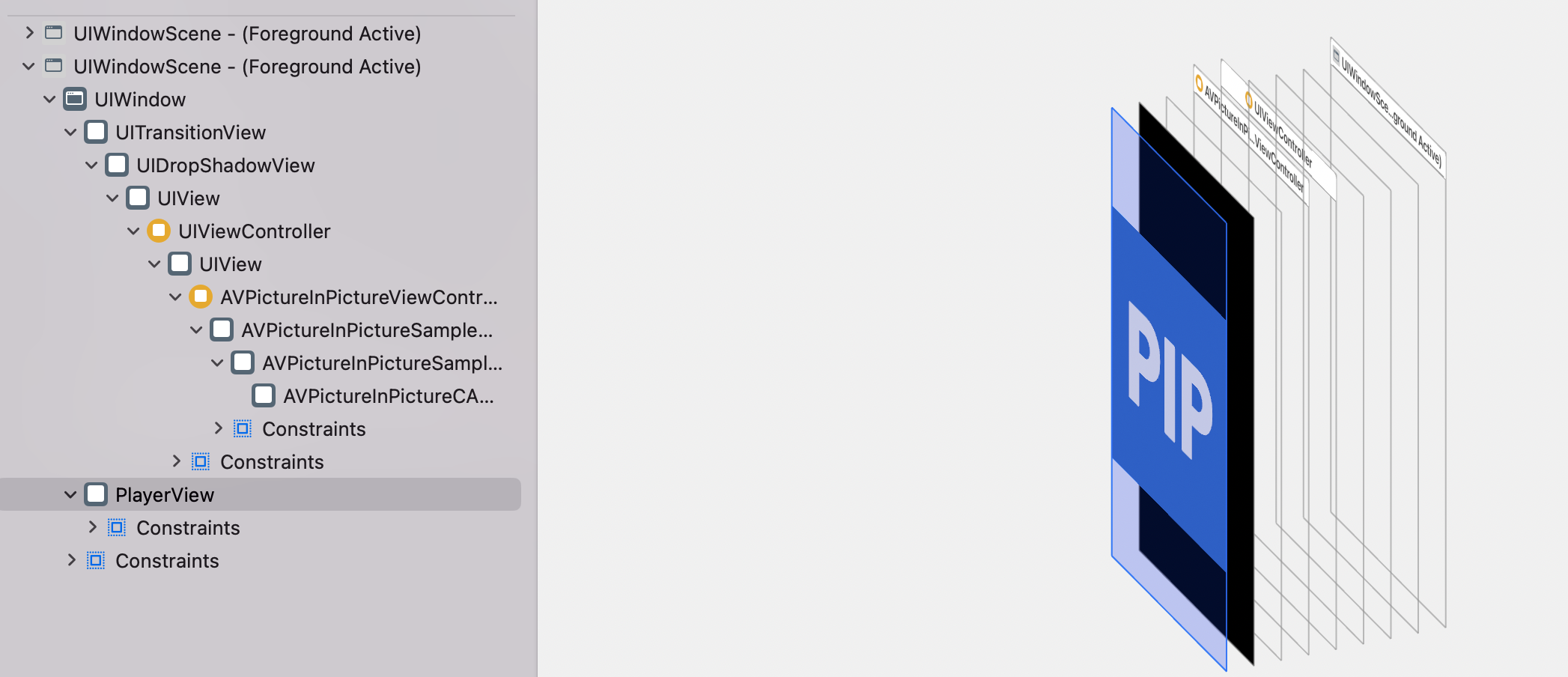

Flutter PIP 插件 ---- 为iOS 重构PipController, Demo界面,更好的体验

接上文 Flutter PIP 插件 ---- 新增PipActivity,Android 11以下支持自动进入PIP Mode 项目地址 PIP, pub.dev也已经同步发布 pip 0.0.3,你的加星和点赞,将是我继续改进最大的动力 在之前的界面设计中,还原动画等体验一…...

Redis 基本命令与操作全面解析:从入门到实战

前言 Redis 作为高性能内存数据库,其丰富的命令体系是发挥强大功能的基础。掌握 Redis 的基本命令,不仅能实现数据的高效读写,还能深入理解其内存模型与工作机制。本文将系统梳理 Redis 的核心命令,涵盖连接操作、键管理、数据类…...

数据库管理-第325期 ADG Failover后该做啥(20250513)

数据库管理325期 2025-05-13 数据库管理-第325期 ADG Failover后该做啥(20250513)1 故障处置2 恢复原主库3 其他操作总结 数据库管理-第325期 ADG Failover后该做啥(20250513) 作者:胖头鱼的鱼缸(尹海文&a…...

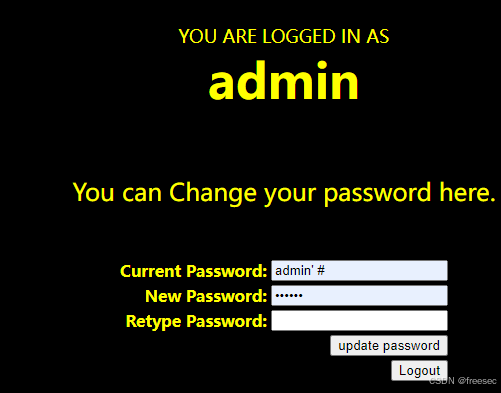

SQLi-Labs 第21-24关

Less-21 http://127.0.0.1/sqli-labs/Less-21/ 1,抓个请求包看看 分析分析cookie被base64URL编码了,解码之后就是admin 2,那么这个网站的漏洞利用方式也是和Less-20关一样的,只是攻击语句要先base64编码,再URL编码&…...

Oracle — 数据管理

介绍 Oracle数据库作为全球领先的关系型数据库管理系统,其数据管理能力以高效性、安全性和智能化为核心。系统通过多维度技术实现海量数据的存储与实时处理,支持高并发事务操作与复杂分析查询,满足企业关键业务需求。在安全领域,O…...

在 Qt Creator 中为 QDockWidget 设置隐藏和显示按钮

在 Qt Creator 中为 QDockWidget 设置隐藏和显示按钮 是的,QDockWidget 内置了隐藏和显示的功能,可以通过以下几种方式实现: 1. 使用 QDockWidget 自带的关闭按钮 QDockWidget 默认带有一个关闭按钮,可以通过以下代码启用&…...

LS-NET-012-TCP的交互过程详解

LS-NET-012-TCP的交互过程详解 附加:TCP如何保障数据传输 TCP的交互过程详解 一、TCP协议核心交互流程 TCP协议通过三次握手建立连接、数据传输、四次挥手终止连接三大阶段实现可靠传输。整个过程通过序列号、确认应答、窗口控制等机制保障传输可靠性。 1.1 三次…...

每日算法刷题Day1 5.9:leetcode数组3道题,用时1h

1.LC寻找数组的中心索引(简单) 数组和字符串 - LeetBook - 力扣(LeetCode)全球极客挚爱的技术成长平台 思想: 计算总和和左侧和,要让左侧和等于右侧和,即左侧和总和-左侧和-当前数字 代码 c代码: class Solution { public:i…...

解构认知边界:论万能方法的本体论批判与方法论重构——基于跨学科视阈的哲学-科学辩证

一、哲学维度的本体论批判 (1)理性主义的坍缩:从笛卡尔幻想到哥德尔陷阱 笛卡尔在《方法论》中构建的理性主义范式,企图通过"普遍怀疑-数学演绎"双重机制确立绝对方法体系。然而哥德尔不完备定理(Gdel, 19…...

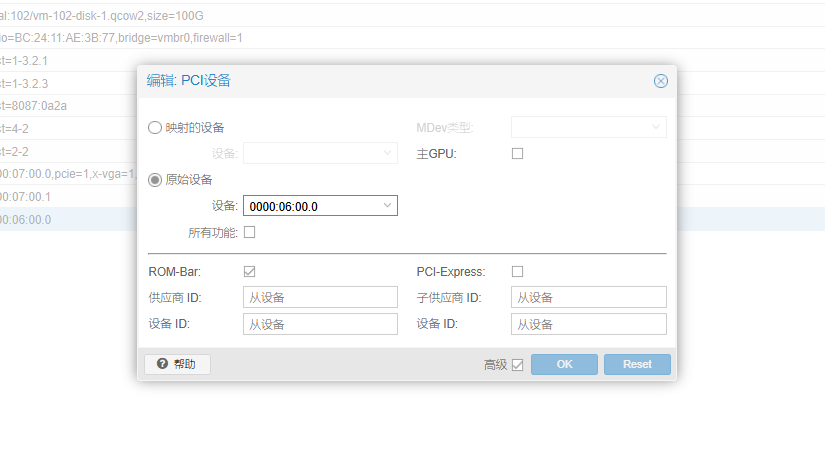

PVE WIN10直通无线网卡蓝牙

在 Proxmox VE (PVE) 中直通 Intel AC3165 无线网卡的 **蓝牙模块**(通常属于 USB 设备,而非 PCIe 设备)需要特殊处理,因为它的蓝牙部分通常通过 USB 连接,而 Wi-Fi 部分才是 PCIe 设备。以下是详细步骤: …...

第六节第二部分:抽象类的应用-模板方法设计模式

模板方法设计模式的写法 建议使用final关键字修饰模板方法 总结 代码: People(父类抽象类) package com.Abstract3; public abstract class People {/*设计模板方法设计模式* 1.定义一个模板方法出来*/public final void write(){System.out.println("\t\t\t…...

在另一个省发布抖音作品,IP属地会随之变化吗?

你是否曾有过这样的疑惑:出差旅游时在外地发布了一条抖音视频,评论区突然冒出“IP怎么显示xx省了?”的提问?随着各大社交平台上线“IP属地”功能,用户的地理位置标识成为公开信息,而属地显示的“灵敏性”也…...

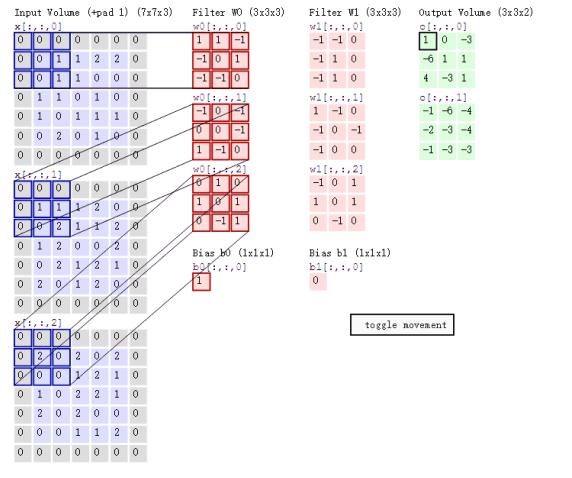

卷积神经网络-从零开始构建一个卷积神经网络

目录 一、什么是卷积神经网络CNN 1.1、核心概念 1.2、卷积层 二、什么是卷积计算 2.1、卷积计算的例子: 2.2、点积 2.3、卷积与点积的关系 2.4、Padding(填充) 2.4.1、Padding的主要作用 1、控制输出特征图尺寸 2、保留边缘信息 3. 支持深层网络训练 2.4.2、Str…...

力扣-101.对称二叉树

题目描述 给你一个二叉树的根节点 root , 检查它是否轴对称。 class Solution { public:bool check(TreeNode* p,TreeNode* q){if(!p&&!q)return true;if(!p&&q||!q&&p)return false;if(p->val!q->val)return false;return check(p…...

Tomcat和Nginx的主要区别

1、功能定位 Nginx:核心是高并发HTTP服务器和反向代理服务器,擅长处理静态资源(如HTML、图片)和负载均衡。Tomcat:是Java应用服务器,主要用于运行动态内容(如JSP、Servlet)…...

贪心算法:最小生成树

假设无向图为: A-B:1 A-C:3 B-C:1 B-D:4 C-D:1 C-E:5 D-E:6 一、使用Prim算法: public class Prim {//声明了两个静态常量,用于辅助 Prim 算法的实现private static final int V 5;//点数private static final int INF Integer.MA…...

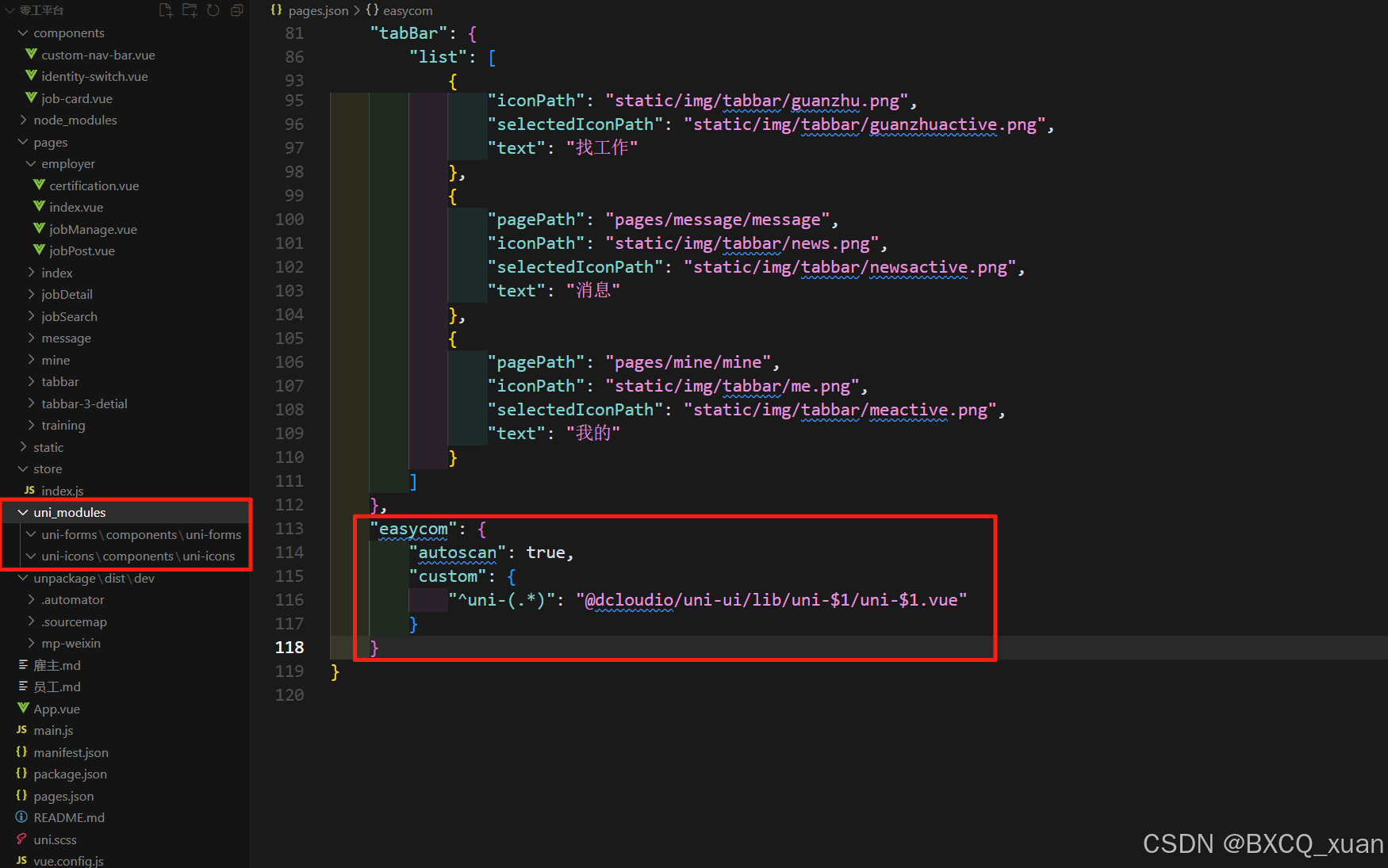

uniapp-文件查找失败:‘@dcloudio/uni-ui/lib/uni-icons/uni-icons.vue‘

uniapp-文件查找失败:‘dcloudio/uni-ui/lib/uni-icons/uni-icons.vue’ 今天在HBuilderX中使用uniapp开发微信小程序时遇到了这个问题,就是找不到uni-ui组件 当时创建项目,选择了一个中间带的底部带选项卡模板,并没有选择内置u…...

Vue2.x 和 Vue3.x 对比-差异

Vue3的优点 diff算法的提升 vue2中的虚拟DOM是全量的对比,也就是不管是写死的还是动态节点都会一层层比较,浪费时间在静态节点上。 vue3新增静态标记(patchflag ),与之前虚拟节点对比,只对比带有patch fla…...