使用DDR4控制器实现多通道数据读写(十二)

一、章节概括

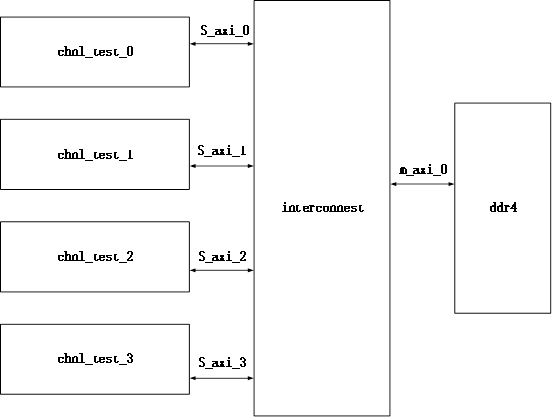

这一节使用interconnect RTL ip核将DDR4与四个读写通道级联,在测试工程中,将四个通道同时写入/读出地址与数据,并使用modelsim仿真器仿真,四个通道同时发送写请求或读请求后,经过interconnect后,观察数据的读写功能。

二、功能框架

三、interconnect RTL IP 核例化模版

axi_interconnect_0 axi_interconnect_0 (

.INTERCONNECT_ACLK(c0_ddr4_clk), // input wire INTERCONNECT_ACLK

.INTERCONNECT_ARESETN(~c0_ddr4_rst), // input wire INTERCONNECT_ARESETN

//chnl 0

.S00_AXI_ARESET_OUT_N(S00_AXI_ARESET_OUT_N), // output wire S00_AXI_ARESET_OUT_N

.S00_AXI_ACLK(clk_75m), // input wire S00_AXI_ACLK

.S00_AXI_AWID(S00_AXI_AWID), // input wire [3 : 0] S00_AXI_AWID

.S00_AXI_AWADDR(S00_AXI_AWADDR), // input wire [31 : 0] S00_AXI_AWADDR

.S00_AXI_AWLEN(S00_AXI_AWLEN), // input wire [7 : 0] S00_AXI_AWLEN

.S00_AXI_AWSIZE(S00_AXI_AWSIZE), // input wire [2 : 0] S00_AXI_AWSIZE

.S00_AXI_AWBURST(S00_AXI_AWBURST), // input wire [1 : 0] S00_AXI_AWBURST

.S00_AXI_AWLOCK(S00_AXI_AWLOCK), // input wire S00_AXI_AWLOCK

.S00_AXI_AWCACHE(S00_AXI_AWCACHE), // input wire [3 : 0] S00_AXI_AWCACHE

.S00_AXI_AWPROT(S00_AXI_AWPROT), // input wire [2 : 0] S00_AXI_AWPROT

.S00_AXI_AWQOS(S00_AXI_AWQOS), // input wire [3 : 0] S00_AXI_AWQOS

.S00_AXI_AWVALID(S00_AXI_AWVALID), // input wire S00_AXI_AWVALID

.S00_AXI_AWREADY(S00_AXI_AWREADY), // output wire S00_AXI_AWREADY

.S00_AXI_WDATA(S00_AXI_WDATA), // input wire [511 : 0] S00_AXI_WDATA

.S00_AXI_WSTRB(S00_AXI_WSTRB), // input wire [63 : 0] S00_AXI_WSTRB

.S00_AXI_WLAST(S00_AXI_WLAST), // input wire S00_AXI_WLAST

.S00_AXI_WVALID(S00_AXI_WVALID), // input wire S00_AXI_WVALID

.S00_AXI_WREADY(S00_AXI_WREADY), // output wire S00_AXI_WREADY

.S00_AXI_BID(S00_AXI_BID), // output wire [3 : 0] S00_AXI_BID

.S00_AXI_BRESP(S00_AXI_BRESP), // output wire [1 : 0] S00_AXI_BRESP

.S00_AXI_BVALID(S00_AXI_BVALID), // output wire S00_AXI_BVALID

.S00_AXI_BREADY(S00_AXI_BREADY), // input wire S00_AXI_BREADY

.S00_AXI_ARID(S00_AXI_ARID), // input wire [3 : 0] S00_AXI_ARID

.S00_AXI_ARADDR(S00_AXI_ARADDR), // input wire [31 : 0] S00_AXI_ARADDR

.S00_AXI_ARLEN(S00_AXI_ARLEN), // input wire [7 : 0] S00_AXI_ARLEN

.S00_AXI_ARSIZE(S00_AXI_ARSIZE), // input wire [2 : 0] S00_AXI_ARSIZE

.S00_AXI_ARBURST(S00_AXI_ARBURST), // input wire [1 : 0] S00_AXI_ARBURST

.S00_AXI_ARLOCK(S00_AXI_ARLOCK), // input wire S00_AXI_ARLOCK

.S00_AXI_ARCACHE(S00_AXI_ARCACHE), // input wire [3 : 0] S00_AXI_ARCACHE

.S00_AXI_ARPROT(S00_AXI_ARPROT), // input wire [2 : 0] S00_AXI_ARPROT

.S00_AXI_ARQOS(S00_AXI_ARQOS), // input wire [3 : 0] S00_AXI_ARQOS

.S00_AXI_ARVALID(S00_AXI_ARVALID), // input wire S00_AXI_ARVALID

.S00_AXI_ARREADY(S00_AXI_ARREADY), // output wire S00_AXI_ARREADY

.S00_AXI_RID(S00_AXI_RID), // output wire [3 : 0] S00_AXI_RID

.S00_AXI_RDATA(S00_AXI_RDATA), // output wire [511 : 0] S00_AXI_RDATA

.S00_AXI_RRESP(S00_AXI_RRESP), // output wire [1 : 0] S00_AXI_RRESP

.S00_AXI_RLAST(S00_AXI_RLAST), // output wire S00_AXI_RLAST

.S00_AXI_RVALID(S00_AXI_RVALID), // output wire S00_AXI_RVALID

.S00_AXI_RREADY(S00_AXI_RREADY), // input wire S00_AXI_RREADY

//chnl 1

.S01_AXI_ARESET_OUT_N(S01_AXI_ARESET_OUT_N), // output wire S01_AXI_ARESET_OUT_N

.S01_AXI_ACLK(clk_125m), // input wire S01_AXI_ACLK

.S01_AXI_AWID(S01_AXI_AWID), // input wire [3 : 0] S01_AXI_AWID

.S01_AXI_AWADDR(S01_AXI_AWADDR), // input wire [31 : 0] S01_AXI_AWADDR

.S01_AXI_AWLEN(S01_AXI_AWLEN), // input wire [7 : 0] S01_AXI_AWLEN

.S01_AXI_AWSIZE(S01_AXI_AWSIZE), // input wire [2 : 0] S01_AXI_AWSIZE

.S01_AXI_AWBURST(S01_AXI_AWBURST), // input wire [1 : 0] S01_AXI_AWBURST

.S01_AXI_AWLOCK(S01_AXI_AWLOCK), // input wire S01_AXI_AWLOCK

.S01_AXI_AWCACHE(S01_AXI_AWCACHE), // input wire [3 : 0] S01_AXI_AWCACHE

.S01_AXI_AWPROT(S01_AXI_AWPROT), // input wire [2 : 0] S01_AXI_AWPROT

.S01_AXI_AWQOS(S01_AXI_AWQOS), // input wire [3 : 0] S01_AXI_AWQOS

.S01_AXI_AWVALID(S01_AXI_AWVALID), // input wire S01_AXI_AWVALID

.S01_AXI_AWREADY(S01_AXI_AWREADY), // output wire S01_AXI_AWREADY

.S01_AXI_WDATA(S01_AXI_WDATA), // input wire [511 : 0] S01_AXI_WDATA

.S01_AXI_WSTRB(S01_AXI_WSTRB), // input wire [63 : 0] S01_AXI_WSTRB

.S01_AXI_WLAST(S01_AXI_WLAST), // input wire S01_AXI_WLAST

.S01_AXI_WVALID(S01_AXI_WVALID), // input wire S01_AXI_WVALID

.S01_AXI_WREADY(S01_AXI_WREADY), // output wire S01_AXI_WREADY

.S01_AXI_BID(S01_AXI_BID), // output wire [3 : 0] S01_AXI_BID

.S01_AXI_BRESP(S01_AXI_BRESP), // output wire [1 : 0] S01_AXI_BRESP

.S01_AXI_BVALID(S01_AXI_BVALID), // output wire S01_AXI_BVALID

.S01_AXI_BREADY(S01_AXI_BREADY), // input wire S01_AXI_BREADY

.S01_AXI_ARID(S01_AXI_ARID), // input wire [3 : 0] S01_AXI_ARID

.S01_AXI_ARADDR(S01_AXI_ARADDR), // input wire [31 : 0] S01_AXI_ARADDR

.S01_AXI_ARLEN(S01_AXI_ARLEN), // input wire [7 : 0] S01_AXI_ARLEN

.S01_AXI_ARSIZE(S01_AXI_ARSIZE), // input wire [2 : 0] S01_AXI_ARSIZE

.S01_AXI_ARBURST(S01_AXI_ARBURST), // input wire [1 : 0] S01_AXI_ARBURST

.S01_AXI_ARLOCK(S01_AXI_ARLOCK), // input wire S01_AXI_ARLOCK

.S01_AXI_ARCACHE(S01_AXI_ARCACHE), // input wire [3 : 0] S01_AXI_ARCACHE

.S01_AXI_ARPROT(S01_AXI_ARPROT), // input wire [2 : 0] S01_AXI_ARPROT

.S01_AXI_ARQOS(S01_AXI_ARQOS), // input wire [3 : 0] S01_AXI_ARQOS

.S01_AXI_ARVALID(S01_AXI_ARVALID), // input wire S01_AXI_ARVALID

.S01_AXI_ARREADY(S01_AXI_ARREADY), // output wire S01_AXI_ARREADY

.S01_AXI_RID(S01_AXI_RID), // output wire [3 : 0] S01_AXI_RID

.S01_AXI_RDATA(S01_AXI_RDATA), // output wire [511 : 0] S01_AXI_RDATA

.S01_AXI_RRESP(S01_AXI_RRESP), // output wire [1 : 0] S01_AXI_RRESP

.S01_AXI_RLAST(S01_AXI_RLAST), // output wire S01_AXI_RLAST

.S01_AXI_RVALID(S01_AXI_RVALID), // output wire S01_AXI_RVALID

.S01_AXI_RREADY(S01_AXI_RREADY), // input wire S01_AXI_RREADY

//chnl 2

.S02_AXI_ARESET_OUT_N(S02_AXI_ARESET_OUT_N), // output wire S02_AXI_ARESET_OUT_N

.S02_AXI_ACLK(clk_75m), // input wire S02_AXI_ACLK

.S02_AXI_AWID(S02_AXI_AWID), // input wire [3 : 0] S02_AXI_AWID

.S02_AXI_AWADDR(S02_AXI_AWADDR), // input wire [31 : 0] S02_AXI_AWADDR

.S02_AXI_AWLEN(S02_AXI_AWLEN), // input wire [7 : 0] S02_AXI_AWLEN

.S02_AXI_AWSIZE(S02_AXI_AWSIZE), // input wire [2 : 0] S02_AXI_AWSIZE

.S02_AXI_AWBURST(S02_AXI_AWBURST), // input wire [1 : 0] S02_AXI_AWBURST

.S02_AXI_AWLOCK(S02_AXI_AWLOCK), // input wire S02_AXI_AWLOCK

.S02_AXI_AWCACHE(S02_AXI_AWCACHE), // input wire [3 : 0] S02_AXI_AWCACHE

.S02_AXI_AWPROT(S02_AXI_AWPROT), // input wire [2 : 0] S02_AXI_AWPROT

.S02_AXI_AWQOS(S02_AXI_AWQOS), // input wire [3 : 0] S02_AXI_AWQOS

.S02_AXI_AWVALID(S02_AXI_AWVALID), // input wire S02_AXI_AWVALID

.S02_AXI_AWREADY(S02_AXI_AWREADY), // output wire S02_AXI_AWREADY

.S02_AXI_WDATA(S02_AXI_WDATA), // input wire [511 : 0] S02_AXI_WDATA

.S02_AXI_WSTRB(S02_AXI_WSTRB), // input wire [63 : 0] S02_AXI_WSTRB

.S02_AXI_WLAST(S02_AXI_WLAST), // input wire S02_AXI_WLAST

.S02_AXI_WVALID(S02_AXI_WVALID), // input wire S02_AXI_WVALID

.S02_AXI_WREADY(S02_AXI_WREADY), // output wire S02_AXI_WREADY

.S02_AXI_BID(S02_AXI_BID), // output wire [3 : 0] S02_AXI_BID

.S02_AXI_BRESP(S02_AXI_BRESP), // output wire [1 : 0] S02_AXI_BRESP

.S02_AXI_BVALID(S02_AXI_BVALID), // output wire S02_AXI_BVALID

.S02_AXI_BREADY(S02_AXI_BREADY), // input wire S02_AXI_BREADY

.S02_AXI_ARID(S02_AXI_ARID), // input wire [3 : 0] S02_AXI_ARID

.S02_AXI_ARADDR(S02_AXI_ARADDR), // input wire [31 : 0] S02_AXI_ARADDR

.S02_AXI_ARLEN(S02_AXI_ARLEN), // input wire [7 : 0] S02_AXI_ARLEN

.S02_AXI_ARSIZE(S02_AXI_ARSIZE), // input wire [2 : 0] S02_AXI_ARSIZE

.S02_AXI_ARBURST(S02_AXI_ARBURST), // input wire [1 : 0] S02_AXI_ARBURST

.S02_AXI_ARLOCK(S02_AXI_ARLOCK), // input wire S02_AXI_ARLOCK

.S02_AXI_ARCACHE(S02_AXI_ARCACHE), // input wire [3 : 0] S02_AXI_ARCACHE

.S02_AXI_ARPROT(S02_AXI_ARPROT), // input wire [2 : 0] S02_AXI_ARPROT

.S02_AXI_ARQOS(S02_AXI_ARQOS), // input wire [3 : 0] S02_AXI_ARQOS

.S02_AXI_ARVALID(S02_AXI_ARVALID), // input wire S02_AXI_ARVALID

.S02_AXI_ARREADY(S02_AXI_ARREADY), // output wire S02_AXI_ARREADY

.S02_AXI_RID(S02_AXI_RID), // output wire [3 : 0] S02_AXI_RID

.S02_AXI_RDATA(S02_AXI_RDATA), // output wire [511 : 0] S02_AXI_RDATA

.S02_AXI_RRESP(S02_AXI_RRESP), // output wire [1 : 0] S02_AXI_RRESP

.S02_AXI_RLAST(S02_AXI_RLAST), // output wire S02_AXI_RLAST

.S02_AXI_RVALID(S02_AXI_RVALID), // output wire S02_AXI_RVALID

.S02_AXI_RREADY(S02_AXI_RREADY), // input wire S02_AXI_RREADY

//chnl 3

.S03_AXI_ARESET_OUT_N(S03_AXI_ARESET_OUT_N), // output wire S03_AXI_ARESET_OUT_N

.S03_AXI_ACLK(clk_75m), // input wire S03_AXI_ACLK

.S03_AXI_AWID(S03_AXI_AWID), // input wire [3 : 0] S03_AXI_AWID

.S03_AXI_AWADDR(S03_AXI_AWADDR), // input wire [31 : 0] S03_AXI_AWADDR

.S03_AXI_AWLEN(S03_AXI_AWLEN), // input wire [7 : 0] S03_AXI_AWLEN

.S03_AXI_AWSIZE(S03_AXI_AWSIZE), // input wire [2 : 0] S03_AXI_AWSIZE

.S03_AXI_AWBURST(S03_AXI_AWBURST), // input wire [1 : 0] S03_AXI_AWBURS

.S03_AXI_AWLOCK(S03_AXI_AWLOCK), // input wire S03_AXI_AWLOCK

.S03_AXI_AWCACHE(S03_AXI_AWCACHE), // input wire [3 : 0] S03_AXI_AWCACHE

.S03_AXI_AWPROT(S03_AXI_AWPROT), // input wire [2 : 0] S03_AXI_AWPROT

.S03_AXI_AWQOS(S03_AXI_AWQOS), // input wire [3 : 0] S03_AXI_AWQOS

.S03_AXI_AWVALID(S03_AXI_AWVALID), // input wire S03_AXI_AWVALID

.S03_AXI_AWREADY(S03_AXI_AWREADY), // output wire S03_AXI_AWREADY

.S03_AXI_WDATA(S03_AXI_WDATA), // input wire [511 : 0] S03_AXI_WDATA

.S03_AXI_WSTRB(S03_AXI_WSTRB), // input wire [63 : 0] S03_AXI_WSTRB

.S03_AXI_WLAST(S03_AXI_WLAST), // input wire S03_AXI_WLAST

.S03_AXI_WVALID(S03_AXI_WVALID), // input wire S03_AXI_WVALID

.S03_AXI_WREADY(S03_AXI_WREADY), // output wire S03_AXI_WREADY

.S03_AXI_BID(S03_AXI_BID), // output wire [3 : 0] S03_AXI_BID

.S03_AXI_BRESP(S03_AXI_BRESP), // output wire [1 : 0] S03_AXI_BRESP

.S03_AXI_BVALID(S03_AXI_BVALID), // output wire S03_AXI_BVALID

.S03_AXI_BREADY(S03_AXI_BREADY), // input wire S03_AXI_BREADY

.S03_AXI_ARID(S03_AXI_ARID), // input wire [3 : 0] S03_AXI_ARID

.S03_AXI_ARADDR(S03_AXI_ARADDR), // input wire [31 : 0] S03_AXI_ARADDR

.S03_AXI_ARLEN(S03_AXI_ARLEN), // input wire [7 : 0] S03_AXI_ARLEN

.S03_AXI_ARSIZE(S03_AXI_ARSIZE), // input wire [2 : 0] S03_AXI_ARSIZE

.S03_AXI_ARBURST(S03_AXI_ARBURST), // input wire [1 : 0] S03_AXI_ARBURST

.S03_AXI_ARLOCK(S03_AXI_ARLOCK), // input wire S03_AXI_ARLOCK

.S03_AXI_ARCACHE(S03_AXI_ARCACHE), // input wire [3 : 0] S03_AXI_ARCACHE

.S03_AXI_ARPROT(S03_AXI_ARPROT), // input wire [2 : 0] S03_AXI_ARPROT

.S03_AXI_ARQOS(S03_AXI_ARQOS), // input wire [3 : 0] S03_AXI_ARQOS

.S03_AXI_ARVALID(S03_AXI_ARVALID), // input wire S03_AXI_ARVALID

.S03_AXI_ARREADY(S03_AXI_ARREADY), // output wire S03_AXI_ARREADY

.S03_AXI_RID(S03_AXI_RID), // output wire [3 : 0] S03_AXI_RID

.S03_AXI_RDATA(S03_AXI_RDATA), // output wire [511 : 0] S03_AXI_RDATA

.S03_AXI_RRESP(S03_AXI_RRESP), // output wire [1 : 0] S03_AXI_RRESP

.S03_AXI_RLAST(S03_AXI_RLAST), // output wire S03_AXI_RLAST

.S03_AXI_RVALID(S03_AXI_RVALID), // output wire S03_AXI_RVALID

.S03_AXI_RREADY(S03_AXI_RREADY), // input wire S03_AXI_RREADY

//master

//ddr4 awaddr

.M00_AXI_ARESET_OUT_N(c0_ddr4_aresetn_n), // output wire M00_AXI_ARESET_OUT_N

.M00_AXI_ACLK(c0_ddr4_clk), // input wire M00_AXI_ACLK

.M00_AXI_AWID(c0_ddr4_s_axi_awid), // output wire [7 : 0] M00_AXI_AWID

.M00_AXI_AWADDR(c0_ddr4_s_axi_awaddr), // output wire [31 : 0] M00_AXI_AWADDR

.M00_AXI_AWLEN(c0_ddr4_s_axi_awlen), // output wire [7 : 0] M00_AXI_AWLEN

.M00_AXI_AWSIZE(c0_ddr4_s_axi_awsize), // output wire [2 : 0] M00_AXI_AWSIZE

.M00_AXI_AWBURST(c0_ddr4_s_axi_awburst), // output wire [1 : 0] M00_AXI_AWBURST

.M00_AXI_AWLOCK(c0_ddr4_s_axi_awlock), // output wire M00_AXI_AWLOCK

.M00_AXI_AWCACHE(c0_ddr4_s_axi_awcache), // output wire [3 : 0] M00_AXI_AWCACHE

.M00_AXI_AWPROT(c0_ddr4_s_axi_awprot), // output wire [2 : 0] M00_AXI_AWPROT

.M00_AXI_AWQOS(c0_ddr4_s_axi_awqos), // output wire [3 : 0] M00_AXI_AWQOS

.M00_AXI_AWVALID(c0_ddr4_s_axi_awvalid), // output wire M00_AXI_AWVALID

.M00_AXI_AWREADY(c0_ddr4_s_axi_awready), // input wire M00_AXI_AWREADY

//ddr4 wdata

.M00_AXI_WDATA(c0_ddr4_s_axi_wdata), // output wire [511 : 0] M00_AXI_WDATA

.M00_AXI_WSTRB(c0_ddr4_s_axi_wstrb), // output wire [63 : 0] M00_AXI_WSTRB

.M00_AXI_WLAST(c0_ddr4_s_axi_wlast), // output wire M00_AXI_WLAST

.M00_AXI_WVALID(c0_ddr4_s_axi_wvalid), // output wire M00_AXI_WVALID

.M00_AXI_WREADY(c0_ddr4_s_axi_wready), // input wire M00_AXI_WREADY

//ddr4 w bresp

.M00_AXI_BID(c0_ddr4_s_axi_bid), // input wire [7 : 0] M00_AXI_BID

.M00_AXI_BRESP(c0_ddr4_s_axi_bresp), // input wire [1 : 0] M00_AXI_BRESP

.M00_AXI_BVALID(c0_ddr4_s_axi_bvalid), // input wire M00_AXI_BVALID

.M00_AXI_BREADY(c0_ddr4_s_axi_bready), // output wire M00_AXI_BREADY

//ddr4 araddr

.M00_AXI_ARID(c0_ddr4_s_axi_arid), // output wire [7 : 0] M00_AXI_ARID

.M00_AXI_ARADDR(c0_ddr4_s_axi_araddr), // output wire [31 : 0] M00_AXI_ARADDR

.M00_AXI_ARLEN(c0_ddr4_s_axi_arlen), // output wire [7 : 0] M00_AXI_ARLEN

.M00_AXI_ARSIZE(c0_ddr4_s_axi_arsize), // output wire [2 : 0] M00_AXI_ARSIZE

.M00_AXI_ARBURST(c0_ddr4_s_axi_arburst), // output wire [1 : 0] M00_AXI_ARBURST

.M00_AXI_ARLOCK(c0_ddr4_s_axi_arlock), // output wire M00_AXI_ARLOCK

.M00_AXI_ARCACHE(c0_ddr4_s_axi_arcache), // output wire [3 : 0] M00_AXI_ARCACHE

.M00_AXI_ARPROT(c0_ddr4_s_axi_arprot), // output wire [2 : 0] M00_AXI_ARPROT

.M00_AXI_ARQOS(c0_ddr4_s_axi_arqos), // output wire [3 : 0] M00_AXI_ARQOS

.M00_AXI_ARVALID(c0_ddr4_s_axi_arvalid), // output wire M00_AXI_ARVALID

.M00_AXI_ARREADY(c0_ddr4_s_axi_arready), // input wire M00_AXI_ARREADY

//ddr4 rdata

.M00_AXI_RID(c0_ddr4_s_axi_rid), // input wire [7 : 0] M00_AXI_RID

.M00_AXI_RDATA(c0_ddr4_s_axi_rdata), // input wire [511 : 0] M00_AXI_RDATA

.M00_AXI_RRESP(c0_ddr4_s_axi_rresp), // input wire [1 : 0] M00_AXI_RRESP

.M00_AXI_RLAST(c0_ddr4_s_axi_rlast), // input wire M00_AXI_RLAST

.M00_AXI_RVALID(c0_ddr4_s_axi_rvalid), // input wire M00_AXI_RVALID

.M00_AXI_RREADY(c0_ddr4_s_axi_rready) // output wire M00_AXI_RREADY

);

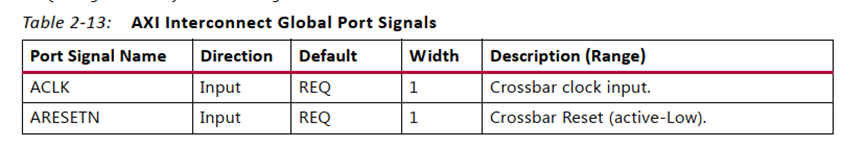

例化说明:IP核系统时钟由DDR4的用户时钟提供。IP核的系统复位为低有效复位,由ddr4输出的用户复位信号取反得到。

四个通道的信号连接到四个通道测试模块,四个测试模块为axi主端口,与IP核的从端口交互。DDR4为axi从端口,与ip核的主端口交互。

为了测试在不同的时钟域时的读写情况,0、2、3通道为75MHz时钟,1通道为125MHz时钟。IP核的四个从端口输出低有效复位信号。供四个通道使用。

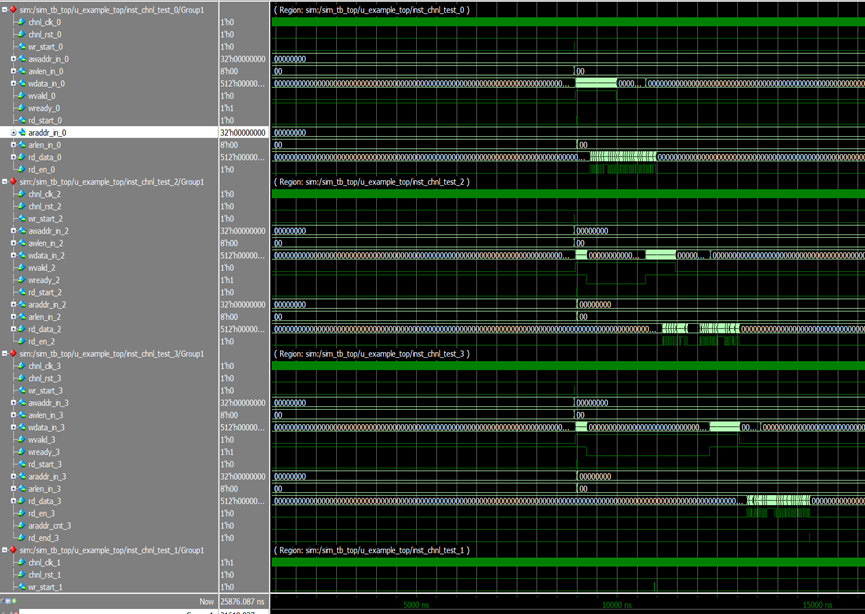

四、仿真测试:

在测试模块中,在同一时刻在不同的起始地址写入128个数据,并在同一时刻在不同的起始地址读出128个数据。

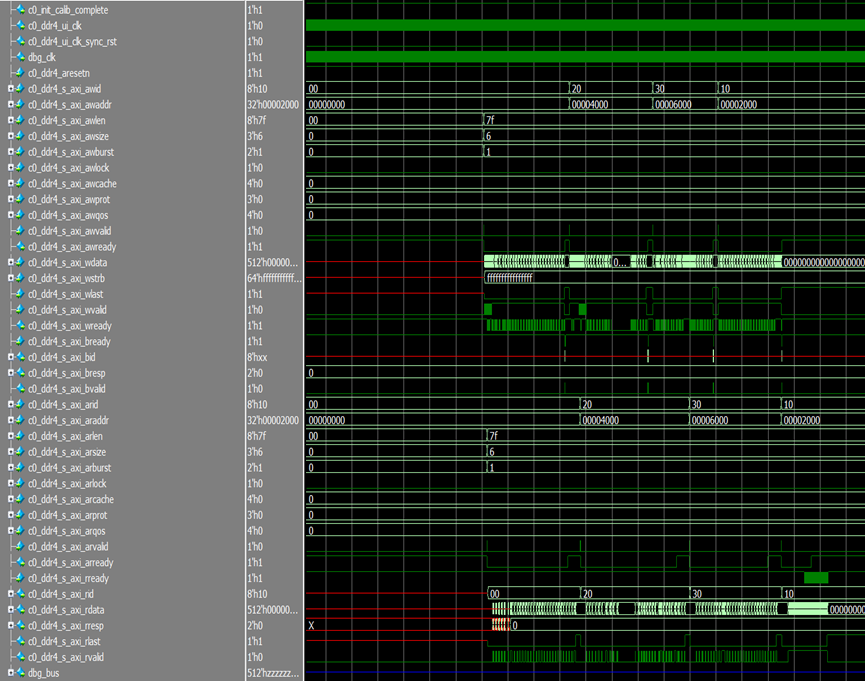

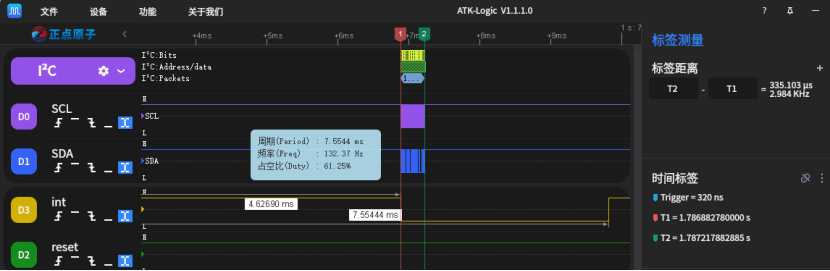

下图为测试通道0、2、3的读写数据波形,可以看到三个通道同时发起读写请求,然后根据通道顺序决定仲裁。通道号越小,优先级越高。

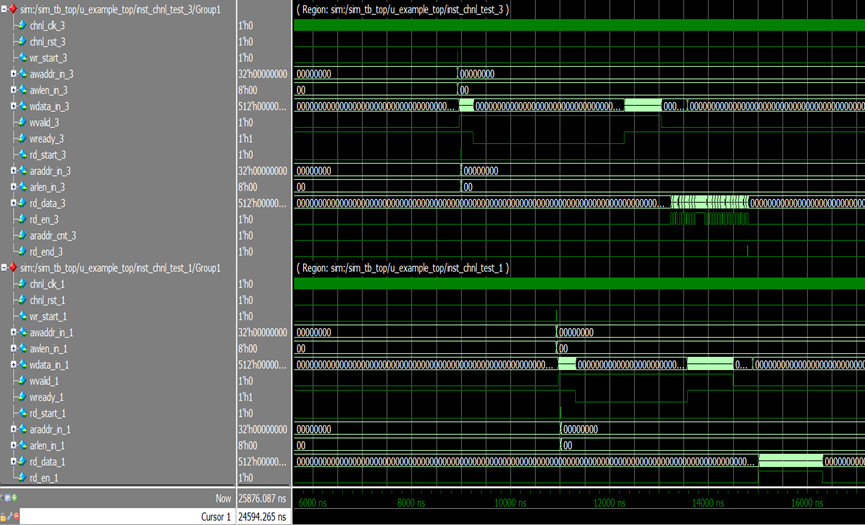

下图为通道1和通道3的读写测试波形,由于通道1的读写请求最晚,所以通道1的响应优先级最小。

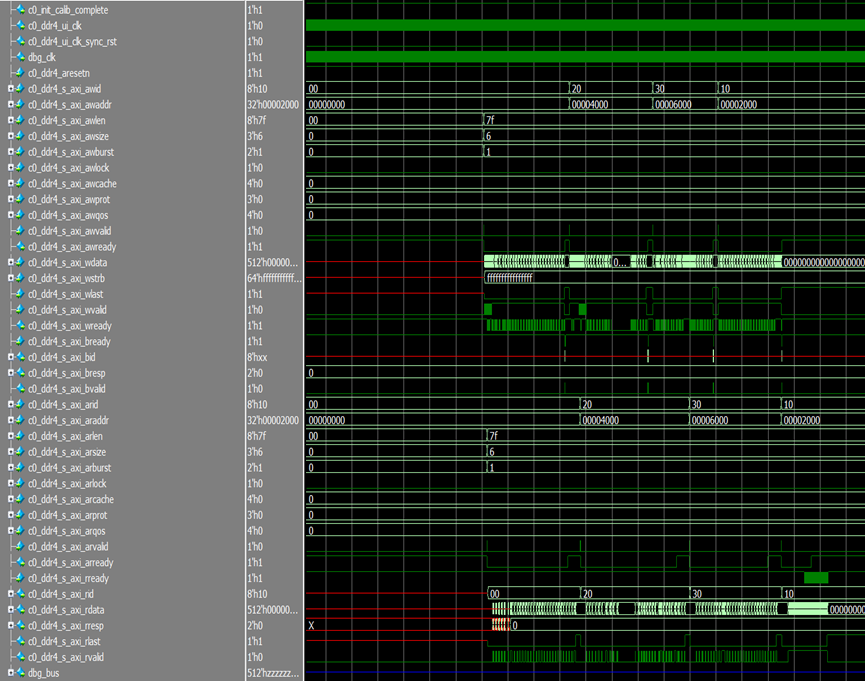

下图为DDR4接口的波形图,可以看到经过interconnect后,将每个读写请求依次进行。因为同时只能读或只能写,所以在读写未完成时交替操作。

本文章由威三学社出品

对课程感兴趣可以私信联系

相关文章:

使用DDR4控制器实现多通道数据读写(十二)

一、章节概括 这一节使用interconnect RTL ip核将DDR4与四个读写通道级联,在测试工程中,将四个通道同时写入/读出地址与数据,并使用modelsim仿真器仿真,四个通道同时发送写请求或读请求后,经过interconnect后ÿ…...

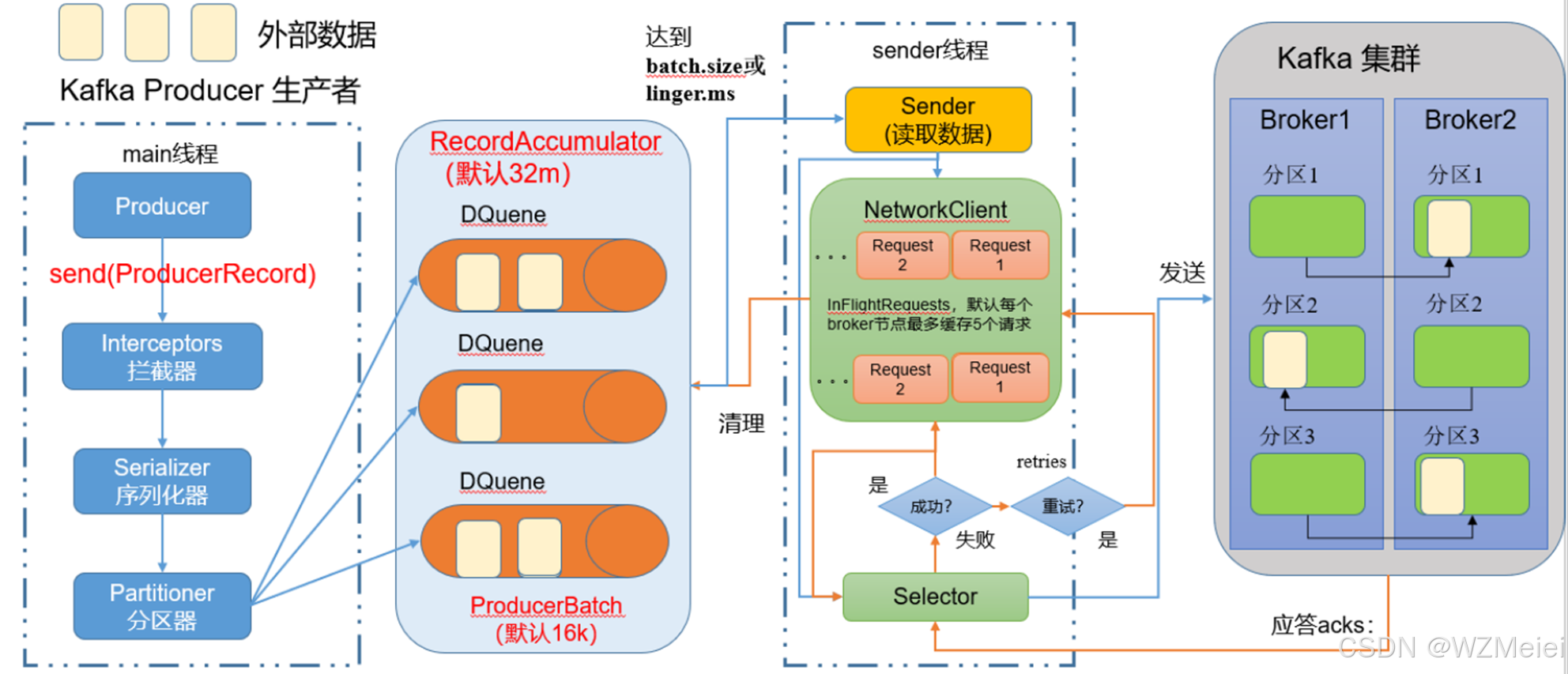

Kafka 生产者工作流程详解

以下是 Kafka 生产者工作流程的清晰分步解释,结合关键机制与用户数据: 1. 生产者初始化与数据发送 主线程创建生产者对象,调用 send(ProducerRecord) 发送消息。 拦截器(可选):可添加自定义逻辑(…...

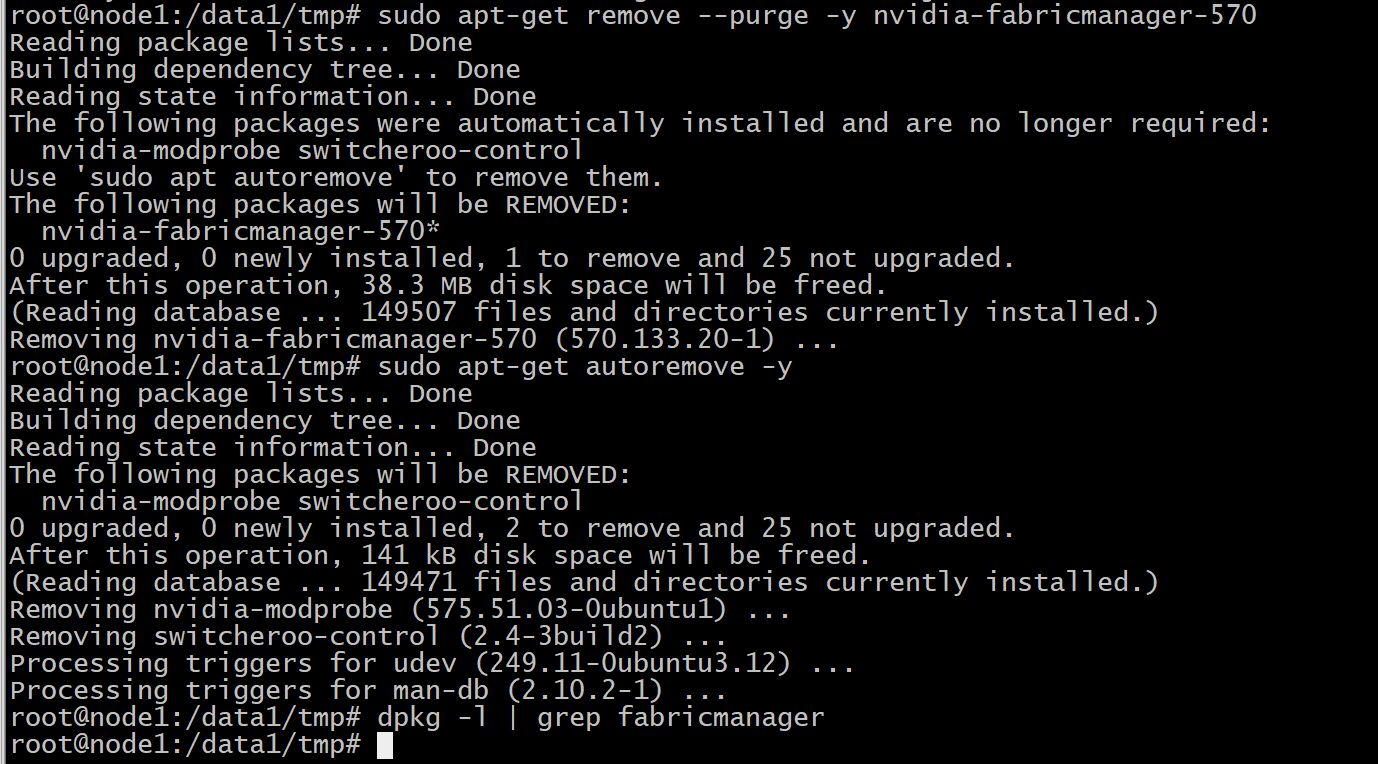

完整卸载 Fabric Manager 的方法

目录 ✅ 完整卸载 Fabric Manager 的方法 1️⃣ 停止并禁用服务 2️⃣ 卸载 Fabric Manager 软件包 3️⃣ 自动清理无用依赖(可选) 4️⃣ 检查是否卸载成功 ✅ 补充(仅清除服务,不删包) ✅ 完整卸载 Fabric Mana…...

地下停车场调频广播无线覆盖系统:融合精准选频光纤传输均匀覆盖于一体的创新型地下车库广播无线覆盖平台

地下停车场调频广播无线覆盖系统:融合精准选频光纤传输均匀覆盖于一体的创新型地下车库广播无线覆盖平台 北京海特伟业科技有限公司任洪卓发布于2025年5月16日 在现代城市建设中,地下停车场已成为商业综合体、写字楼、住宅区及交通枢纽的标配设施。然而…...

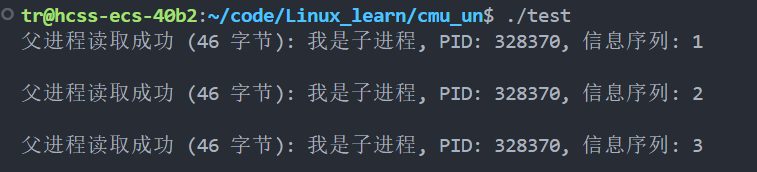

【Linux】进程间通信(一):认识管道

📝前言: 这篇文章我们来讲讲进程间通信——认识管道 🎬个人简介:努力学习ing 📋个人专栏:Linux 🎀CSDN主页 愚润求学 🌄其他专栏:C学习笔记,C语言入门基础&a…...

中大型水闸安全监测系统解决方案

一、方案概述 中大型水闸作为水利工程的重要组成部分,承担着调节水位、控制水流、防洪排涝等多重功能,在防洪减灾、水资源配置、生态环境改善等方面发挥着巨大作用。然而,由于历史原因,许多水闸存在建设标准偏低、质量较差、配套设…...

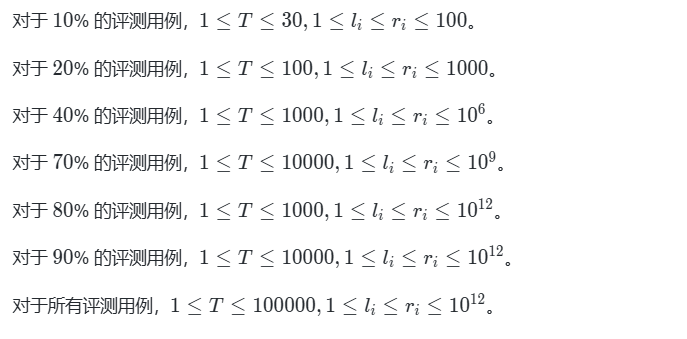

蓝桥杯12届国B 123

题目描述 小蓝发现了一个有趣的数列,这个数列的前几项如下: 1,1,2,1,2,3,1,2,3,4,⋯ 小蓝发现,这个数列前 1 项是整数 1,接下来 2 项是整数 1 至 2,接下来 3 项是整数 1 至 3,接下来 4 项是整数 1 至 4&…...

Harmony开发 List、Grid拖动自定义排序实现

1. Harmony开发 List、Grid拖动自定义排序实现 1.1. List拖动功能 本示例基于显式动画、List组件实现了ListItem的上下拖动、ListItem切换以及ListItem插入的效果。 实现思路:List手势拖动 @Entry @Component struct ListDragPage {@State private arr: string[] = [0, …...

迅龙3号基于兆讯MH22D3适配CST328多点触摸驱动开发笔记

MH22D3芯片是兆讯公司新推出的基于cortex-M3内核的新一代芯片,专注于显示应用,其主频高达216Mhz,64KB SRAM,512KB Flash,开发UI应用游刃有余。详细介绍请看:MH22D3新一代显控应用性价比之王 新龙微基于MH22…...

【001】.so文件分析之 ELF格式符号

.so 文件的结构标识主要依据 ELF 格式(Executable and Linkable Format) 一个 .so 文件其实是一个 ELF(可执行与可链接格式) 文件,里面包含多个结构标识符和段(Sections)用于支持动态加载、符号…...

QT之LayOut布局

文章目录 QFormLayoutQGridLayoutQFormLayout、QGridLayout、QHBoxLayout、QVBoxLayout综合案例用QFormLayout 代替 界面左边部分的QGridLayout QFormLayout #include "widget.h"#include <QFormLayout> #include <QLineEdit>Widget::Widget(QWidget *p…...

无需配置光猫,使用网管交换机配合路由器的IPTV功能实现单线复用

一、背景 弱电箱和电视柜只预留了一根网线,路由器放在电视柜,想实现既可以上网又可以正常观看iptv,本文提供了一种方法。 二、准备工作 1、带iptv功能的路由器;2、水星sg105pro网管交换机;3、网线若干; …...

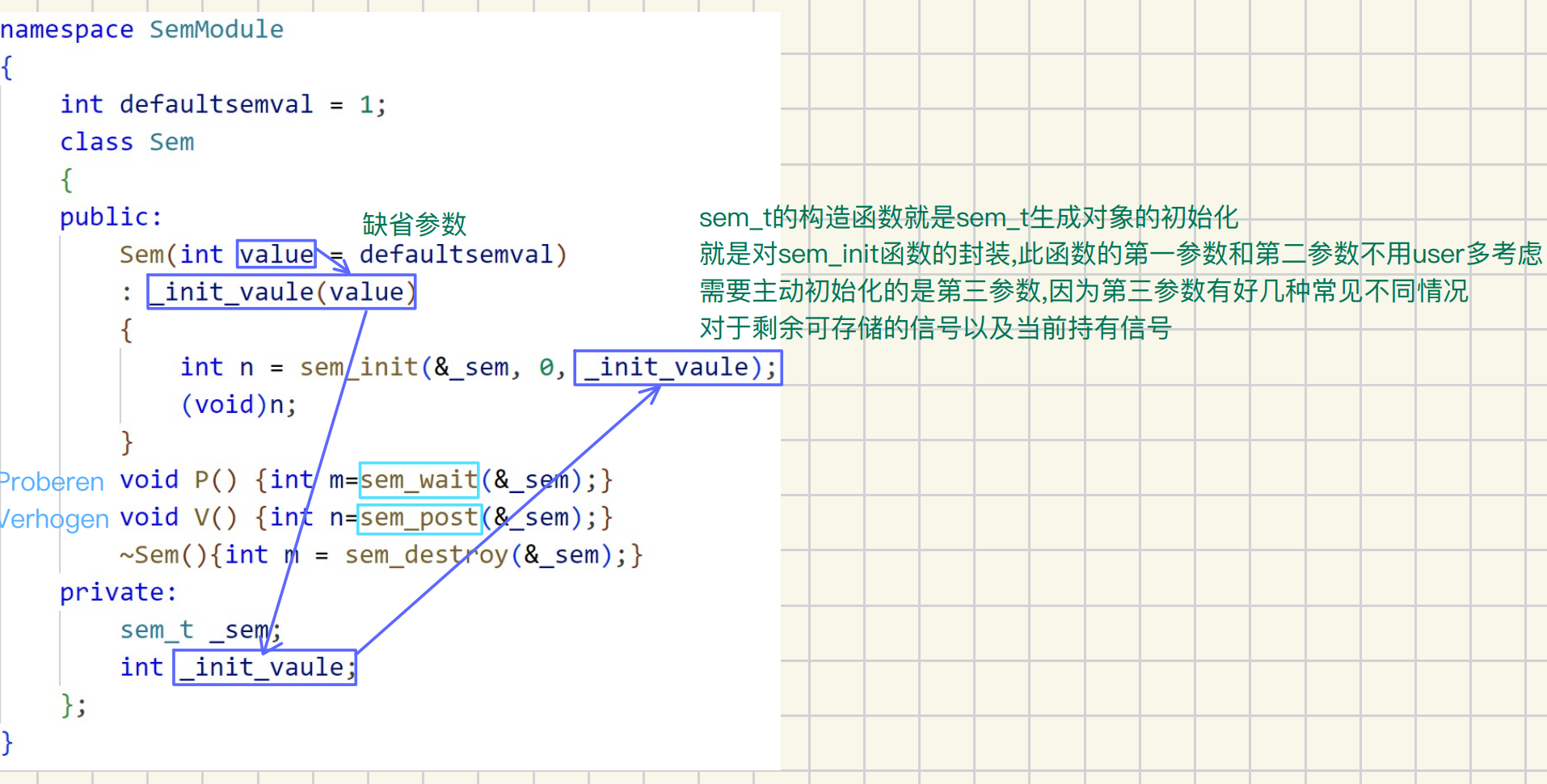

C++类与对象--1 特性一:封装

C面向对象三大特性: (1)封装;(2)继承;(3)多态; C认为万物皆是对象,对象上有对应的属性(数据)和行为(方法&…...

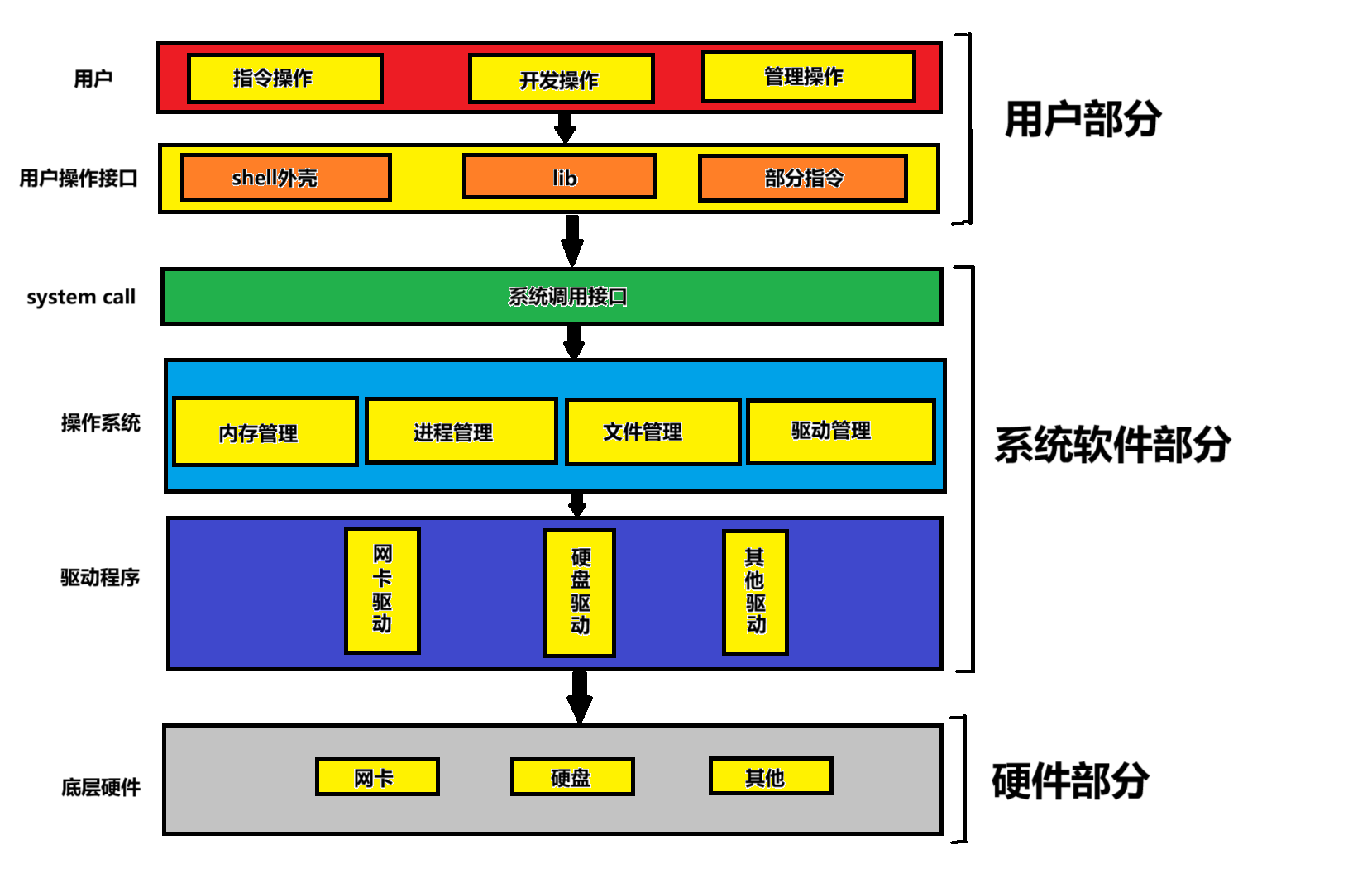

Linux:计算机的层状结构

1.冯诺依曼体系结构 我们常见的计算机,如笔记本、台式机。我们不常见的计算机,如服务器,大部分都遵守冯诺依曼体系结构。 CPU:运算器和控制器组成。运算器主要工作是做算术运算和逻辑运算。控制器主要工作是协调设备之间信息流动的…...

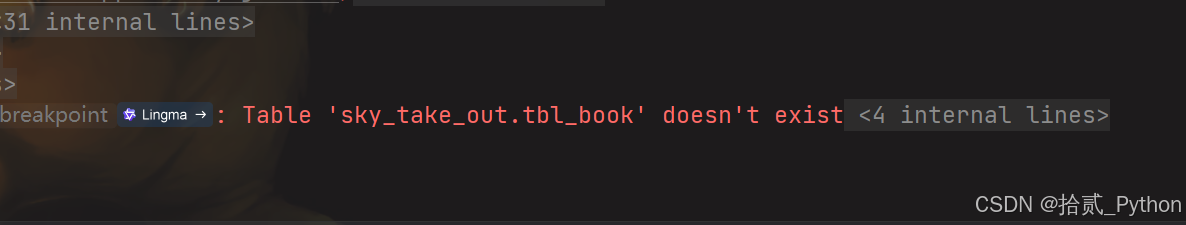

【SpringBoot】关于MP使用中配置了数据库表前缀的问题

problem 使用MP时,在application.yml配置文件中配置了MP匹配数据库表中的表名时的前缀作了规定,如下: 那么当我运行时报错了错误,报错信息如下: 因为我数据库表的书类表名是book,MP在匹配时使用了表名前…...

AI 赋能防艾宣传:从创意到实践,我的 IP 形象设计之旅

在数字技术飞速发展的今天,如何让严肃的健康传播变得更有温度、更具吸引力?作为一名参与防艾宣传实践的学生,我尝试通过 AI 工具构建专属 IP 形象,让防艾知识从 "被动接受" 转化为 "主动探索"。这篇文章将分享…...

Redis 事务与管道:原理、区别与应用实践

在现代分布式系统开发中,Redis 作为高性能的内存数据库,其事务处理和管道技术是开发者必须掌握的核心知识点。本文将深入探讨 Redis 事务和管道的实现原理、使用场景、性能差异以及最佳实践,帮助开发者根据实际需求选择合适的技术方案。 一、…...

每日算法刷题Day9 5.17:leetcode定长滑动窗口3道题,用时1h

9. 1652.拆炸弹(简单,学习) 1652. 拆炸弹 - 力扣(LeetCode) 思想 为了获得正确的密码,你需要替换掉每一个数字。所有数字会 同时 被替换。 如果 k > 0 ,将第 i 个数字用 接下来 k 个数字之和替换。如果 k < 0…...

手机打电话时如何将通话对方的声音在手机上识别成文字

手机打电话时如何将通话对方的声音在手机上识别成文字 --本地AI电话机器人 上一篇:手机打电话时由对方DTMF响应切换多级IVR语音应答(一) 下一篇:手机打电话时由对方DTMF响应切换多级IVR语音应答(二) 一、…...

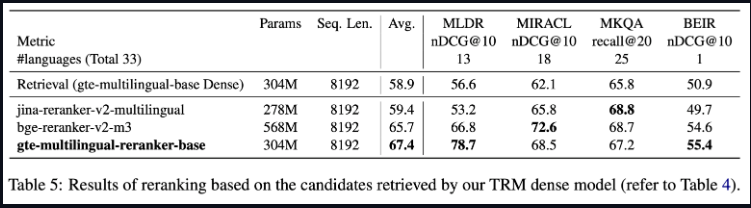

重排序模型解读:gte-multilingual-reranker-base 首个GTE系列重排模型诞生

模型介绍 gte-multilingual-reranker-base 模型是 GTE 模型系列中的第一个 reranker 模型,由阿里巴巴团队开发。 模型特征: Model Size: 306MMax Input Tokens: 8192 benchmark 关键属性: 高性能:与类似大小的 reranker 模型…...

C++学习:六个月从基础到就业——C++11/14:列表初始化

C学习:六个月从基础到就业——C11/14:列表初始化 本文是我C学习之旅系列的第四十三篇技术文章,也是第三阶段"现代C特性"的第五篇,主要介绍C11/14中的列表初始化特性。查看完整系列目录了解更多内容。 引言 在C11之前&a…...

SQL语句执行问题

执行顺序 select [all|distinct] <目标列的表达式1> AS [别名], <目标列的表达式2> AS [别名]... from <表名1或视图名1> [别名],<表名2或视图名2> [别名]... [where <条件表达式>] [group by <列名>] [having <条件表达式>] [ord…...

)

2025系统架构师---选择题知识点(押题)

1.《计算机信息系统安全保护等级划分准则》(GB 17859-1999)由低到高定义了五个不同级别的计算机系统安全保护能力。 第一级:用户自主保护级---通过隔离用户与数据实现访问控制,保护用户信息安全; 第二级:系统审计保护级---实施更细粒度的访问控制,通过审计和隔离资源确…...

flutter flutter run 运行项目卡在Running Gradle task ‘assembleDebug‘...

flutter run --verbose在运行flutter run 可以看到是卡在哪一步 最重要的就是自己查看日志,具体哪一步有问题flutter run --verbose使用这个,运行了项目会将错误信息放在控制台 可能原因 静态资源问题如果:图片、字体文件等没有在pubspec.yam…...

P5682 [CSP-J2019 江西] 次大值

P5682 [CSP-J2019 江西] 次大值 题目描述 Alice 有 n n n 个正整数,数字从 1 ∼ n 1 \sim n 1∼n 编号,分别为 a 1 , a 2 , … , a n a_1,a_2, \dots , a_n a1,a2,…,an。 Bob 刚学习取模运算,于是便拿这 n n n 个数进行练习&…...

Elasticsearch 性能优化面试宝典

Elasticsearch 性能优化面试宝典 🚀 目录 设计调优 🏗️写入调优 ⚡查询调优 🔍综合设计 💎总结 📝设计调优 🏗️ 面试题1:索引设计优化 题目: 假设需要设计一个电商商品索引,日增数据量1TB,要求支持多维度查询(名称、分类、价格区间)。请说明索引设计的关…...

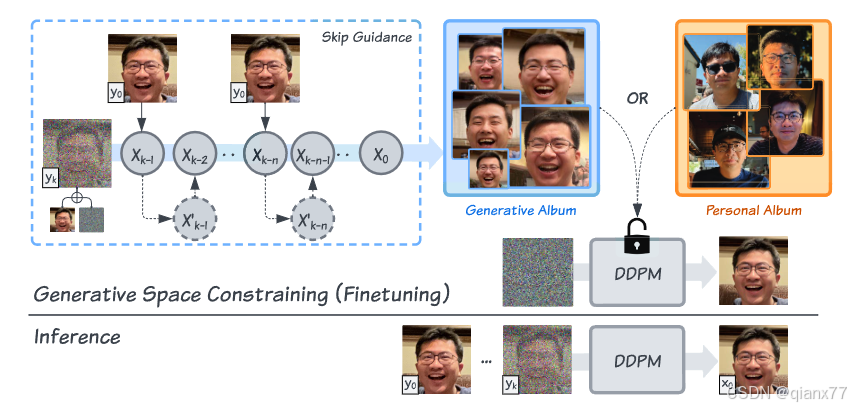

【论文阅读】人脸修复(face restoration ) 不同先验代表算法整理2

文章目录 一、前述二、不同的先验及代表性论文2.1 几何先验(Geometric Prior)2.2 生成式先验(Generative Prior)2.3 codebook先验(Vector Quantized Codebook Prior)2.4 扩散先验 (Diffusion Pr…...

无监督学习在医疗AI领域的前沿:多模态整合、疾病亚型发现与异常检测

引言 人工智能技术在医疗领域的应用正经历着从辅助决策向深度赋能的转变。无监督学习作为人工智能的核心范式之一,因其无需大量标注数据、能够自动发现数据内在规律的特性,在医疗AI领域展现出独特优势。尤其在2025年,无监督学习技术在医疗AI应用中呈现出多模态整合、疾病亚…...

计算机操作系统概要

不谋万世者,不⾜谋⼀时。不谋全局者 ,足谋⼀域 。 ——陈澹然《寤⾔》《迁都建藩议》 操作系统 一.对文件简单操作的常用基础指令 ls ls 选项 目录或⽂件名:罗列当前⽬录下的⽂件 -l:以长格式显示⽂件和⽬录的详细信息 -a 或 --all&…...

C语言进阶-数组和函数

C语言 一、数组 一维数组 通过数组,可以一次性的分配多个同类型的连续存储区 语法: 类型 数组名字[元素个数]; 例:int arr[6]; arr占用内存6个整型大小的连续存储空间 注意: 通过下标可以区分数组的每个…...