FPGA项目实现:秒表设计

文章目录

- 项目要求

- 项目设计

项目要求

设计一个时钟秒表,共六个数码管,前两位显示分钟,中间两位显示时间秒,后两位显示毫秒的高两位,可以通过按键来开始、暂停以及重新开始秒表的计数。

项目设计

为完成此项目共设计四个模块,按键消抖模块、时钟计时器模块、数码管显示模块以及顶层文件模块,详细代码设计如下:

按键消抖模块:

/** @Description: 按键销抖模块(延迟方法销抖)* @Author: Fu Yu* @Date: 2023-08-01 14:31:19* @LastEditTime: 2023-08-01 16:29:44* @LastEditors: Fu Yu*/module key_filter (input wire clk ,input wire rst_n ,input wire key_in ,//按键输入,低有效output wire key_down //按键输出,高有效

);parameter MAX_20MS = 20'd999_999;//20msreg key_r;//同步

reg key_r1;//打拍

reg key_r2;

wire nedge;//下降沿reg key_down_r;//保存key_down信号reg [19:0] cnt_20ms;

reg flag;//计数开始标志信号

wire add_cnt_20ms;

wire end_cnt_20ms;//****************************************************************

//--同步打拍,检测下降沿

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginkey_r <= 1'b1;key_r1 <= 1'b1;key_r2 <= 1'b1;endelse beginkey_r <= key_in;key_r1 <= key_r;key_r2 <= key_r1;end

end//下降沿检测

assign nedge = ~key_r1 & key_r2;//****************************************************************

//--flag信号定义

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginflag <= 1'b0;endelse if(nedge) beginflag <= 1'b1;endelse if(end_cnt_20ms) beginflag <= 1'b0;endelse beginflag <= flag;end

end//****************************************************************

//--计数

//****************************************************************

always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_20ms <= 20'd0;end else if(add_cnt_20ms)begin if(end_cnt_20ms)begin cnt_20ms <= 20'd0;endelse begin cnt_20ms <= cnt_20ms + 1'b1;end end

end assign add_cnt_20ms = flag;

assign end_cnt_20ms = add_cnt_20ms && cnt_20ms == MAX_20MS;//****************************************************************

//--key_down

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginkey_down_r <= 1'b0;endelse if(end_cnt_20ms) beginkey_down_r <= ~key_r2;endelse beginkey_down_r <= 1'b0;end

endassign key_down = key_down_r;endmodule //key_filter

时钟计时器模块:

/** @Description: 通过输入的按键控制计数开始与暂停,实现秒表设计(毫秒、秒、分计时)* @Author: Fu Yu* @Date: 2023-08-01 14:46:43* @LastEditTime: 2023-08-01 15:53:12* @LastEditors: Fu Yu*/module counter_time (input wire clk ,input wire rst_n ,input wire key_in ,//销抖后的脉冲信号,高有效output wire [23:0] din_out //输出当前计数的值

);parameter MAX_1MS = 16'd49_999;//1ms

parameter MAX_1S = 10'd999;//1ms*1000 = 1s

parameter MAX_1MIN = 6'd59;//1s*60 = 1min

parameter MAX_1H = 6'd59;//1min*60 = 1hreg flag;//开始、暂停结束信号reg [15:0] cnt_1ms;

wire add_cnt_1ms;

wire end_cnt_1ms;reg [9:0] cnt_1s;

wire add_cnt_1s;

wire end_cnt_1s;reg [5:0] cnt_1min;

wire add_cnt_1min;

wire end_cnt_1min;reg [5:0] cnt_1h;

wire add_cnt_1h;

wire end_cnt_1h;reg [7:0] data_min;//保存此时有多少分钟

reg [7:0] data_s;//保存此时有多少秒

reg [7:0] data_ms;//保存此时有多少毫秒,只取高两位//****************************************************************

//--flag

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginflag <= 1'b0;endelse if (key_in) beginflag <= ~flag;endelse beginflag <= flag;end

end//****************************************************************

//--1ms计数器

//****************************************************************

always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1ms <= 16'd0;end else if(add_cnt_1ms)begin if(end_cnt_1ms)begin cnt_1ms <= 16'd0;endelse begin cnt_1ms <= cnt_1ms + 1'b1;end end

end assign add_cnt_1ms = flag;

assign end_cnt_1ms = add_cnt_1ms && cnt_1ms == MAX_1MS;//****************************************************************

//--1s计数器

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1s <= 10'd0;end else if(add_cnt_1s)begin if(end_cnt_1s)begin cnt_1s <= 10'd0;endelse begin cnt_1s <= cnt_1s + 1'b1;end end

end assign add_cnt_1s = end_cnt_1ms;

assign end_cnt_1s = add_cnt_1s && cnt_1s == MAX_1S ;

//&& end_cnt_1ms//****************************************************************

//--1min计数器

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1min <= 6'd0;end else if(add_cnt_1min)begin if(end_cnt_1min)begin cnt_1min <= 6'd0;endelse begin cnt_1min <= cnt_1min + 1'b1;end end

end assign add_cnt_1min = end_cnt_1s;

assign end_cnt_1min = add_cnt_1min && cnt_1min == MAX_1MIN ;

//&& end_cnt_1s

//****************************************************************

//--1h计数器

//****************************************************************

always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1h <= 6'd0;end else if(add_cnt_1h)begin if(end_cnt_1h)begin cnt_1h <= 6'd0;endelse begin cnt_1h <= cnt_1h + 1'b1;end end

end assign add_cnt_1h = end_cnt_1min;

assign end_cnt_1h = add_cnt_1h && cnt_1h == MAX_1H;

// && end_cnt_1min

//****************************************************************

//--din_out

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begindata_min <= 8'd0;data_s <= 8'd0;data_ms <= 8'd0;endelse begindata_min <= cnt_1h;data_s <= cnt_1min;data_ms <= cnt_1s/10;end

endassign din_out = {data_min,data_s,data_ms};endmodule //counter_time

数码管显示模块:

/** @Description: 数码管显示时钟,前两位显示分钟,中间两位显示秒,最后两位显示毫秒* @Author: Fu Yu* @Date: 2023-08-01 15:19:52* @LastEditTime: 2023-08-01 16:22:40* @LastEditors: Fu Yu*/module seg_sel (input wire clk ,input wire rst_n ,input wire [23:0] din ,output wire [5:0] sel ,//位选信号output wire [7:0] dig //段选信号

);parameter MAX_1MS = 16'd49_999;//1msparameter ZERO = 7'b100_0000,ONE = 7'b111_1001,TWO = 7'b010_0100,THREE = 7'b011_0000,FOUR = 7'b001_1001,FIVE = 7'b001_0010,SIX = 7'b000_0010,SEVEN = 7'b111_1000,EIGHT = 7'b000_0000,NINE = 7'b001_0000;reg [5:0] point_n;//小数点位置

reg point_n_r;reg [15:0] cnt_1ms;

wire add_cnt_1ms;

wire end_cnt_1ms;reg [5:0] sel_r;

reg [7:0] dig_r;

reg [3:0] disp_data ;//每一位数码管显示的数值//****************************************************************

//--1ms计数器

//****************************************************************

always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1ms <= 16'd0;end else if(add_cnt_1ms)begin if(end_cnt_1ms)begin cnt_1ms <= 16'd0;endelse begin cnt_1ms <= cnt_1ms + 1'b1;end end

end assign add_cnt_1ms = 1'b1;

assign end_cnt_1ms = add_cnt_1ms && cnt_1ms == MAX_1MS;//****************************************************************

//--小数点

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginpoint_n <= 6'b111111;endelse beginpoint_n <= 6'b110101;end

end//****************************************************************

//--sel信号

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginsel_r <= 6'b111110;endelse if(end_cnt_1ms) beginsel_r <= {sel_r[4:0],sel_r[5]};//循环左移end

endassign sel = sel_r;//****************************************************************

//--disp_data

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)begindisp_data <= 'd0;point_n_r <= 1'b1;end else begin case (sel_r)6'b111_110 : begin disp_data <= din[23:16]/10 ; point_n_r <= point_n[0]; end//第一位数码管显示的数值6'b111_101 : begin disp_data <= din[23:16]%10 ; point_n_r <= point_n[1]; end6'b111_011 : begin disp_data <= din[15:8]/10 ; point_n_r <= point_n[2]; end6'b110_111 : begin disp_data <= din[15:8]%10 ; point_n_r <= point_n[3]; end6'b101_111 : begin disp_data <= din[7:0]/10 ; point_n_r <= point_n[4]; end6'b011_111 : begin disp_data <= din[7:0]%10 ; point_n_r <= point_n[5]; enddefault: disp_data <= 'd0;endcaseend end//****************************************************************

//--dig

//****************************************************************

always @(*)begin case (disp_data)0 : dig_r <= {point_n_r,ZERO };1 : dig_r <= {point_n_r,ONE };2 : dig_r <= {point_n_r,TWO };3 : dig_r <= {point_n_r,THREE };4 : dig_r <= {point_n_r,FOUR };5 : dig_r <= {point_n_r,FIVE };6 : dig_r <= {point_n_r,SIX };7 : dig_r <= {point_n_r,SEVEN };8 : dig_r <= {point_n_r,EIGHT };9 : dig_r <= {point_n_r,NINE };default: dig_r <= 8'hff;endcaseendassign dig = dig_r;endmodule //seg_sel顶层文件模块:

module top (input wire clk ,input wire rst_n ,input wire key_in ,output wire [5:0] sel ,output wire [7:0] dig

);wire key;

wire [23:0] data;key_filter u_key_filter(. clk (clk) ,. rst_n (rst_n),. key_in (key_in),. key_down (key)

);counter_time u_counter_time(. clk (clk) ,. rst_n (rst_n) ,. key_in (key) ,. din_out (data)

);seg_sel u_seg_sel(. clk (clk) ,. rst_n (rst_n) ,. din (data) ,. sel (sel) ,. dig (dig)

);endmodule //top

效果展示:

秒表

相关文章:

FPGA项目实现:秒表设计

文章目录 项目要求项目设计 项目要求 设计一个时钟秒表,共六个数码管,前两位显示分钟,中间两位显示时间秒,后两位显示毫秒的高两位,可以通过按键来开始、暂停以及重新开始秒表的计数。 项目设计 为完成此项目共设计…...

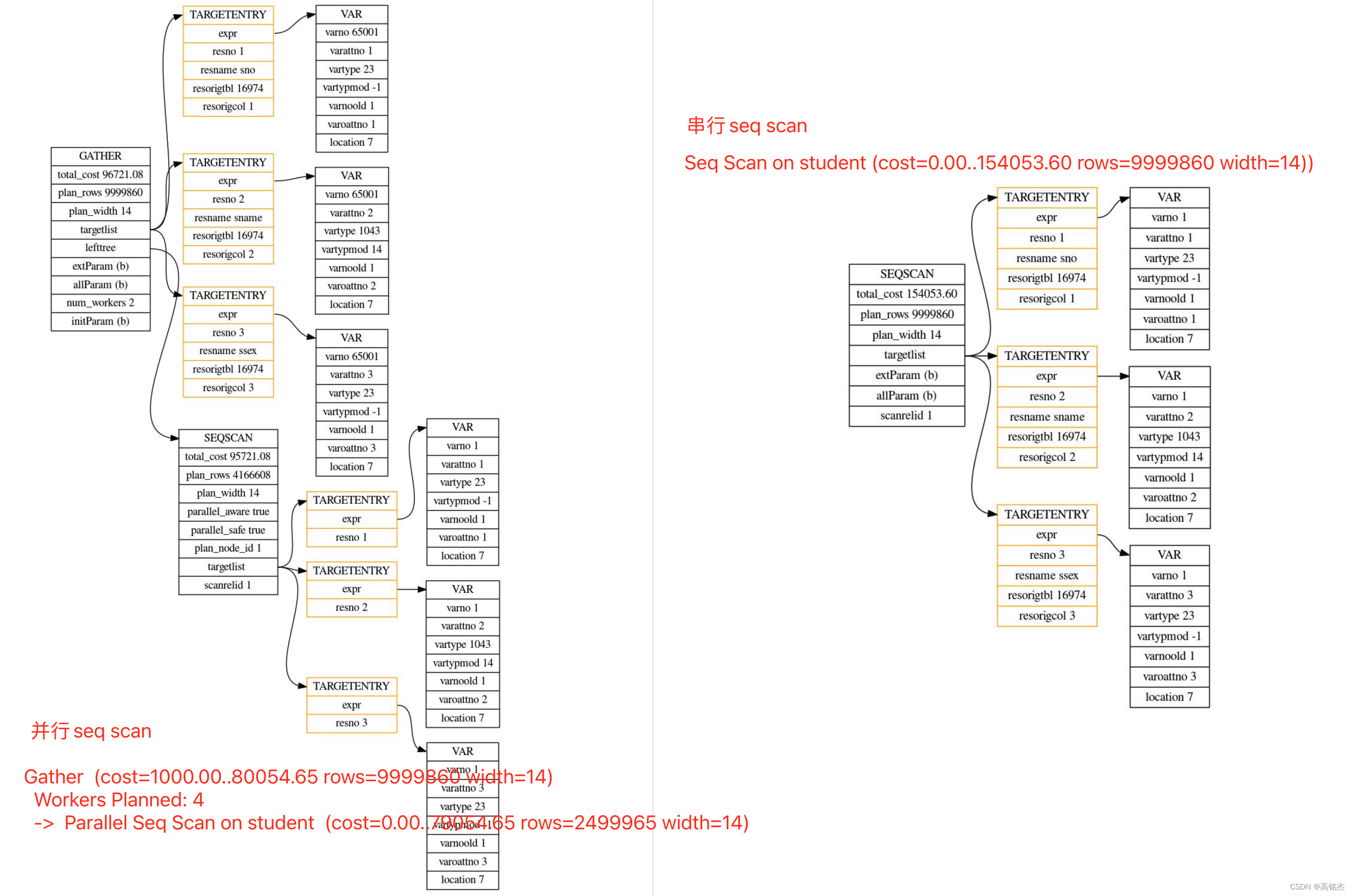

Postgresql源码(109)并行框架实例与分析

1 PostgreSQL并行参数 系统参数 系统总worker限制:max_worker_processes 默认8 系统总并发限制:max_parallel_workers 默认8 单Query限制:max_parallel_workers_per_gather 默认2 表参数限制:parallel_workers alter table tbl …...

ES派生类的prototype方法中,不能访问super的解决方案

1 下面的B.prototype.compile方法中,无法访问super class A {compile() {console.log(A)} }class B extends A {compile() {super.compile()console.log(B)} }B.prototype.compile function() {super.compile() // 报错,不可以在此处使用superconsole.…...

使用adb通过电脑给安卓设备安装apk文件

最近碰到要在开发板上安装软件的问题,由于是开发板上的安卓系统没有解析apk文件的工具,所以无法通过直接打开apk文件来安装软件。因此查询各种资料后发现可以使用adb工具,这样一来可以在电脑上给安卓设备安装软件。 ADB 就是连接 Android 手…...

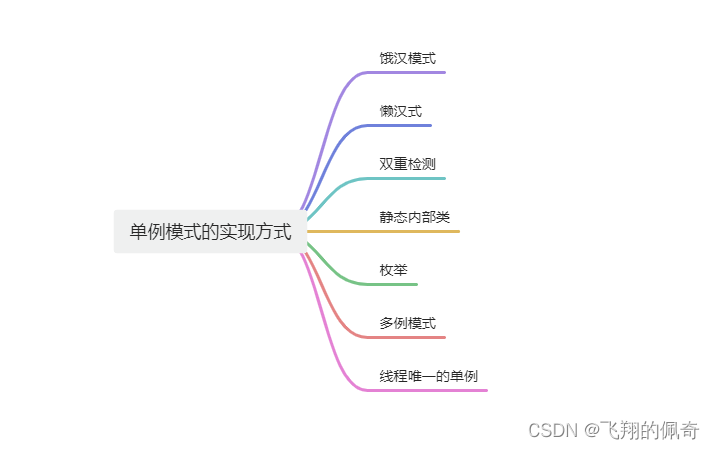

113、单例Bean是单例模式吗?

单例Bean是单例模式吗? 通常来说,单例模式是指在一个JVM中,一个类只能构造出来一个对象,有很多方法来实现单例模式,比如懒汉模式,但是我们通常讲的单例模式有一个前提条件就是规定在一个JVM中,那如果要在两个JVM中保证单例呢?那可能就要用分布式锁这些技术,这里的重点…...

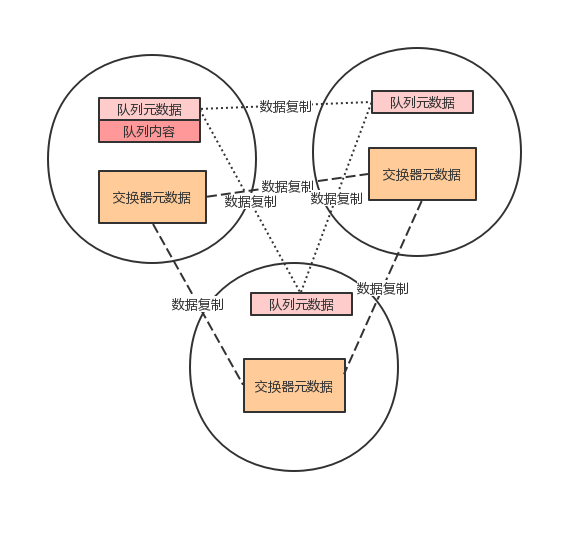

RabbitMQ 集群部署

RabbiMQ 是用 Erlang 开发的,集群非常方便,因为 Erlang 天生就是一门分布式语言,但其本身并不支持负载均衡。 RabbitMQ 的集群节点包括内存节点、磁盘节点。RabbitMQ 支持消息的持久化,也就是数据写在磁盘上,最合适的方案就是既有内存节点,又有磁盘节点。 RabbitMQ 模式大…...

2023年【零声教育】13代C/C++Linux服务器开发高级架构师课程体系分析

对于零声教育的C/CLinux服务器高级架构师的课程到2022目前已经迭代到13代了,像之前小编也总结过,但是课程每期都有做一定的更新,也是为了更好的完善课程跟上目前互联网大厂的岗位技术需求,之前课程里面也包含了一些小的分支&#…...

iOS开发-实现热门话题标签tag显示控件

iOS开发-实现热门话题标签tag显示控件 话题标签tag显示非常常见,如选择你的兴趣,选择关注的群,超话,话题等等。 一、效果图 二、实现代码 由于显示的是在列表中,这里整体控件是放在UITableViewCell中的。 2.1 标签…...

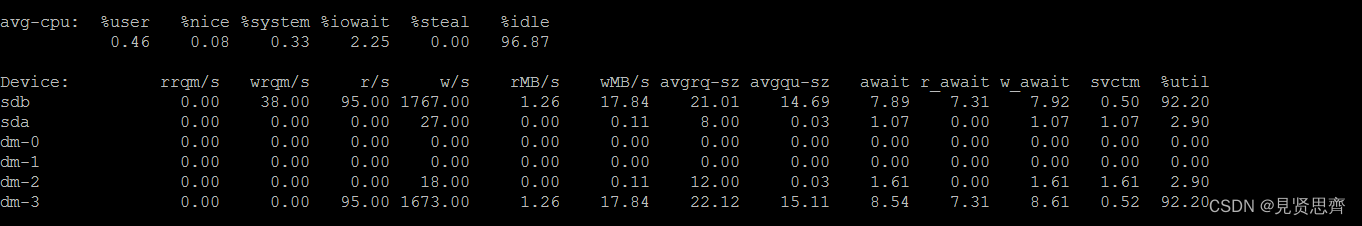

linux系统磁盘性能监视工具iostat

目录 一、iostat介绍 二、命令格式 三、命令参数 四、参考命令:iostat -c -x -k -d 1 (一)输出CPU 属性值 (二)CPU参数分析 (三)磁盘每一列的含义 (四)磁盘参数分…...

BT#蓝牙 - Link Policy Settings

对于Classic Bluetooth的Connection,有一个Link_Policy_Settings,是HCI configuration parameters中的一个。 Link_Policy_Settings 参数决定了本地链路管理器(Link Manager)在收到来自远程链路管理器的请求时的行为,还用来决定改变角色(rol…...

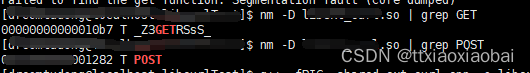

c++ | 动态链接库 | 小结

//环境 linux c //生成动态链接库 //然后调用动态链接库中的函数//出现的问题以及解决//注意在win和在linux中调用动态链接库的函数是不一样的//在要生成链接库的cpp文件中比如以后要调用本文件中的某个函数,需要extern "c" 把你定的函数“再封装”避免重…...

如何使用Flask-SQLAlchemy来管理数据库连接和操作数据?

首先,我们需要安装Flask-SQLAlchemy。你可以使用pip来安装它,就像这样: pip install Flask-SQLAlchemy好了,现在我们已经有了一个可以操作数据库的工具,接下来让我们来看看如何使用它吧! 首先,…...

麒麟-飞腾Kylin-V4桌面arm64系统静态编译QT

1.系统具体版本: 2. 因为此版本的源很老了,需要修改版本的源,才能正常更新各种软件,否则,你连麒麟商店都打不开。 sudo vi /etc/apt/sources.list 选择你系统对应版本的源地址: #4.0.2桌面版本: deb ht…...

CentOS 项目发出一篇奇怪的博文

导读最近,在红帽限制其 RHEL 源代码的访问之后,整个社区围绕这件事发生了很多事情。 CentOS 项目发出一篇奇怪的博文 周五,CentOS 项目董事会发出了一篇模糊不清的简短博文,文中称,“发展社区并让人们更容易做出贡献…...

【Mybatis-Plus】or拼接

Mybatis-Plus的or拼接是个坑: 这是需要的结果: queryWrapper.and(c->c.or(a->a.eq("qcs3.status", "SIGNING").eq("qcs.status", "SIGNING")).or(b->b.eq("qcs.status","INVALIDING&q…...

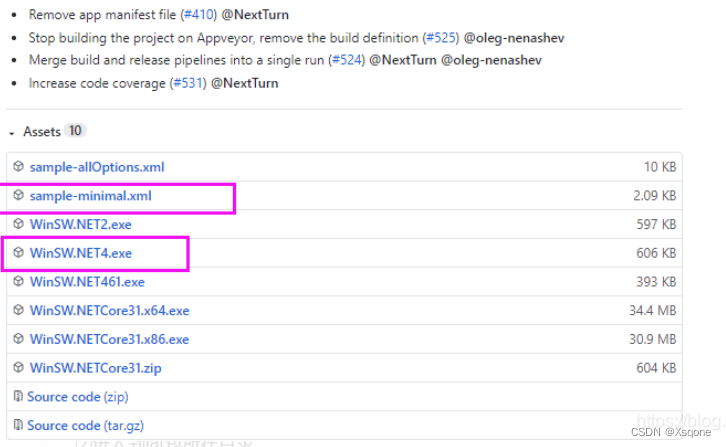

SpringBoot项目部署在Windows与Centos上

文章目录 Windows部署一、github上下载文件winsw二、文件目录三、编辑xml文件四、安装服务五、启动服务六、把jar包放到项目外面七、添加限制内存 Linux部署一、准备二、服务三、操作 Windows部署 windows部署服务借鉴于此篇博文 一、github上下载文件winsw 点击链接下载下图…...

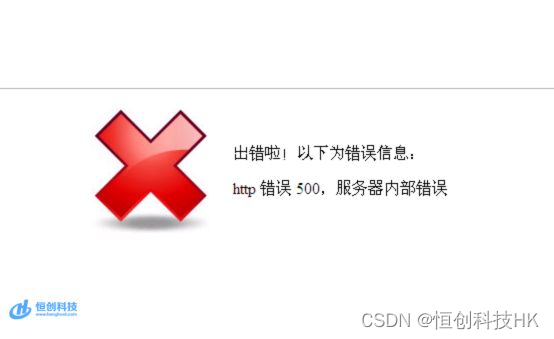

网站服务器出错的原因分析和解决方法

网站在日常运行的过程中,难免会遇见一些问题,这次我们就来分析关于网站服务器出错、服务器异常的原因以及如何解决网站服务器错误的方法。 如何知道是网站服务器的问题呢? 只要网站不能正常访问运行,那么一定会反馈相关的错误代码和原…...

电影推荐系统】系统初步搭建及离线个性化推荐

上篇博文我们已经写完统计推荐部分,现在我们将使用VueElement-uiSpringBoot来快速搭建系统,展示出电影,并介绍个性化推荐部分。 1 系统页面设计 初步是想设计一个类似豆瓣电影推荐系统 用户登陆后,可以查看高分电影可以查看推荐…...

Redis 集群 (cluster)

是什么 官网:Redis cluster specification | Redis 由于数据量过大,单个Master复制集难以承担,因此需要对多个复制集进行集群,形成水平扩展每个复制集只负责存储整个数据集的一部分,这就是Redis的集群,其作…...

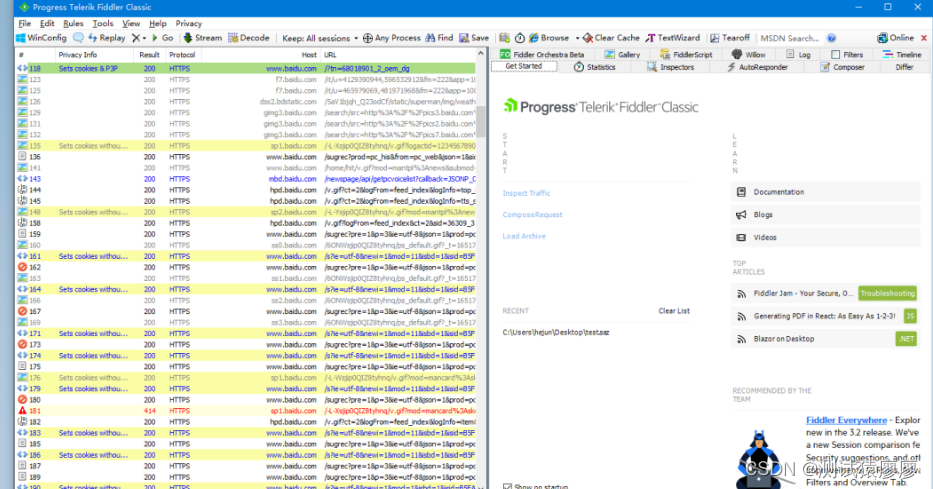

《吐血整理》进阶系列教程-拿捏Fiddler抓包教程(19)-Fiddler精选插件扩展安装,将你的Fiddler武装到牙齿

1.简介 Fiddler本身的功能其实也已经很强大了,但是Fiddler官方还有很多其他扩展插件功能,可以更好地辅助Fiddler去帮助用户去开发、测试和管理项目上的任务。Fiddler已有的功能已经够我们日常工作中使用了,为了更好的扩展Fiddler,…...

)

【信息科学与工程学】计算机科学与自动化 第十篇 芯片设计04(5)

载流子统计与输运函数方程式详表 1. 载流子统计基础 (zailiu-1 ~ zailiu-100) 序号 名称 数学表达式/核心描述 参数说明 物理意义 应用场景 条件描述 zailiu-1 麦克斯韦-玻尔兹曼分布 f(E)=Ae−E/(kBT)或 f(v)=(2πkBTm)3/2e−mv2/(2kBT) E: 能量, v: 速度,…...

260513实训:路由器连接

路由器工作原理: 转发动作:路由器收到数据后,根据目的IP地址查路由器路由表(地图)转发 路由表:路由器默认会将直连网段加入路由表 查看IP路由表:display ip routing-table 127.0.0.0/8 本地环…...

3PEAK思瑞浦 TPA1811-SO1R SOP8 运算放大器

特性 供电电压:4伏至30伏 低功耗:25C时为55安培(典型值) 低偏移电压:25C时最大8V 零漂:0.01V/C 轨到轨输出 增益带宽积:500kHz 斜率:0.3V/us...

Taotoken助力初创团队以可控成本集成大模型能力

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 Taotoken助力初创团队以可控成本集成大模型能力 为产品添加智能对话功能是许多初创团队提升用户体验的关键一步。然而,…...

MacOS Telegram语音实时转译:本地化音频捕获与离线语音识别实践

1. 项目概述:一个为MacOS打造的Telegram语音实时转译工具如果你和我一样,经常在Telegram上参与多语言群组讨论,或者需要处理来自不同地区的语音消息,那么语言障碍绝对是一个头疼的问题。想象一下,你收到一条长达一分钟…...

量子振荡与拓扑输运调控:从实验测量到主动驾驭

1. 项目概述:从“驾驭”一词说起“如何在量子振荡中驾驭拓扑量子输运?”——当我第一次看到这个问题时,脑海里浮现的不是复杂的公式,而是一个更形象的画面:你驾驶着一艘小船,航行在一片由无数微小漩涡&…...

GenAIScript:用脚本化AI工作流提升代码生成效率与工程化实践

1. 项目概述:当AI遇上代码生成,GenAIScript带来了什么?如果你最近在关注AI如何改变开发工作流,特别是微软在AI领域的动作,那么microsoft/genaiscript这个项目绝对值得你花时间深入研究。这不仅仅是一个简单的代码生成工…...

LZ4并行压缩:线程池设计与性能瓶颈突破的终极指南

LZ4并行压缩:线程池设计与性能瓶颈突破的终极指南 【免费下载链接】lz4 Extremely Fast Compression algorithm 项目地址: https://gitcode.com/GitHub_Trending/lz/lz4 LZ4作为一款Extremely Fast Compression algorithm,其并行压缩能力是提升处…...

Freewall跨浏览器兼容性:解决IE8+布局问题的完整方案

Freewall跨浏览器兼容性:解决IE8布局问题的完整方案 【免费下载链接】freewall kombai/freewall: Freewall 是一个灵活、响应式的网格布局引擎,可用于创建具有自适应布局功能的网页或应用组件,尤其适合于图片墙、瀑布流布局等场景。 项目地…...

古吉拉特语TTS项目上线倒计时48小时!这份含11个合规性检查项的ElevenLabs交付清单请立刻保存

更多请点击: https://intelliparadigm.com 第一章:古吉拉特语TTS项目上线倒计时全景概览 古吉拉特语(Gujarati)作为印度西部广泛使用的官方语言,拥有超过 5500 万母语使用者,但其高质量、低延迟、可商用的…...