中科亿海微乘法器(LPMMULT)

引言

FPGA(可编程逻辑门阵列)是一种可在硬件级别上重新配置的集成电路。它具有灵活性和可重构性,使其成为处理各种应用的理想选择,包括数字信号处理、图像处理、通信、嵌入式系统等。在FPGA中,乘法器是一种重要的硬件资源。乘法器用于执行乘法运算,可以在数字信号处理、滤波、图像处理、嵌入式系统等领域中发挥关键作用。传统的乘法运算通常采用基于加法和移位的算法,但这些方法可能需要较长的计算时间,并且在某些应用中效率较低。为了提高计算效率,FPGA芯片通常会集成专门的乘法器资源。FPGA中的乘法器通常是基于二进制乘法算法实现的。这些乘法器可以支持不同大小的操作数,例如8位、16位、32位或更大。乘法器通常具有高速、低功耗和高精度的特点,能够在短时间内完成大量复杂的乘法运算。乘法器的设计和优化是FPGA开发中的重要课题之一。设计者需要考虑乘法器的延迟、功耗、面积占用和精度等因素,以满足特定应用的需求。同时,还可以通过并行计算、流水线技术和优化算法等方法来提高乘法器的性能和效率。

正文

技术概述

在电路中,乘法器是一种用于执行乘法运算的重要组件。它能够将两个输入数相乘,并输出它们的乘积。乘法器在数字信号处理、通信系统、图像处理等领域都有广泛的应用。乘法器的基本原理是基于二进制乘法算法。在二进制乘法中,每个位的乘积可以通过将一个数乘以另一个数的每一位,并将这些部分乘积相加来得到。例如,对于两个4位的二进制数A和B,其乘积可以通过计算A的每一位与B的每一位的乘积,并将这些部分乘积相加得到。乘法器通常采用布斯-加法器(Booth's algorithm)或Wallace树(Wallace tree)等算法来实现高效的乘法运算。这些算法利用了二进制数的特性,通过位移、加法和累加等操作来计算乘积。

FPGA(可编程逻辑门阵列)芯片中的乘法器是一种硬件资源,用于执行乘法运算。它是通过组合逻辑电路的方式来实现的。FPGA中的乘法器基本原理是基于二进制乘法算法。对于两个n位的二进制数A和B,乘法器会将A的每一位与B的每一位相乘,并将这些部分乘积相加得到最终结果。FPGA中的乘法器通常采用了布斯-加法器(Booth's algorithm)或Wallace树(Wallace tree)等高效的算法来实现。这些算法可以减少部分乘积的数量,从而提高计算效率。布斯-加法器是一种基于移位和加法操作来计算乘积的方法。它通过将乘法运算转化为一系列的加法和移位操作,从而实现高速的乘法计算。布斯-加法器通常采用串行或并行的方式来计算乘法结果。Wallace树是一种并行计算的乘法器实现方法。它通过将乘法运算分解为多个部分乘积的累加,从而实现更高的计算速度。Wallace树利用了并行计算的特性,可以同时计算多个部分乘积,提高乘法器的性能。除了布斯-加法器和Wallace树,FPGA中的乘法器还可以采用其他的优化技术和算法来提高计算效率和资源利用率。例如,可以使用部分乘积树、树型累加器等。

具体步骤或方法

-

二进制数表示:了解二进制数的表示方法,包括正数、负数和小数的表示方式。

-

二进制加法和移位:理解二进制数的加法运算和移位操作,这是乘法器实现中常用的基本操作。

-

布斯-加法器:布斯-加法器是一种优化的乘法器实现方法,通过减少乘法器中的部分乘积数量,从而提高计算效率。

-

Wallace树:Wallace树是一种并行计算的乘法器实现方法,通过将乘法运算分解为多个部分乘积的累加来提高计算速度。

-

乘法器的延迟和面积:了解乘法器的延迟(计算时间)和面积(硬件资源占用)之间的权衡关系,以及如何进行设计和优化。

使用Verilog编写的布斯-乘法器的示例代码:

module CFQ(clk, reset, load, A, B, done, result);

parameter WidthMultiplicand = 16,

WidthMultiplier = 16,

WidthCount = 5,

Comp_add = 3'b010,

Add = 3'b001;input clk, reset, load;input [WidthMultiplicand-1:0] A;input [WidthMultiplier-1:0] B;output [WidthMultiplicand+WidthMultiplier-1:0] result;output done; reg done, sign, E, shift, Qn_1;reg [WidthMultiplicand-1:0] regA;reg [WidthMultiplier-1:0] regB, regQ;reg [WidthCount-1:0] SeqCount;assign result = {regA,regQ};always @(posedge clk) beginif(!reset) beginregA = 0;regB = 0;regQ = 0;Qn_1 = 0;shift = 0;SeqCount = WidthMultiplier;done = 0;endelse if (load) beginregA = 0;regB = A;regQ = B;Qn_1 = 0;shift = 0;SeqCount = WidthMultiplier;done = 0;endelse if (!done) case({shift,regQ[0],Qn_1})Comp_add:beginregA = regA + ~regB + 1;shift = 1;endAdd:beginregA = regA + regB;shift = 1;enddefault:begin{regA,regQ,Qn_1} = ({regA,regQ,Qn_1}>>1);regA[WidthMultiplicand-1] = regA[WidthMultiplicand-2];SeqCount = SeqCount - 1;shift = 0;if (SeqCount == 0)done = 1;endendcase endendmodule 实验结果

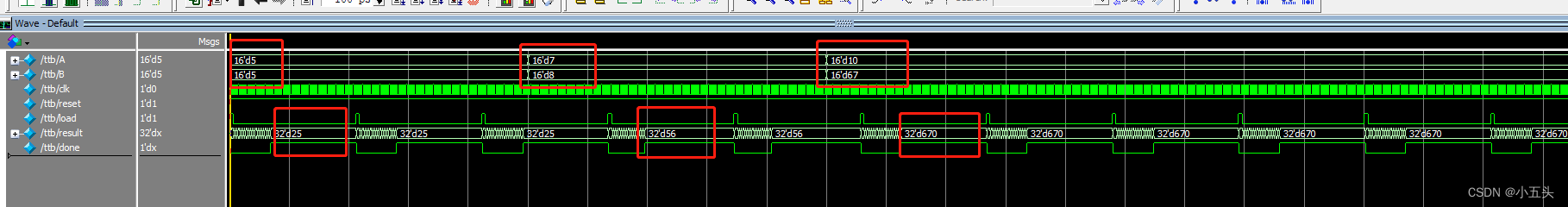

使用eLinx工具开发:

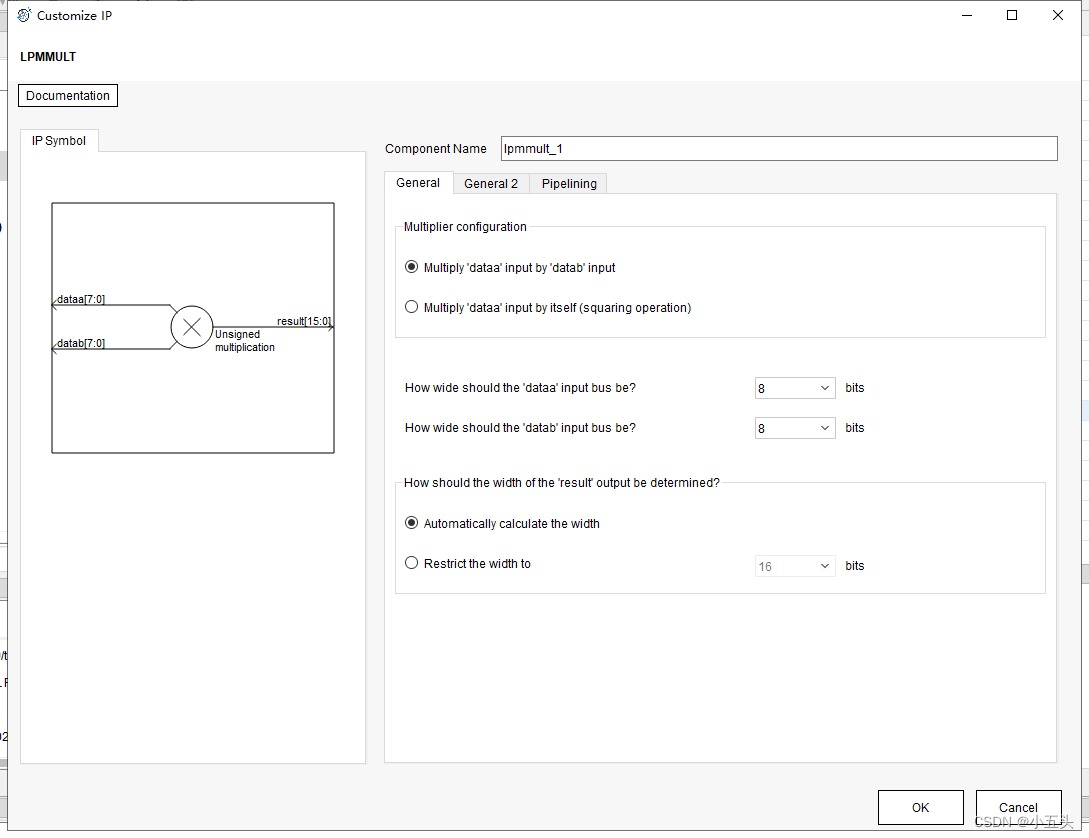

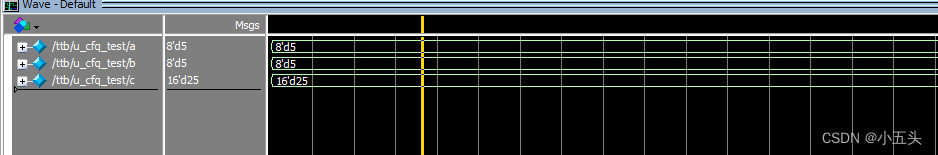

module cfq_test(input wire clk);wire [7:0] a= 5;wire [7:0] b= 5;wire [15:0] c;lpmmult_1 u_lpmmult_1(.dataa (a),.datab (b),.result (c));endmodule实验结果

结论

确定乘法器的位宽:根据应用需求,确定乘法器的输入和输出位宽。确保适当的位宽可以处理所需的数值范围和精度。选择适当的乘法器结构:根据应用需求和资源限制,选择合适的乘法器结构。常见的结构包括布斯-加法器、Wallace树、Dadda树等。不同的结构具有不同的性能和资源开销,因此需要进行权衡和选择。优化资源利用:FPGA资源有限,因此在设计乘法器时需要考虑资源利用的优化。例如,可以使用乘法器硬件资源共享技术,减少重复使用的硬件单元。考虑时钟和延迟:在设计乘法器时,需要考虑时钟频率和延迟。乘法器的延迟可能会影响整个系统的性能。因此,需要合理设置时钟频率,并进行时序分析以确保正确的操作和稳定性。进行仿真和验证:在将乘法器部署到FPGA之前,进行全面的仿真和验证是非常重要的。通过仿真,可以验证乘法器的功能正确性,并进行性能评估。验证还可以帮助发现和解决潜在的问题和错误。进行资源和功耗优化:对于FPGA设计,资源和功耗优化是关键考虑因素。通过使用合适的优化技术和工具,可以减少乘法器的资源占用和功耗消耗,从而提高设计的效率和性能。考虑设计复杂度和可扩展性:乘法器的设计复杂度随着位宽的增加而增加。因此,在设计乘法器时,需要平衡设计复杂度和可扩展性。合理划分模块,并考虑模块化设计和重用性,以便将来的扩展和修改更加方便。注意时序约束:在FPGA设计中,时序约束是确保正确操作的关键。在设计乘法器时,需要正确设置时序约束,并进行时序分析和优化,以确保信号传输和计算正确。

参考文献

verilog的布斯乘法器资源-CSDN文库 ----- 特别感谢贡献软核代码

-

"FPGA Prototyping by Verilog Examples: Xilinx Spartan-3 Version" by Pong P. Chu - 这本书介绍了基于Xilinx Spartan-3 FPGA的Verilog语言和FPGA设计技术。其中包含了有关乘法器设计的章节,并提供了实际的例子和案例分析。

-

"Digital Design and Computer Architecture" by David Harris, Sarah Harris - 这本书是关于数字设计和计算机体系结构的综合性教材。其中涵盖了FPGA设计和乘法器的基本原理与实践。

-

"FPGAs: Instant Access" by Clive Maxfield - 这本书提供了对FPGA设计和开发的快速入门指南。其中包含了有关乘法器设计和优化的简洁介绍,适合初学者快速了解。

-

"FPGA-Based Implementation of Signal Processing Systems" by Roger Woods, John McAllister, Gaye Lightbody, Ying Yi - 这本书深入介绍了FPGA在信号处理系统中的应用。其中包括乘法器设计和优化的内容,并提供了实际的案例和应用示例。

-

"Digital System Design with FPGA: Implementation Using Verilog and VHDL" by Cem Unsalan, Bora Tar - 这本书涵盖了FPGA设计的基础知识和实践技巧。其中包含有关乘法器设计和优化的章节,适合初学者和有一定经验的设计工程师阅读。

相关文章:

中科亿海微乘法器(LPMMULT)

引言 FPGA(可编程逻辑门阵列)是一种可在硬件级别上重新配置的集成电路。它具有灵活性和可重构性,使其成为处理各种应用的理想选择,包括数字信号处理、图像处理、通信、嵌入式系统等。在FPGA中,乘法器是一种重要的硬件资…...

Redis_持久化(AOF、RDB)

6. Redis AOF 6.1 简介 目前,redis的持久化主要应用AOF(Append Only File)和RDF两大机制,AOF以日志的形式来记录每个写操作(增量保存),将redis执行过的所有指令全部安全记录下来(读…...

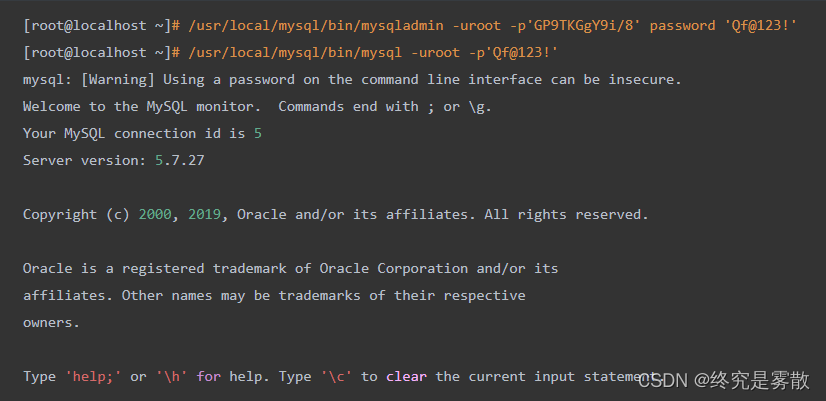

开源数据库Mysql_DBA运维实战 (部署服务篇)

前言❀ 1.数据库能做什么 2.数据库的由来 数据库的系统结构❀ 1.数据库系统DBS 2.SQL语言(结构化查询语言) 3.数据访问技术 部署Mysql❀ 1.通过rpm安装部署Mysql 2.通过源码包安装部署Mysql 前言❀ 1.数据库能做什么 a.不论是淘宝,吃鸡,爱奇艺…...

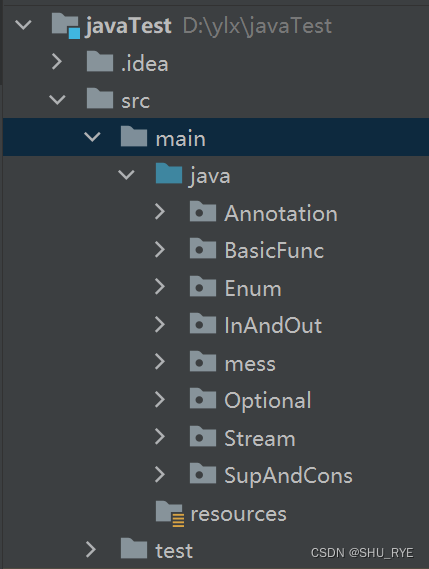

【Java学习】System.Console使用

背景 在自学《Java核心技术卷1》的过程中看到了对System.Console的介绍,编写下列测试代码, public class ConsoleTest {public static void main(String[] args) {Console cs System.console();String name cs.readLine("AccountInfo: ");…...

从零学算法154

154.已知一个长度为 n 的数组,预先按照升序排列,经由 1 到 n 次 旋转 后,得到输入数组。例如,原数组 nums [0,1,4,4,5,6,7] 在变化后可能得到: 若旋转 4 次,则可以得到 [4,5,6,7,0,1,4] 若旋转 7 次&#…...

95 | Python 设计模式 —— 策略模式

策略模式(Strategy Pattern) 引言 策略模式是一种行为型设计模式,它定义了一系列的算法,并将每个算法封装在独立的策略类中,使得这些算法可以相互替换,而不影响客户端的使用。策略模式可以让客户端根据不同的需求选择不同的算法,从而使得系统更加灵活和可扩展。 在本…...

)

【BASH】回顾与知识点梳理(十九)

【BASH】回顾与知识点梳理 十九 十九. 循环 (loop)19.1 while do done, until do done (不定循环)19.2 for...do...done (固定循环)19.3 for...do...done 的数值处理(C写法)19.4 搭配随机数与数组的实验19.5 shell script 的追踪与 debug19.6 what_to_eat-2.sh debug结果解析 该…...

Selenium之css怎么实现元素定位?

世界上最远的距离大概就是明明看到一个页面元素站在那里,但是我却定位不到!! Selenium定位元素的方法有很多种,像是通过id、name、class_name、tag_name、link_text等等,但是这些方法局限性太大, 随着自动…...

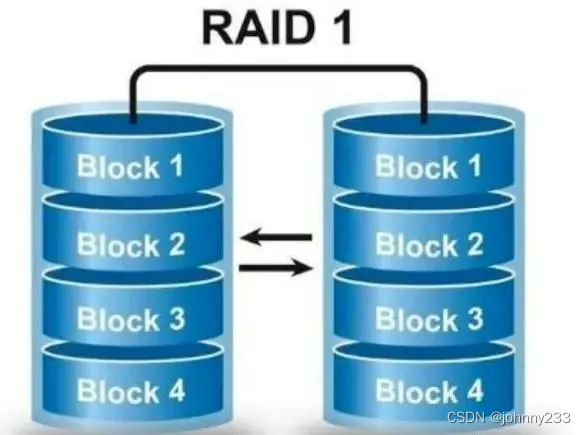

计算机基础之RAID技术

概述 RAID,Redundant Array of Independent Disks,独立磁盘冗余阵列,一种把多块独立的硬盘(物理硬盘)按不同的方式组合起来形成一个硬盘组(逻辑硬盘),从而提供比单个硬盘更高的存储…...

辽宁线上3D三维虚拟工厂生产仿真系统应用场景及优势

工厂虚拟仿真是一种基于计算机技术和虚拟现实技术的数字化解决方案,它可以通过模拟工厂中的设备、流程和操作,来为工程师和操作人员提供了一个沉浸式的虚拟环境,帮助他们更好地了解和优化工厂生产过程。 工厂VR三维可视化技术为工业生产提供了…...

、扩展默认的auth_user表)

csrf跨站请求的相关装饰器、Auth模块(模块的使用、相关方法、退出系统、修改密码功能、注册功能)、扩展默认的auth_user表

一、csrf跨站请求的相关装饰器 django.middleware.csrf.CsrfViewMiddlewareDjango中有一个中间件对csrf跨站做了验证,我只要把csrf的这个中间件打开, 那就意味着所有的方法都要被验证 在所有的视图函数中:只有几个视图函数做验证只有几个函数…...

论文阅读-Detecting Social Media Manipulation in Low-ResourceLanguages)

(WWW2023)论文阅读-Detecting Social Media Manipulation in Low-ResourceLanguages

论文链接:https://arxiv.org/pdf/2011.05367.pdf 摘要 社交媒体被故意用于恶意目的,包括政治操纵和虚假信息。大多数研究都集中在高资源语言上。然而,恶意行为者会跨国家/地区和语言共享内容,包括资源匮乏的语言。 在这里…...

centos-stream-9 centos9 配置国内yum源 阿里云源

源配置 tips: yum配置文件路径 /etc/yum.repos.d/centos.repo 1.备份源配置 [Very Important!]mv /etc/yum.repos.d/centos.repo /etc/yum.repos.d/centos.repo.backup2.Clean Cache: yum clean all3.Backup the Old CentOS-Base.repo If exist this file.cd /etc/yum.repos.…...

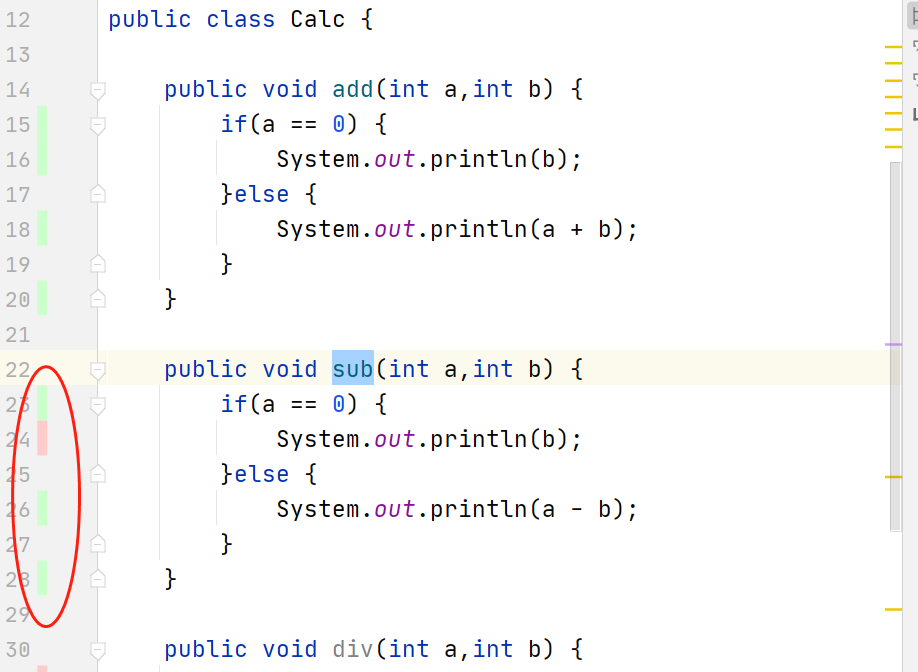

查看单元测试用例覆盖率新姿势:IDEA 集成 JaCoCo

1、什么是 IDEA IDEA 全称 IntelliJ IDEA,是 Java 编程语言开发的集成环境。IntelliJ 在业界被公认为最好的 Java 开发工具,尤其在智能代码助手、代码自动提示、重构、JavaEE 支持、各类版本工具(git、SVN 等)、JUnit、CVS 整合、代码分析、 创新的 GUI…...

js和nodejs如何将文件切片和合并

nodejs进行文件切片合并 使用nodejs读取文件流,并对流进行切片合并等操作,就需要用到Buffer对象,可对文件流进行切片,并合并。 const fs require(fs)// 读取一个文件,使用fs读取文件获取一个Buffer类型数据 const b…...

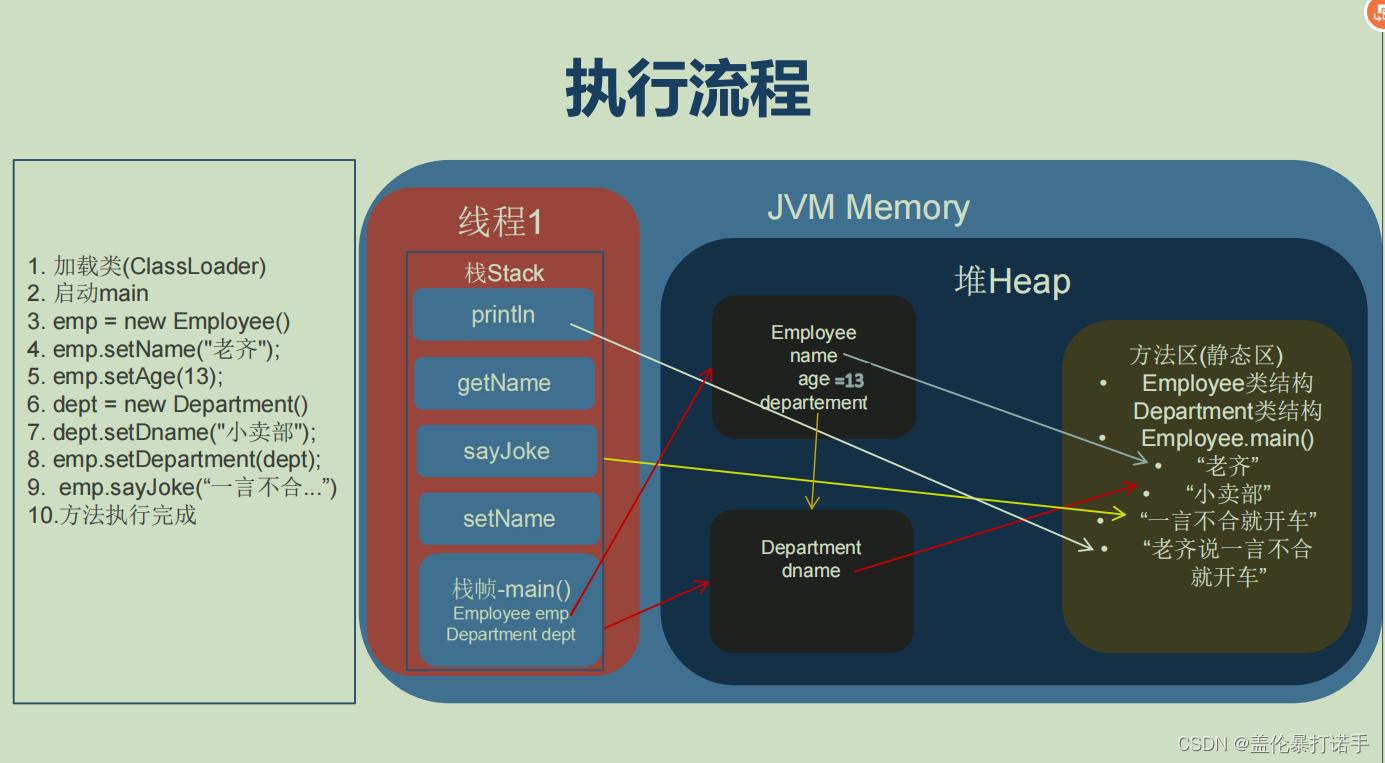

Java内存模型

Java内存模型全称JMM(Java Memory Model) 内存主要有堆和栈组成 下面来一段demo代码详细讲解堆栈的作用,以及流程 public class Employee {private String name;private Integer age;private Department department;public Employee(){}pub…...

[国产MCU]-BL602开发实例-看门狗定时器(WDG)

看门狗定时器(WDG) 文章目录 看门狗定时器(WDG)1、看门狗定时器(WDG)介绍2、看门狗定时器驱动API介绍3、看门狗定时器使用实例看门狗(Watchdog),又叫看门狗定时器(Watchdog Timer),是一种硬件的计时设备,当系统的主程序发生某些错误时,导致未及时清除看门狗计时器…...

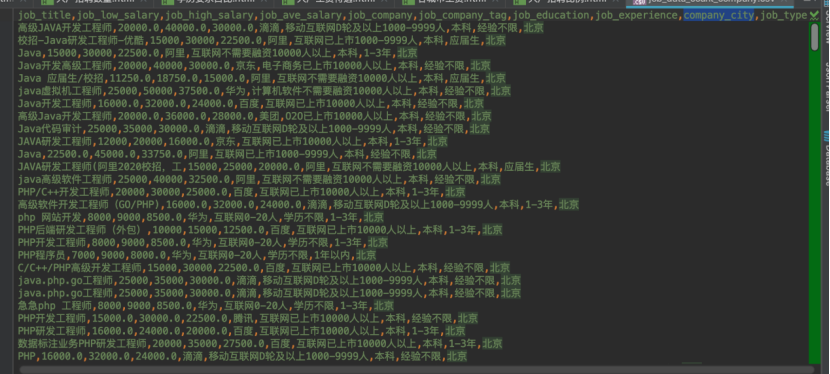

28 | Boss直聘数据分析

针对boss直聘网的招聘信息,然后分析互联网发展排名前十的城市在互联网方面职位的薪水,学历要求,经验要求,等等信息。 准备从以下几个方面进行分析: (1)各个城市的平均工资 (2)各个学历的平均工资 (3)各个岗位的平均工资 (4)不同工作经验要求的工资 (5)各个经验…...

Hash 缓存

Hash 缓存 输出文件名(Hash) 静态资源缓存是前端性能优化的一个点,所以在前端开发过程中,一般会最大限度的利用缓存(这里主要是强缓存)。如果设置了强缓存后,每次当我们部署了新的项目文件到线…...

腾讯云CVM服务器标准型S5性能CPU处理器测试

腾讯云服务器CVM标准型S5实例是次新一代的标准型实例,CPU采用主频2.5GHzIntel Xeon Cascade Lake或者Intel Xeon Cooper Lake处理器,睿频3.1GHz,云服务器S5基于全新优化虚拟化平台,提供了平衡、稳定的计算、内存和网络资源&#x…...

从电机控制到光伏逆变器:Clark/Park变换的‘单相应用’实战避坑指南

从电机控制到光伏逆变器:Clark/Park变换的‘单相应用’实战避坑指南 在单相电力电子系统中,Clark和Park变换的应用远比教科书上描述的要复杂得多。去年调试某款单相光伏逆变器时,我在锁相环设计环节耗费了两周时间——明明按照三相系统的思路…...

)

别再只会下载程序了!J-Link在Keil MDK下的SWD仿真调试全攻略(STM32实战)

别再只会下载程序了!J-Link在Keil MDK下的SWD仿真调试全攻略(STM32实战) 当你的STM32程序终于成功下载到板子上,却发现运行时行为异常或变量值不符合预期时,单纯的下载功能就显得力不从心了。J-Link作为业界标杆的调试…...

实现永磁同步电机无模型预测控制(MFPC)的Simulink仿真指南)

告别调参烦恼!用扩张状态观测器(ESO)实现永磁同步电机无模型预测控制(MFPC)的Simulink仿真指南

永磁同步电机无模型预测控制实战:基于ESO的Simulink仿真指南 电机控制工程师们常常陷入参数辨识和PI调节的泥潭——电阻、电感、磁链的微小变化就能让精心设计的控制器性能骤降。有没有一种方法能跳出这个循环?扩张状态观测器(ESO࿰…...

)

告别三极管!用CH340X/C直连搞定CH32/STM32一键下载(附完整电路图与驱动版本避坑)

极简主义嵌入式开发:CH340直连实现CH32/STM32一键下载全攻略 当你在深夜调试一个嵌入式项目,反复插拔USB线、手动切换BOOT跳线、按复位按钮时,是否想过——这些繁琐操作真的有必要吗?传统的一键下载电路通常需要两个三极管构成的逻…...

5分钟学会m4s-converter:B站缓存视频永久保存终极指南

5分钟学会m4s-converter:B站缓存视频永久保存终极指南 【免费下载链接】m4s-converter 一个跨平台小工具,将bilibili缓存的m4s格式音视频文件合并成mp4 项目地址: https://gitcode.com/gh_mirrors/m4/m4s-converter 你是否遇到过B站收藏的视频突然…...

探索未来教育:10个Agora Flat开源课堂的核心功能解析

探索未来教育:10个Agora Flat开源课堂的核心功能解析 【免费下载链接】flat Project flat is the Web, Windows and macOS client of Agora Flat open source classroom. 项目地址: https://gitcode.com/gh_mirrors/fl/flat Agora Flat是一款开源的Web、Wind…...

终极指南:3分钟解锁鸣潮120FPS体验的免费工具箱

终极指南:3分钟解锁鸣潮120FPS体验的免费工具箱 【免费下载链接】WaveTools 🧰鸣潮工具箱 项目地址: https://gitcode.com/gh_mirrors/wa/WaveTools 鸣潮工具箱是一款专为《鸣潮》玩家设计的开源性能优化工具,能够轻松突破游戏内置的6…...

BuildRoot下RTL8822CE蓝牙模块驱动加载与固件路径排错指南

1. RTL8822CE蓝牙模块驱动加载问题排查 遇到RTL8822CE蓝牙模块驱动加载失败时,内核日志通常会显示"load firmware failed"错误。这个问题我遇到过多次,根本原因是系统找不到正确的固件文件。先别急着改代码,让我们从最基础的排查开…...

局域网组网技术

与为了互联全球不同网络而设计的、复杂的OSI七层模型不同,局域网参考模型更专注于解决一个局部区域内的网络通信问题。因此,它的结构被大大简化了。下图清晰地展示了局域网参考模型与OSI模型的关系:一、设计思想:简化与专注局域网…...

Koodo Reader:如何用AI智能助手打造你的终极数字阅读体验

Koodo Reader:如何用AI智能助手打造你的终极数字阅读体验 【免费下载链接】koodo-reader A modern ebook manager and reader with sync and backup capacities for Windows, macOS, Linux, Android, iOS and Web 项目地址: https://gitcode.com/GitHub_Trending/…...