【Verilog 教程】6.5 Verilog避免Latch

关键词:触发器,锁存器

Latch 的含义

锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

当电平信号无效时,输出信号随输入信号变化,就像通过了缓冲器;当电平有效时,输出信号被锁存。激励信号的任何变化,都将直接引起锁存器输出状态的改变,很有可能会因为瞬态特性不稳定而产生振荡现象。

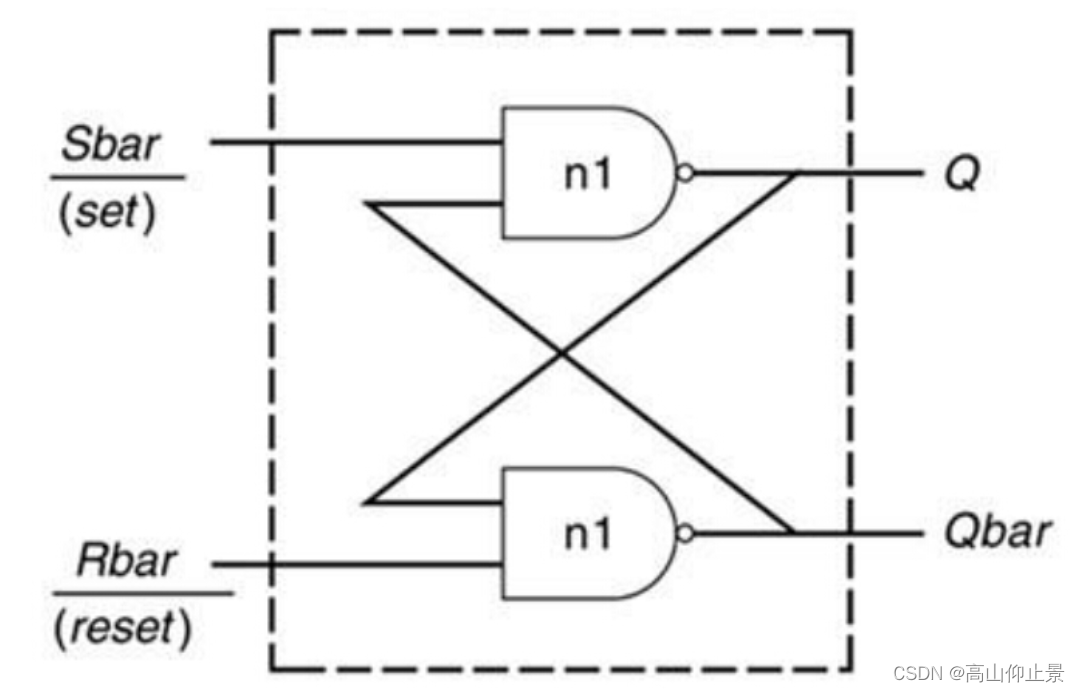

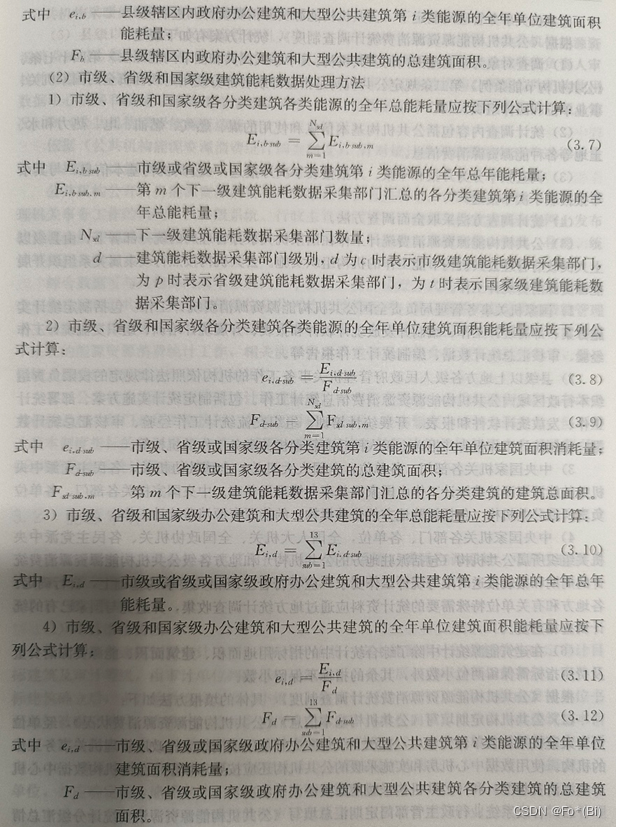

锁存器示意图如下:

触发器(flip-flop),是边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升沿或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内)。

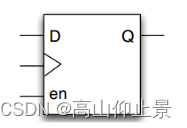

触发器示意图如下:

寄存器(register),在 Verilog 中用来暂时存放参与运算的数据和运算结果的变量。一个变量声明为寄存器时,它既可以被综合成触发器,也可能被综合成 Latch,甚至是 wire 型变量。但是大多数情况下我们希望它被综合成触发器,但是有时候由于代码书写问题,它会被综合成不期望的 Latch 结构。

Latch 的主要危害有:

1)输入状态可能多次变化,容易产生毛刺,增加了下一级电路的不确定性;

2)在大部分 FPGA 的资源中,可能需要比触发器更多的资源去实现 Latch 结构;

3)锁存器的出现使得静态时序分析变得更加复杂。

Latch 多用于门控时钟(clock gating)的控制,一般设计时,我们应当避免 Latch 的产生。

if 结构不完整

组合逻辑中,不完整的 if - else 结构,会产生 latch。

例如下面的模型,if 语句中缺少 else 结构,系统默认 else 的分支下寄存器 q 的值保持不变,即具有存储数据的功能,所以寄存器 q 会被综合成 latch 结构。

实例

module module1_latch1(input data,input en ,output reg q) ;always @(*) beginif (en) q = data ;endendmodule

避免此类 latch 的方法主要有 2 种,一种是补全 if-else 结构,或者对信号赋初值。

例如,上面模型中的always语句,可以改为以下两种形式:

实例

// 补全条件分支结构

always @(*) begin

if (en) q = data ;

else q = 1’b0 ;

end

//赋初值

always @(*) begin

q = 1’b0 ;

if (en) q = data ; //如果en有效,改写q的值,否则q会保持为0

end

但是在时序逻辑中,不完整的 if - else 结构,不会产生 latch,例如下面模型。

这是因为,q 寄存器具有存储功能,且其值在时钟的边沿下才会改变,这正是触发器的特性。

实例

module module1_ff(input clk ,input data,input en ,output reg q) ;always @(posedge clk) beginif (en) q <= data ;endendmodule

在组合逻辑中,当条件语句中有很多条赋值语句时,每个分支条件下赋值语句的不完整也是会产生 latch。

其实对每个信号的逻辑拆分来看,这也相当于是 if-else 结构不完整,相关寄存器信号缺少在其他条件下的赋值行为。例如:

实例

module module1_latch11(input data1,input data2,input en ,output reg q1 ,output reg q2) ;always @(*) beginif (en) q1 = data1 ;else q2 = data2 ;endendmodule

这种情况也可以通过补充完整赋值语句或赋初值来避免 latch。例如:

实例

always @(*) begin//q1 = 0; q2 = 0 ; //或在这里对 q1/q2 赋初值if (en) beginq1 = data1 ;q2 = 1'b0 ;endelse beginq1 = 1'b0 ;q2 = data2 ;endend

case 结构不完整

case 语句产生 Latch 的原理几乎和 if 语句一致。在组合逻辑中,当 case 选项列表不全且没有加 default 关键字,或有多个赋值语句不完整时,也会产生 Latch。例如:

实例

module module1_latch2(input data1,input data2,input [1:0] sel ,output reg q ) ;always @(*) begincase(sel)2'b00: q = data1 ;2'b01: q = data2 ;endcaseendendmodule

当然,消除此种 latch 的方法也是 2 种,将 case 选项列表补充完整,或对信号赋初值。

补充完整 case 选项列表时,可以罗列所有的选项结果,也可以用 default 关键字来代替其他选项结果。

例如,上述 always 语句有以下 2 种修改方式。

实例

always @(*) begincase(sel)2'b00: q = data1 ;2'b01: q = data2 ;default: q = 1'b0 ;endcaseendalways @(*) begincase(sel)2'b00: q = data1 ;2'b01: q = data2 ;2'b10, 2'b11 : q = 1'b0 ;endcaseend

原信号赋值或判断

在组合逻辑中,如果一个信号的赋值源头有其信号本身,或者判断条件中有其信号本身的逻辑,则也会产生 latch。因为此时信号也需要具有存储功能,但是没有时钟驱动。此类问题在 if 语句、case 语句、问号表达式中都可能出现,例如:

实例

//signal itself as a part of conditionreg a, b ;always @(*) beginif (a & b) a = 1'b1 ; //a -> latchelse a = 1'b0 ;end//signal itself are the assigment sourcereg c;wire [1:0] sel ;always @(*) begincase(sel)2'b00: c = c ; //c -> latch2'b01: c = 1'b1 ;default: c = 1'b0 ;endcaseend//signal itself as a part of condition in "? expression"wire d, sel2;assign d = (sel2 && d) ? 1'b0 : 1'b1 ; //d -> latch

避免此类 Latch 的方法,就只有一种,即在组合逻辑中避免这种写法,信号不要给信号自己赋值,且不要用赋值信号本身参与判断条件逻辑。

例如,如果不要求立刻输出,可以将信号进行一个时钟周期的延时再进行相关逻辑的组合。上述第一个产生 Latch 的代码可以描述为:

实例

reg a, b ;

reg a_r ;

always (@posedge clk)

a_r <= a ;

always @(*) begin

if (a_r & b) a = 1’b1 ; //there is no latch

else a = 1’b0 ;

end

敏感信号列表不完整

如果组合逻辑中 always@() 块内敏感列表没有列全,该触发的时候没有触发,那么相关寄存器还是会保存之前的输出结果,因而会生成锁存器。

这种情况,把敏感信号补全或者直接用 always@(*) 即可消除 latch。

小结

总之,为避免 latch 的产生,在组合逻辑中,需要注意以下几点:

1)if-else 或 case 语句,结构一定要完整

2)不要将赋值信号放在赋值源头,或条件判断中

3)敏感信号列表建议多用 always@(*)

相关文章:

【Verilog 教程】6.5 Verilog避免Latch

关键词:触发器,锁存器 Latch 的含义 锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着…...

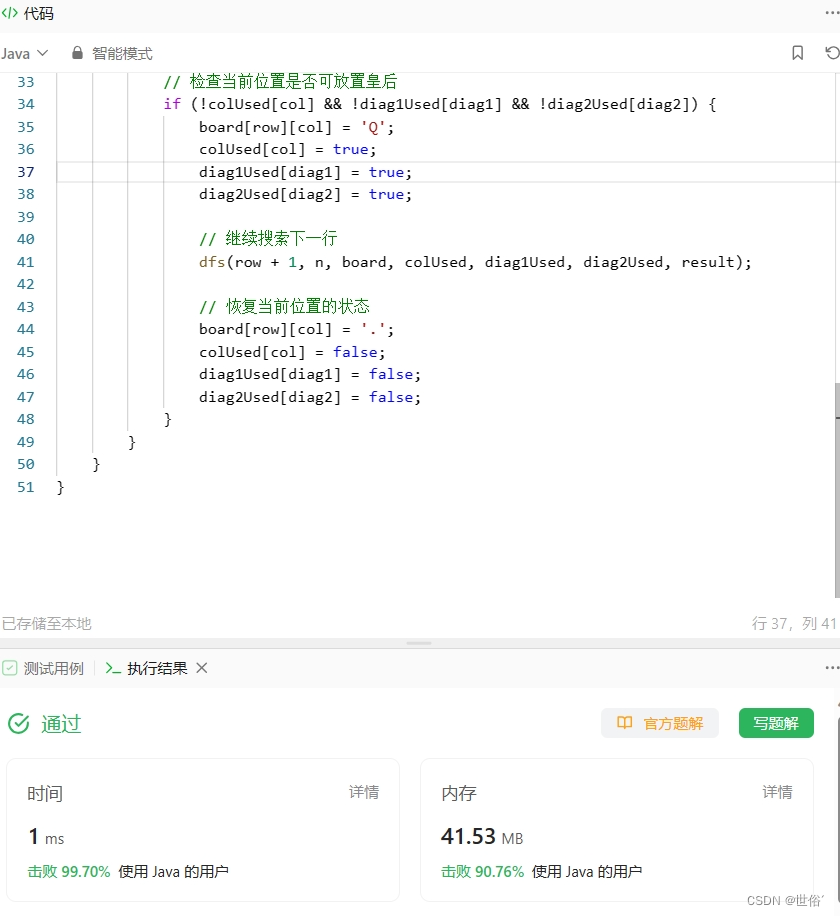

怒刷LeetCode的第21天(Java版)

目录 第一题 题目来源 题目内容 解决方法 方法一:哈希表 方法二:计数器数组 第二题 题目来源 题目内容 解决方法 方法一:分治法 方法二:快速幂 迭代 方法三:快速幂 递归 第三题 题目来源 题目内容 …...

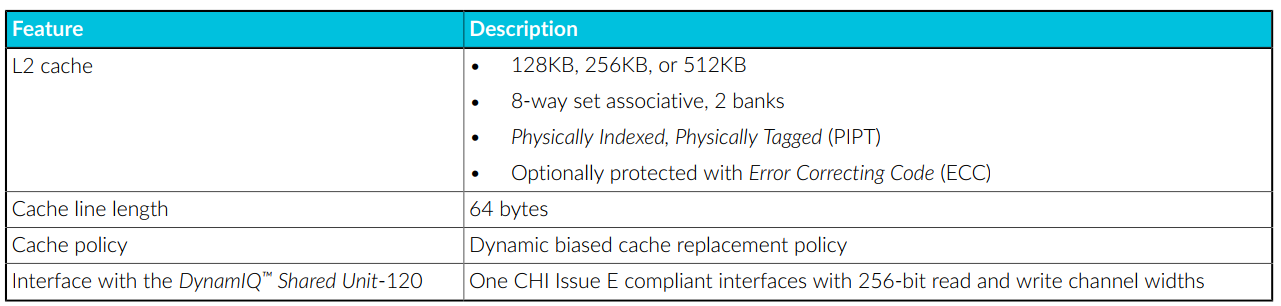

Armv9 Cortex-A720的L2 memory system 和 L2 Cache

9 L2 memory system Cortex-A720核心的L2内存系统通过CPU bridge连接core与DynamIQ Shared Unit-120,其中包括私有的L2缓存。 L2缓存是统一的,每个Cortex-A720核心在一个集群中都有私有的L2缓存。 L2内存系统包括使用虚拟地址(VA)和程序计数器(PC)的数据预取引擎。不同…...

蓝桥等考Python组别九级003

第一部分:选择题 1、Python L9 (15分) 运行下面程序,可以输出几行“*”?( ) for i in range(3): for j in range(4): print(*, end = ) print() 6374正确答案:B 2、Python L9...

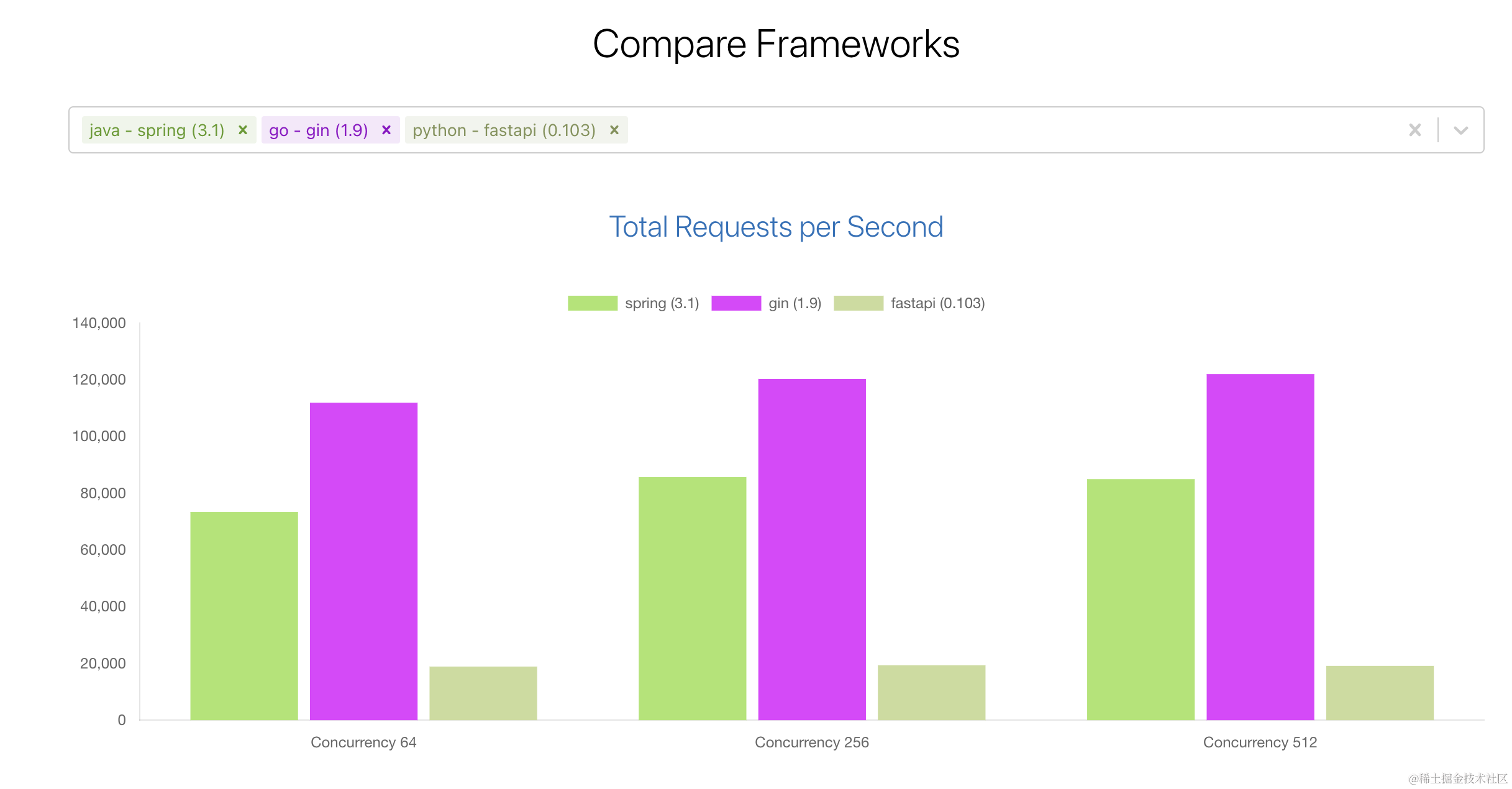

Python异步框架大战:FastAPI、Sanic、Tornado VS Go 的 Gin

一、前言 异步编程在构建高性能 Web 应用中起着关键作用,而 FastAPI、Sanic、Tornado 都声称具有卓越的性能。本文将通过性能压测对这些框架与Go的Gin框架进行全面对比,揭示它们之间的差异。 原文:Python异步框架大战:FastAPI、Sa…...

Docker笔记1

一、Docker介绍 Docker是一个开源的应用容器引擎,基于Go语言并遵从Apache2.0协议开源 可以让开发者打包他们的应用以及依赖包到一个轻量级、可移植的容器中,然后发布到任何流行的Linux机器上,也可以实现虚拟化。 容器是完全使用沙箱机制&a…...

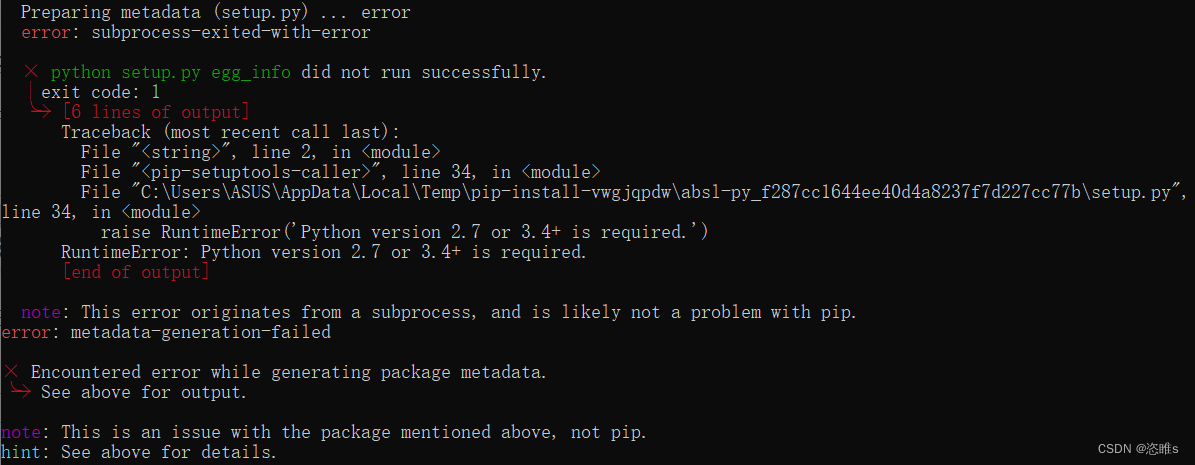

TensorFlow-Federated简介与安装

1、简介 TensorFlow Federated(TFF)是一个用于机器学习和其他分布式数据计算的开源框架。TFF 的开发旨在促进联邦学习 (FL)的开放研究和实验。联邦学习是一种机器学习方法,其中一个共享的全局模型在许多参与的客户之间…...

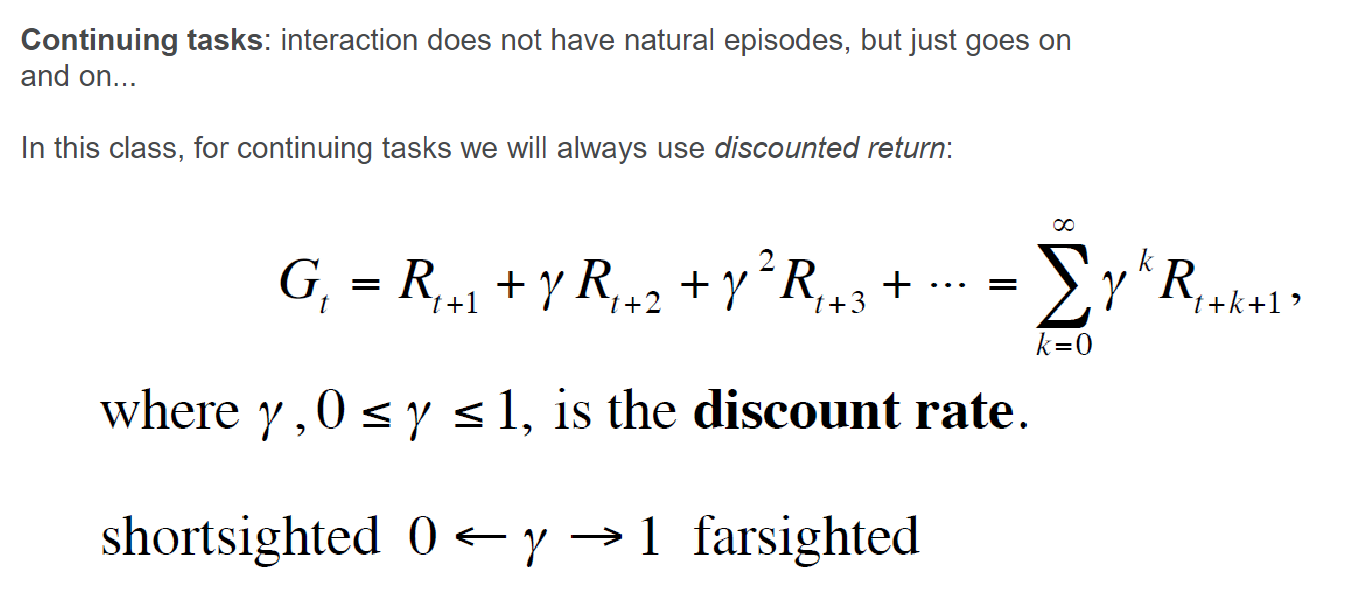

【强化学习】基础概念

1. Agent (智能体) 智能体是进行决策和学习的实体,它能感知环境的状态,并基于策略采取动作以影响环境。智能体的目标是通过与环境的交互获得最大化的累积奖励。 2. Environment (环境) 环境是智能体所处的外部系统,它与智能体交互。环境的…...

云原生Kubernetes:K8S集群各组件服务重启

目录 一、理论 1.各组件服务重启命令 一、理论 1.各组件服务重启命令 (1)Master节点Node节点共同服务 systemctl restart etcd systemctl daemon-reload systemctl enable flanneld systemctl restart flanneld (2)Master节…...

闲话Python编程-循环

1. for循环 Python的for语句有点特别,只能对序列和字符串进行处理,序列自然包括list、tuple和range对象。 #!/usr/bin/env python3 # -*- coding: utf-8 -*- # 练习for语句def loop_for():names [Tom, Jack, Black]for name in names:print(name)s ab…...

建筑能源管理(3)——建筑能源监管

为了全面落实科学发展观,提高建筑能源管理水平,进一步降低能源和水资源消耗、合理利用资源,以政府办公建筑和大型公共建筑的运行节能管理为突破口,建立了既有政府办公建筑和大型公共建筑运行节能监管体系,旨在提高政府…...

中国逐年干燥度指数数据集

简介: 中国逐年干燥度指数,空间分辨率为1km,时间为1901-2022,为比值,没有单位。该数据集是基于中国1km逐月潜在蒸散发(PET)和降水量(PRE)采用比值法计算式得到ÿ…...

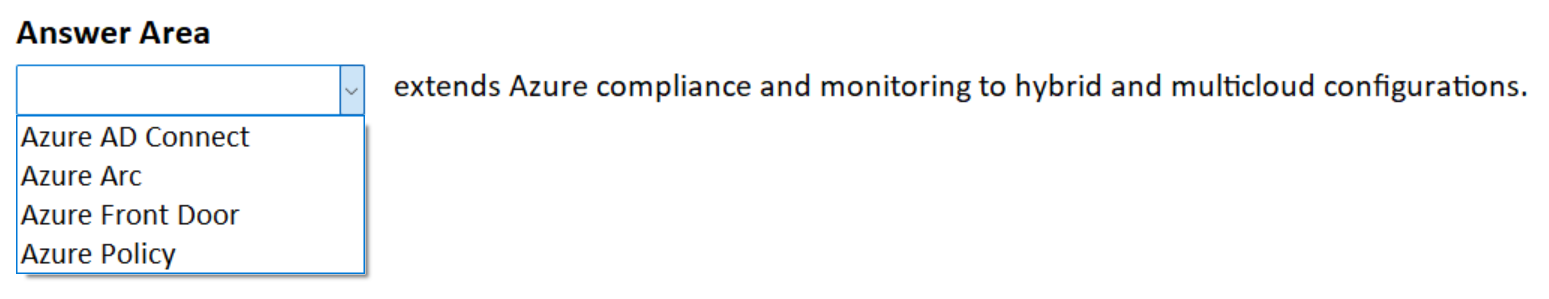

Azure Arc 概要:功能、管理和应用场景详解,AZ900 考点示例

文章目录 本文大纲一、什么是 Azure Arc二、使用 Azure Arc 可以做什么操作三、使用 Azure Arc 可以管理什么资源3.1 如何使用Azure Arc与服务器? 四、Azure Arc 支持的主要场景五、在 AZ900 中的考点示例5.1 示例题 15.2 示例题 2 本文大纲 本文思维导图概述的主要内容&…...

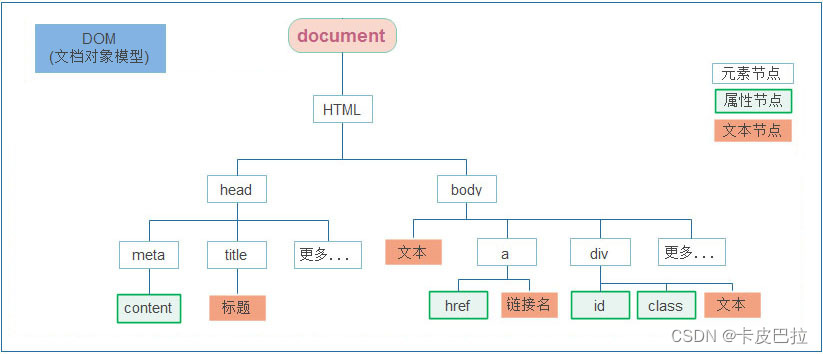

JavaScript Web APIs第一天笔记

复习: splice() 方法用于添加或删除数组中的元素。 **注意:**这种方法会改变原始数组。 删除数组: splice(起始位置, 删除的个数) 比如:1 let arr [red, green, blue] arr.splice(1,1) // 删除green元素 consol…...

十六.镜头知识之工业镜头的质量判断因素

十六.镜头知识之工业镜头的质量判断因素 文章目录 十六.镜头知识之工业镜头的质量判断因素1.分辨率(Resolution)2.明锐度(Acutance)3.景深(DOF):4. 最大相对孔径与光圈系数5.工业镜头各参数间的相互影响关系5.1.焦距大小的影响情况5.2.光圈大小的影响情况5.3.像场中…...

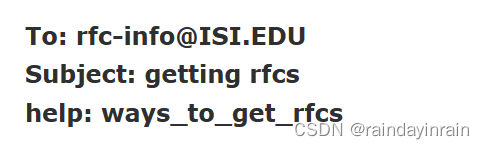

网络协议--概述

1.2 分层 网络协议通常分不同层次进行开发,每一层分别负责不同的通信功能。一个协议族,比如TCP/IP,是一组不同层次上的多个协议的组合。 TCP/IP通常被认为是一个四层协议系统,如图1-1所示。每一层负责不同的功能: 1.链…...

aarch64 平台 musl gcc 工具链手动编译方法

目标 手动编译一个 aarch64 平台的 musl gcc 工具链 musl libc 与 glibc、uclibc 等,都是 标准C 库, musl libc 是基于系统调用之上的 标准C 库,也就是用户态的 标准C 库。 musl libc 轻量、开源、免费,是一些 操作系统的选择,当前 Lite-OS 与 RT-Smart 等均采用自制的 mu…...

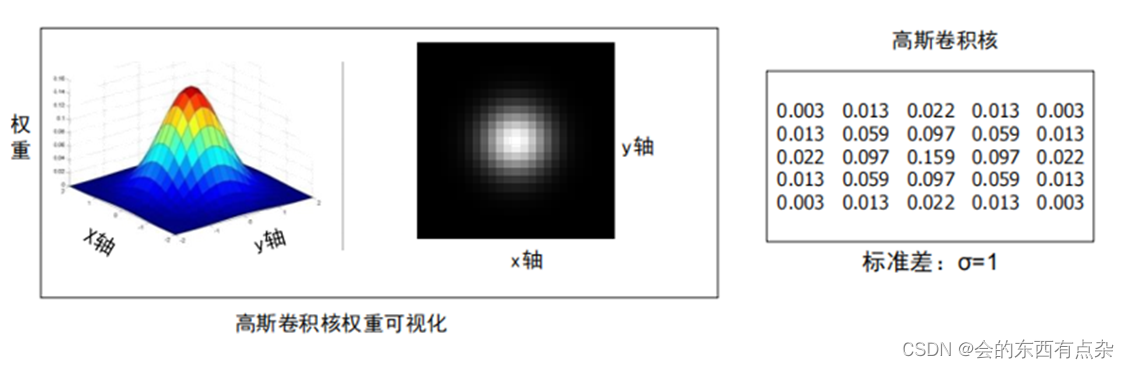

计算机图像处理-高斯滤波

高斯滤波 高斯滤波是一种线性平滑滤波,适用于消除高斯噪声,广泛应用于图像处理的减噪过程。通俗的讲,高斯滤波就是对整幅图像进行加权平均的过程,每一个像素点的值,都由其本身和邻域内的其他像素值经过加权平均后得到…...

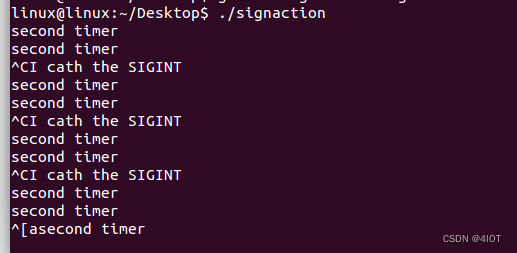

lv5 嵌入式开发-9 信号机制(上)

目录 1 信号机制 2 信号的产生 3 常用信号 4 相关命令 4.1 信号相关命令 kill / killall 4.2 信号发送 – kill / raise 4.3 定时器函数相关函数 – alarm /ualarm/ pause 4.4 信号捕捉:设置信号响应方式 – signal /sigaction,闹钟实现 4.5 子…...

460. LFU 缓存

请你为 最不经常使用(LFU)缓存算法设计并实现数据结构。 实现 LFUCache 类: LFUCache(int capacity) - 用数据结构的容量 capacity 初始化对象int get(int key) - 如果键 key 存在于缓存中,则获取键的值,否则返回 -1…...

创业团队如何利用多模型聚合能力优化产品开发成本

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 创业团队如何利用多模型聚合能力优化产品开发成本 对于预算有限的创业团队而言,在拥抱大模型能力的同时,如…...

树莓派SPI屏幕Python GUI开发:Pillow+Adafruit打造动态监控仪表盘

1. 项目概述与核心价值在嵌入式开发领域,尤其是物联网和智能硬件项目中,一个直观、动态的图形界面往往是连接设备与用户的桥梁。你可能已经习惯了通过串口打印日志来调试,或者用几个LED灯来指示状态,但当你的项目需要展示更丰富的…...

Blender家具模型下载|9000+个室内家居资产库下载和资产库导入教程 Blender家具模型下载、Blender资产库、Blender室内模型、Blender家居模型、

Blender家具模型下载|9000个室内家居资产库下载和安装教程 关键词:* Blender家具模型下载、Blender资产库、Blender室内模型、Blender家居模型、Blender Asset Library、Blender模型导入教程、Blender室内设计资源 一、前言 做室内渲染或产品展示时&am…...

别再凭感觉了!手把手教你用MPE和NOHD评估激光笔、测距仪的人眼安全距离

别再凭感觉了!手把手教你用MPE和NOHD评估激光笔、测距仪的人眼安全距离 激光笔和手持测距仪已经成为现代生活中常见的工具,从教学演示到户外测量,它们的应用场景越来越广泛。然而,这些看似小巧的设备如果使用不当,可能…...

3步解锁百度网盘SVIP极速下载:告别限速困扰的完整指南

3步解锁百度网盘SVIP极速下载:告别限速困扰的完整指南 【免费下载链接】BaiduNetdiskPlugin-macOS For macOS.百度网盘 破解SVIP、下载速度限制~ 项目地址: https://gitcode.com/gh_mirrors/ba/BaiduNetdiskPlugin-macOS 还在为百度网盘那蜗牛般的下载速度而…...

Unlock Music音乐解锁工具:5步实现跨平台音乐文件自由转换

Unlock Music音乐解锁工具:5步实现跨平台音乐文件自由转换 【免费下载链接】unlock-music 在浏览器中解锁加密的音乐文件。原仓库: 1. https://github.com/unlock-music/unlock-music ;2. https://git.unlock-music.dev/um/web 项目地址: h…...

Yaade与Postman对比:为什么自托管是更好的选择

Yaade与Postman对比:为什么自托管是更好的选择 【免费下载链接】yaade Yaade is an open-source, self-hosted, collaborative API development environment. 项目地址: https://gitcode.com/gh_mirrors/ya/yaade 在当今API开发领域,选择合适的工…...

)

Jetson Nano到手后别急着烧系统,先做好这5步准备(含SD卡选购与电源避坑)

Jetson Nano开箱必做的5项硬件准备:从SD卡到电源的完整避坑指南 当你第一次拿到Jetson Nano开发板时,那种迫不及待想立刻通电体验的冲动完全可以理解。但作为一个经历过多次"翻车"的老玩家,我必须提醒你:直接烧录系统很…...

初创公司技术选型时为何应考虑 Taotoken 这类大模型聚合平台

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 初创公司技术选型时为何应考虑 Taotoken 这类大模型聚合平台 对于初创公司而言,技术栈的早期选择往往决定了未来数年的…...

OpenClaw QQ机器人一键接入指南

准备工作 软件环境 已成功安装并运行 OpenClaw Windows 版本OpenClaw Gateway 运行状态正常(建议保持在线状态) 账号准备 已准备好有效的 QQ 账号(用于平台扫码登录)已安装 QQ 手机客户端(用于扫码登录及机器人功…...