FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1)

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1)

- 单字节写时序

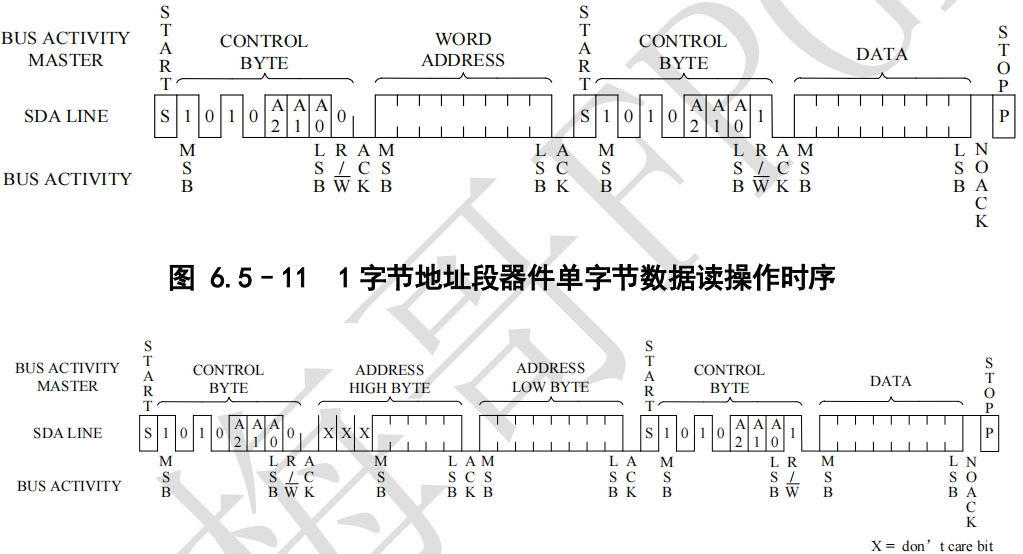

- 单字节读时序

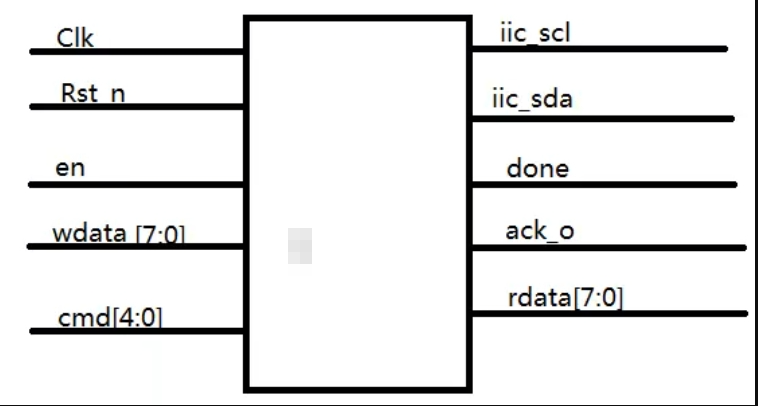

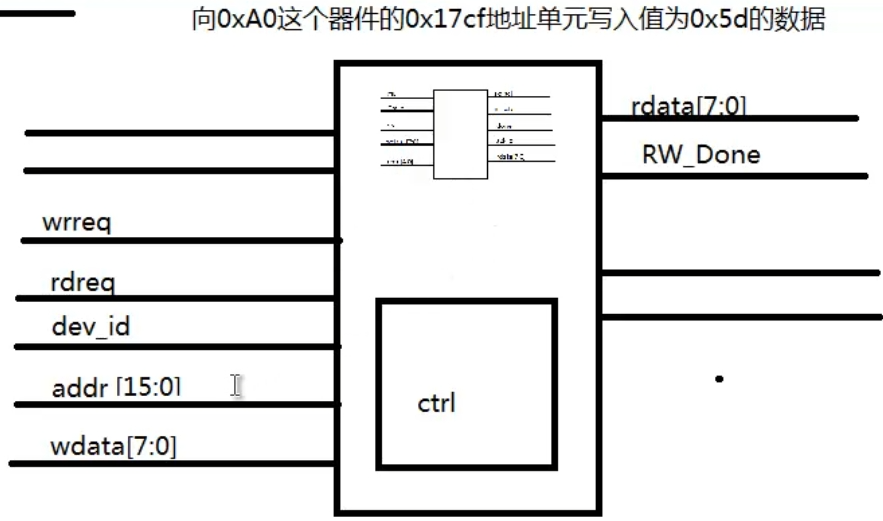

- I2C 控制器设计

- 模块框图

- scl_high 和 scl_low 产生的时序图

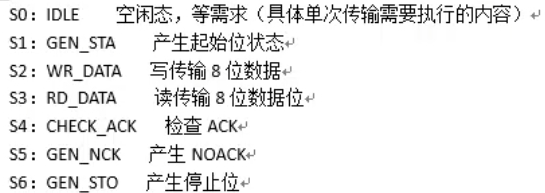

- 状态转移图

- Verilog代码

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1)

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(2)

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(3)

单字节写时序

EEPROM器件或其他不同器件,I2C 器件地址字节不同,这样对于 I2C 单字节写时序就会有所差别,如下图分别为 1 字节地址段器件和 2 字节地址段器件单字节写时序图。

根据时序图,从主机角度来描述一次写入单字节数据过程如下:

主机设置 SDA 为输出;

主机发起起始信号;

主机传输器件地址字节,其中最低位为 0,表明为写操作;

主机设置 SDA 为三态门输入,读取从机应答信号;

读取应答信号成功,主机设置 SDA 为输出,传输 1 字节地址数据;

主机设置 SDA 为三态门输入,读取从机应答信号;

读取应答信号成功,对于两字节地址段器件,传输地址数据低字节,对于 1字节地址段器件,主机设置 SDA 为输出,传输待写入的数据;

设置 SDA 为三态门输入,读取从机应答信号,对于两字节地址段器件,接着步骤 i;对于 1 字节地址段器件,直接跳转到步骤 k;

读取应答信号成功,主机设置 SDA 为输出,传输待写入的数据(对于两字节地址段器件);

设置 SDA 为三态门输入,读取从机应答信号(两字节地址段器件);

读取应答信号成功,主机产生 STOP 位,终止传输。

单字节读时序

根据时序图,从主机角度描述一次读数据过程,如下:

主机设置 SDA 为输出;

主机发起起始信号;

主机传输器件地址字节,其中最低位为 0,表明为写操作;

主机设置 SDA 为三态门输入,读取从机应答信号;

读取应答信号成功,主机设置 SDA 输出,传输 1 字节地址数据;

主机设置 SDA 为三态门输入,读取从机应答信号;

读取应答信号成功,主机设置 SDA 输出,对于两字节地址段器件,传输低字节地址数据;对于 1 字节地址段器件,无此步骤,直接跳转到步骤 h;

主机发起起始信号;

主机传输器件地址字节,其中最低位为 1,表明为读操作;

设置 SDA 为三态门输入,读取从机应答信号;

读取应答信号成功,主机设置 SDA 为三态门输入,读取 SDA 总线上的一个字节的数据;

产生无应答信号(高电平)(无需设置为输出高电平,因为总线会被自动拉高);

主机产生 STOP 位,终止传输。

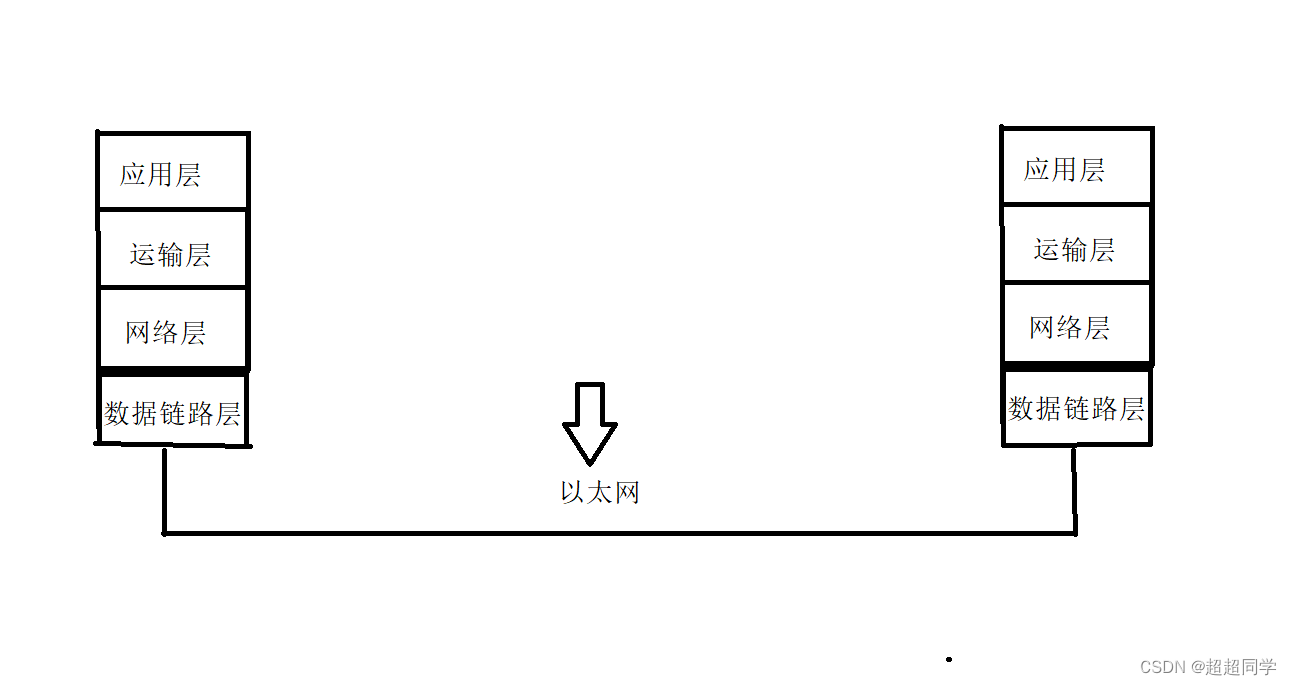

I2C 控制器设计

模块框图

状态机里面线性序列机思路

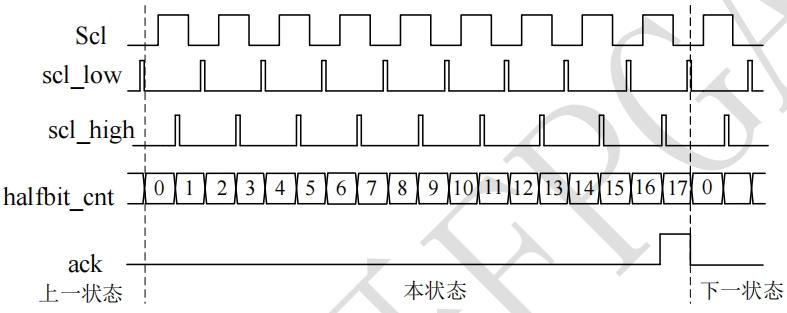

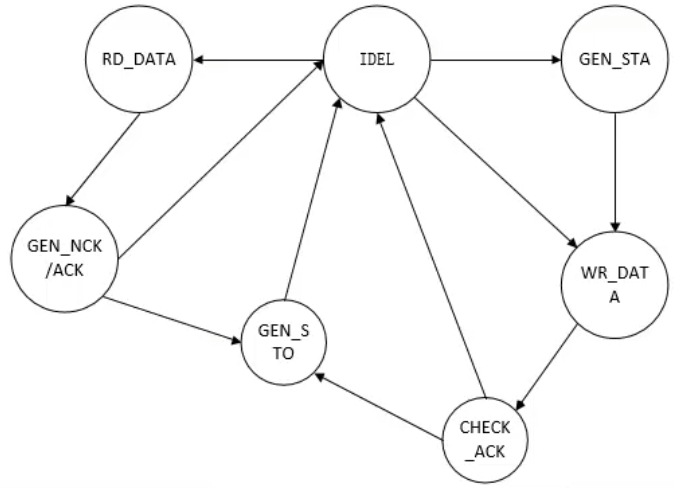

scl_high 和 scl_low 产生的时序图

通过上述的讲述,对 I2C 读写器件数据时序有了一定的了解,下面将开始进行控制程序的设计。根据上面 I2C 的基本概念中有关读写时SDA 与 SCL 时序,不管对于从机还是主机,SDA 上的每一位数据在 SCL 的高电平期间保持不变,而数据的改变总是在 SCL 的低电平期间发生。因此,我们可以选用 2 个标志位对时钟 SCL 的高电平和低电平进行标记,如下图所示:scl_high 对 SCL 高电平期间进行标志,scl_low 对 SCL 低电平期间进行标志。这样就可以在 scl_high 有效时读 SDA 数据,在 scl_low 有效时改变数据。

如下图所示

在状态机中,从主机角度来看,SDA 数据线上在写控制、写数据、读控制状态过程是需要串行输出数据,而在读数据状态过程是需要串行输入数据。根据数据在时钟高电平期间保持不变,改变数据在低电平时期的规则,本设计对时钟信号的高低电平进行计数,从而在指定的计数值进行输出或读取数据实现数据的串行输出和串行输入。串行输出和串行输入数据采用任务的形式进行表示,便于在主状态机中多次的调用。图下为计数的过程以及特定状态变化的时序图,这里的特定状态主要是指读/写控制、读/写地址和读/写数据状态。

状态转移图

定义

独热码

为了节省资源,可以通过上一个状态一定会执行下一个状态进而连贯在一起弄一个组合拳法。

创建任务的思想

对于计数器 halfbit_cnt 只在写控制、写数据、读控制、读数据状态下才进行计数,其他状态为零。代码中 FF 是进行串行输出或输入任务的标志位,当 FF 为1 时表示退出任务,FF 为 0 时表示进入任务。这样便于在状态机中对任务的调用,以及在指定的时间退出任务。

状态机里面线性序列机思路

Verilog代码

module I2C(Clk,Rst_n,Rddata_num,Wrdata_num,Wdaddr_num,Device_addr,Word_addr,Wr,Wr_data,Wr_data_vaild,Rd,Rd_data,Rd_data_vaild,Scl,Sda,Done

);//系统时钟采用50MHz

parameter SYS_CLOCK = 50_000_000;

//SCL总线时钟采用400kHz

parameter SCL_CLOCK = 400_000;

//产生时钟SCL计数器最大值

localparam SCL_CNT_M = SYS_CLOCK/SCL_CLOCK;input Clk; //系统时钟input Rst_n; //系统复位信号input [5:0] Rddata_num; //I2C总线连续读取数据字节数input [5:0] Wrdata_num; //I2C总线连续读取数据字节数input [1:0] Wdaddr_num; //I2C器件数据地址字节数input [2:0] Device_addr; //I2C器件地址input [15:0] Word_addr; //I2C寄存器地址input Wr; //I2C器件写使能input [7:0] Wr_data; //I2C器件写数据output Wr_data_vaild;//I2C器件写数据有效标志位input Rd; //I2C器件读使能output reg[7:0] Rd_data; //I2C器件读数据output reg Rd_data_vaild;//I2C器件读数据有效标志位output reg Scl; //I2C时钟线inout Sda; //I2C数据线output reg Done; //对I2C器件读写完成标识位//主状态机状态localparam IDLE = 9'b0_0000_0001,//空闲状态WR_START = 9'b0_0000_0010,//写开始状态WR_CTRL = 9'b0_0000_0100,//写控制状态WR_WADDR = 9'b0_0000_1000,//写地址状态WR_DATA = 9'b0_0001_0000,//写数据状态RD_START = 9'b0_0010_0000,//读开始状态RD_CTRL = 9'b0_0100_0000,//读控制状态RD_DATA = 9'b0_1000_0000,//读数据状态STOP = 9'b1_0000_0000;//停止状态reg [8:0] main_state; //主状态机状态寄存器reg sda_en; //sda数据总线控制位reg sda_reg; //sda数据输出寄存器reg W_flag; //IIC写操作标志位reg R_flag; //IIC读操作标志位reg FF; //串行输出输入任务执行标志位wire[7:0] wr_ctrl_word; //写控制数据寄存器wire[7:0] rd_ctrl_word; //读控制数据寄存器reg [15:0]scl_cnt; //SCL时钟计数器reg scl_vaild; //IIC非空闲时期reg scl_high; //SCL时钟高电平中部标志位reg scl_low; //SCL时钟低电平中部标志位 reg [7:0] halfbit_cnt; //串行数据传输计数器reg ack; //串行输出输入高低电平计数完成标志位reg [1:0] waddr_cnt; //地址字节数计数器reg [7:0] wdata_cnt; //写数据字节数计数器reg [7:0] rdata_cnt; //读数据字节数计数器reg [7:0] sda_data_out; //待输出SDA串行数据reg [7:0] sda_data_in; //SDA串行输入后数据wire rdata_vaild_r; //读写控制字assign wr_ctrl_word = {4'b1010, Device_addr,1'b0};assign rd_ctrl_word = {4'b1010, Device_addr,1'b1};//I2C数据线采用三态门传输assign Sda = sda_en ? sda_reg : 1'bz;//I2C非空闲时期scl_vaild的产生always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)scl_vaild <= 1'b0;else if(Wr | Rd)scl_vaild <= 1'b1;else if(Done)scl_vaild <= 1'b0;elsescl_vaild <= scl_vaild;end//scl时钟计数器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)scl_cnt <= 16'd0;else if(scl_vaild)beginif(scl_cnt == SCL_CNT_M - 1)scl_cnt <= 16'd0;elsescl_cnt <= scl_cnt + 16'd1;endelsescl_cnt <= 16'd0;end//scl时钟,在计数器值到达最大值一半和0时翻转always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Scl <= 1'b1;else if(scl_cnt == SCL_CNT_M >>1)Scl <= 1'b0;else if(scl_cnt == 16'd0)Scl <= 1'b1;elseScl <= Scl;end //scl时钟高低电平中部标志位always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)scl_high <= 1'b0;else if(scl_cnt == (SCL_CNT_M>>2))scl_high <= 1'b1;elsescl_high <= 1'b0;end//scl时钟低电平中部标志位//(SCL_CNT_M>>2)和(SCL_CNT_M>>1)+(SCL_CNT_M>>2)分别为 1/4 的 SCL_CNT_M 和 3/4 的SCL_CNT_M 的计数值。always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)scl_low <= 1'b0;else if(scl_cnt == (SCL_CNT_M>>1)+(SCL_CNT_M>>2))scl_low <= 1'b1;elsescl_low <= 1'b0;end //主状态机always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginmain_state <= IDLE;sda_reg <= 1'b1;//三态控制信号W_flag <= 1'b0;//写标注 R_flag <= 1'b0;//读标注 Done <= 1'b0;//完成waddr_cnt <= 2'd1;//地址 wdata_cnt <= 8'd1;//写数据rdata_cnt <= 8'd1;//读数据endelse begincase(main_state)IDLE:begin//空闲状态sda_reg <= 1'b1;W_flag <= 1'b0;R_flag <= 1'b0;Done <= 1'b0;waddr_cnt <= 2'd1;wdata_cnt <= 8'd1;rdata_cnt <= 8'd1;if(Wr)beginmain_state <= WR_START;W_flag <= 1'b1;endelse if(Rd)beginmain_state <= WR_START;R_flag <= 1'b1;endelsemain_state <= IDLE;endWR_START:begin//写开始状态if(scl_low)begin//在scl_low寄存器下个周期发送起始信号main_state <= WR_CTRL;sda_data_out <= wr_ctrl_word;FF <= 1'b0;endelse if(scl_high)beginsda_reg <= 1'b0;main_state <= WR_START;endelsemain_state <= WR_START;endWR_CTRL:begin//写控制状态if(FF == 1'b0)send_8bit_data;else beginif(ack == 1'b1) begin//收到响应if(scl_low)beginmain_state <= WR_WADDR;FF <= 1'b0;if(Wdaddr_num == 2'b1)sda_data_out <= Word_addr[7:0];elsesda_data_out <= Word_addr[15:8];endelsemain_state <= WR_CTRL;endelse//未收到响应main_state <= IDLE;endendWR_WADDR:begin//写地址状态if(FF == 1'b0)send_8bit_data;else beginif(ack == 1'b1) begin//收到响应if(waddr_cnt == Wdaddr_num)beginif(W_flag && scl_low)beginmain_state <= WR_DATA;sda_data_out <= Wr_data;waddr_cnt <= 2'd1;FF <= 1'b0;endelse if(R_flag && scl_low)beginmain_state <= RD_START;sda_reg <= 1'b1;endelsemain_state <= WR_WADDR;endelse beginif(scl_low)beginwaddr_cnt <= waddr_cnt + 2'd1;main_state <= WR_WADDR;sda_data_out <= Word_addr[7:0];FF <= 1'b0;endelsemain_state <= WR_WADDR;endendelse//未收到响应main_state <= IDLE;endendWR_DATA:begin//写数据状态if(FF == 1'b0)send_8bit_data;else beginif(ack == 1'b1) begin//收到响应if(wdata_cnt == Wrdata_num)beginif(scl_low)beginmain_state <= STOP;sda_reg <= 1'b0;wdata_cnt <= 8'd1;endelsemain_state <= WR_DATA;endelse beginif(scl_low)beginwdata_cnt <= wdata_cnt + 8'd1;main_state <= WR_DATA;sda_data_out <= Wr_data;FF <= 1'b0;endelsemain_state <= WR_DATA;endendelse//未收到响应main_state <= IDLE;endendRD_START:begin//读开始状态if(scl_low)beginmain_state <= RD_CTRL;sda_data_out <= rd_ctrl_word;FF <= 1'b0;endelse if(scl_high)beginmain_state <= RD_START;sda_reg <= 1'b0;endelsemain_state <= RD_START;endRD_CTRL:begin//读控制状态if(FF == 1'b0)send_8bit_data;else beginif(ack == 1'b1) begin//收到响应if(scl_low)beginmain_state <= RD_DATA;FF <= 1'b0;endelsemain_state <= RD_CTRL;endelse//未收到响应main_state <= IDLE;endendRD_DATA:begin//读数据状态if(FF == 1'b0)receive_8bit_data;else beginif(rdata_cnt == Rddata_num)beginsda_reg <= 1'b1;if(scl_low)beginmain_state <= STOP;sda_reg <= 1'b0;endelsemain_state <= RD_DATA;endelse beginsda_reg <= 1'b0;if(scl_low)beginrdata_cnt <= rdata_cnt + 8'd1;main_state <= RD_DATA;FF <= 1'b0;endelsemain_state <= RD_DATA;endendendSTOP:begin//结束操作if(scl_high)beginsda_reg <= 1'b1;main_state <= IDLE;Done <= 1'b1;endelsemain_state <= STOP;enddefault:main_state <= IDLE;endcaseendend//sda串行接收与发送时scl高低电平计数器根据中计数器 halfbit_cnt 和数据接收方对发送的响应检测标志位 ack 以及串行输出、输入数据任务always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)halfbit_cnt <= 8'd0;else if((main_state == WR_CTRL)||(main_state == WR_WADDR)||(main_state == WR_DATA)||(main_state == RD_CTRL)||(main_state == RD_DATA))beginif(scl_low | scl_high)beginif(halfbit_cnt == 8'd17)halfbit_cnt <= 8'd0;elsehalfbit_cnt <= halfbit_cnt + 8'd1;endelsehalfbit_cnt <= halfbit_cnt;endelsehalfbit_cnt <= 8'd0;end//数据接收方对发送的响应检测标志位always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)ack <= 1'b0;else if((halfbit_cnt == 8'd16)&&scl_high&&(Sda==1'b0))ack <= 1'b1;else if((halfbit_cnt == 8'd17)&&scl_low)ack <= 1'b0;elseack <= ack;end//输出串行数据任务task send_8bit_data;if(scl_high && (halfbit_cnt == 8'd16))FF <= 1;else if(halfbit_cnt < 8'd17)beginsda_reg <= sda_data_out[7];if(scl_low)sda_data_out <= {sda_data_out[6:0],1'b0};elsesda_data_out <= sda_data_out;endelse;endtask//串行数据输入任务task receive_8bit_data;if(scl_low && (halfbit_cnt == 8'd15))FF <= 1;else if((halfbit_cnt < 8'd15))beginif(scl_high)sda_data_in <= {sda_data_in[6:0],Sda};else beginsda_data_in <= sda_data_in;endendelse;endtask//sda三态使能信号sda_enalways@(*)begincase(main_state)IDLE:sda_en = 1'b0;WR_START,RD_START,STOP:sda_en = 1'b1;WR_CTRL,WR_WADDR,WR_DATA,RD_CTRL:if(halfbit_cnt < 16)sda_en = 1'b1;elsesda_en = 1'b0;RD_DATA:if(halfbit_cnt < 16)sda_en = 1'b0;elsesda_en = 1'b1; default:sda_en = 1'b0; endcaseend//写数据有效标志位assign Wr_data_vaild = ((main_state==WR_WADDR)&&(waddr_cnt==Wdaddr_num)&&(W_flag && scl_low)&&(ack == 1'b1))||((main_state == WR_DATA)&&(ack == 1'b1)&&(scl_low)&&(wdata_cnt != Wrdata_num));//读数据有效标志位前寄存器assign rdata_vaild_r = (main_state == RD_DATA)&&(halfbit_cnt == 8'd15)&&scl_low;//读出数据有效标志位always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Rd_data_vaild <= 1'b0;else if(rdata_vaild_r)Rd_data_vaild <= 1'b1;elseRd_data_vaild <= 1'b0;end//读出的有效数据always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Rd_data <= 8'd0;else if(rdata_vaild_r)Rd_data <= sda_data_in;elseRd_data <= Rd_data;endendmodule

相关文章:

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1)

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1) 单字节写时序单字节读时序I2C 控制器设计模块框图scl_high 和 scl_low 产生的时序图状态转移图 Verilog代码 FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(1) FPG…...

LabVIEW编程开发NI-USRP

LabVIEW编程开发NI-USRP 可编程性是SDR的关键特性,它使人们能够将无线电外围设备转换为先进的无线系统。USRP是市场上最开放、最通用的SDR,可帮助工程师在主机和FPGA上使用各种软件开发工具构建系统。 有多种选项可用于对基于SDR的系统的主机进行编程。…...

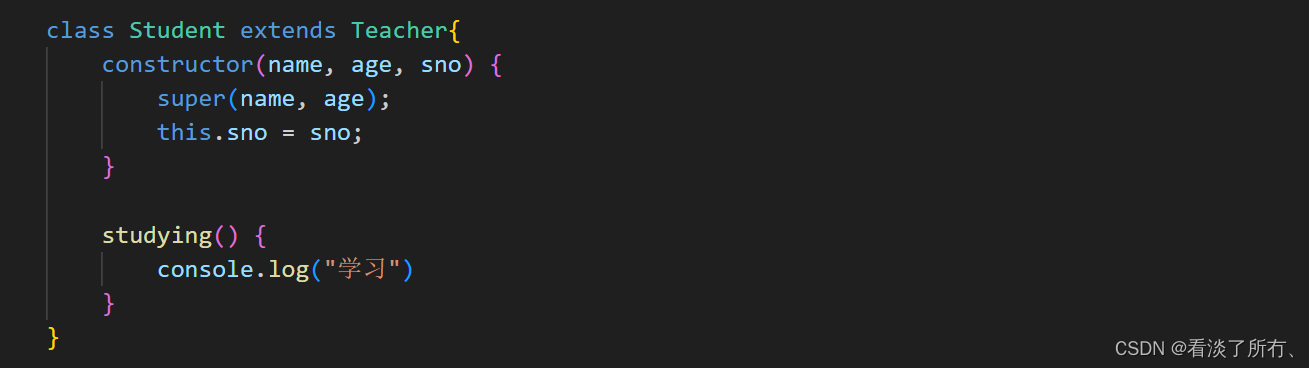

ES6中实现继承

本篇文章主要说明在ES6中如何实现继承,学过java的小伙伴,对class这个关键字应该不陌生,ES6中也提供了class这个关键字作为实现类的语法糖,咱们一起实现下ES6中的继承。 实现思路 首先直接通过class来声明一个Teacther类ÿ…...

车载通信架构 —— 新车载总线类型下(以太网)的通信架构

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。 老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师: 屏蔽力是信息过载时代一个人的特殊竞争力,任何消耗你的人和事,多看一眼都是你的不…...

ArkTS - HarmonyOS服务卡片(创建)

可以参考官网文档 其中我们在已有的文件中File > New > Service Widget创建你想要的小卡片 本文章发布时目前可使用的模板就三种 有卡片后的new 最终效果...

Zotero在word中插入带超链接的参考文献/交叉引用/跳转参考文献

Zotero以其丰富的插件而闻名,使用起来十分的带劲,最重要的是它是免费的、不卡顿,不像某专业软件。 然而Zotero在word插入参考文献时,无法为参考文献添加超链接,这是一个不得不提的遗憾。 不过,有大佬已经…...

持续集成部署-k8s-配置与存储-配置管理:ConfigMap 的热更新

ConfigMap 的热更新 1. 简介2. 新建 Pod3. 使用 edit 命令编辑修改4. 使用 replace 命令替换修改1. 简介 在 Kubernetes 中,ConfigMap 是用于存储非敏感配置数据的 API 对象,它可以被挂载到 Pod 中作为文件或环境变量。ConfigMap 的热更新指的是在不重启 Pod 的情况下,动态…...

Python文本段落翻译

Python文本段落翻译 1、Translate库2、基本使用 1、Translate库 translate非标准库是Python中可以实现对多种语言进行互相翻译的库,translate可以将原始文本或段落翻译成我们需要的目标语言 translate支持多种语言,常见的例如: zh/zh-CN&…...

Flink(七)【输出算子(Sink)】

前言 今天是我写博客的第 200 篇,恍惚间两年过去了,现在已经是大三的学长了。仍然记得两年前第一次写博客的时候,当时学的应该是 Java 语言,菜的一批,写了就删,怕被人看到丢脸。当时就想着自己一年之后&…...

【自我管理】To-do list已过时?学写Done List培养事业成功感

自我管理:已完成清单(doneList)培养事业成功感 待办事项清单常常让人感到压力山大,让人不想面对工作。但是,你知道吗?除了待办清单之外,还有一个叫做「已完成清单」的东西,它可能更符…...

优思学院|什么是精益生产管理?从一个生活上的故事出发来说明。

你关掉电脑,离开办公室。 一个小时后,你进入家门和孩子们在一起。 你和家人一起吃晚饭。 你的老板打电话来查看你的项目进展。 你哄孩子入睡并给他们读个故事。 作为一个负责任的父母,你想要与孩子们的互动时间增加并提高生活的质量&…...

Swagger-----knife4j框架

简介 使得前后端分离开发更加方便,有利于团队协作 接口的文档在线自动生成,降低后端开发人员编写接口文档的负担 功能测试 Spring已经将Swagger纳入自身的标准,建立了Spring-swagger项目,现在叫Springfox。通过在项目中引入Spri…...

企业数字化过程中数据仓库与商业智能的目标

当前环境下,各领域企业通过数字化相关的一切技术,以数据为基础、以用户为核心,创建一种新的,或对现有商业模式进行重塑就是数字化转型。这种数字化转型给企业带来的效果就像是一次重构,会对企业的业务流程、思维文化、…...

协议)

从零开始写一个APM监控程序(一)协议

APM(Application Performance Monitoring)是一种用于监控和管理应用程序性能的解决方案。它通过收集、分析和报告应用程序的性能数据,帮助开发人员和系统管理员更好地了解应用程序的运行状况,识别潜在的性能问题,并进行…...

UDP网络套接字编程

先来说说数据在网络上的传输过程吧,我们知道系统其实终究是根据冯诺依曼来构成的,而网络数据是怎么发的呢? 其实很简单,网络有五层。如下: 如上图,我们知道的是,每层对应的操作系统中的那些地方…...

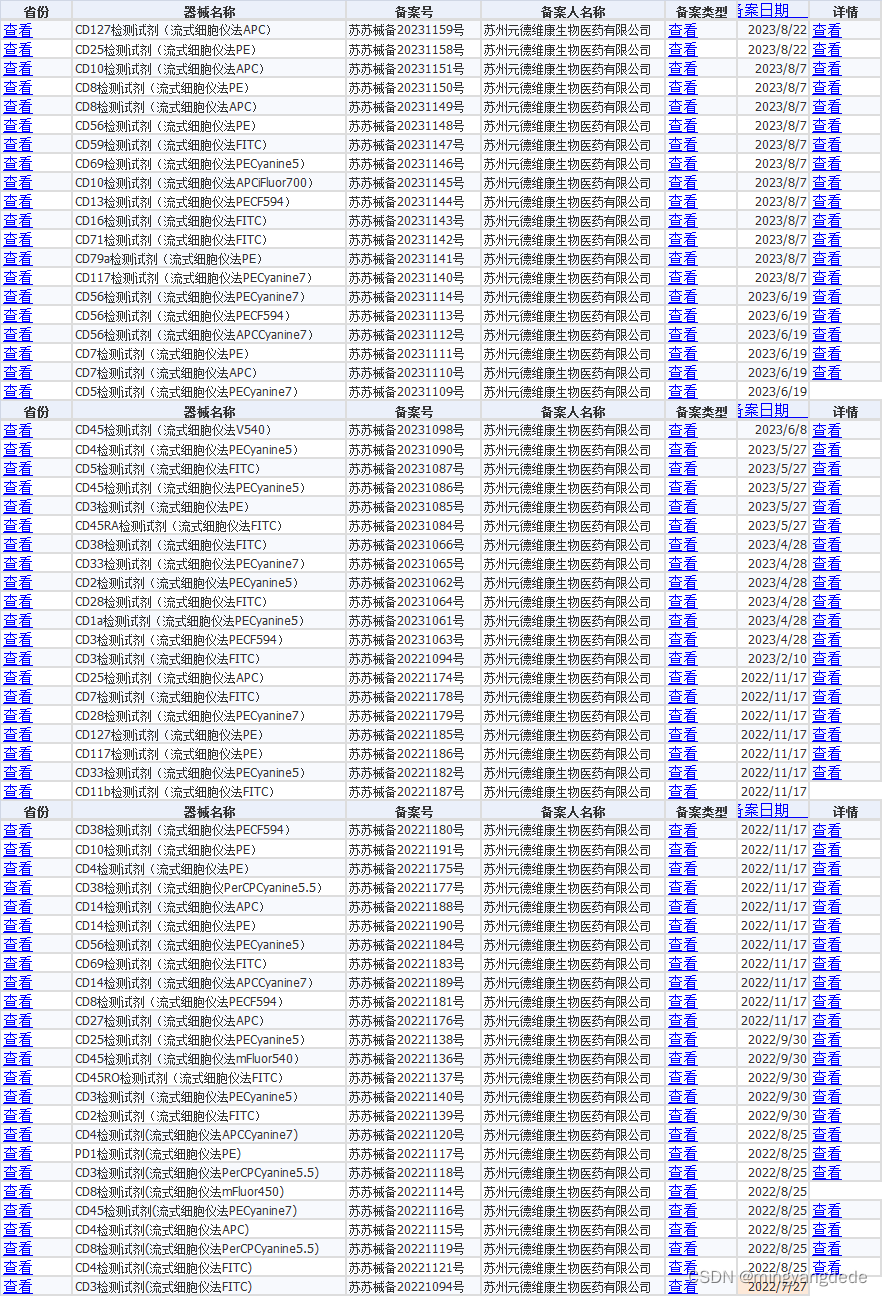

【苏州元德维康生物医药-注册】

...

)

从零带你底层实现unordered_map (1)

💯 博客内容:从零带你实现unordered_map 😀 作 者:陈大大陈 🚀 个人简介:一个正在努力学技术的准C后端工程师,专注基础和实战分享 ,欢迎私信! 💖 欢迎大家…...

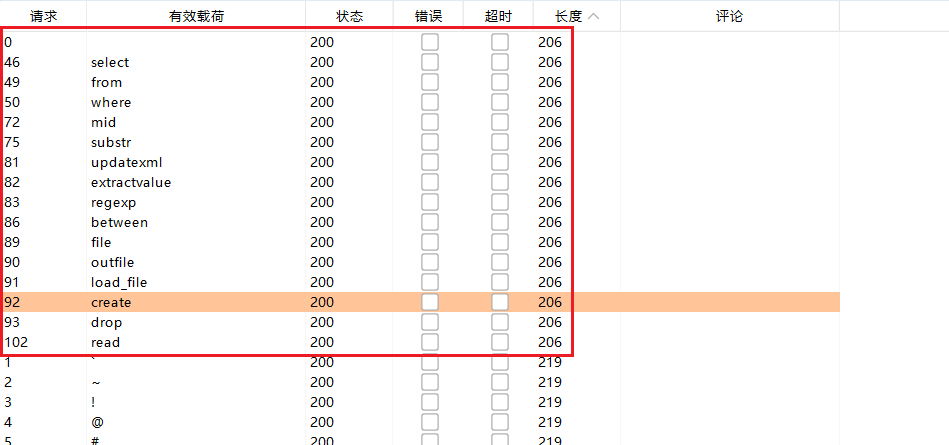

第六届浙江省大学生网络与信息安全竞赛 2023年 初赛/决赛 WEB方向 Writeup

-------------------【初赛】------------------- easy php 简单反序列化 __debuginfo()魔术方法打印所需调试信息,反序列化时候执行! 链子如下: BBB::__debuginfo()->CCC::__toString()->AAA::__call()EXP: <?php…...

设计模式篇---装饰模式

文章目录 概念结构实例总结 概念 装饰模式:动态的给一个对象增加一些额外的职责。就扩展功能而言,装饰模式提供了 一种比使用子类更加灵活的替代方案。 装饰模式是一种对象结构型模式,它以对客户透明的方式动态地给一个对象附加上更多的责任…...

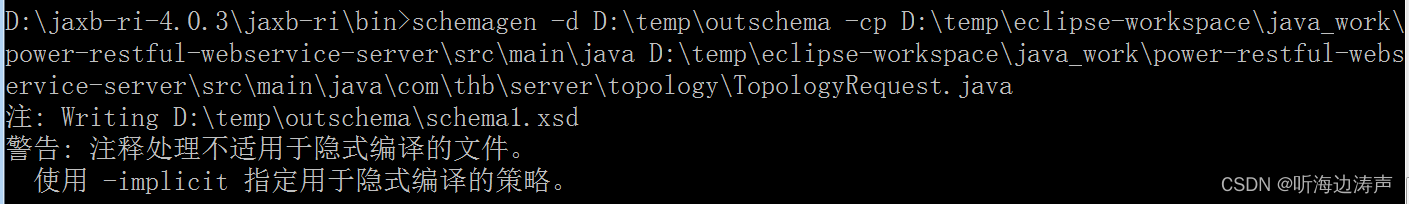

JAXB:根据Java文件生成XML schema文件

说明 JAXB有个schemagen脚本,可以根据Java文件生成XML schema。这个工具在JAXB独立发布包中有,可以从官网下载JAXB的独立发布包: https://eclipse-ee4j.github.io/jaxb-ri/ 示例 使用schemagen -d <path> <java files>格式 …...

毕业季论文救星:深度解析百考通AI如何智能攻克文献综述与开题报告

又到一年毕业季,无数莘莘学子在为自己学术生涯的“终极答卷”——毕业论文而挑灯夜战。其中,文献综述的浩如烟海与开题报告的千头万绪,无疑是横亘在大多数同学面前的两座大山。你是否也曾面对海量文献不知如何筛选梳理?是否为构建…...

)

从RS-485到MQTT:手把手教你为BMS Modbus设备搭建物联网网关(Node-RED实战)

从RS-485到MQTT:手把手教你为BMS Modbus设备搭建物联网网关(Node-RED实战) 当工业现场的BMS设备还在使用Modbus-RTU协议时,如何让这些"信息孤岛"融入现代物联网架构?这个问题困扰着许多能源管理系统工程师。…...

tao-8k在AI应用开发中的价值:为LangChain+LlamaIndex提供高质量向量底座

tao-8k在AI应用开发中的价值:为LangChainLlamaIndex提供高质量向量底座 1. 为什么需要高质量的文本嵌入模型 在构建AI应用时,我们经常需要将文本转换为计算机能够理解的数值表示,这就是文本嵌入(embedding)的核心任务…...

16-Kotlin高阶特性-Lambda详解

Kotlin Lambda 表达式完全指南Lambda 表达式是 Kotlin 函数式编程的核心特性之一,它让代码更简洁、表达力更强。无论是集合操作、协程、还是 Jetpack Compose 中的 UI 回调,都大量使用 lambda。本文将系统讲解 Kotlin lambda 的语法形式、含义、各种语法…...

别再乱调参数了!用Matlab polyfit做曲线拟合,从欠拟合到过拟合的实战避坑指南

Matlab曲线拟合实战:从polyfit到正则化的高阶避坑指南 当你面对一组杂乱无章的实验数据时,是否曾为选择哪个多项式阶数而纠结?工程师小张最近就遇到了这个难题——他在处理传感器温度补偿数据时,发现3阶拟合不够精准,但…...

WaveTools鸣潮工具箱终极指南:画质优化与抽卡分析的完整解决方案

WaveTools鸣潮工具箱终极指南:画质优化与抽卡分析的完整解决方案 【免费下载链接】WaveTools 🧰鸣潮工具箱 项目地址: https://gitcode.com/gh_mirrors/wa/WaveTools WaveTools鸣潮工具箱是一款专为《鸣潮》玩家设计的强大辅助工具,它…...

如何让Windows任务栏变透明?TranslucentTB完整教程指南

如何让Windows任务栏变透明?TranslucentTB完整教程指南 【免费下载链接】TranslucentTB A lightweight utility that makes the Windows taskbar translucent/transparent. 项目地址: https://gitcode.com/gh_mirrors/tr/TranslucentTB 想要为你的Windows桌面…...

运维实战:思科NAT配置全解析与典型场景应用

1. 为什么企业网络离不开NAT技术 想象一下你公司的内网有200台电脑,但ISP只分配了5个公网IP地址——这就是NAT技术大显身手的场景。作为网络工程师,我处理过太多类似案例,最夸张的一个客户用1个公网IP支撑了整个500人办公区的上网需求。 NA…...

在Windows 11上用VirtualBox搞定WRF-Hydro 5.2.0:一个水文模型小白的Ubuntu 22.04虚拟机避坑实录

在Windows 11上用VirtualBox搞定WRF-Hydro 5.2.0:一个水文模型小白的Ubuntu 22.04虚拟机避坑实录 第一次接触WRF-Hydro时,我盯着满屏的命令行代码和复杂的依赖关系,感觉像在破解某种外星密码。作为一名水文专业的研究生,我的Linux…...

的Split Mode配置实战)

解析RK3566平台双摄(OV5648+GC2145)的Split Mode配置实战

1. RK3566双摄系统架构解析 当我们需要在嵌入式设备上实现双摄像头功能时,RK3566平台提供了一个非常灵活的解决方案。这个平台虽然只有一个物理MIPI CSI-2 DPHY接口,但通过Split Mode技术,可以将其拆分为多个逻辑接口使用。这就好比一条四车道…...