Xilinx Zynq-7000系列FPGA任意尺寸图像缩放,提供两套工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- FPGA图像处理方案

- FPGA图像缩放方案

- 3、设计思路详解

- HLS 图像缩放介绍

- 4、工程代码1:图像缩放 HDMI 输出

- PL 端 FPGA 逻辑设计

- PS 端 SDK 软件设计

- 5、工程代码2:图像缩放 LCD 输出

- PL 端 FPGA 逻辑设计

- PS 端 SDK 软件设计

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证并演示

- 准备工作

- 工程1输出静态演示

- 工程2输出静态演示

- 8、福利:工程源码获取

Xilinx Zynq-7000系列FPGA任意尺寸图像缩放,提供两套工程源码和技术支持

1、前言

没玩过图像缩放都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。

目前市面上主流的FPGA图像缩放方案如下:

1:Xilinx的HLS方案,该方案简单,易于实现,但只能用于Xilinx自家的FPGA;

2:非纯Verilog方案,大部分代码使用Verilog实现,但中间的fifo或ram等使用了IP,导致移植性变差,难以在Xilinx、Altera和国产FPGA之间自由移植;

3:纯Verilog方案;

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为1280x720@30Hz分辨率;然后调用Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;添加自定义的HLS图像缩放IP核,将输入视频进行任意尺寸图像缩放操作,该操作通过Zynq软核SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,调用Zynq将VDMA配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示,或然后添加自定义的LCD发送IP将RGB视频转换为LCD的RGB视频送LCD显示;

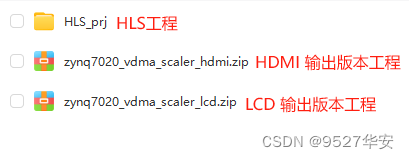

提供两套vivado2019.1版本的工程源码和技术支持,两套工程的区别在于输出方式不同,详情如下:

第一套vivado工程源码:输入,OV5640摄像头;输出,HDMI显示器;

第二套vivado工程源码:输入,OV5640摄像头;输出,LCD显示器;

本博客详细描述了Xilinx Zynq7000系列FPGA任意尺寸图像缩放的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;整个工程调用Zynq软核做IP的配置,Zynq的配置在SDK里以C语言软件代码的形式运行,所以整个工程包括FPGA逻辑设计和SDK软件设计两部分,需要具备FPGA和嵌入式C语言的综合能力,不适合初学者或者小白;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

FPGA图像处理方案

我的主页目前有FPGA图像处理专栏,改专栏收录了我目前手里已有的FPGA图像处理方案,包括图像缩放、图像识别、图像拼接、图像融合、图像去雾、图像叠加、图像旋转、图像增强、图像字符叠加等等;以下是专栏地址:

点击直接前往

FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

3、设计思路详解

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为1280x720@30Hz分辨率;然后调用Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;添加自定义的HLS图像缩放IP核,将输入视频进行任意尺寸图像缩放操作,该操作通过Zynq软核SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,调用Zynq将VDMA配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示,或然后添加自定义的LCD发送IP将RGB视频转换为LCD的RGB视频送LCD显示;

提供两套vivado2019.1版本的工程源码和技术支持,两套工程的区别在于输出方式不同,详情如下:

第一套vivado工程源码:输入,OV5640摄像头;输出,HDMI显示器;

第二套vivado工程源码:输入,OV5640摄像头;输出,LCD显示器;

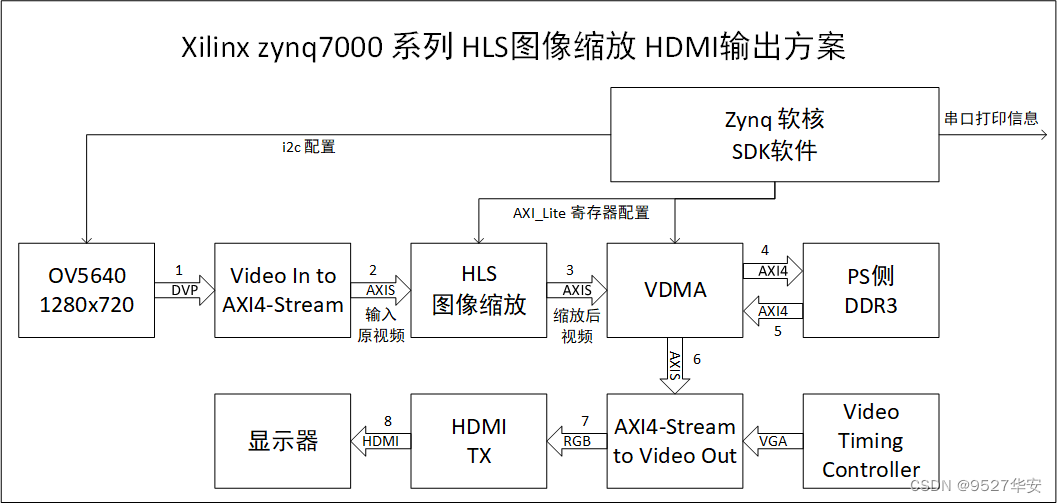

第一套vivado工程源码设计框图如下:

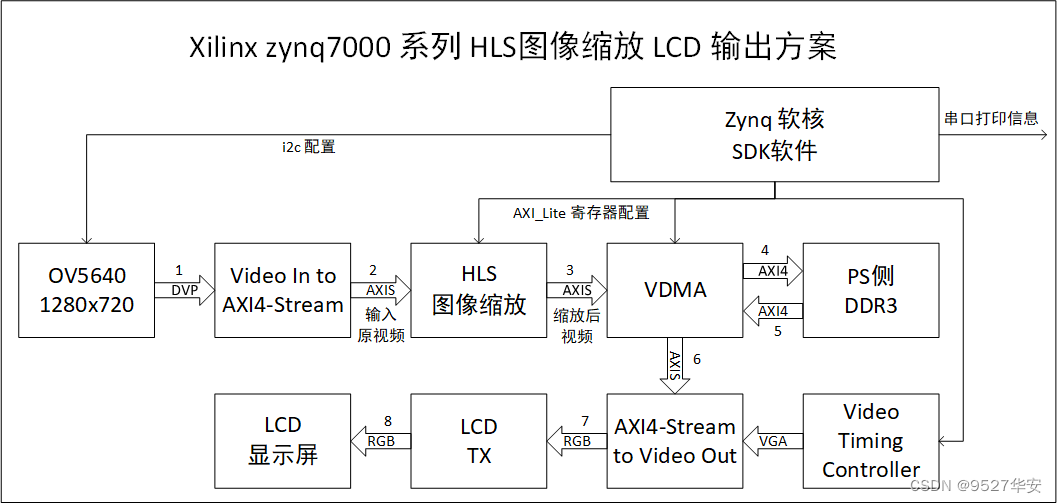

第二套vivado工程源码设计框图如下:

框图解释:箭头表示数据流向,箭头内文字表示数据格式,箭头外数字表示数据柳巷的步骤;

HLS 图像缩放介绍

由于工程所用到的IP都是常用IP,所以这里重点介绍一下HLS图像缩放IP;

支持最大分辨率:1920x1080@60Hz;但可以修改HLS源码增大分辨率,前提是你的FPGA逻辑资源要够大;

输入视频格式:AXI4-Stream;

输出视频格式:AXI4-Stream;

需要SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;目前只适用于Xilinx Zynq7000系列FPGA使用,但可以修改HLS工程的器件类型来适应其他器件,比如Artix7、Kintex7等等;

提供自定义的配置API,通过调用该库函数即可轻松使用,具体参考SDK代码;

提供HLS工程源码,可任意修改,HLS版本为2019.1;

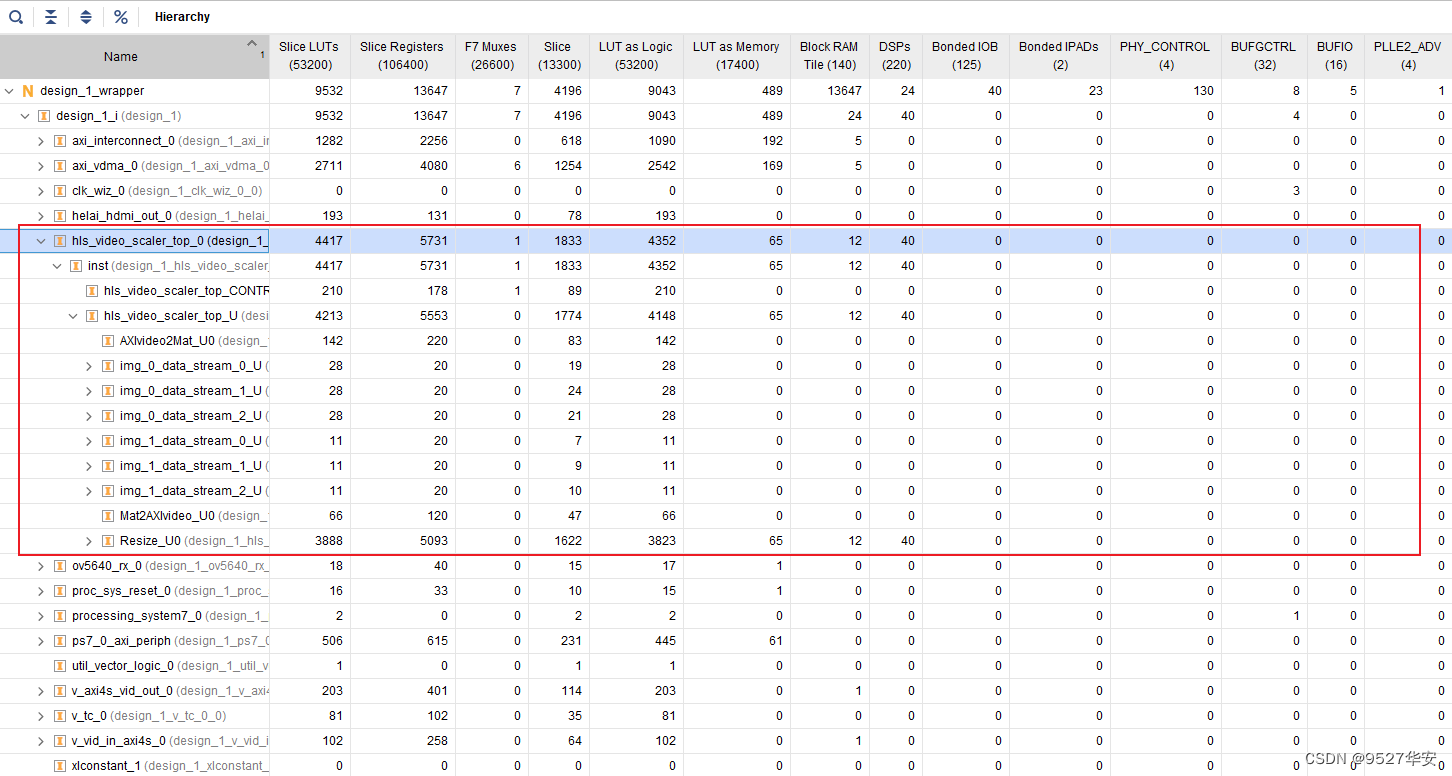

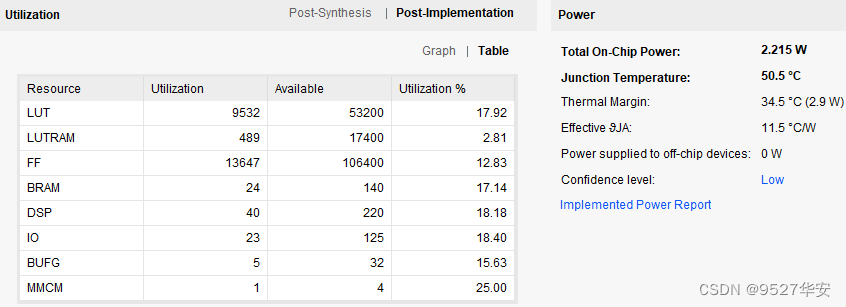

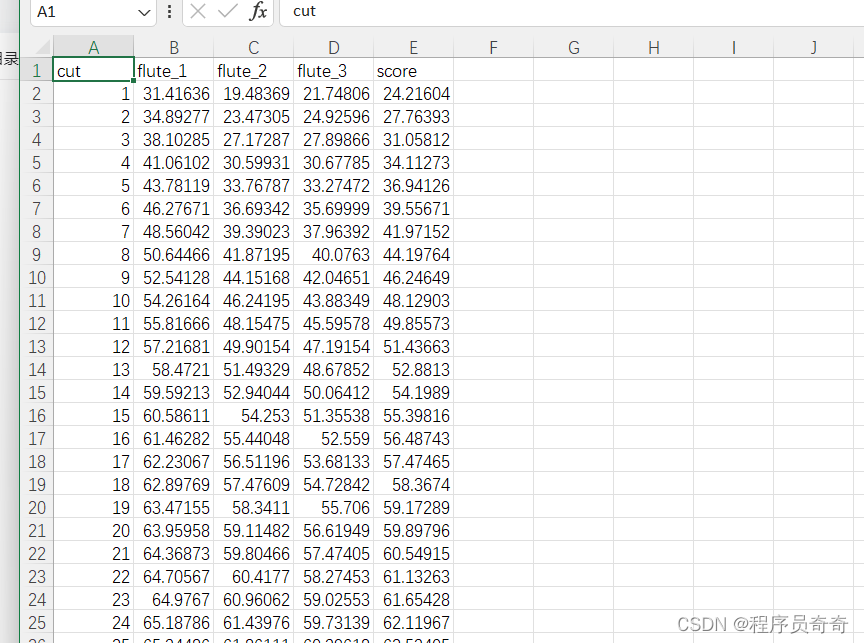

模块占用的FPGA逻辑资源如下:

请谨慎评估你的FPGA资源情况;

4、工程代码1:图像缩放 HDMI 输出

PL 端 FPGA 逻辑设计

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720p;

输出:HDMI,1080P分辨率下的有效区域显示;

工程作用:Xilinx Zynq7000系列FPGA任意尺寸图像缩放, HDMI 输出;

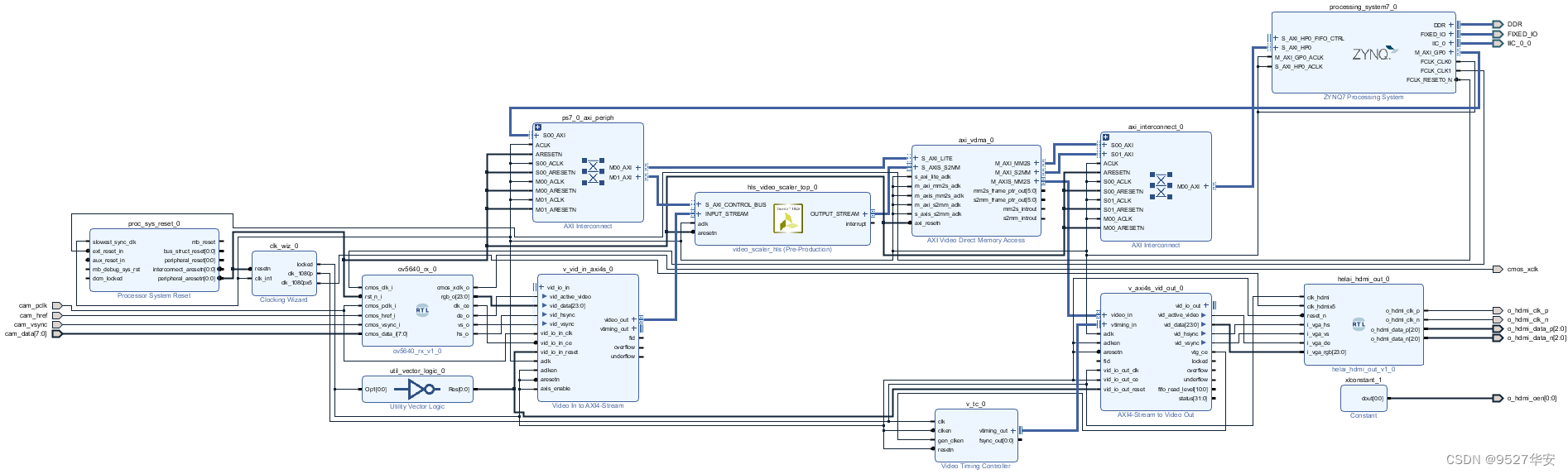

工程BD如下:

工程代码架构如下:

工程的资源消耗和功耗如下:

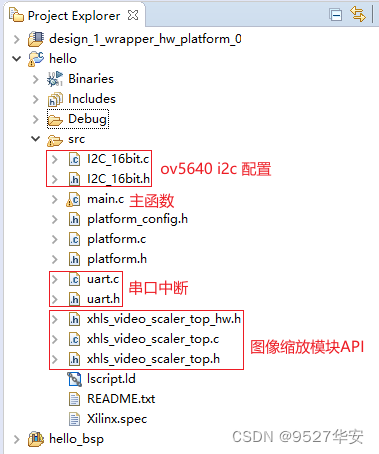

PS 端 SDK 软件设计

PS 端 SDK 软件工程代码架构如下:

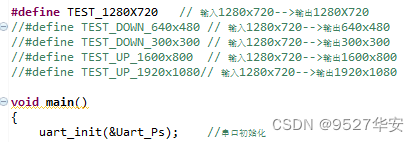

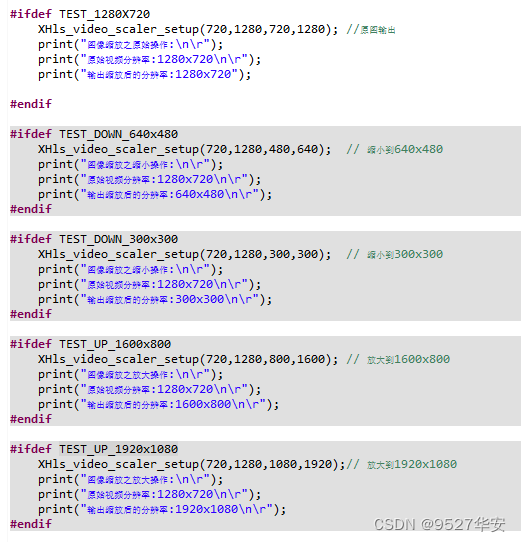

主函数通过如下的五个宏定义设计了五种不同的图像缩放方案:

ov5640输入分辨率1280x720,HDMI输出分辨率1280x720;

ov5640输入分辨率1280x720,HDMI输出分辨率640x480;

ov5640输入分辨率1280x720,HDMI输出分辨率300x300;

ov5640输入分辨率1280x720,HDMI输出分辨率1600x800;

ov5640输入分辨率1280x720,HDMI输出分辨率1920x1080;

主函数进行相应的图像缩放操作,并打印相关信息,代码如下:

5、工程代码2:图像缩放 LCD 输出

PL 端 FPGA 逻辑设计

开发板FPGA型号:Xilinx–Zynq7020–xc7z020clg400-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头,分辨率1280x720p;

输出:LCD 4.3寸显示屏,分辨率800x480,800x480分辨率下的有效区域显示;

工程作用:Xilinx Zynq7000系列FPGA任意尺寸图像缩放, LCD 输出;

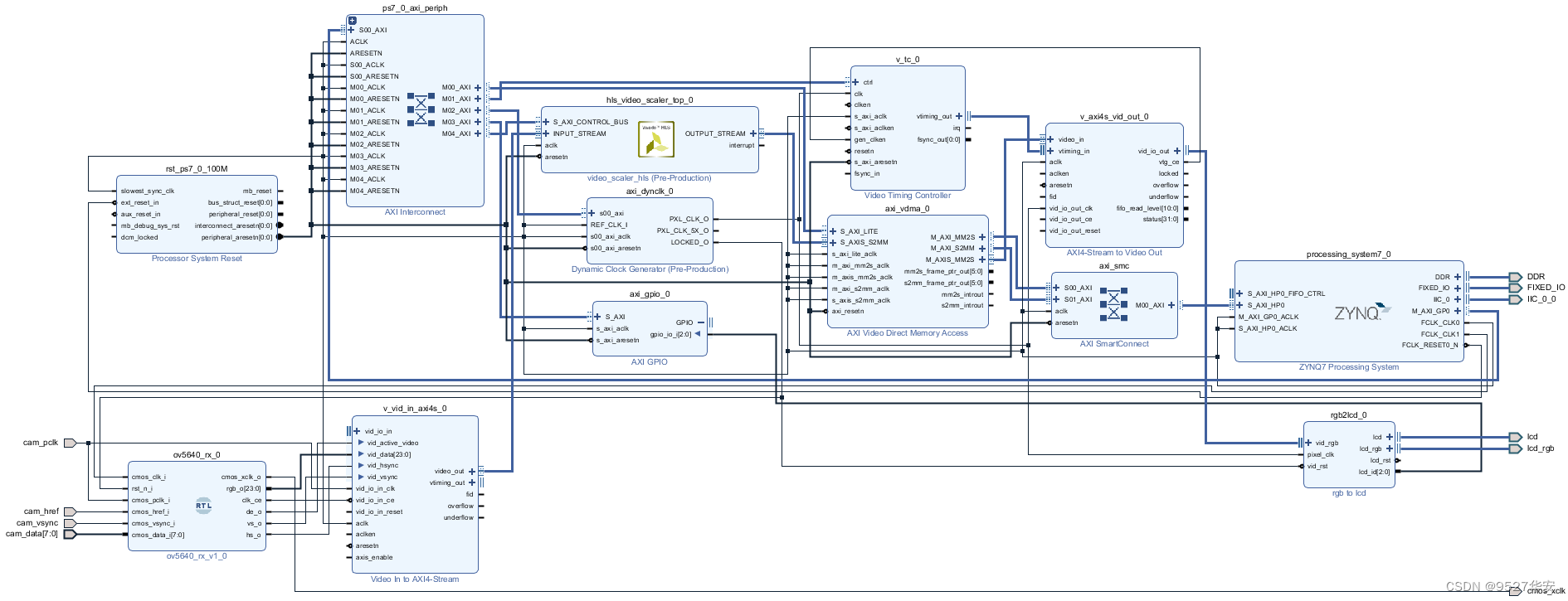

工程BD如下:

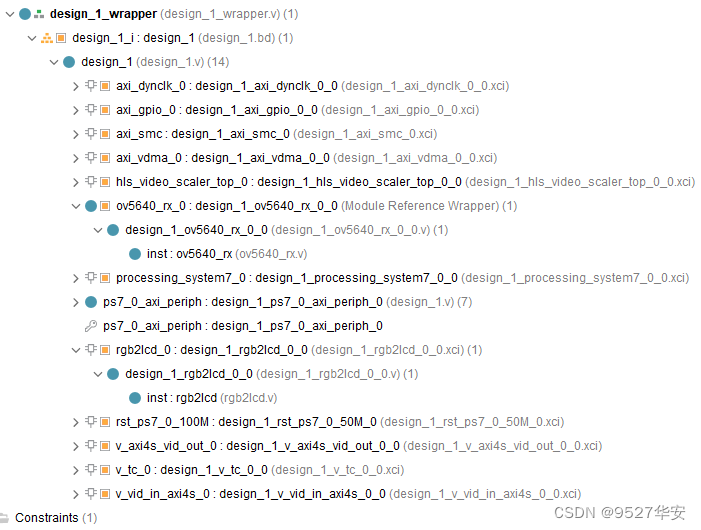

工程代码架构如下:

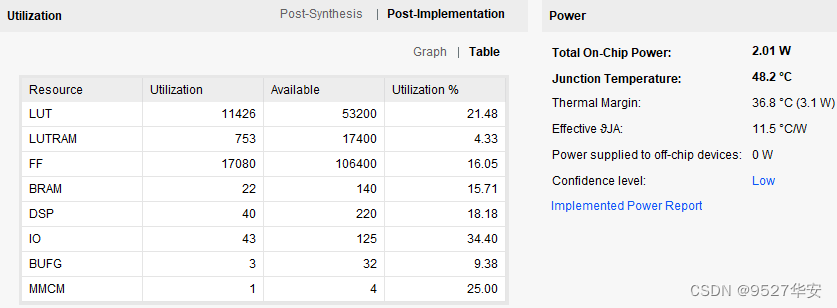

工程的资源消耗和功耗如下:

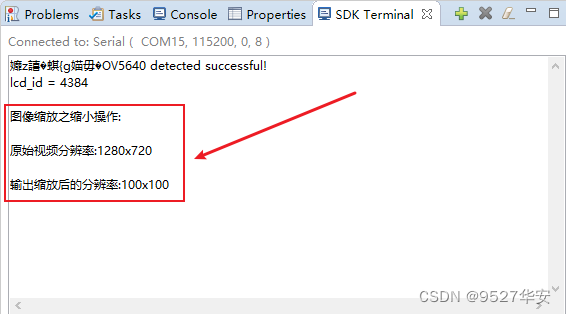

PS 端 SDK 软件设计

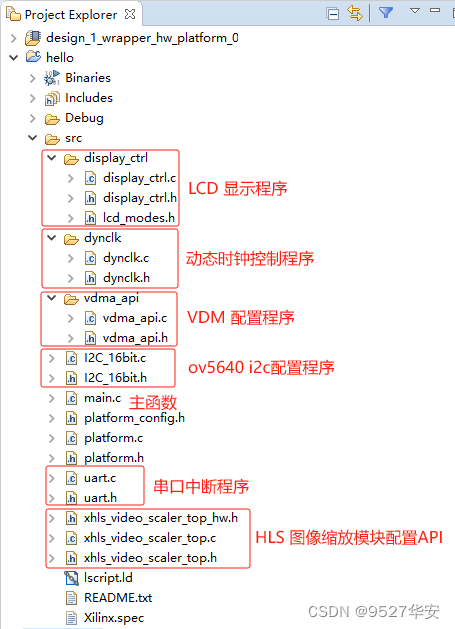

PS 端 SDK 软件工程代码架构如下:

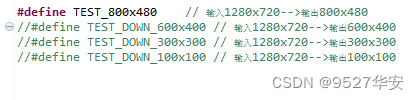

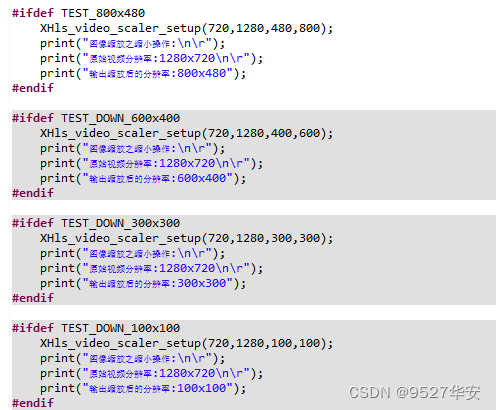

主函数通过如下的五个宏定义设计了四种不同的图像缩放方案:

ov5640输入分辨率1280x720,LCD输出分辨率800x480;

ov5640输入分辨率1280x720,LCD输出分辨率600x400;

ov5640输入分辨率1280x720,LCD输出分辨率300x300;

ov5640输入分辨率1280x720,LCD输出分辨率100x100;

主函数进行相应的图像缩放操作,并打印相关信息,代码如下:

6、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证并演示

准备工作

Zynq7000系列开发板;

OV5640摄像头;

HDMI显示器或者LCD显示屏,我用到的LCD显示屏为4.3寸分辨率800x480;

工程1输出静态演示

工程1:ov5640输入分辨率1280x720,HDMI输出分辨率1280x720;

HDMI显示输出和串口打印分别如下:

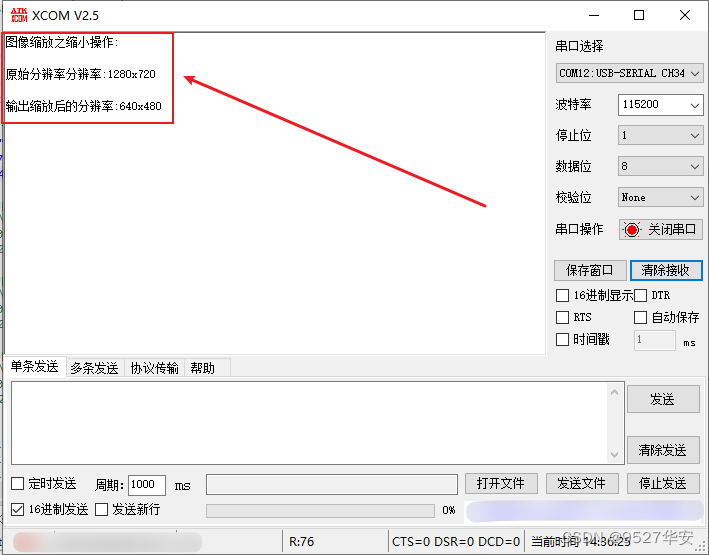

工程1:ov5640输入分辨率1280x720,HDMI输出分辨率640x480;

HDMI显示输出和串口打印分别如下:

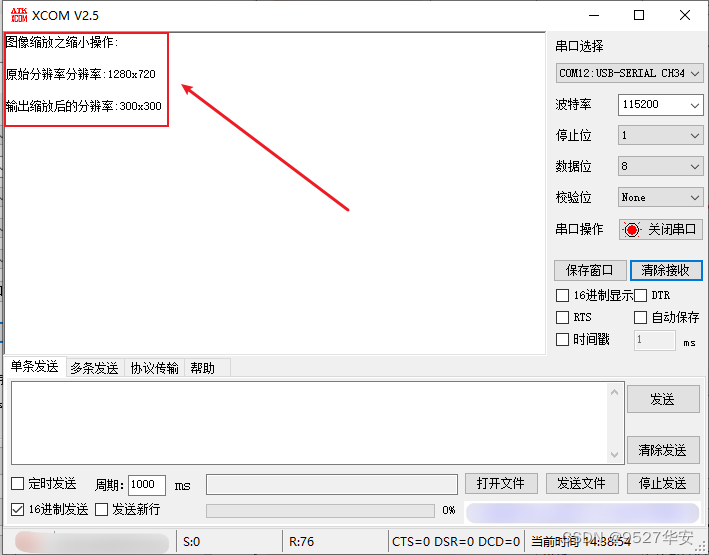

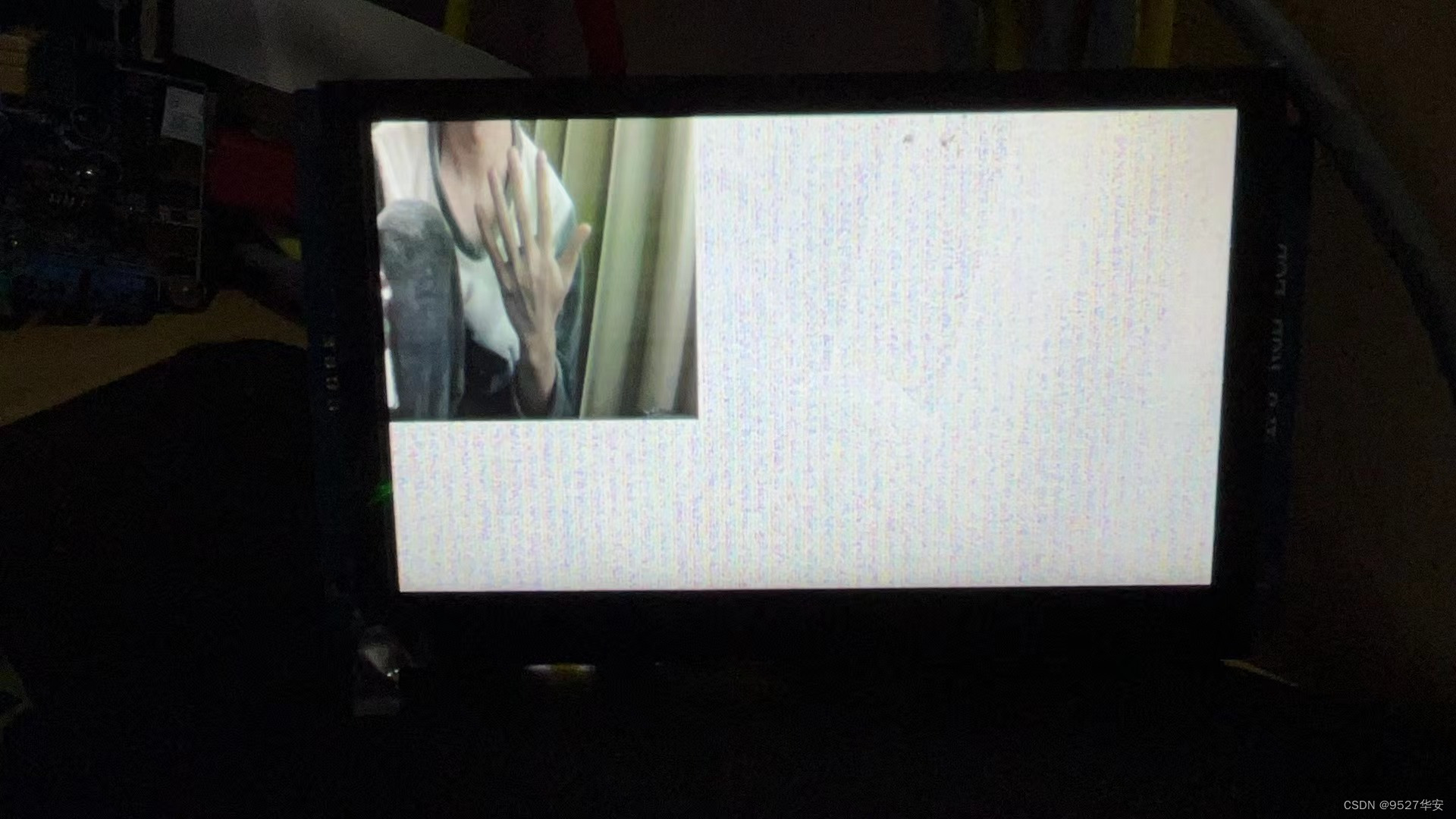

工程1:ov5640输入分辨率1280x720,HDMI输出分辨率300x300;

HDMI显示输出和串口打印分别如下:

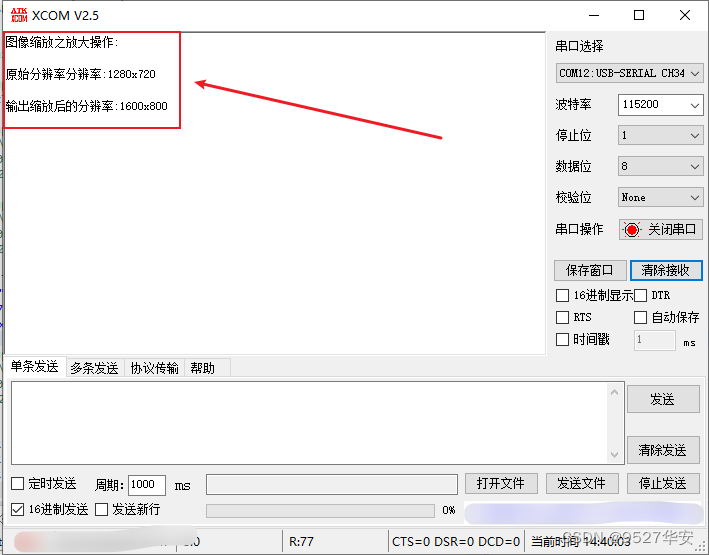

工程1:ov5640输入分辨率1280x720,HDMI输出分辨率1600x800;

HDMI显示输出和串口打印分别如下:

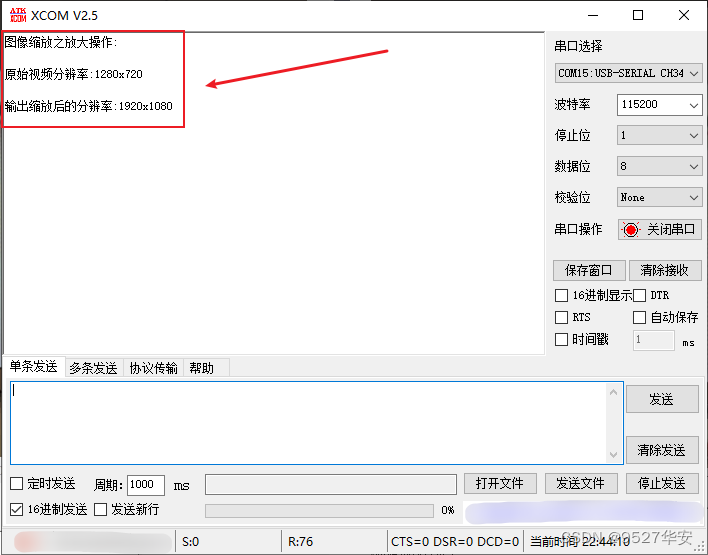

工程1:ov5640输入分辨率1280x720,HDMI输出分辨率1920x1080;

HDMI显示输出和串口打印分别如下:

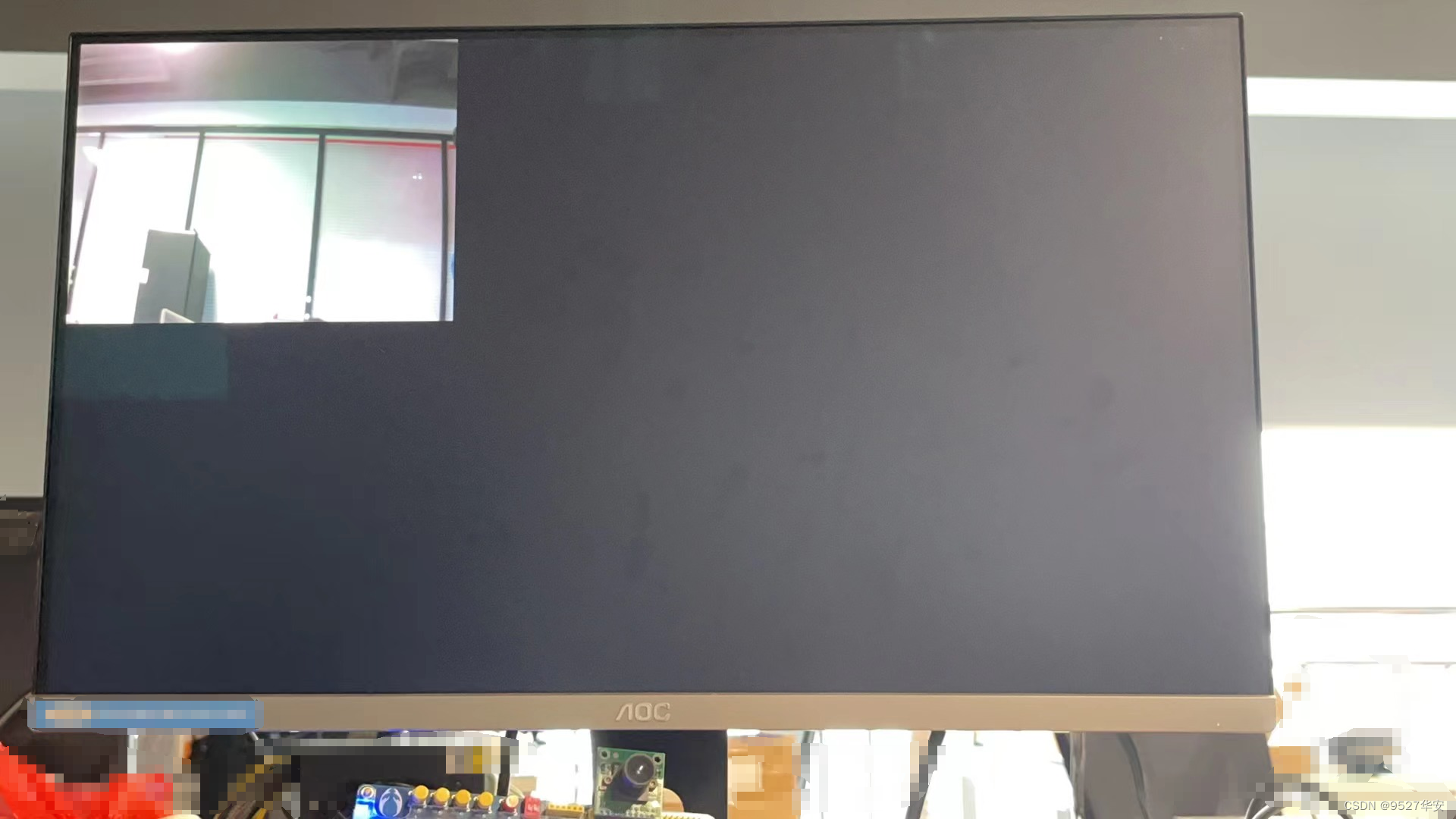

工程2输出静态演示

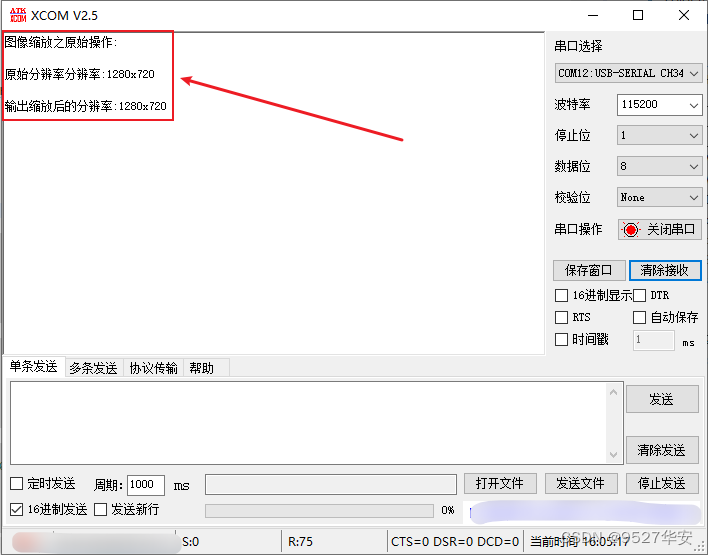

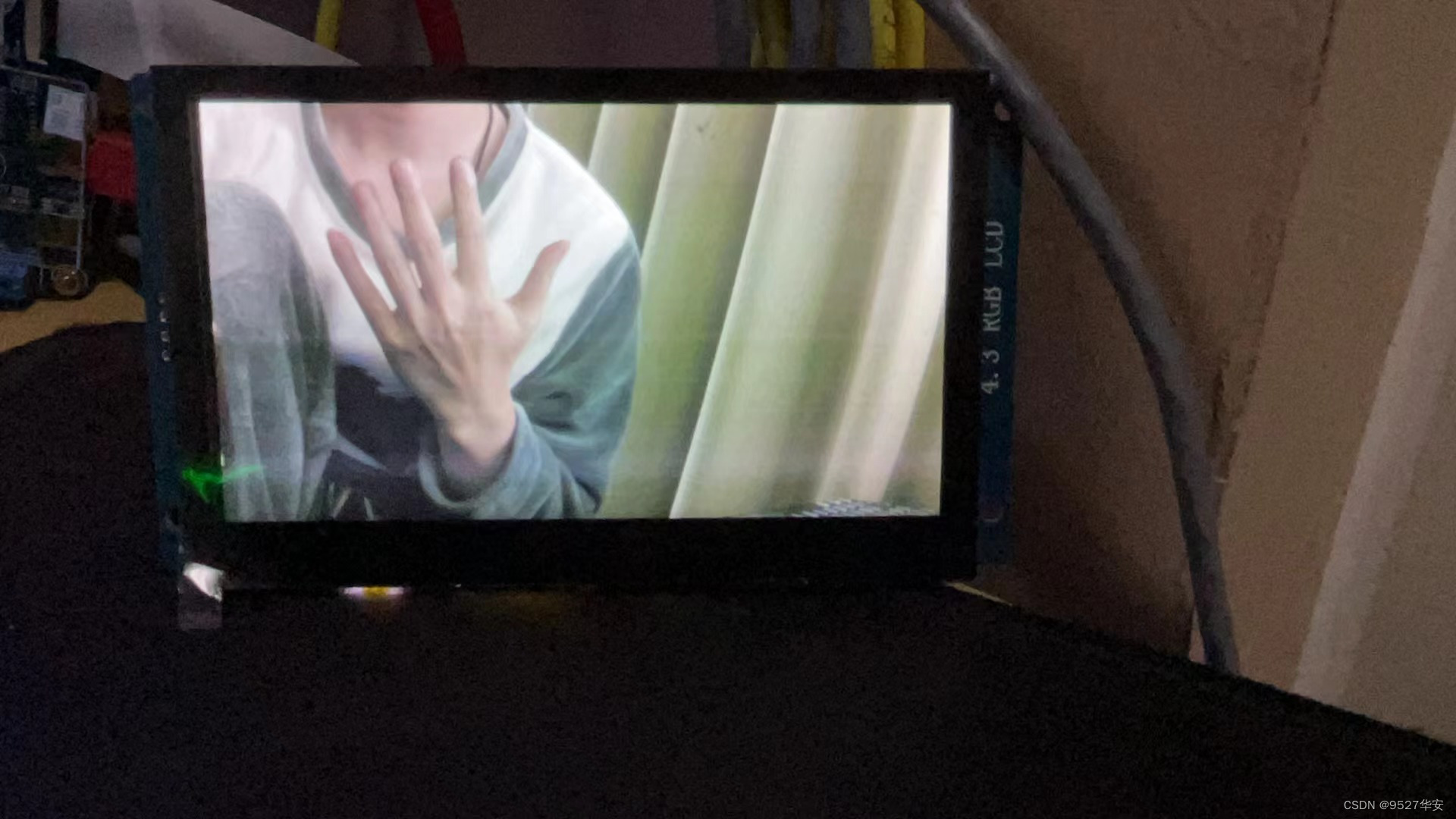

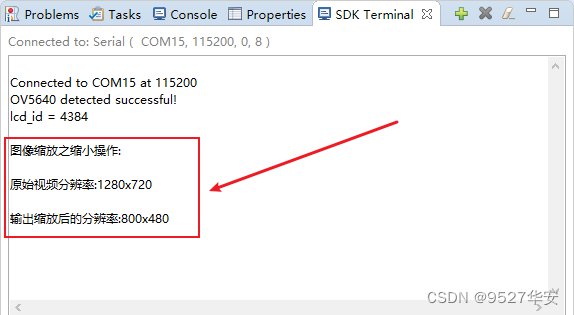

工程2:ov5640输入分辨率1280x720,LCD输出分辨率800x480;

LCD显示输出和串口打印分别如下:

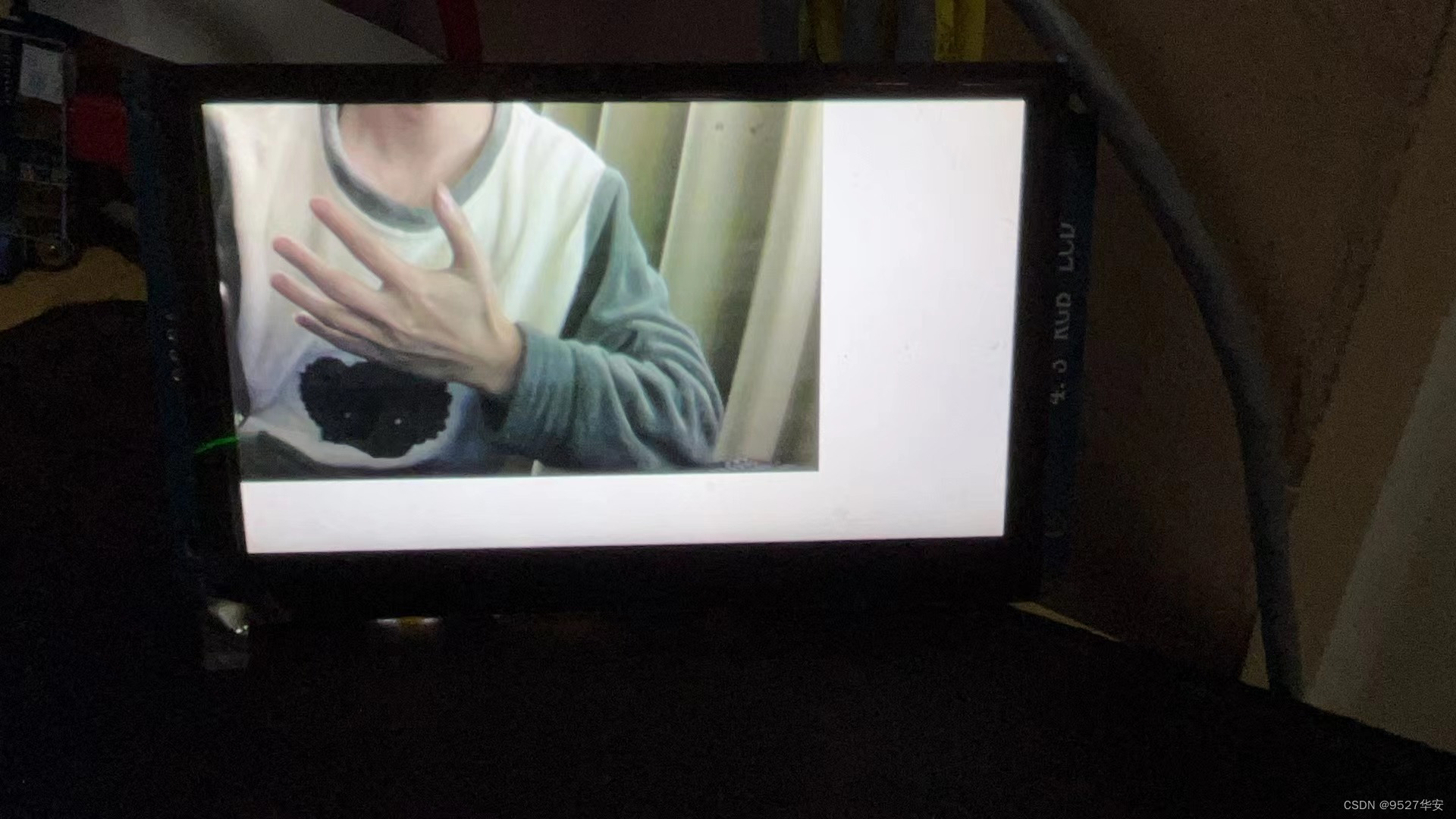

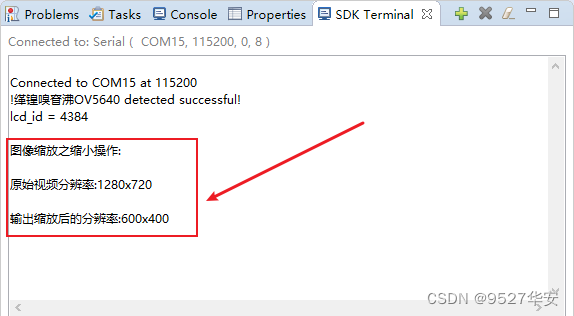

工程2:ov5640输入分辨率1280x720,LCD输出分辨率600x400;

LCD显示输出和串口打印分别如下:

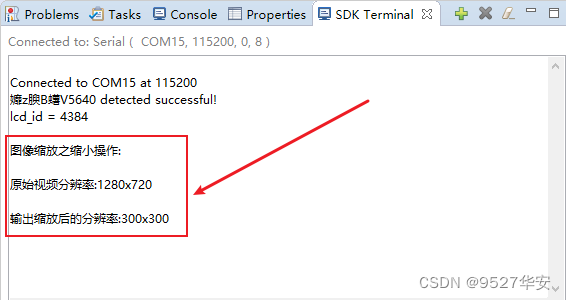

工程2:ov5640输入分辨率1280x720,LCD输出分辨率300x300;

LCD显示输出和串口打印分别如下:

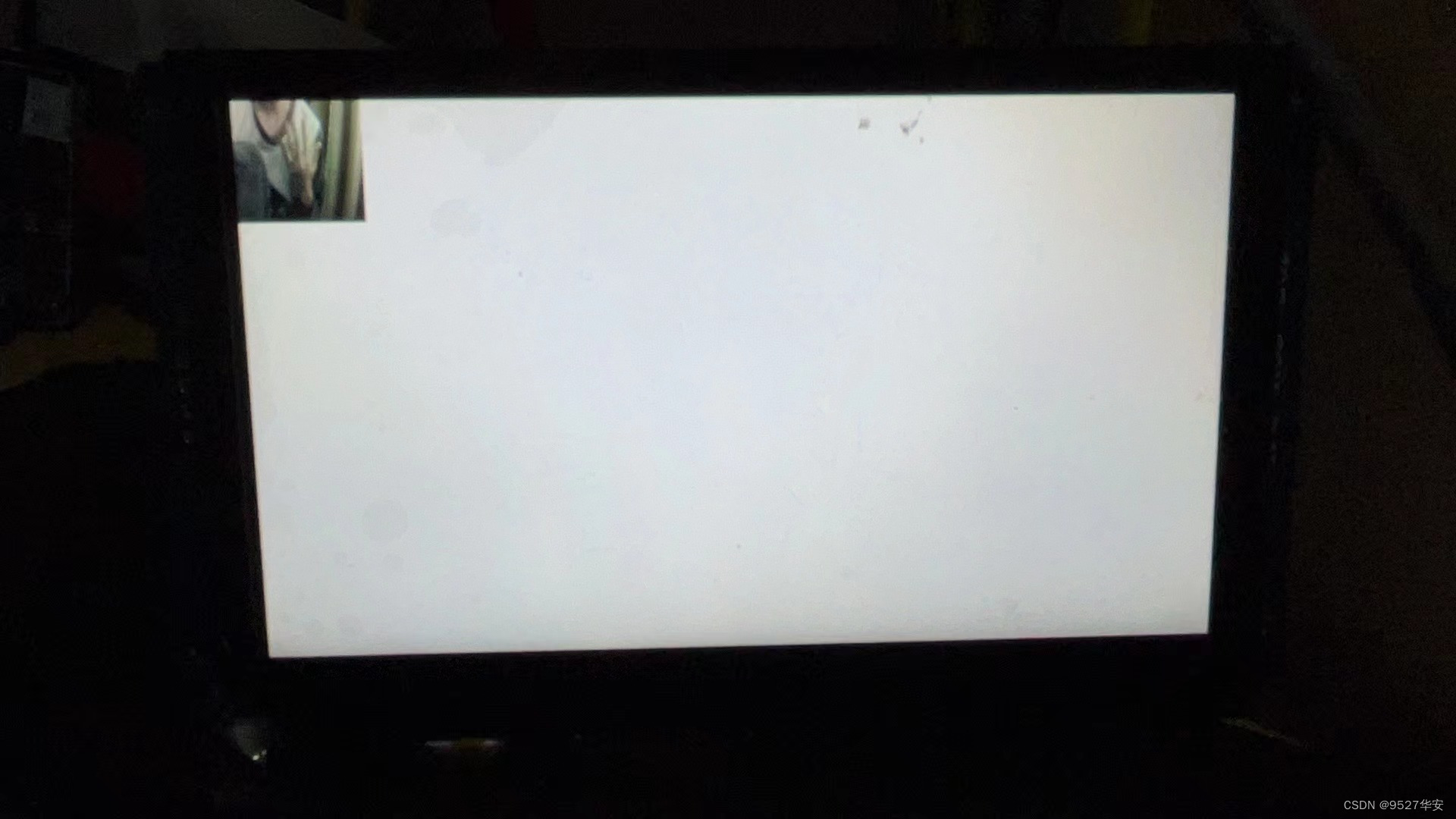

工程2:ov5640输入分辨率1280x720,LCD输出分辨率100x100;

LCD显示输出和串口打印分别如下:

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

Xilinx Zynq-7000系列FPGA任意尺寸图像缩放,提供两套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐FPGA图像处理方案FPGA图像缩放方案 3、设计思路详解HLS 图像缩放介绍 4、工程代码1:图像缩放 HDMI 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设计 5、工程代码2:图像缩放 LCD 输出PL 端 FPGA 逻辑设计PS 端 SDK 软件设…...

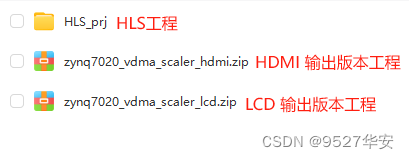

基于 Glibc 版本升级的 DolphinDB 数据查询性能优化实践

在高并发查询、查询需要涉及很多个分区的情况下,低版本的 glibc(低于2.23)会严重影响查询性能。需要升级 glibc 解决该问题优化性能。我们撰写了本文,通过 patchelf 工具修改可执行文件和动态库的 rpath,达到无需升级系…...

【顺序表的应用-通讯录的实现】

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 目录 前言 一、顺序表的应用 1. 基于动态顺序表实现通讯录 1、功能要求 2、代码实现 二、通讯录的代码实现 1.通讯录的底层结构(顺序表) (1)思路展示 (2)底层代码实现(顺序表…...

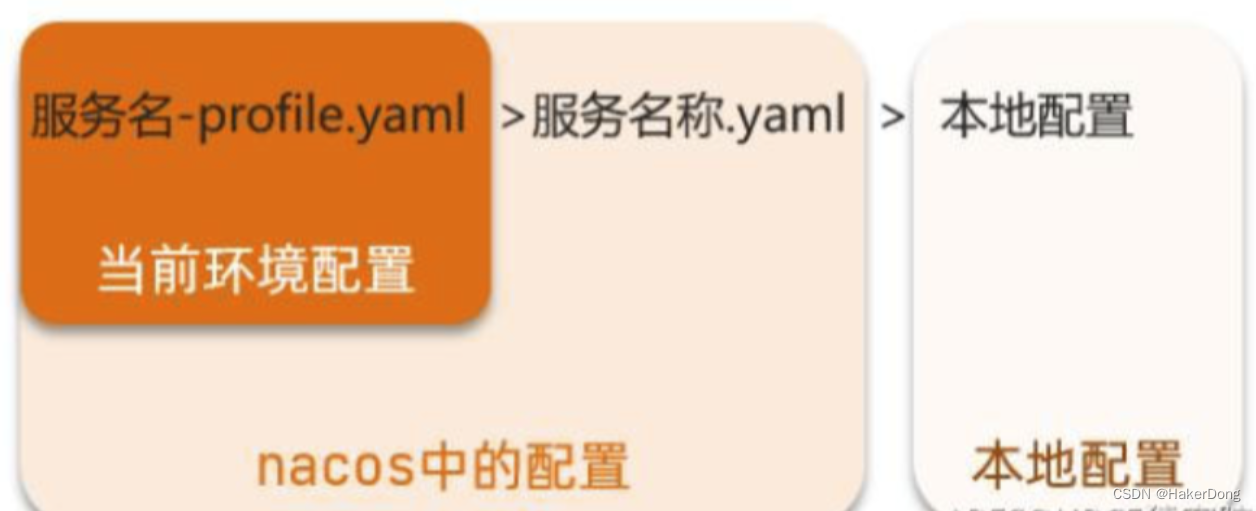

[Spring Cloud] Nacos 实战 + Aws云服务器

文章目录 前言一、拥有一台Aws Linux服务器1.1、选择Ubuntu版本Linux系统1.2、创建新密钥对1.3、网络设置1.4、配置成功,启动实例1.5、回到实例区域1.6、进入具体的实例1.7、设置安全组 二、在Mac上连接Aws云服务,并安装配置JDK112.1、解决离奇的错误2.2…...

SpringCloud微服务注册中心:Nacos介绍,微服务注册,Ribbon通信,Ribbon负载均衡,Nacos配置管理详细介绍

微服务注册中心 注册中心可以说是微服务架构中的”通讯录“,它记录了服务和服务地址的映射关系。在分布式架构中,服务会注册到这里,当服务需要调用其它服务时,就这里找到服务的地址,进行调用。 微服务注册中心 服务注…...

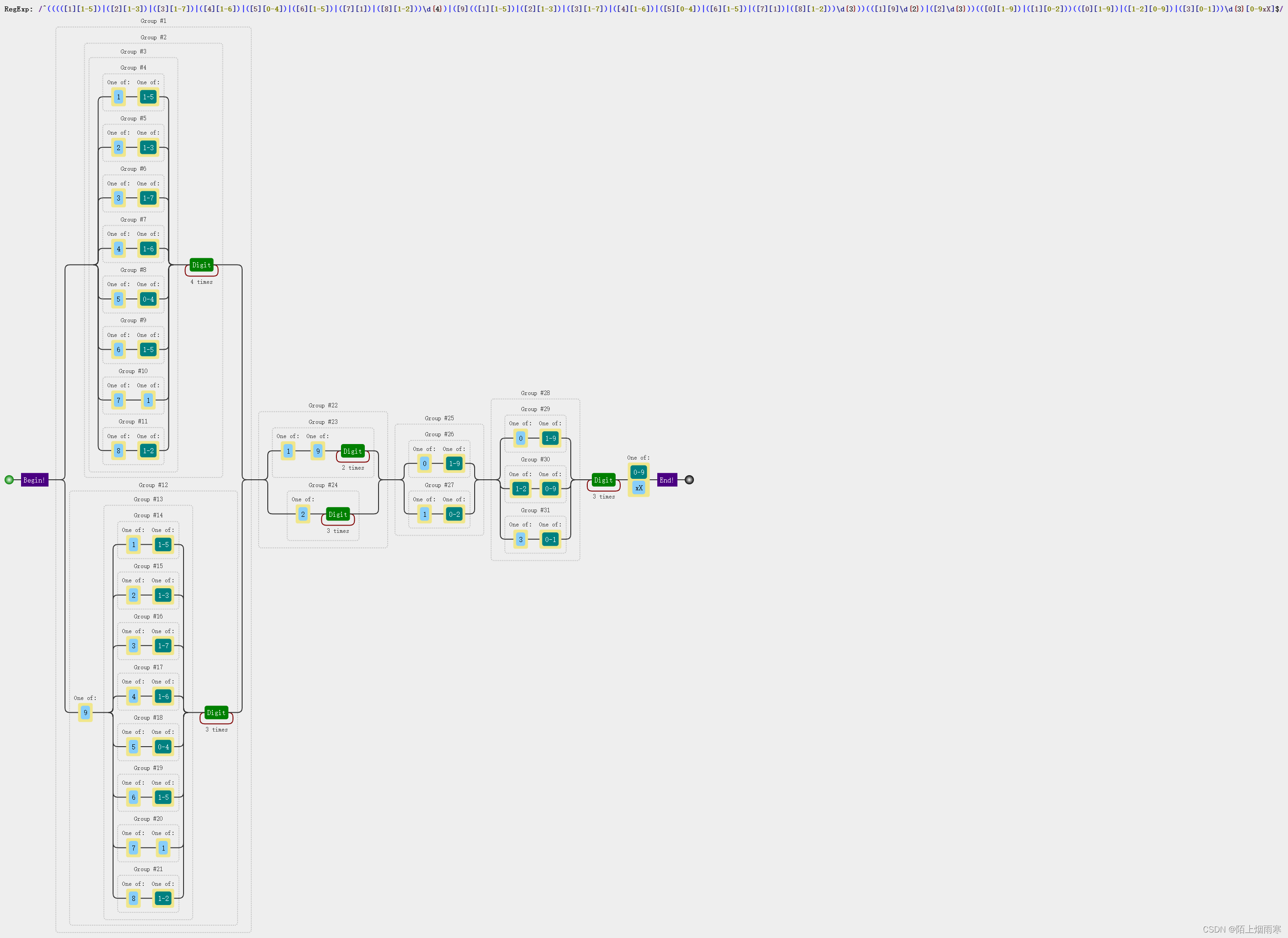

身份证号码校验

根据《新版外国人永久居留身份证适配性改造要点》,公司需要把代码中对身份证的校验进行优化 就文档内容可以看到需要优化的要点是: 新版永居证号码以 9 开头 受理地区代码出生日期顺序码校验码;(共18位) egÿ…...

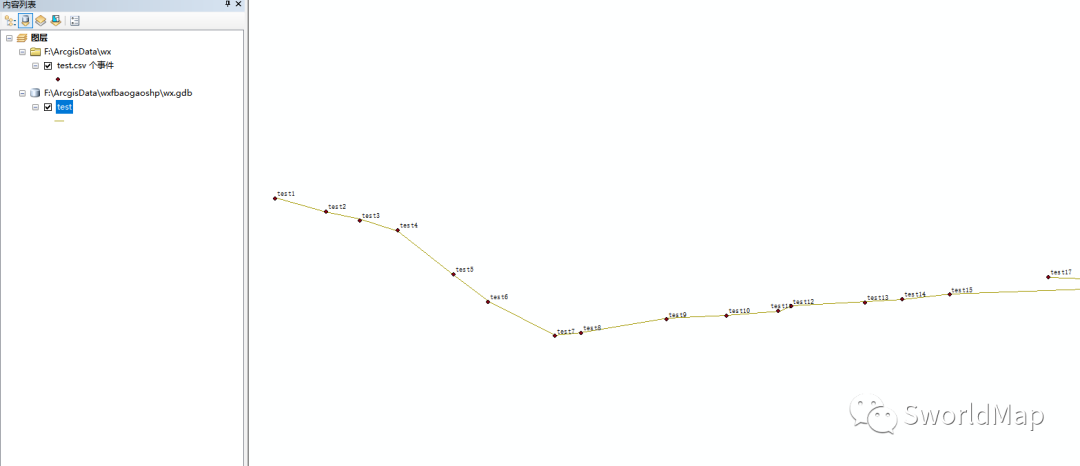

ArcGIS如何处理并加载Excel中坐标数据?

做GIS行业的各位肯定免不了跟数据打交道,其中数据的处理说复杂也复杂,因为我们要花时间去做数据的转换及调整工作,那说简单也简单,因为我们有很多的工具可以使用,那么今天我就给大家带来处理Excel中的GIS数据中的其中一…...

- 类型支持 (类型修改,从给定类型移除 const 或/与 volatile 限定符,std::remove_cv))

C++标准模板(STL)- 类型支持 (类型修改,从给定类型移除 const 或/与 volatile 限定符,std::remove_cv)

类型特性 类型特性定义一个编译时基于模板的结构,以查询或修改类型的属性。 试图特化定义于 <type_traits> 头文件的模板导致未定义行为,除了 std::common_type 可依照其所描述特化。 定义于<type_traits>头文件的模板可以用不完整类型实例…...

nodejs搭建本地服务

前端开发时想自己有个本地服务如下操作直接上干货 1.在桌面上直接在powerShell 输入命令行 npm install -g express-generator 然后 npm install -g express 然后新建一个例如server的文件夹 在powerShell执行 express myStudy -e 端口号默认是3000 直接在地址栏输入 http://…...

如何看待Unity新收费模式?

Unity新收费模式的变化主要在于将收费重心从功能分级收费转变为资源使用量收费,这个改变已经引起了一定的争议和反响。以下是我个人的看法: 优点: 更公平的收费方式:新的收费模式将更加公平,用户只需按照实际使用的数…...

Excel数据可视化—波士顿矩阵图【四象限图】

EXCEL系列文章目录 Excel系列文章是本人亲身经历职场之后萌发的想法,为什么Excel覆盖如此之广,几乎每个公司、学校、家庭都在使用,但是它深藏的宝藏功能却很少被人使用,PQ、BI这些功能同样适用于数据分析;并且在一些需…...

【Java】智慧工地管理系统源代码,支持二次开发,SaaS模式

智慧工地系统围绕工程现场人、机、料、法、环及施工过程中质量、安全、进度、成本等各项数据满足工地多角色、多视角的有效监管,实现工程建设管理的降本增效。 一、行业现状 1、施工现场管理难:安全事故频发,人工巡检难度大,质量进度协同难等…...

Lstm+transformer的刀具磨损预测

视频讲解: 基于Lstm+transformer的刀具磨损预测实战_哔哩哔哩_bilibili 结果展示: 数据展示: 主要代码: # pip install openpyxl -i https://pypi.tuna.tsinghua.edu.cn/simple/ # pip install optuna -i https://pypi.tuna.tsinghua.edu.cn/simple/ import numpy as np…...

本机idea连接虚拟机中的Hbase

相关环境: 虚拟机:Centos7 hadoop版本:3.1.3 hbase版本:2.4.11 zookeeper版本:3.5.7 Java IDE:IDEA JDK:8 步骤 步骤一:在idea创建一个maven项目 步骤二:在虚拟机里找到core-site.x…...

.NET中的Object类学习3_MemberwiseClone方法

文章目录 一、前言二、Object.MemberwiseClone方法1 定义2 示例3 备注 三、总结 一、前言 按照MSDN文档的章节顺序来,本文应该是第五节。 但是学了上一节 Finalize之后,发现其内容对实际开发帮助不大。 所以这次跳过了前面的GetHashCode、GetType章节&a…...

)

鼎捷前端开发校招岗技术面面经(已过)

前言 鼎捷一共两面,一面针对技术,这篇博客记录下我认为有价值的问题。 有价值的提问 js类的继承的方式 es5,涉及到原型、原型链的继承; es6,类与对象,extends,super; 还问到Vue…...

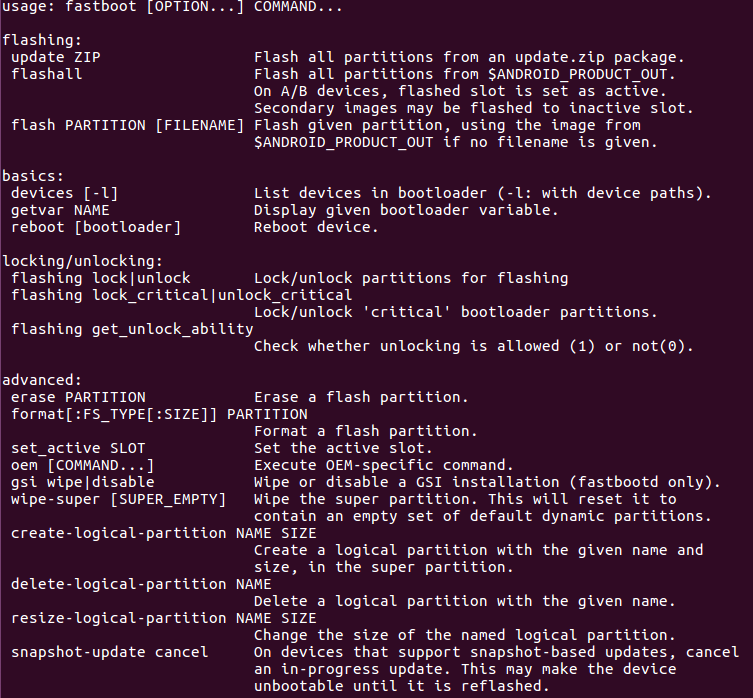

Rockchip平台rk3588源码下载编译(基于Android13)

Rockchip平台rk3588源码下载编译(基于Android13) 源码下载 下载地址 repo init --repo-url https://gerrit.rock-chips.com:8443/repo-release/tools/repo -u https://gerrit.rock-chips.com:8443/Android_T/manifests.git -m Android13.xml服务器镜像下载 repo init --rep…...

.)

RuntimeError: PyPI no longer supports ‘pip search‘ (or XML-RPC search).

RuntimeError: PyPI no longer supports ‘pip search’ (or XML-RPC search). 1. ERROR: XMLRPC request failed Deprecated Methods https://warehouse.pypa.io/api-reference/xml-rpc.html#deprecated-methods PyPI XMLRPC Search Disabled https://status.python.org/inc…...

21款奔驰GLS450升级23P驾驶辅助 提升安全出行

辅助驾驶越来越多的被大家所青睐!为了提升驾驶安全性和舒适便捷性奔驰改装原厂半自动驾驶23P辅助系统 23P智能辅助驾驶系统还是很有必要的,因为在跑高速的时候可以使用23P智能驾驶的自动保持车速,保持车距,车道自动居中行驶以及自…...

iOS越狱检测总结

文章目录 前言检测越狱文件私有目录检测检测越狱软件检测系统目录是否变为链接动态库检测环境变量检测系统调用检测指令集调用检测其他方式检测 前言 在之前的文章中,已经带大家一起制作了一个屏蔽越狱检测的Tweak。本文就和大家一起学习整理一下iOS系统中有哪些越…...

CC26XX低功耗实战:手把手教你配置TI-RTOS自动睡眠策略,让设备续航翻倍

CC26XX低功耗实战:TI-RTOS自动睡眠策略配置与深度优化指南 在物联网设备开发中,电池续航能力往往是决定产品成败的关键因素。德州仪器(TI)的CC26XX系列无线微控制器凭借其出色的低功耗特性,成为众多智能家居、可穿戴设备和工业传感器节点的首…...

不只是骷髅海:从《亡灵》设定看游戏设计中“死亡”主题的5种高级玩法与平衡性设计

超越骷髅海:游戏设计中死亡主题的五大高阶玩法与平衡艺术 当《魔兽争霸3》中死亡骑士高举霜之哀伤召唤食尸鬼大军时,玩家第一次体验到亡灵军团"越打越多"的独特快感。但二十年后的今天,单纯的数量压制早已无法满足硬核玩家对策略深…...

怎么部署OpenClaw?2026年云端9分钟零门槛保姆级指南及百炼Coding Plan流程

怎么部署OpenClaw?2026年云端9分钟零门槛保姆级指南及百炼Coding Plan流程。OpenClaw作为阿里云生态下新一代的开源AI自动化代理平台,曾用名Moltbot/Clawdbot,凭借“自然语言交互自动化任务执行大模型智能决策”的核心能力,正在重…...

TradingAgents 深度讲解:让 AI 智能体团队替你“开交易公司“——从原理到手把手部署

一个在 GitHub 收获 6.9 万星标、由 Tauric Research 团队开源的多智能体金融交易框架。它不是一个简单的"AI 选股工具",而是用 LLM 模拟了一整个真实交易公司的决策流程。 项目地址:https://github.com/TauricResearch/TradingAgents 论文地址…...

)

保姆级避坑指南:在VMware Workstation 17上搞定macOS Ventura虚拟机(附Intel/AMD配置差异)

VMware Workstation 17上完美运行macOS Ventura虚拟机的终极指南 在Windows环境下运行macOS虚拟机一直是开发者和技术爱好者的热门需求,尤其是对于需要跨平台测试或体验苹果生态的用户。然而,这个过程充满了各种技术陷阱和兼容性问题。本文将深入探讨在V…...

STM32新手避坑指南:PWM驱动舵机时,为什么你的角度总是不准?

STM32 PWM驱动舵机精度问题全解析:从原理到调试实战 第一次用STM32的PWM功能控制舵机时,看着那个本该精准转动到90度的舵臂在45度和135度之间来回抽搐,我盯着示波器上飘忽不定的波形,突然理解了为什么有些工程师会对着开发板自言自…...

的完整流程)

别再手写浮点运算了!Vivado 2023.2里用Floating Point IP核实现e^x和ln(x)的完整流程

高效实现e^x与ln(x):Vivado 2023.2中Floating Point IP核的工程实践 在FPGA开发中,数学函数的高效实现一直是性能优化的关键环节。传统RTL手写浮点运算不仅耗时费力,还容易引入精度问题和时序瓶颈。Vivado提供的Floating Point IP核为这一难题…...

AI 系统主链路分层设计:从 RAG 检索到 Agent 执行的模块职责划分

问题现象:长链路 AI 系统频繁出现静默失败与状态不一致 在 AI 应用上线后,用户反馈智能问答结果偶尔返回空值或重复内容,且后台日志显示任务已提交但无执行记录。进一步排查发现,RAG 检索模块与 Agent 执行模块之间存在状态流转断…...

独立开发者如何利用 Taotoken 按需调用不同模型优化个人项目

独立开发者如何利用 Taotoken 按需调用不同模型优化个人项目 对于独立开发者或自由职业者而言,技术项目的成本控制和灵活性至关重要。在预算有限且需求多变的日常开发中,大模型 API 的调用费用常常是一笔不小的开销,而不同任务对模型能力的需…...

Windows 10 下 Qt 5.15 组件选择避坑指南:从MSVC到MinGW,32G空间怎么装最合理?

Windows 10下Qt 5.15组件选择避坑指南:从MSVC到MinGW的32G空间优化方案 Qt作为跨平台开发框架,其组件选择直接影响开发效率和磁盘空间占用。面对Qt在线安装器中庞大的组件列表,开发者常陷入两难:既希望功能完备,又担心…...