FIFO IP Core

FIFO IP Core

- 先进先出的缓存器

- 常常被用于数据的缓存,或者高速异步数据交互(跨时钟信号传递)

- 和RAM和ROM的区别是没有地址线,无法指定地址

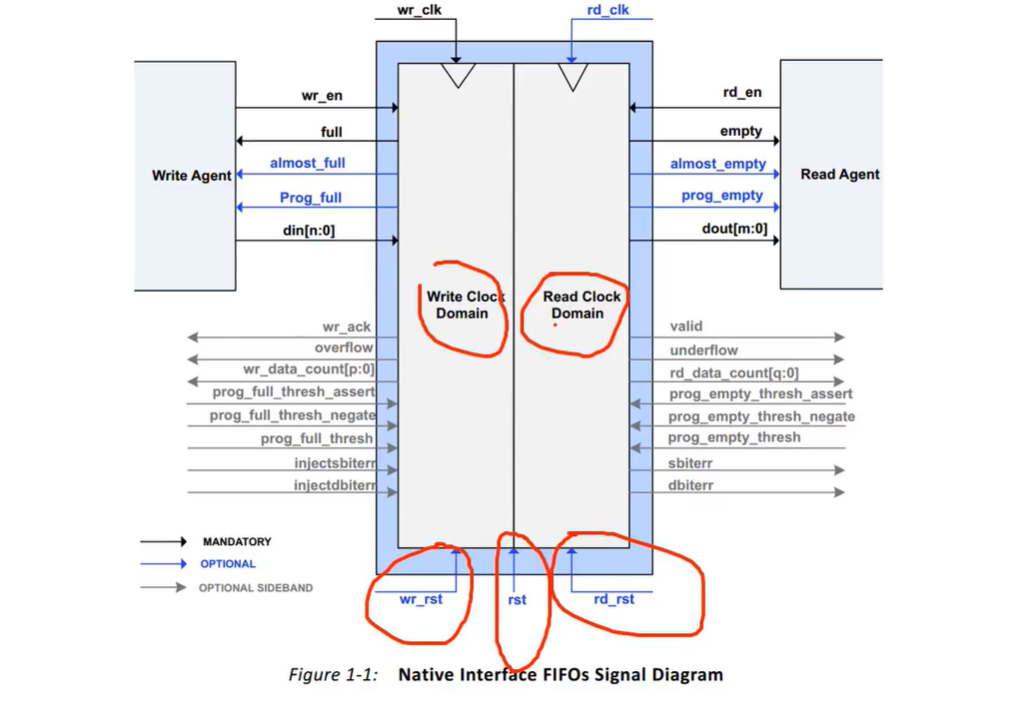

- 写时钟(Write Clock Domain),读时钟

- 写复位(wr_rst),读复位,整体复位

- 写使能(wr_en),读使能

- 写满标志(full),读空标志(empty)

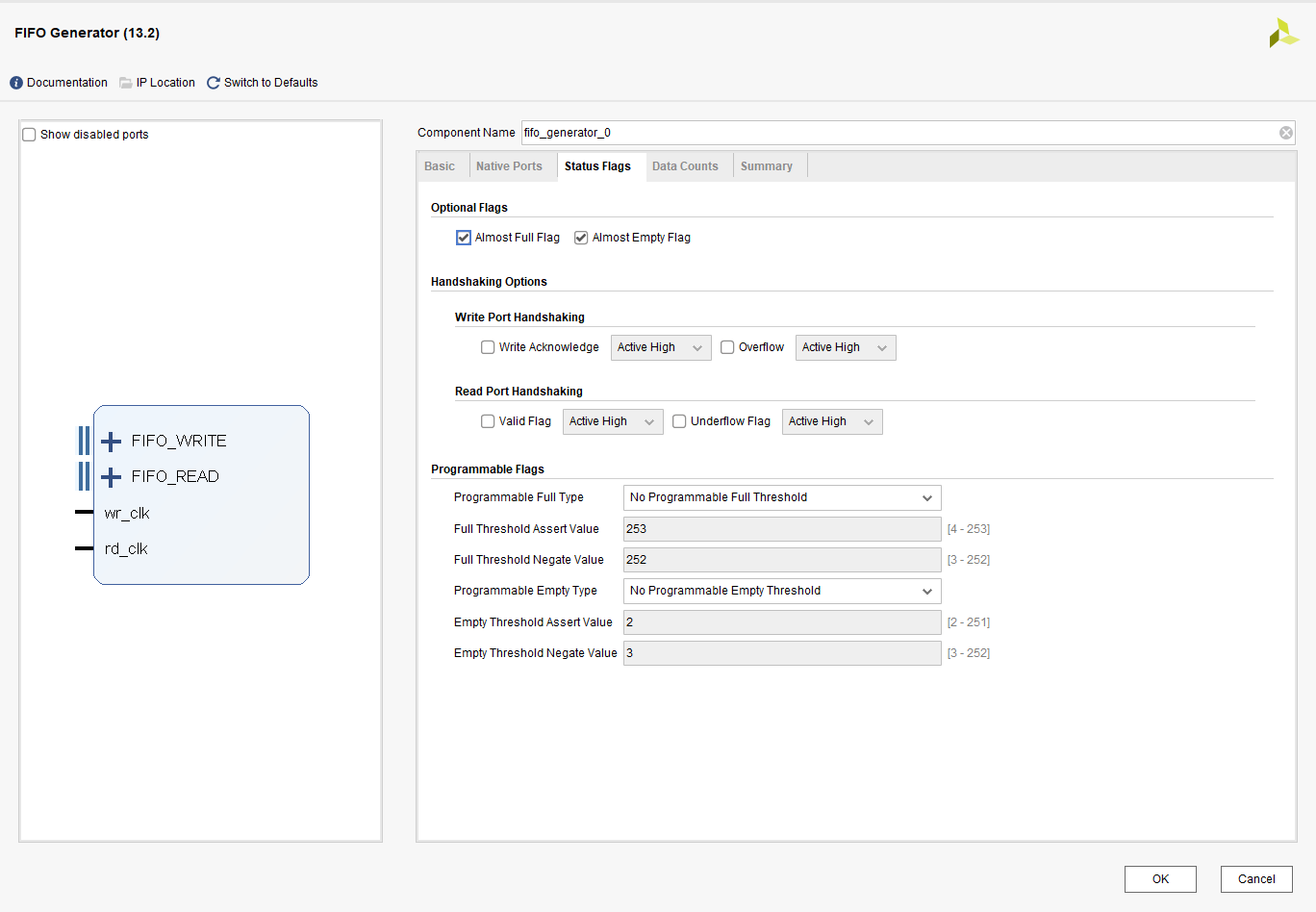

- almost_full:快要满了,almost_empty:快要空了

- Prog_full:可编程写满,prog_empty:可编程读空(根据自己设置的数据个数拉高或拉低)

- wr_ack:写反馈(对写使能的应答) valid:读出的数据是一个稳定有效的值

- overflow:写溢出 underflow:读空(下溢出)

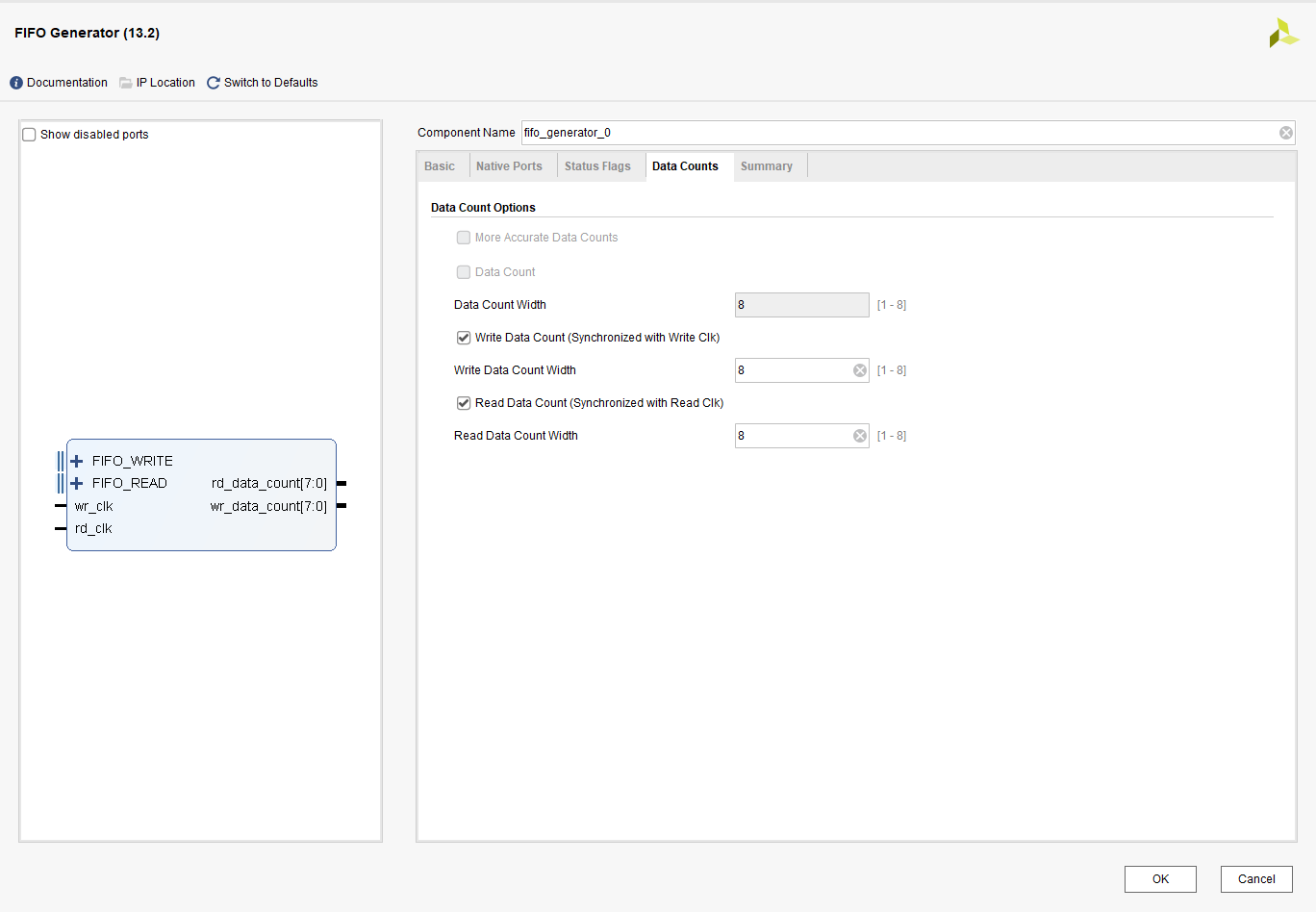

- wr_data_count: Fifo中储存的写数据的数量 rd_data_count:储存的读数据的数量

- prog_full_thresh_assert: 动态修改prog_full的值

- prog_full_thresh_negate:门限值失效

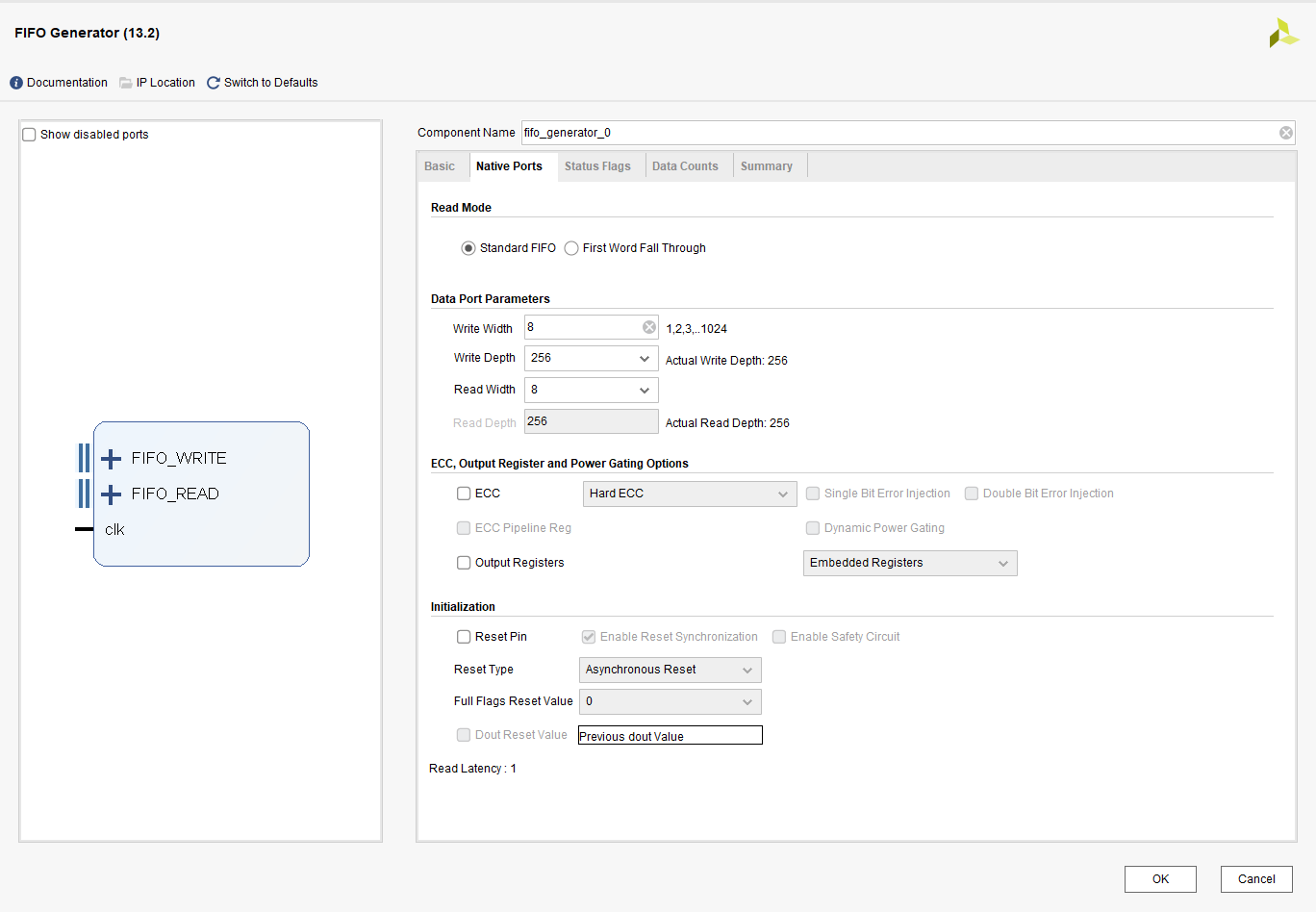

FIFO IP Core的设置

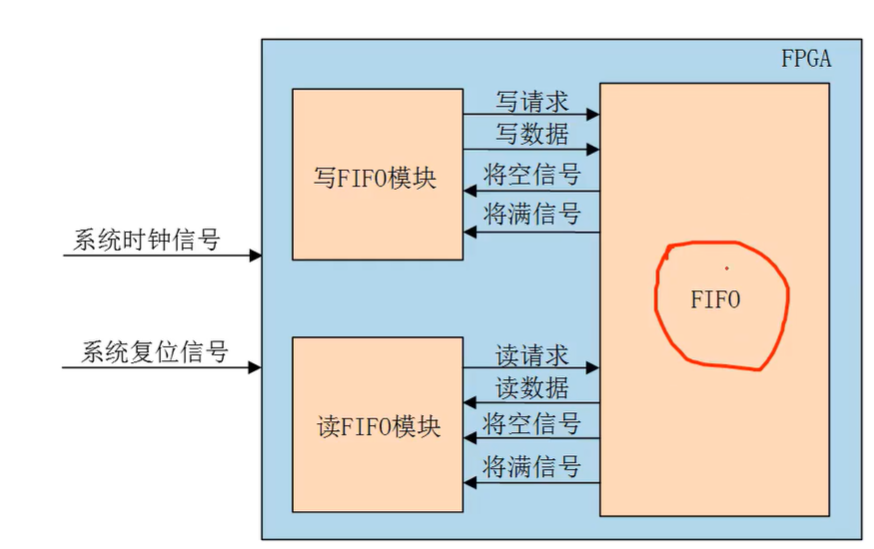

实验结构:

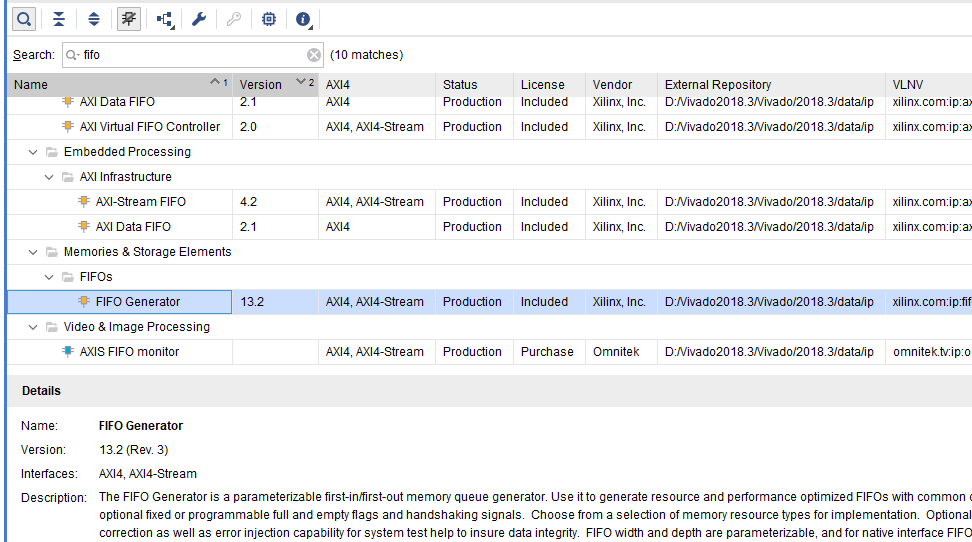

创建工程和设计文件ip_fifo,添加FIFO IP Core

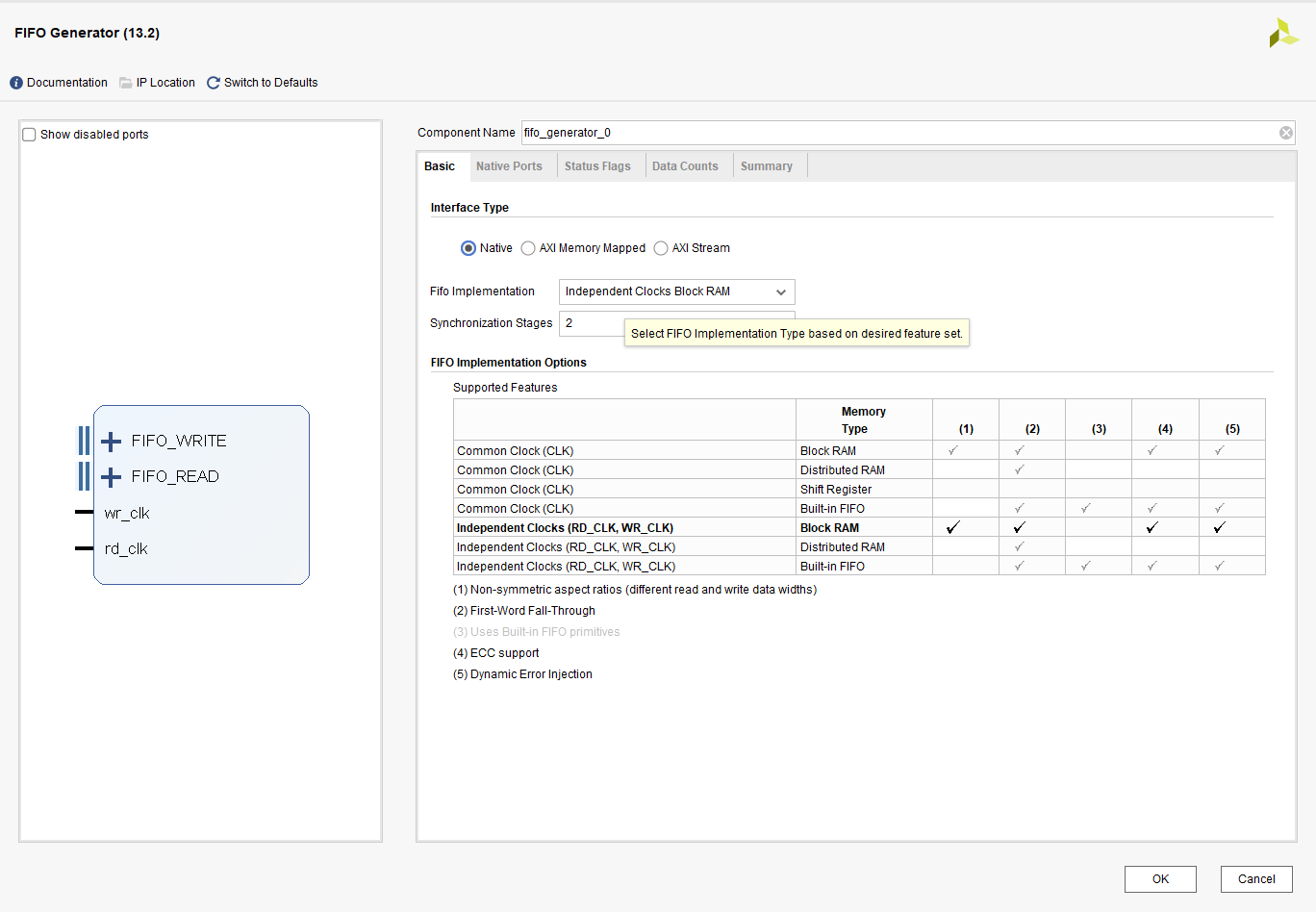

选择异步时钟的BRAM(这样后面的读写数据量才能设置,同步时钟的默认相等)

设置读写宽度和深度,取消复位引脚

勾选Almost Full Flag & Almost Empty Flag

勾选读写数据量的计数

如何抓取上升沿/下降沿?

信号en: _________|————

reg d0 = en 当前时刻的值

reg d1 = d0 前一时刻的值

当d1 = 0, d0 = 1时 说明是上升沿 == ~d1&d0 为真

当d1 = 1, d0 = 0时 说明是下降沿 == ~d0&d1 为真

写模块 fifo_wr

输入信号:时钟,复位,将空,将满

输出信号:写使能,写数据

module fifo_wr(input clk,input rst,input almost_empty,input almost_full,output reg fifo_wr_en,output reg[7:0] fifo_wr_data);endmodule

抓取almost_empty信号上升沿

reg almost_empty_cur;

reg almost_empty_pre;

wire syn;

// assign 过程赋值,右边的值发送变化会重新赋值

assign syn = ~almost_empty_pre & almost_empty_cur;

always @(posedge clk or posedge rst) beginif(rst) beginalmost_empty_cur <= 1'b0;almost_empty_pre <= 1'b0;endelse beginalmost_empty_cur <= almost_empty;almost_empty_pre <= almost_empty_cur;end

end

不能对数据立刻赋值,fpga内部不一样准备好了,需要延迟等待一段时间,这样的需求可以用状态机完成

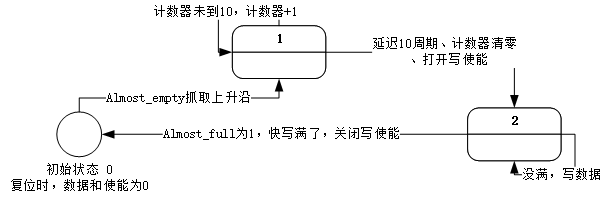

状态机

6.3 Verilog 状态机 | 菜鸟教程 (runoob.com)

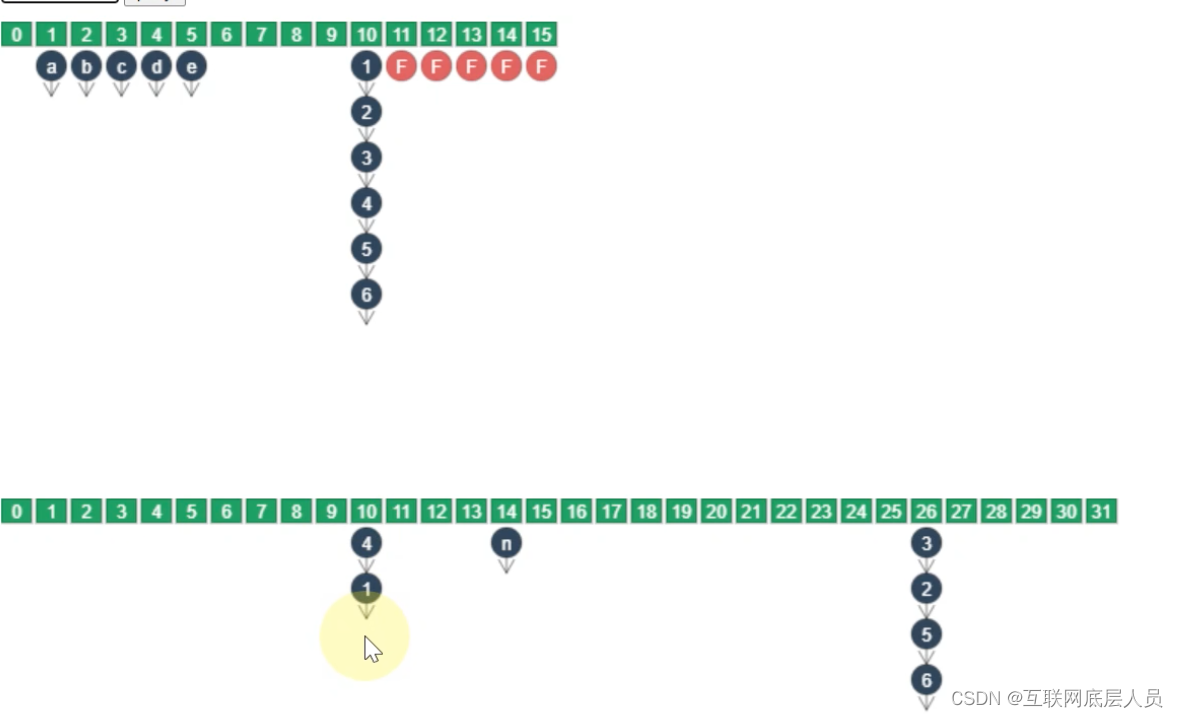

这里有三个状态,延迟等待10个周期

所以定义:

reg [1:0] state;

reg [3:0] delay_cnt;

状态转换:

// 状态机

reg [1:0] state;

// 延迟数

reg [3:0] delay_cnt;

always @(posedge clk or posedge rst) beginif(rst) beginfifo_wr_en <= 1'b0;fifo_wr_data <= 8'd0;state <= 2'b0;delay_cnt <= 4'b0;endelse begincase(state)2'd0:beginif(syn) state <= 2'b1;else state <= 2'b0;end2'd1: beginif(delay_cnt == 4'd10) beginfifo_wr_en <= 1'b1;delay_cnt <= 4'd0;state <= 2'd2;endelse delay_cnt <= delay_cnt + 1'b1;end2'd2: beginif(almost_full) beginfifo_wr_en <= 1'b0;fifo_wr_data <= 8'd0;state <= 2'b0;endelse beginfifo_wr_data <= fifo_wr_data + 1'd1;endenddefault:state <= 2'b0;endcaseend

end

读模块fifo_rd

将写模块中的写使能变为读使能

写满判断变为读空判断

去掉写数据

module fifo_rd(input clk,input rst,input almost_empty,input almost_full,input [7:0] fifo_rd_data,output reg fifo_rd_en );reg almost_full_cur;reg almost_full_pre;wire syn;// assign 过程赋值,右边的值发送变化会重新赋值assign syn = ~almost_full_pre & almost_full_cur;always @(posedge clk or posedge rst) beginif(rst) beginalmost_full_cur <= 1'b0;almost_full_pre <= 1'b0;endelse beginalmost_full_cur <= almost_full;almost_full_pre <= almost_full_cur;endend// 状态机reg [1:0] state; // 延迟数reg [3:0] delay_cnt;always @(posedge clk or posedge rst) beginif(rst) beginfifo_rd_en <= 1'b0;state <= 2'b0;delay_cnt <= 4'b0;endelse begincase(state)2'd0:beginif(syn) state <= 2'b1;else state <= 2'b0;end2'd1: beginif(delay_cnt == 4'd10) begindelay_cnt <= 4'd0;state <= 2'd2;endelse delay_cnt <= delay_cnt + 1'b1;end2'd2: beginif(almost_empty) beginfifo_rd_en <= 1'b0;state <= 2'b0;endelse fifo_rd_en <= 1'b1;enddefault:state <= 2'b0;endcaseendend

endmodule

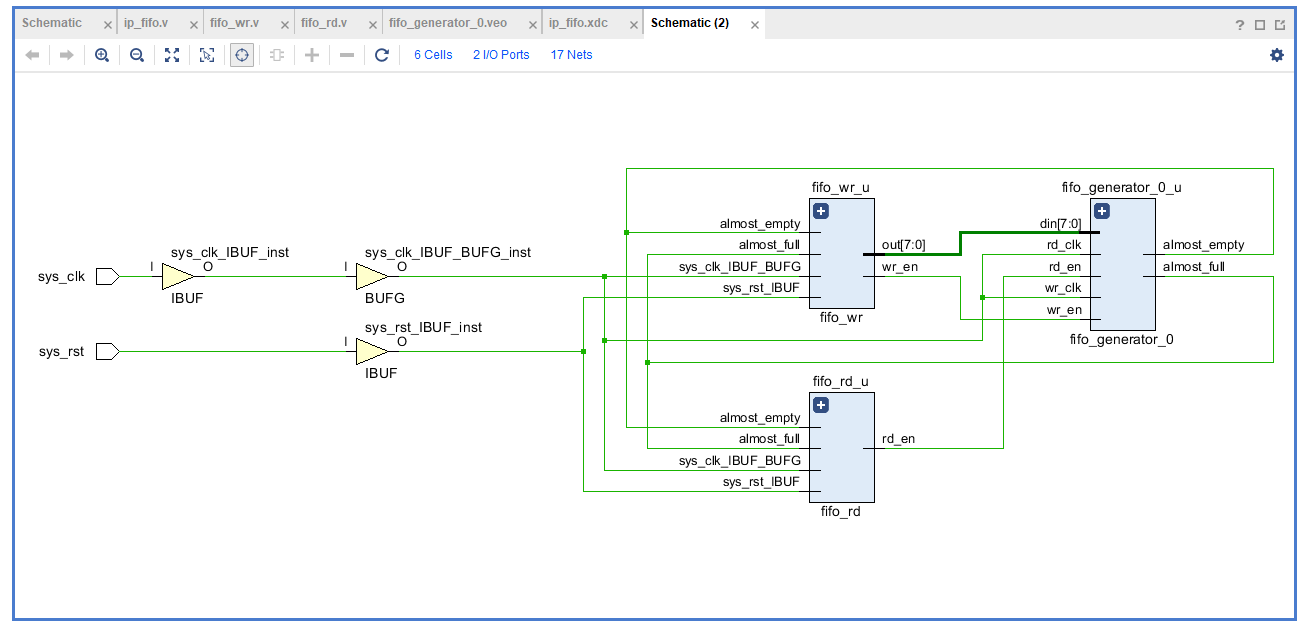

例化顶层模块 fifo_ip

module ip_fifo(input sys_clk,input sys_rst);wire almost_empty;wire almost_full;wire fifo_wr_en; wire[7:0] fifo_wr_data;fifo_wr fifo_wr_u(.clk (sys_clk), .rst (sys_rst),.almost_empty (almost_empty),.almost_full (almost_full),.fifo_wr_en (fifo_wr_en), .fifo_wr_data (fifo_wr_data));wire fifo_rd_en;fifo_rd fifo_rd_u(.clk (sys_clk), .rst (sys_rst),.almost_empty (almost_empty),.almost_full (almost_full),.fifo_rd_en (fifo_rd_en));wire [7:0] dout;wire full;wire empty;wire [7:0] rd_data_count;wire [7:0] wr_data_count;fifo_generator_0 fifo_generator_0_u(.wr_clk(sys_clk), // input wire wr_clk.rd_clk(sys_clk), // input wire rd_clk.din(fifo_wr_data), // input wire [7 : 0] din.wr_en(fifo_wr_en), // input wire wr_en.rd_en(fifo_rd_en), // input wire rd_en.dout(dout), // output wire [7 : 0] dout.full(full), // output wire full.almost_full(almost_full), // output wire almost_full.empty(empty), // output wire empty.almost_empty(almost_empty), // output wire almost_empty.rd_data_count(rd_data_count), // output wire [7 : 0] rd_data_count.wr_data_count(wr_data_count) // output wire [7 : 0] wr_data_count);

endmodule

约束

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { sys_clk }]; #IO_L11P_T1_SRCC_35 Sch=sysclkset_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { sys_rst}];

综合

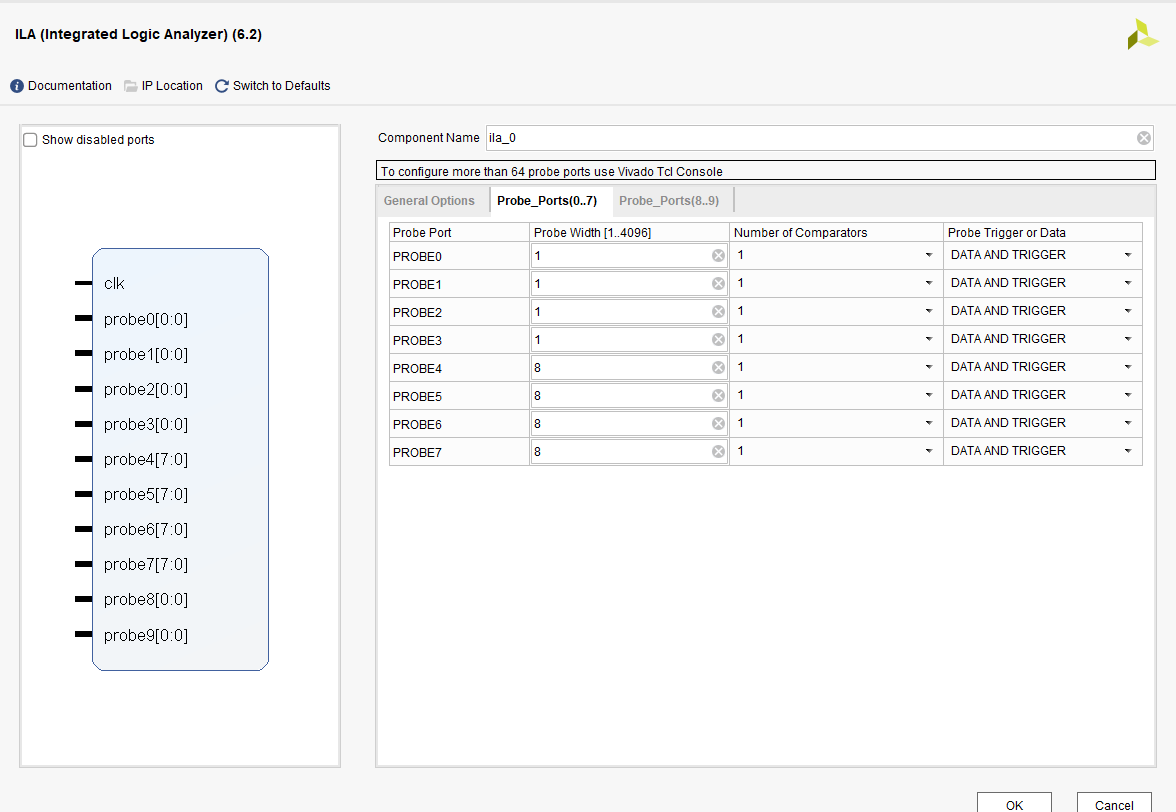

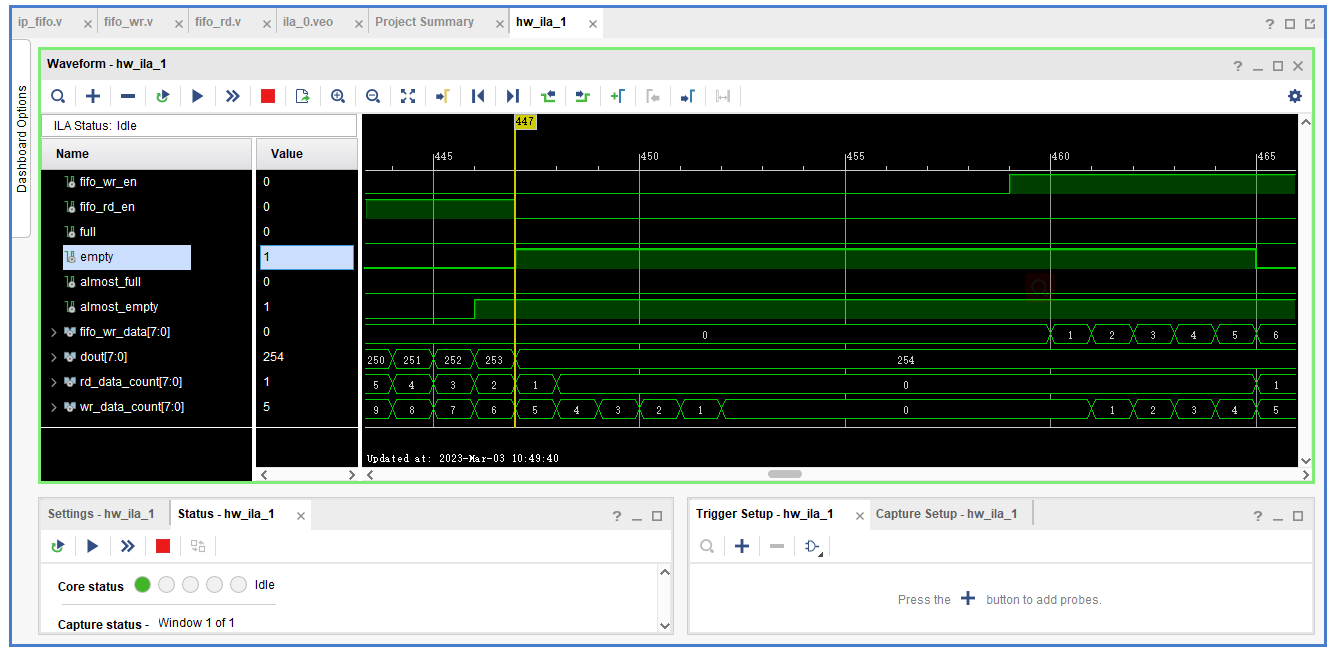

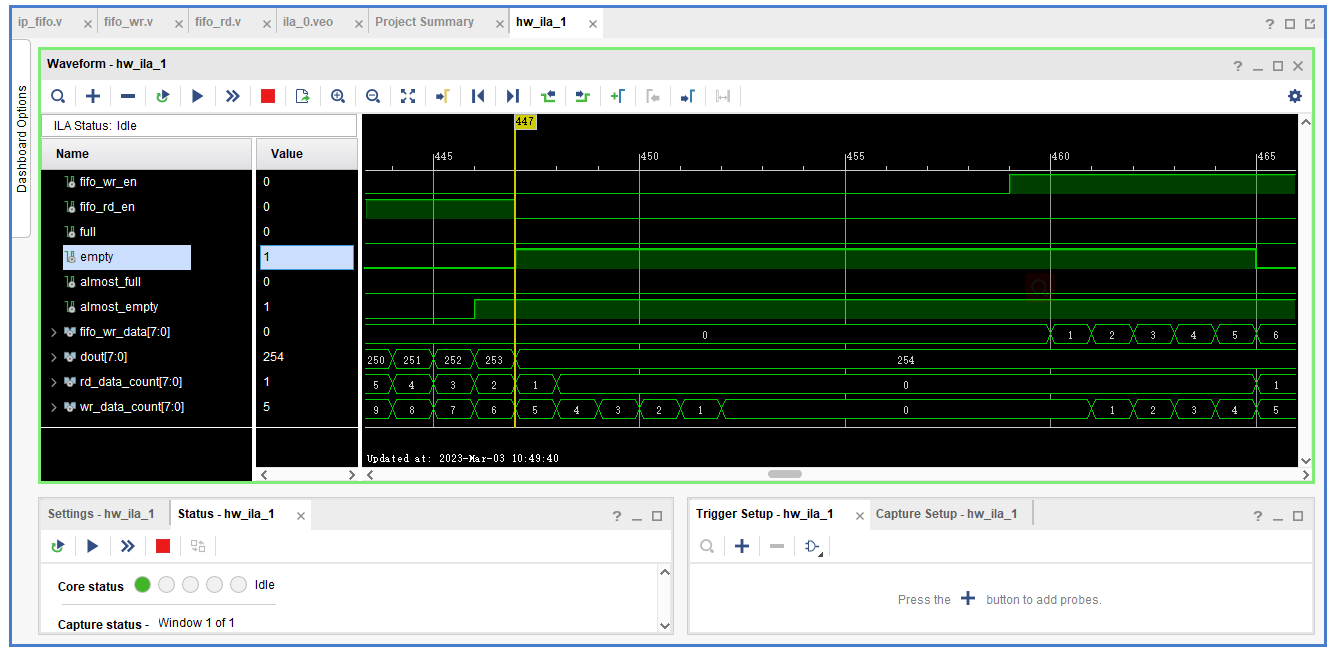

ILA

10个探针,设置位宽:

例化ILA添加到顶层模块ip_fifo

ila_0 your_instance_name (.clk(sys_clk), // input wire clk.probe0(fifo_wr_en), // input wire [0:0] probe0 .probe1(fifo_rd_en), // input wire [0:0] probe1 .probe2(full), // input wire [0:0] probe2 .probe3(almost_full), // input wire [0:0] probe3 .probe4(fifo_wr_data), // input wire [7:0] probe4 .probe5(dout), // input wire [7:0] probe5 .probe6(rd_data_count), // input wire [7:0] probe6 .probe7(wr_data_count), // input wire [7:0] probe7 .probe8(empty), // input wire [0:0] probe8 .probe9(almost_empty) // input wire [0:0] probe9

);

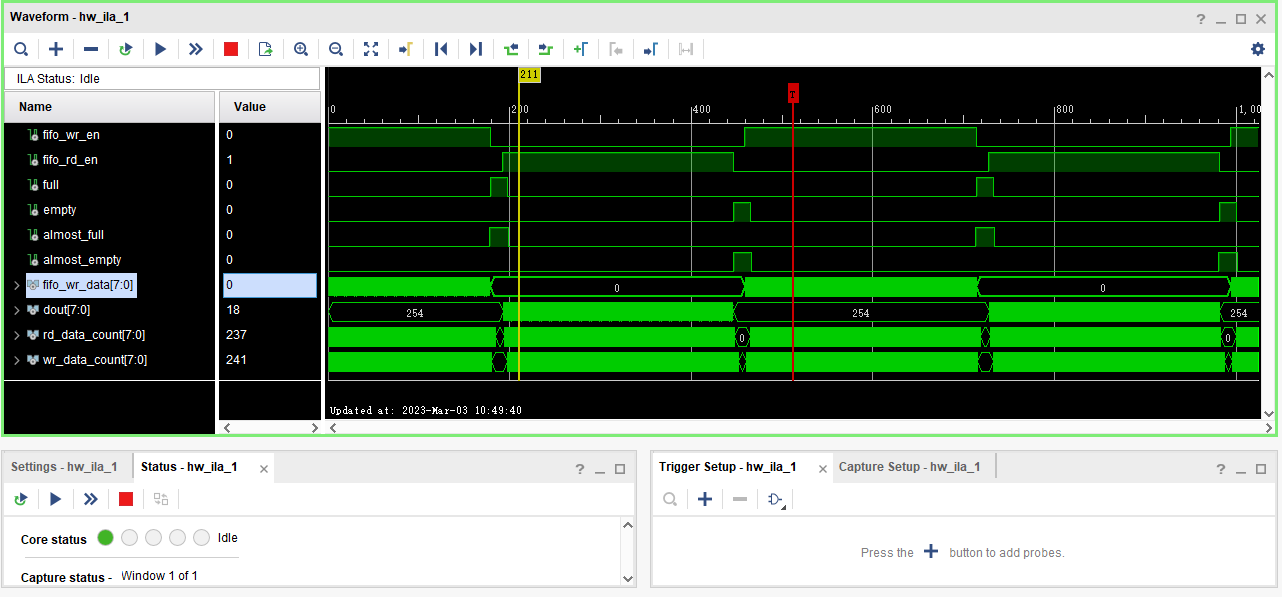

下载验证

生成bitstream,连接开发板,观看ila波形

相关文章:

FIFO IP Core

FIFO IP Core 先进先出的缓存器常常被用于数据的缓存,或者高速异步数据交互(跨时钟信号传递)和RAM和ROM的区别是没有地址线,无法指定地址 写时钟(Write Clock Domain),读时钟写复位(wr_rst),读…...

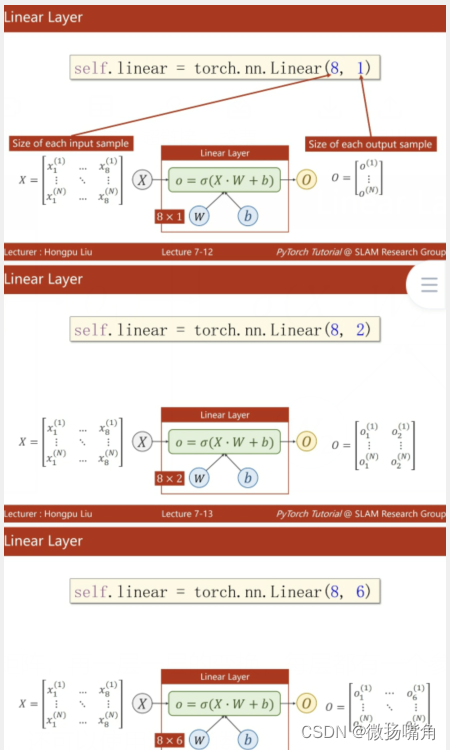

从FPGA说起的深度学习(四)

这是新的系列教程,在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。在本教程中,旨在加深对深度学习和 FPGA 的理解。用 C/C 编写深度学习推理代码高级综合 (HLS) 将 C/C 代码转换为硬…...

pytorch入门7--自动求导和神经网络

深度学习网上自学学了10多天了,看了很多大神的课总是很快被劝退。终于,遇到了一位对小白友好的刘二大人,先附上链接,需要者自取:https://b23.tv/RHlDxbc。 下面是课程笔记。 一、自动求导 举例说明自动求导。 torch中的…...

QT 之wayland 事件处理分析基于qt5wayland5.14.2

1. Qt wayland 初始化 接收鼠标/案件,触摸屏等事件事件 QWaylandNativeInterface : public QPlatformNativeInterface 在QWaylandNativeInterface 继承qpa 接口类QPlatformNativeInterface; 1.1 初始化鼠标: void *QWaylandNativeInterface::nativeR…...

【this 和 super 的区别】

在 Java 中,this 和 super 都是关键字,表示当前对象和父类对象。 this 关键字可以用于以下几种情况: 引用当前对象的成员变量,方法和构造方法,用于区分局部变量和成员变量重名的情况; 调用当前类的另外一…...

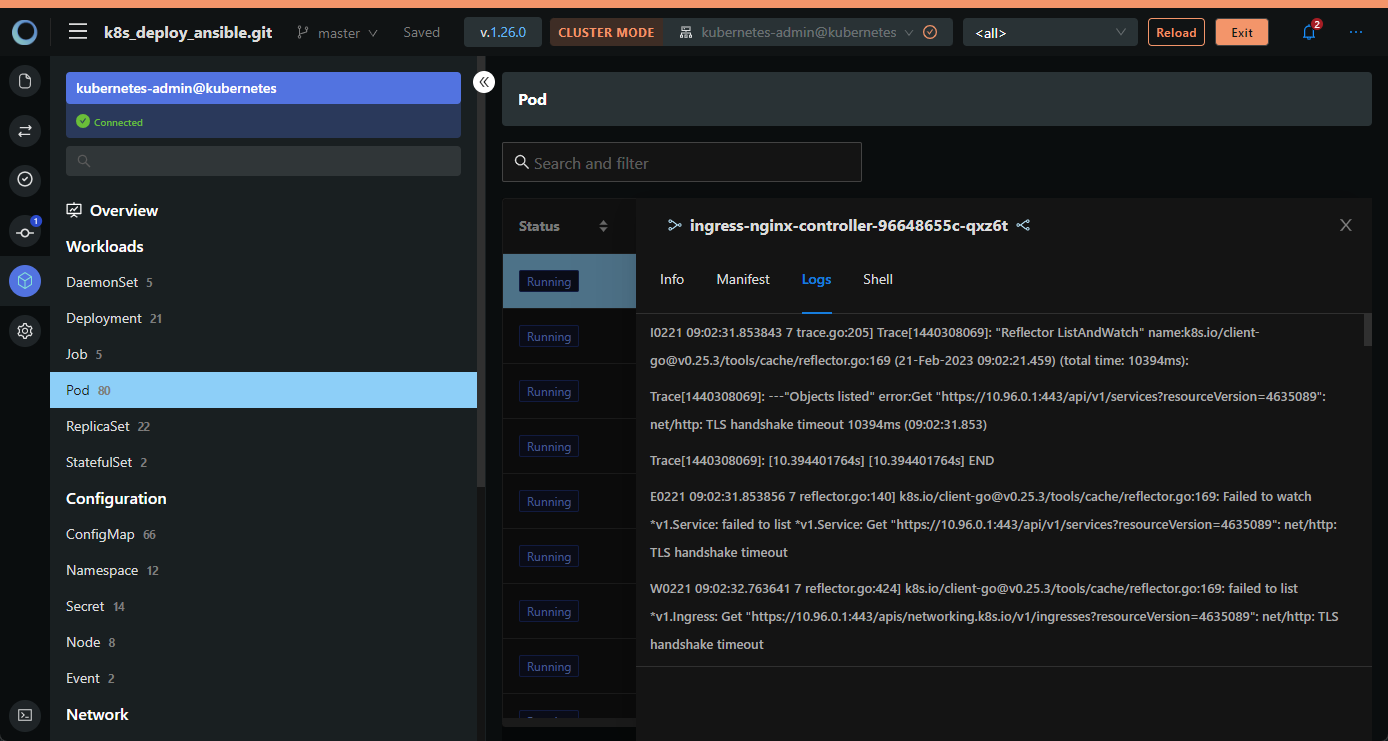

K8s:Monokle Desktop 一个集Yaml资源编写、项目管理、集群管理的 K8s IDE

写在前面 Monokle Desktop 是 kubeshop 推出的一个开源的 K8s IDE相关项目还有 Monokle CLI 和 Monokle Cloud相比其他的工具,Monokle Desktop 功能较全面,涉及 k8s 管理的整个生命周期博文内容:Monokle Desktop 下载安装,项目管理…...

自动化测试实战篇(8),jmeter并发测试登录接口,模拟从100到1000个用户同时登录测试服务器压力

首先进行使用jmeter进行并发测试之前就需要搞清楚线程和进程的区别还需要理解什么是并发、高并发、并行。还需要理解高并发中的以及老生常谈的,TCP三次握手协议和TCP四次握手协议**TCP三次握手协议指:****TCP四次挥手协议:**进入Jmeter&#…...

ATTCK v12版本战术实战研究—持久化(二)

一、前言前几期文章中,我们介绍了ATT&CK中侦察、资源开发、初始访问、执行战术、持久化战术的知识。那么从前文中介绍的相关持久化子技术来开展测试,进行更深一步的分析。本文主要内容是介绍攻击者在运用持久化子技术时,在相关的资产服务…...

python函数式编程

1 callable内建函数判断一个名字是否为一个可调用函数 >>> import math >>> x 1 >>> y math.sqrt >>> callable(x) False >>> callable(y) True 2 记录函数(文档字符串) >>> def square(x): …...

3.linux下安装mysql

1.安装前的环境准备 查看是否安装过mysql 首先检测Linux操作系统中是否安装了MySQL: # rpm -qa | grep -i mysql 卸载安装包 如果有信息出现,则进行删除,命令如下: # rpm -e --nodeps 包名 删除老版本mysql的开发头文件和…...

17、MySQL分库分表,原理实战

MySQL分库分表,原理实战 1.MyCAT分布式架构入门及双主架构1.1 主从架构1.2 MyCAT安装1.3 启动和连接1.4 配置文件介绍2.MyCAT读写分离架构2.1 架构说明2.2 创建用户2.3 schema.xml2.4 连接说明2.5 读写测试2.6 当前是单节点3.MyCAT高可用读写分离架构3.1 架构说明3.3 schema.xm…...

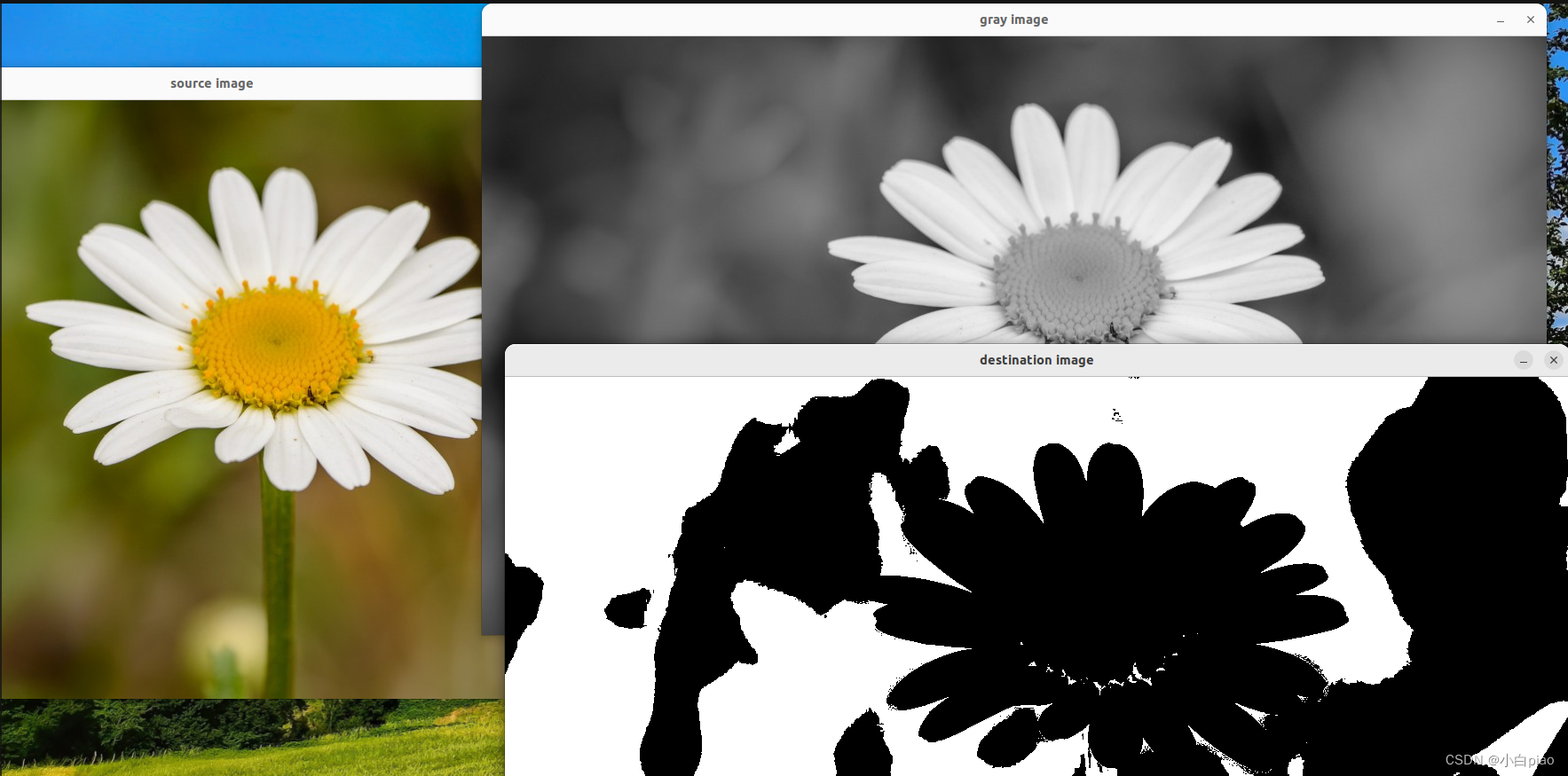

【C++的OpenCV】第九课-OpenCV图像常用操作(六):图像形态学-阈值的概念、功能及操作(threshold()函数))

目录一、阈值(thresh)的概念二、阈值在图形学中的用途三、阈值的作用和操作3.1 在OpenCV中可以进行的阈值操作3.2 操作实例3.2.1 threshold()函数介绍3.2.2 实例3.2.3 结果上节课的内容(作者还是鼓励各位同学按照顺序进行学习哦)&…...

[Java代码审计]—MCMS

环境搭建 MCMS 5.2.4:https://gitee.com/mingSoft/MCMS/tree/5.2.4/利用 idea 打开项目 创建数据库 mcms,导入 doc/mcms-5.2.8.sql 修改 src/main/resources/application-dev.yml 中关于数据库设置参数 启动项目登录后台 http://localhost:8080/ms/l…...

》面试题 01.08. 零矩阵)

《程序员面试金典(第6版)》面试题 01.08. 零矩阵

题目描述 编写代码,移除未排序链表中的重复节点。保留最开始出现的节点。 示例1: 输入:[1, 2, 3, 3, 2, 1] 输出:[1, 2, 3] -示例2: 输入:[1, 1, 1, 1, 2] 输出:[1, 2] 提示: 链表长度在[0, 20000]范…...

初识 Python

文章目录简介用途解释器命令行模式交互模式输入和输出简介 高级编程语言,解释型语言代码在执行时会逐行翻译成 CPU 能理解的机器码代码精简,但运行速度慢基础代码库丰富,还有大量第三方库代码不能加密 用途 网络应用工具软件包装其他语言开…...

常用sql语句分享

SELECT COUNT(DISTINCT money) FROM ac_association_course;#COUNT() 函数返回匹配指定条件的行数SELECT AVG(money) FROM ac_association_course;#AVG 函数返回数值列的平均值。NULL 值不包括在计算中SELECT id FROM ac_association_course order by id desc limit 1;#返回最大…...

极狐GitLab DevSecOps 为企业许可证安全合规保驾护航

本文来自: 小马哥 极狐(GitLab) 技术布道师 开源许可证是开源软件的法律武器,是第三方正确使用开源软件的安全合规依据。 根据 Linux 发布的 SBOM 报告显示,98% 的企业都在使用开源软件(中文版报告详情)。随着开源使用…...

后端程序员的前端基础-前端三剑客之HTML

文章目录1 HTML简介1.1 什么是HTML1.2 HTML能做什么1.3 HTML书写规范2 HTML基本标签2.1 结构标签2.2 排版标签2.3 块标签2.4 基本文字标签2.5 文本格式化标签2.6 标题标签2.7 列表标签(清单标签)2.8 图片标签2.9 链接标签2.10 表格标签3 HTML表单标签3.1 form元素常用属性3.2 i…...

VS2019加载解决方案时不能自动打开之前的文档(回忆消失)

✏️作者:枫霜剑客 📋系列专栏:C实战宝典 🌲上一篇: 错误error c3861 :“_T“:找不到标识符 逐梦编程,让中华屹立世界之巅。 简单的事情重复做,重复的事情用心做,用心的事情坚持做; 文章目录前言一、问题描…...

ConcurrentHashMap-Java八股面试(五)

系列文章目录 第一章 ArrayList-Java八股面试(一) 第二章 HashMap-Java八股面试(二) 第三章 单例模式-Java八股面试(三) 第四章 线程池和Volatile关键字-Java八股面试(四) 提示:动态每日更新算法题,想要学习的可以关注一下 文章目录系列文章目录一、…...

)

别再一张张手动改了!用Python脚本批量解密微信PC版dat图片(附完整代码)

用Python自动化解密微信PC版dat图片的完整指南 微信PC版默认会将接收的图片保存为加密的dat文件格式,这些文件无法直接查看或使用。传统方法需要手动一张张转换,效率极低。本文将详细介绍如何用Python编写脚本,实现dat图片的批量自动解密&am…...

抖音无水印批量下载终极指南:3分钟学会免费下载视频、音乐和直播

抖音无水印批量下载终极指南:3分钟学会免费下载视频、音乐和直播 【免费下载链接】douyin-downloader A practical Douyin downloader for both single-item and profile batch downloads, with progress display, retries, SQLite deduplication, and browser fall…...

羽毛球网前步伐 膝盖疼痛把脉

文章目录 引言 I 羽毛球网前步伐 手脚方向一致 对比 膝盖疼痛把脉 II 知识扩展 调整跑步姿势来避免膝盖受伤的三个具体方法 宽楦(Wide Last) 引言 羽毛球网前步伐技术要点:采用"女前男后"站位,通过并步快速移动(2-3步到位),击球后斜跳回中。强调手脚协调(脚…...

动态寄存器分配优化技术及其在Racetrack内存中的应用

1. 动态寄存器分配优化技术概述寄存器分配优化是计算机体系结构设计中的核心问题之一,它直接影响着处理器的执行效率和能耗表现。传统静态寄存器分配方法在编译时确定寄存器使用方案,虽然实现简单,但无法适应程序运行时的动态行为特征。特别是…...

iOS 18.2提前发布:AI深化、RCS集成与开发者适配全解析

1. 项目概述:一次不寻常的OTA更新如果你是苹果生态的深度用户,或者是一名移动应用开发者,那么最近一周你的神经可能被一条消息牵动着:苹果公司一反常态,将原定于2025年初推送的iOS 18.2操作系统,提前到了今…...

2026技术蓝图:3大架构革新重塑跨平台视觉自动化

2026技术蓝图:3大架构革新重塑跨平台视觉自动化 【免费下载链接】midscene AI-powered, vision-driven UI automation for every platform. 项目地址: https://gitcode.com/GitHub_Trending/mid/midscene 跨平台视觉语言模型驱动的分布式执行引擎与联邦学习框…...

地铁语音系统升级倒计时!2024Q3起新线强制要求TTS可审计日志+合成溯源水印——ElevenLabs合规改造4步法

更多请点击: https://intelliparadigm.com 第一章:地铁语音系统升级倒计时!2024Q3起新线强制要求TTS可审计日志合成溯源水印——ElevenLabs合规改造4步法 随着《城市轨道交通智能语音服务安全规范(试行)》于2024年6月…...

变附着系数AGV横摆稳定性控制【附程序】

✨ 长期致力于无人搬运车、横摆稳定性、变附着系数、路面附着系数估计、直接横摆力矩控制研究工作,擅长数据搜集与处理、建模仿真、程序编写、仿真设计。 ✅ 专业定制毕设、代码 ✅ 如需沟通交流,点击《获取方式》 (1)自适应无迹卡…...

)

别再为固定输入尺寸发愁了:用PyTorch手把手实现SPP层(附完整代码)

突破固定尺寸限制:PyTorch实现空间金字塔池化的工程实践 在计算机视觉任务中,处理不同尺寸的输入图像一直是个令人头疼的问题。想象一下这样的场景:你正在开发一个目标检测系统,训练时所有图像都被统一调整为224224像素ÿ…...

5分钟完成Windows与Office智能激活:KMS_VL_ALL_AIO终极指南

5分钟完成Windows与Office智能激活:KMS_VL_ALL_AIO终极指南 【免费下载链接】KMS_VL_ALL_AIO Smart Activation Script 项目地址: https://gitcode.com/gh_mirrors/km/KMS_VL_ALL_AIO 还在为系统激活问题而烦恼吗?KMS_VL_ALL_AIO是一款功能强大的…...