小梅哥Xilinx FPGA学习笔记18——专用时钟电路 PLL与时钟向导 IP

目录

一:IP核简介(具体可参考野火FPGA文档)

二: 章节导读

三:PLL电路原理

3.1 PLL基本实现框图

3.2 PLL倍频实现

3.3 PLL分频实现

四: 基于 PLL 的多时钟 LED 驱动设计

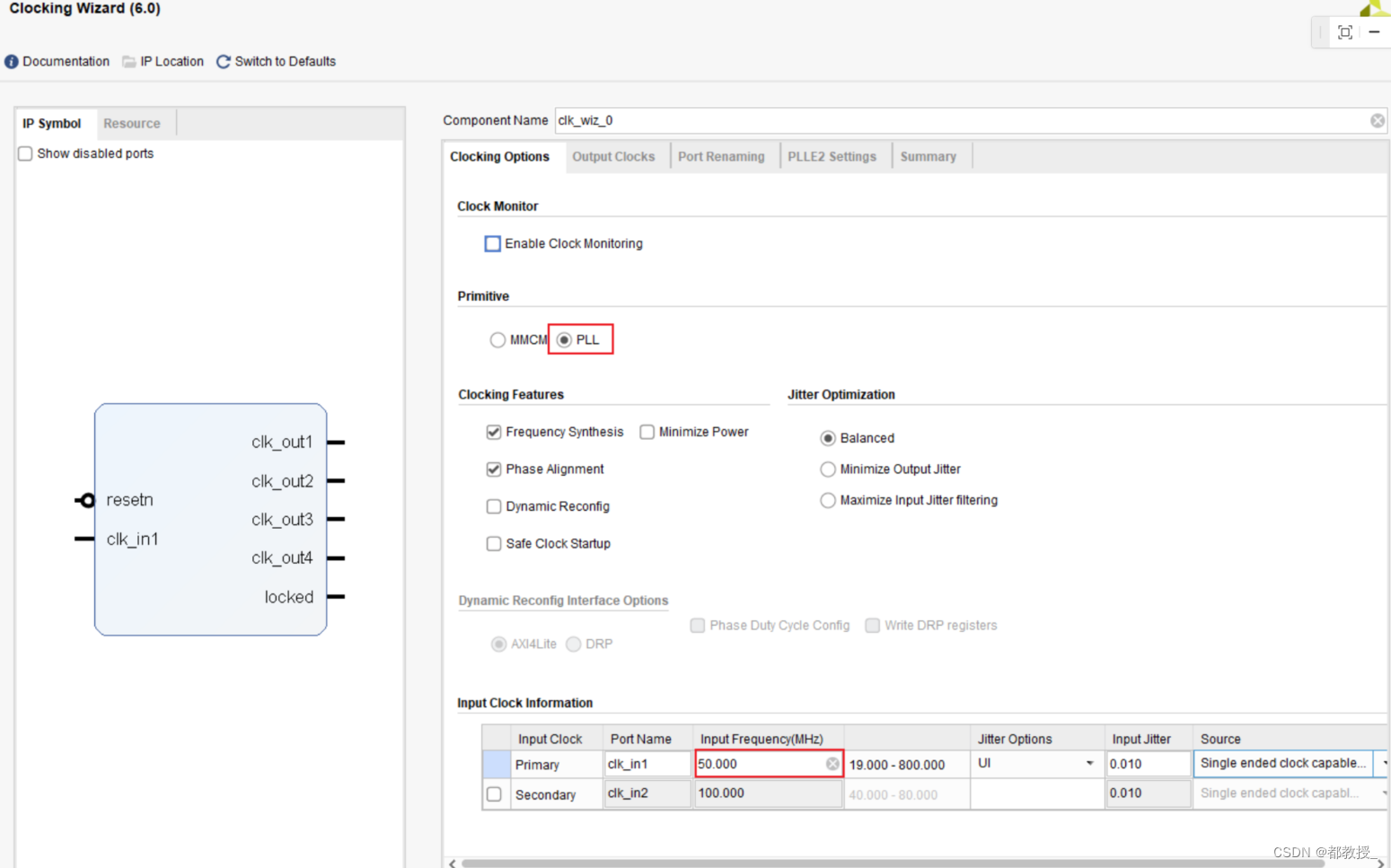

4.1 配置 Clocking Wizard 核

4.2 led 闪烁控制

4.2.1 LED闪烁代码设计

4.3 顶层模块代码设计

4.4 仿真测试文件

4.5 仿真结果

4.6 管脚约束文件

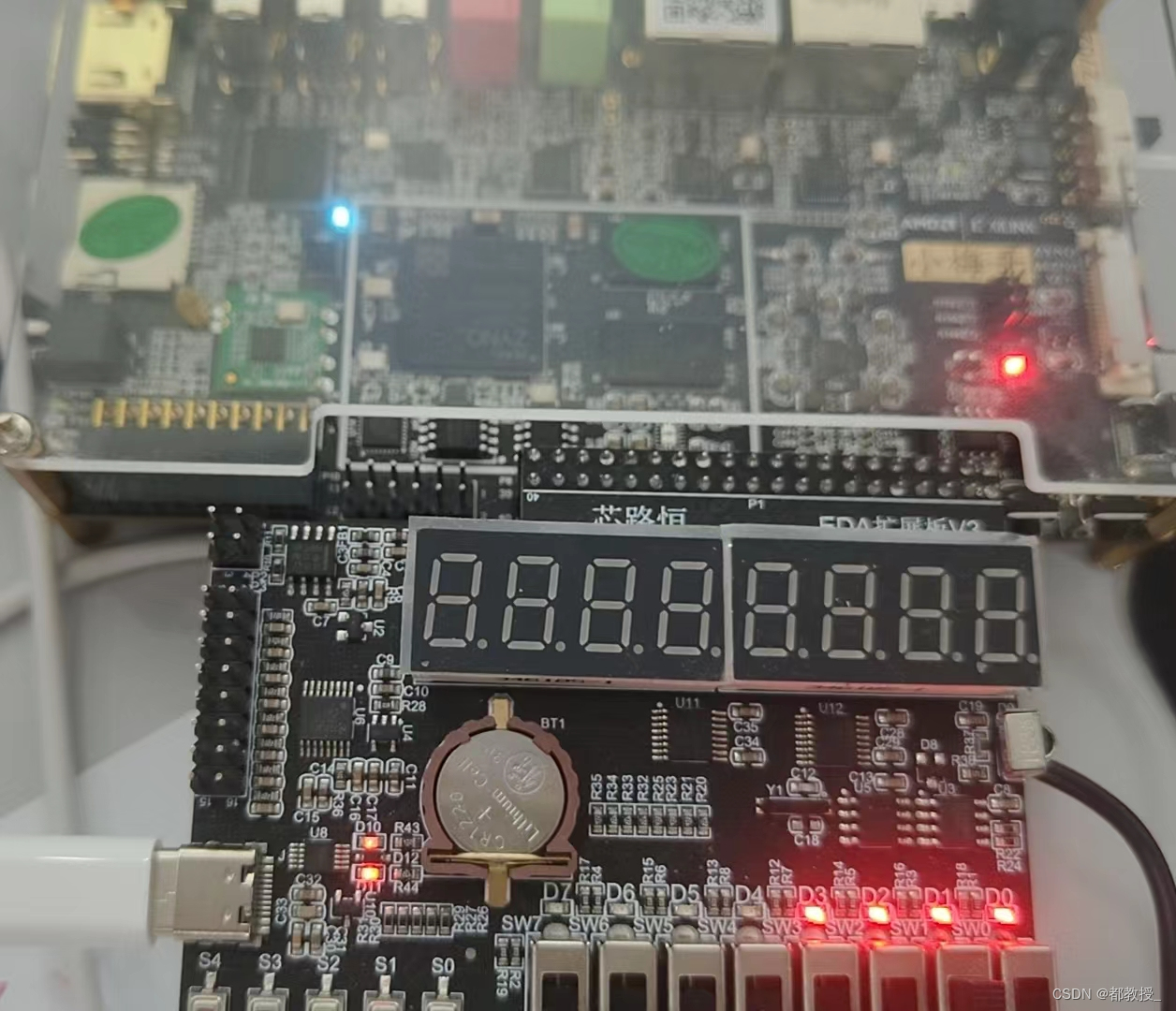

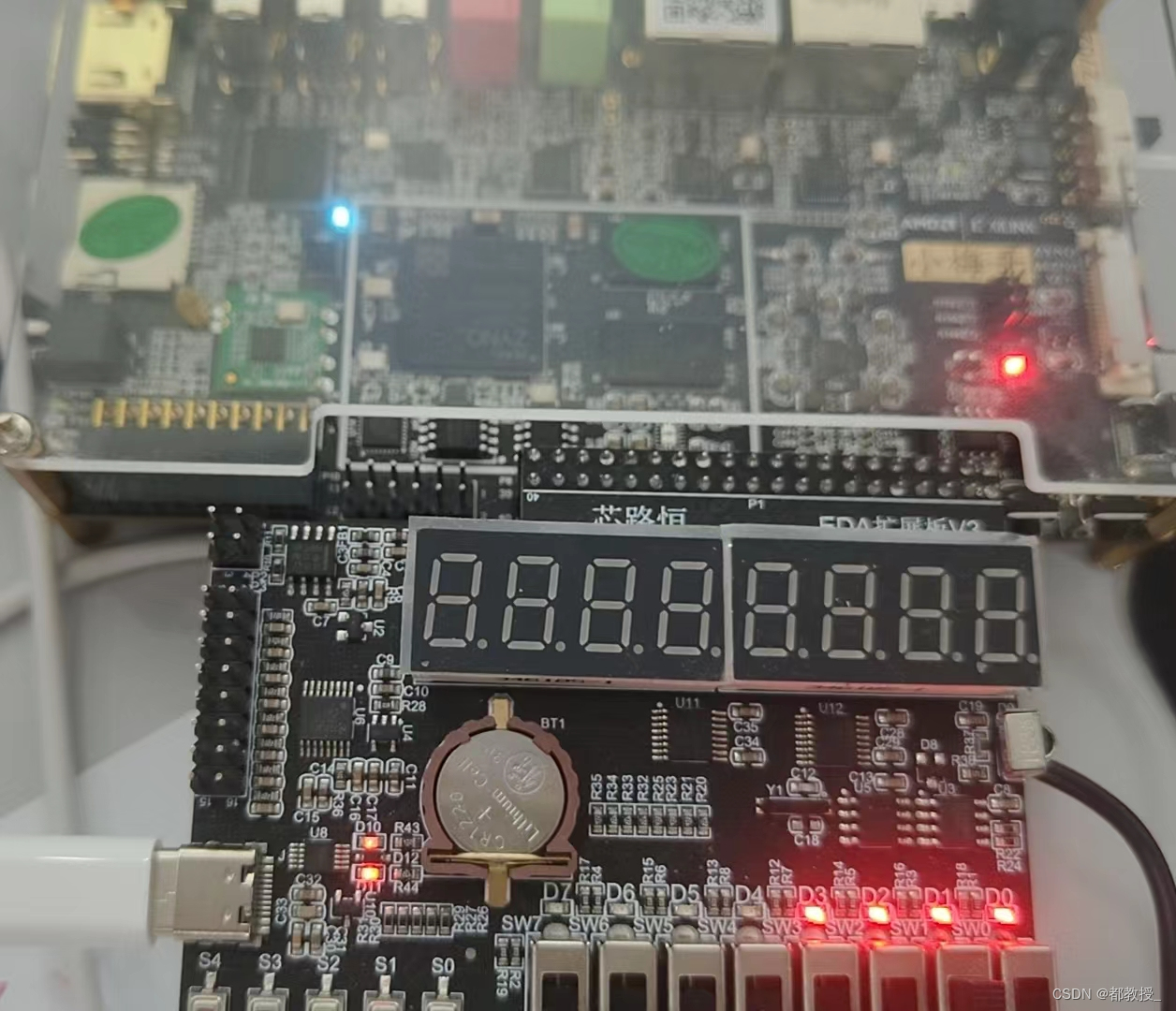

4.7 上板验证结果

一:IP核简介(具体可参考野火FPGA文档)

HDL 语言形式---(软核)硬件描述语言;可进行参数调整、复用性强;布局、布线灵活;设计周期短、设计投入少网表形式---(固核)完成了综合的功能块;可预布线特定信号或分配特定的布线资源。版图形式---(硬核)硬核是完成提供设计的最终阶段产品-掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核的保护。IP核缺点:

- IP核往往不能跨平台使用

- IP核不透明,看不到内部核心代码

- 定制IP需额外收费

二: 章节导读

三:PLL电路原理

- 鉴相鉴频器 PFD(Phase Frequency Detector):对输入的基准信号(通常是来自频率稳定的晶振)和反馈回路的信号进行频率的比较,输出一个代表两者相位差异的信号。若相同则输出0 。参考时钟大于对比时钟频率会输出变大的成正比的值,小于就变小的成正比的值。

3.1 PLL基本实现框图

下图中鉴相鉴频器 PFD(Phase Frequency Detector)是用来比较输入参考信号与反馈信号的频率与相位的。最终它们会趋近于相同,及输出为0。

3.2 PLL倍频实现

从下图可以看出倍频多出了一个DIV倍频环节,如果输入信号是50MHz的频率,因为鉴相鉴频器 PFD的两端最终归趋近于相等,则经过DIV之后的频率会变成50MHz。即如果是2倍频,则pll_out会变成100MHz输出。实现倍频输出。

3.3 PLL分频实现

从下图可以看出分频多出了一个DIV分频环节放在输入信号那里,如果输入信号是50MHz的频率,如果分频器DIV是5倍分频,则输入PFD的频率是10M,因为鉴相鉴频器 PFD的两端最终归趋近于相等,则经过反馈回路输出的频率也为10MHz。则pll_out会变成10MHz输出。实现5分频输出。

四: 基于 PLL 的多时钟 LED 驱动设计

4.1 配置 Clocking Wizard 核

4.2 led 闪烁控制

4.2.1 LED闪烁代码设计

module led_ctrl(input clk,input reset_n,output reg led);parameter MCNT = 1000_0000;reg [29:0]cnt;//led翻转计数逻辑always@(posedge clk or negedge reset_n)if(!reset_n)cnt <= 0;else if(cnt >= MCNT-1) cnt <= 0;else cnt <= cnt + 1;always@(posedge clk or negedge reset_n)if(!reset_n)led <= 0;else if(cnt >= MCNT-1) led <= ~led;else led <= led; endmodule

4.3 顶层模块代码设计

module pll_led(input sys_clk,input reset_n, output [3:0]led

);wire locked ;wire clk_100m ;wire clk_100m_s90 ;wire clk_200m ;wire clk_200m_d20 ;led_ctrl #(.MCNT (5000_0000))led_ctrl_inst0(.clk (clk_100m),.reset_n (locked),//当locked信号为高电平时方可使用,其输出的才是稳定的时钟信号。.led (led[0]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst1(.clk (clk_100m_s90),.reset_n (locked),.led (led[1]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst2(.clk (clk_200m),.reset_n (locked),.led (led[2]));led_ctrl #(.MCNT (5000_0000))led_ctrl_inst3(.clk (clk_200m_d20),.reset_n (locked),.led (led[3]));clk_wiz_0 clk_wiz_0_inst(// Clock out ports.clk_100m(clk_100m), // output clk_100m.clk_100m_s90(clk_100m_s90), // output clk_100m_s90.clk_200m(clk_200m), // output clk_200m.clk_200m_d20(clk_200m_d20), // output clk_200m_d20// Status and control signals.resetn(reset_n), // input resetn.locked(locked), // output locked// Clock in ports.sys_clk(sys_clk)); // input sys_clk

endmodule

4.4 仿真测试文件

`timescale 1ns / 1ps

module pll_led_tb();reg sys_clk ;

reg reset_n ;

wire clk_100m ;

wire clk_100m_s90 ;

wire clk_200m ;

wire clk_200m_d20 ;

wire [3:0]led ;pll_led pll_led(.sys_clk (sys_clk) ,.reset_n (reset_n) ,.clk_100m (clk_100m) ,.clk_100m_s90(clk_100m_s90) ,.clk_200m (clk_200m) ,.clk_200m_d20(clk_200m_d20) ,.led (led)

);//重定义,缩短仿真时间defparam pll_led.led_ctrl_inst0.MCNT = 26'd500;defparam pll_led.led_ctrl_inst1.MCNT = 26'd500;defparam pll_led.led_ctrl_inst2.MCNT = 26'd500; defparam pll_led.led_ctrl_inst3.MCNT = 26'd500;initial sys_clk = 1'b1;always #10 sys_clk = ~sys_clk;initialbeginreset_n = 0;#201;reset_n = 1;#20000; $stop;endendmodule

4.5 仿真结果

4.6 管脚约束文件

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property PACKAGE_PIN F20 [get_ports reset_n]

set_property PACKAGE_PIN G17 [get_ports {led[0]}]

set_property PACKAGE_PIN G19 [get_ports {led[1]}]

set_property PACKAGE_PIN G18 [get_ports {led[3]}]

set_property PACKAGE_PIN G20 [get_ports {led[2]}]

4.7 上板验证结果

至此PLL的IP核调用实验完美成功。

相关文章:

小梅哥Xilinx FPGA学习笔记18——专用时钟电路 PLL与时钟向导 IP

目录 一:IP核简介(具体可参考野火FPGA文档) 二: 章节导读 三:PLL电路原理 3.1 PLL基本实现框图 3.2 PLL倍频实现 3.3 PLL分频实现 四: 基于 PLL 的多时钟 LED 驱动设计 4.1 配置 Clocking Wizard 核 4.2 led …...

低代码平台在金融银行中的应用场景

随着数字化转型的推进,商业银行越来越重视技术在业务发展中的作用。在这个背景下,白码低代码平台作为一种新型的开发方式,正逐渐受到广大商业银行的关注和应用。白码低代码平台能够快速构建各类应用程序,提高开发效率,…...

Css基础内容

<!DOCTYPE html> <html> <head> <meta charset"UTF-8" /> <title>CSS</title> <!-- <link rel"stylesheet" href"Html5与Css3\CSS\my.css"> --> <!-- link引入外部样式表:rel&…...

微服务(11)

目录 51.pod的重启策略是什么? 52.描述一下pod的生命周期有哪些状态? 53.创建一个pod的流程是什么? 54.删除一个Pod会发生什么事情? 55.k8s的Service是什么? 51.pod的重启策略是什么? 可以通过命令kub…...

连锁门店管理需要信息化系统

连锁门店管理的信息化系统可以提供以下功能,以满足连锁企业日常管理的需求: 1. 连锁线下收银:信息化系统可以提供线下收银功能,包括商品扫码、价格结算、支付方式选择等。通过系统记录每笔交易数据,方便对销售情况进行…...

UTF-8编码:打破字符编码的国界

UTF-8编码:打破字符编码的国界 大家好,我是免费搭建查券返利机器人赚佣金就用微赚淘客系统3.0的小编,也是冬天不穿秋裤,天冷也要风度的程序猿!今天,让我们一同探讨编程世界中一项至关重要的技术——“UTF-…...

HTML进阶

列表、表格、表单 文章目录 列表、表格、表单01-列表无序列表有序列表定义列表 02-表格表格结构标签-了解合并单元格 03-表单input 标签input 标签占位文本单选框上传文件多选框下拉菜单文本域label 标签按钮 04-语义化无语义的布局标签有语义的布局标签 05-字符实体 01-列表 …...

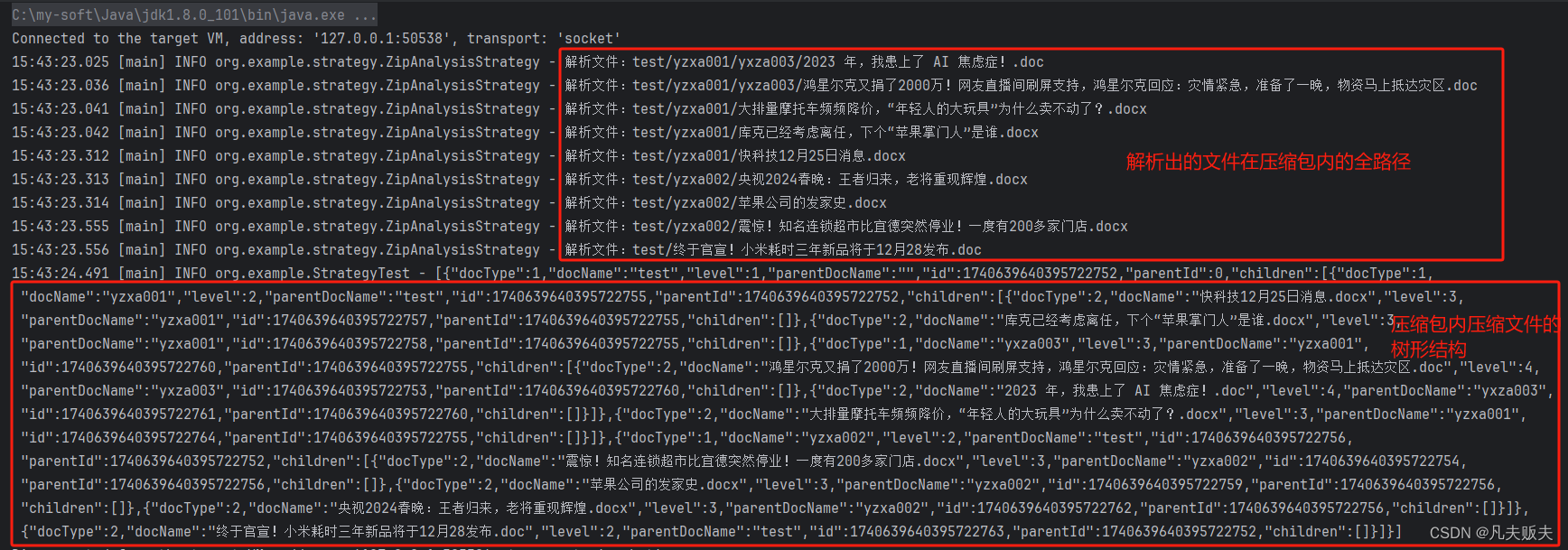

基于策略模式和简单工厂模式实现zip、tar、rar、7z四种压缩文件格式的解压

推荐语 这篇技术文章深入探讨了基于策略模式和简单工厂模式实现四种常见压缩文件格式的解压方法。通过阅读该文章,你将了解到如何利用这两种设计模式来实现灵活、可扩展的解压功能,同时适应不同的压缩文件格式。如果你对设计模式和文件处理感兴趣或刚好…...

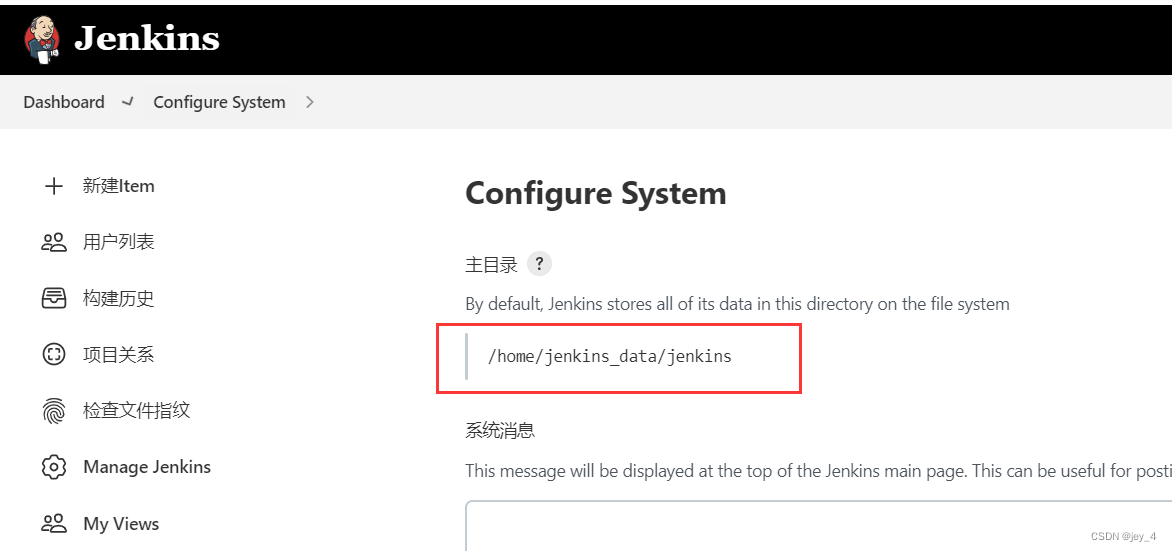

修改jenkins的目录(JENKINS_HOME)

默认JENKINS_HOME是/var/lib/jenkins/ 现要修改为/home/jenkins_data/jenkins 最开始 sudo cp -a /var/lib/jenkins/ /home/jenkins_data/ 然后如下操作: 1、首先 /etc/sysconfig/jenkins:jenkins配置文件,“端口”,“JENKIN…...

Bytebase:统一数据库 CI/CD 解决方案 | 开源日报 No.128

bytebase/bytebase Stars: 7.9k License: NOASSERTION Bytebase 是一个数据库 CI/CD 解决方案,为开发人员和 DBA 提供统一的工具来管理不同数据库系统的开发生命周期。其主要功能包括标准化操作流程、SQL 代码审查、GitOps 集成以及数据访问控制等。关键特性和核心…...

History对象常用方法

文章目录 一、什么是History对象二、使用History对象 一、什么是History对象 history 对象来保存浏览器历史记录信息,也就是用户访问的页面。浏览器的前进与后退功能本质上就是 history 的操作。history 对象记录了用户浏览过的页面,通过该对象提供的 A…...

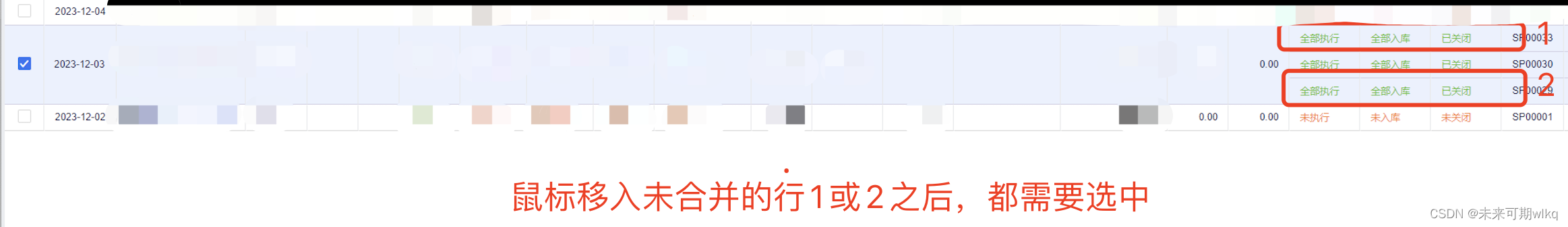

修改源码,element的el-table合并,处理合并产生的hover样式问题

1、确认自己element-ui的版本号 2、此element-ui下的lib包是修改过hover样式的包,如何替换自己文件下的node_modules中的包 修改后将lib文件夹中文件替换你项目中/node_module/element-ui/Lib中的文件问题??如果替换开发环境中的node_module的包无法升级到测试环境,因为nod…...

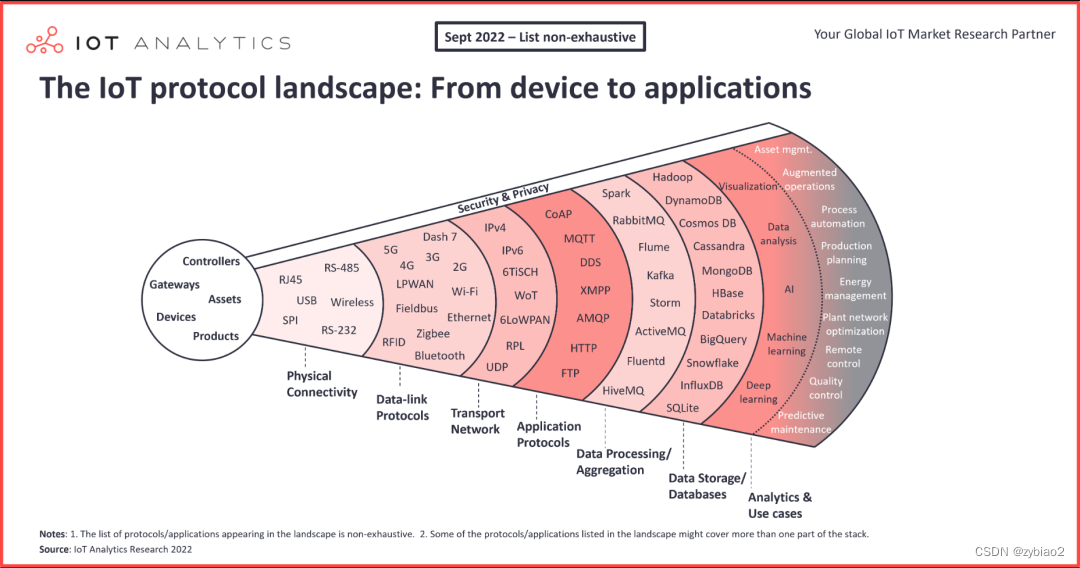

IoT 物联网常用协议

物联网协议是指在物联网环境中用于设备间通信和数据传输的协议。根据不同的作用,物联网协议可分为传输协议、通信协议和行业协议。 传输协议:一般负责子网内设备间的组网及通信。例如 Wi-Fi、Ethernet、NFC、 Zigbee、Bluetooth、GPRS、3G/4G/5G等。这些…...

使用java备份和恢复SQLServer表数据

需求 近来工作中遇到一个问题,内网办公系统中的数据需要导出到外网中进行查询,外网的数据库中还有一些表存储外网的数据,因此无法使用全库备份恢复功能来满足需求。即只从内网数据库中导出若干表的内容至外网数据库的对应表。 其他解决方案…...

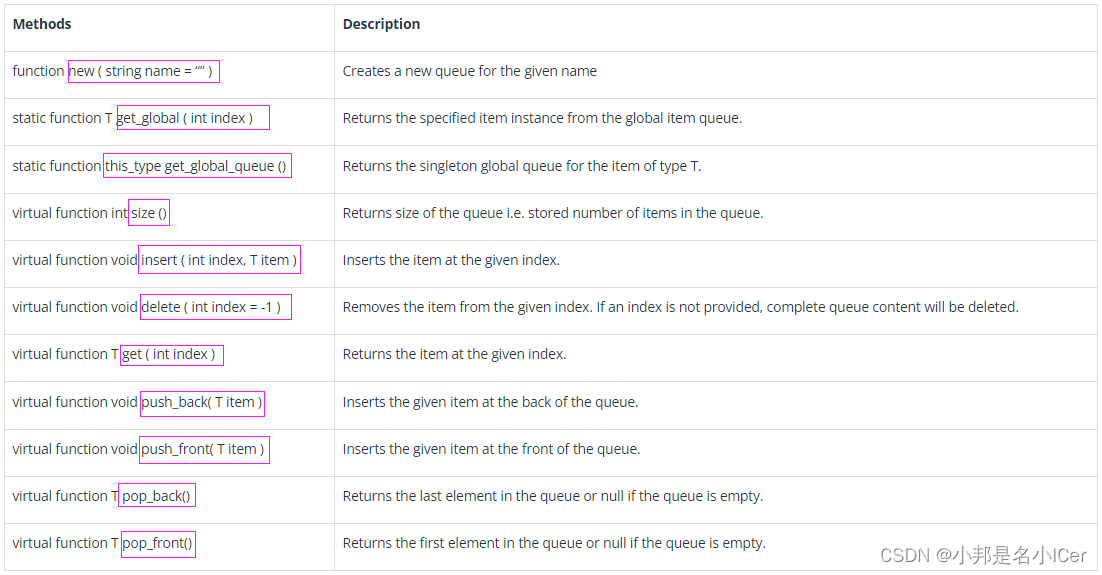

27 UVM queue

uvm_queue类构建一个动态队列,该队列将按需分配并通过引用传递。 uvm_queue类声明: class uvm_queue #( type T int ) extends uvm_object 1 uvm_queue class hierarchy 2 uvm_queue class Methods 3 UVM Queue Example 在下面的示例中,…...

聊聊自动化测试的分层实践

技术群里,有同学聊起了各自在实践自动化测试时遇到的各种问题,最典型的就是落地难度和投入产出比。毕竟在当前这个时间节点,单纯的技术实践如果不能带来实际可见的业务价值,确实很影响个人绩效和团队产出。 这篇文章,…...

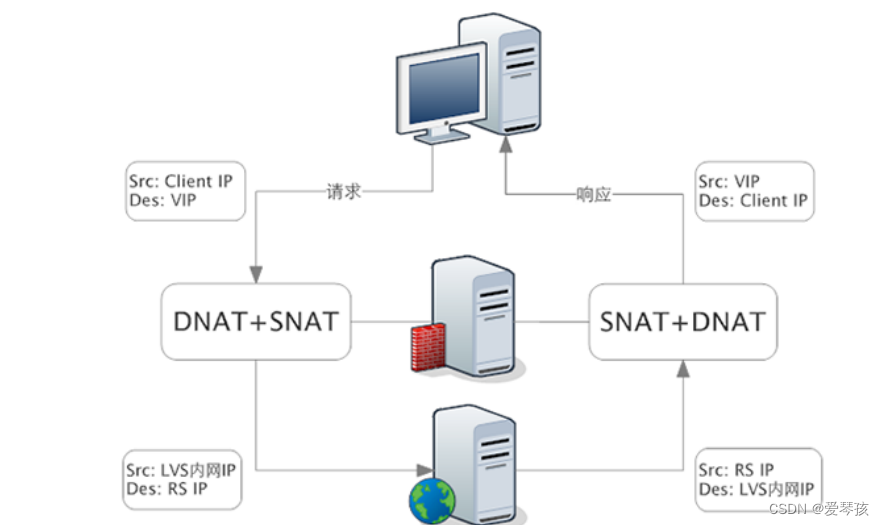

LVS那点事

LVS 原理 IPVS LVS 的 IP 负载均衡技术是通过 IPVS 模块来实现的,IPVS 是 LVS 集群系统的核心软件,它的主要作用是:安装在 Director Server 上,同时在 Director Server 上虚拟出一个 IP 地址,用户必须通过这个虚拟的…...

2022-2023年度广东省职业院校学生专业技能大赛“软件测试”赛项接口测试训练题目

接口测试 新增接口脚本编写和执行测试,并执行脚本。 (1)商品单位添加接口描述如下: 接口功能:提供商品单位新增处理。 接口地址(根据实际系统IP及端口自行替换): http://XX.XX.XX.XX:XXXX/prod-api/manager/category/add。 请求方式:POST。 请求参数:...

[Python][LeetCode]28. 找出字符串中第一个匹配项的下标

给你两个字符串 haystack 和 needle ,请你在 haystack 字符串中找出 needle 字符串的第一个匹配项的下标(下标从 0 开始)。如果 needle 不是 haystack 的一部分,则返回 -1 。 示例 1: 输入:haystack &quo…...

Prometheus监控mysql

docker-compose.yml 创建mysql mkdir/data/mysql -pcat > /data/mysql/docker-compose.yml << EOF version: 3.1 services:db:image: mysql:8.0restart: alwayscontainer_name: mysqlenvironment:TZ: Asia/ShanghaiLANG: en_US.UTF-8MYSQL_ROOT_PASSWORD: 123456comm…...

大语言模型可靠性监测与压缩的谱方法研究

1. 大语言模型可靠性监测与压缩的谱方法研究概述在深度学习领域,大语言模型(LLM)和视觉语言模型(VLM)的可靠性问题与计算效率挑战日益凸显。模型幻觉(生成与输入无关或错误的内容)和分布偏移(面对训练数据分布外的输入时性能下降)会严重损害用户信任,而庞…...

轻量级协作平台设计:集成Git与敏捷开发的项目管理实践

1. 项目概述与核心价值最近在团队协作和项目管理工具选型上,又和几个技术负责人聊了一圈。大家普遍的感受是,市面上的工具要么太重,像Jira、Confluence,配置复杂,学习成本高,小团队用起来像“杀鸡用牛刀”&…...

MySQL-MVCC核心原理-版本链ReadView与可见性判断

MVCC 全称是 Multi-Version Concurrency Control,也就是多版本并发控制。它的核心思想是:为同一行数据维护多个版本,让读写在很多情况下不用互相阻塞。 没有 MVCC 时,读写冲突通常要大量依赖锁。MVCC 让普通 select 可以读一个可见…...

数据模型代码生成器:从OpenAPI/Schema自动生成Python类型安全模型

1. 项目概述:当数据模型遇上代码生成如果你经常和数据模型打交道,无论是OpenAPI规范、JSON Schema,还是数据库的DDL,那你一定体会过手动编写对应数据类(Data Class)或Pydantic模型的繁琐。一个字段类型写错…...

2026 私域救命玩法!90% 的老板赚不到钱,根本不是产品不行

我在杭州做电商、做私域、做投资这么多年,见过各行各业的起起伏伏。这些年接触过的实体老板,没有一百也有八十。手里握着工厂的、拿着自主知识产权的、有正规生产资质的,比比皆是。但 90% 的人都在亏钱。他们天天抱怨流量太贵、同行乱价、客户…...

从“客户匿名”到“可验证”:技术服务案例的工程化写法

在撰写技术服务案例时,我们经常面临一个挑战:客户要求匿名,但案例又需要让潜在客户相信效果。如何平衡?结合文澜天下科技在AI搜索优化项目中的实践,分享一种“可验证”的案例写法。一、定位具体行业和场景 不写“某教育…...

基于STM32单片机人体健康检测血糖检测监测无线蓝牙APP设计S312

本系统由STM32F103C8T6单片机核心板、OLED屏、无线模块、血糖模拟检测、蜂鸣器报警、电源电路、按键电路组成。【1】液晶显示:OLED液晶显示心率值、心率上下限、血氧值、血氧阈值、血压值、血压阈值、血糖值、血糖上下限值以及心率血氧是否在采集测算中、当前数据是…...

扩展卡尔曼滤波锂电池SOC估算【附代码】

✨ 长期致力于锂离子电池、SOC估算、锂离子电池建模、EKF算法研究工作,擅长数据搜集与处理、建模仿真、程序编写、仿真设计。 ✅ 专业定制毕设、代码 ✅ 如需沟通交流,点击《获取方式》 (1)二阶RC等效电路建模与温度自适应参数修正…...

)

别再让电机乱转了!手把手教你用STM32的TIM3和L298N实现精准PWM调速(附完整工程源码)

STM32与L298N电机控制实战:从原理到精准调速的完整指南 在智能小车、机械臂或自动化设备开发中,直流电机控制是最基础却最容易出问题的环节。很多初学者在第一次连接STM32和L298N驱动模块时,都会遇到电机不转、乱转或速度不稳的情况。本文将彻…...

5分钟掌握Snap.Hutao:免费开源的Windows原神桌面工具箱完全指南

5分钟掌握Snap.Hutao:免费开源的Windows原神桌面工具箱完全指南 【免费下载链接】Snap.Hutao 实用的开源多功能原神工具箱 🧰 / Multifunctional Open-Source Genshin Impact Toolkit 🧰 项目地址: https://gitcode.com/GitHub_Trending/sn…...