CPU处理器模式与异常

ARM架构中的Exception Level(EL)

在ARM架构中,Exception Level(EL)是一个关键概念,它表示了处理器当前处理异常或中断的层次。ARMv8-A架构定义了四个Exception Levels:EL0、EL1、EL2和EL3,其中EL0是最低层次,通常用于用户空间的应用程序,而EL3是最高层次,通常用于系统级的服务和中断处理。

当一个异常在较低的EL(例如EL0)发生时,它可能会被传递到更高的EL(例如EL2)进行处理。在这个过程中,需要确定使用哪个Execution State(执行状态)的指令集来处理这个异常。这是因为ARMv8-A架构支持两种执行状态:AArch32(32位执行状态)和AArch64(64位执行状态)。

让我们通过一个具体的例子来解释这个概念:

假设我们有以下的Execution State配置:

- EL0:运行在AArch32状态

- EL1:运行在AArch64状态

- EL2:运行在AArch64状态

现在,如果在EL0(即用户空间的应用程序)发生了一个异常,并且这个异常被传递到EL2进行处理,那么此时我们需要查看比EL2低一级的EL(即EL1)的Execution State来决定使用哪个指令集来处理这个异常。

因为EL1是运行在AArch64状态,所以即使原始的异常是在EL0的AArch32状态下发生的,当异常被传递到EL2进行处理时,它仍然会使用AArch64指令集。

这是因为ARMv8-A架构规定,当异常从一个较低的EL传递到一个较高的EL时,会使用较高EL的Execution State来处理这个异常。

此外,向量表(Vector Table)中的指令块(也称为向量表条目或异常处理程序条目)是用来快速跳转到相应的异常处理程序的。因此,在EL2响应EL0的异常时,会根据EL1的Execution State来选择向量表中的适当条目,作为异常处理的入口点。

总结来说,如果发生异常的EL与响应异常的EL不同,并且发生异常的EL低于响应异常的EL,那么会使用比响应异常的EL低一级的EL的Execution State来决定使用哪个指令集来处理这个异常。这确保了异常可以在正确的执行状态下得到处理。

举个例子

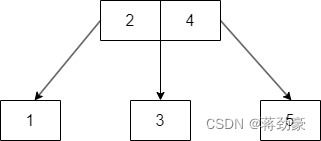

在ARMv8-A架构中,FIQ(Fast Interrupt Request)和IRQ(Interrupt Request)是两种类型的异常,分别对应于快速中断和普通中断。这些异常可以在不同的Exception Levels(ELs)之间传递和处理。为了处理这些异常,系统中会有一个向量表(Vector Table),其中包含了指向不同异常处理程序的入口点。

向量表中的每个条目(或称为指令块)都有一个固定的偏移量,这个偏移量通常是基于异常类型和当前执行状态的。当异常发生时,处理器会根据当前的Execution State和异常类型,从向量表中选取相应的条目,并跳转到该条目指定的地址开始执行异常处理程序。

现在,我们根据你提供的例子来解释这个过程:

EL0:AArch32,EL1:AArch64,EL2:AArch64,EL0发生的FIQ在EL2响应,EL1的Execution State为AArch64,所以execution会跳到offset为0x500的指令块处理异常

-

在这个例子中,一个FIQ异常在EL0(用户空间,32位执行状态)中发生。由于某些原因(如配置或异常处理机制的设计),这个异常被传递到EL2进行处理。

-

当异常传递到EL2时,处理器会查看比EL2低一级的EL(即EL1)的Execution State来确定使用哪个指令集。因为EL1是在AArch64状态下运行的,所以处理器将使用AArch64指令集来处理这个FIQ异常。

-

接下来,处理器会查找向量表中对应于FIQ异常和AArch64执行状态的条目。假设这个条目的偏移量是0x500,那么处理器会跳转到向量表中偏移为0x500的位置,从那里开始执行FIQ异常处理程序。

EL2用的SP是SP_EL0,IRQ exception发生在EL2并在EL2响应,那么execution会跳到offset为0x080的指令块处理异常 -

在这个例子中,一个IRQ异常在EL2中发生并在EL2中响应。这意味着异常处理程序将直接在EL2中执行,不需要传递到其他更低的EL。

-

尽管EL2使用的是SP_EL0(即EL0的栈指针),这通常是为了异常处理过程中的栈管理,但这并不直接影响异常处理程序的执行状态和向量表的查找。

-

处理器会查找向量表中对应于IRQ异常和当前执行状态的条目。如果当前执行状态是AArch64,并且向量表中对应于IRQ异常和AArch64执行状态的条目的偏移量是0x080,那么处理器会跳转到向量表中偏移为0x080的位置,从那里开始执行IRQ异常处理程序。

需要注意的是,向量表的布局和偏移量的具体值是由系统设计和配置决定的,并且可能会根据不同的平台和硬件配置有所不同。因此,在实际系统中,需要参考具体的硬件文档和系统设计来确定向量表的布局和偏移量。

复位异常

在ARMv8-A架构中,复位异常(Reset exception)是一个特殊的异常,它在系统启动或复位时发生。复位异常的处理方式与其他异常有所不同,因为它没有一个固定的返回地址,也就是说,复位后处理器执行的地址是由硬件或软件定义的,而不是由向量表提供的。

-

复位异常处理的地址:当系统复位时,处理器从RVBAR_ELn(Reset Vector Base Address Register at ELn)中定义的地址开始执行。这里的n表示当前实现中最高的Exception Level(EL)级数。换句话说,RVBAR_ELn寄存器中存放的是复位后处理器开始执行的地址。

-

栈指针的使用:在复位异常处理期间,使用的栈指针(SP)是对应当前EL的SP_ELn,而不是SP_EL0。这意味着,如果复位发生在EL2,那么将使用SP_EL2作为栈指针。

-

与ARMv7的不同:在ARMv7架构中,复位处理程序的地址存放在向量表中。但在ARMv8-A中,这个地址存放在RVBAR_ELn寄存器中,这是一个重要的区别。

-

复位后的执行流程:复位异常没有一个“天然”的EL(Exception Level)让其返回,因为复位是一个系统级别的操作,不涉及从一个EL跳转到另一个EL。然而,有时软件可能需要模拟一个返回操作,以便在复位后跳转到某个特定的执行地址。这通常是通过修改SPSR_ELx(Saved Program Status Register at ELx)和ELR_ELx(Exception Link Register at ELx)寄存器,然后执行“ERET”(Exception Return)指令来实现的。

- SPSR_ELx:这个寄存器保存了处理器在执行异常返回之前的状态。通过修改这个寄存器,软件可以设定返回时的处理器状态。

- ELR_ELx:这个寄存器保存了异常返回时要跳转到的地址。通过设置这个寄存器的值,软件可以指定复位后处理器应该跳转到哪个地址执行。

- “ERET”指令:当这个指令被执行时,处理器会使用SPSR_ELx和ELR_ELx中的值来恢复状态,并跳转到指定的地址执行。

总之,在ARMv8-A架构中,复位异常的处理方式是通过RVBAR_ELn寄存器定义的地址开始的,并且使用的栈指针是当前EL对应的SP_ELn。复位后,如果没有天然的EL可以返回,软件可以通过修改SPSR_ELx和ELR_ELx寄存器,并执行“ERET”指令来模拟一个返回操作。

在ARMv8-A架构中,复位异常(Reset exception)是一个特殊的异常,它在系统启动或复位时发生。由于复位是一个系统级别的操作,它并不涉及从一个异常级别(Exception Level,简称EL)跳转到另一个EL。因此,复位异常没有一个“天然”的EL让其返回。然而,在某些情况下,软件可能需要模拟一个返回操作,以便在复位后跳转到某个特定的执行地址。

为了实现这一点,软件可以修改两个关键的寄存器:SPSR_ELx(Saved Program Status Register at ELx)和ELR_ELx(Exception Link Register at ELx)。

-

SPSR_ELx(Saved Program Status Register at ELx):

- 这个寄存器用于保存处理器在执行异常返回之前的状态。它包含了处理器的各种状态信息,如程序计数器(PC)、处理器模式(如EL0、EL1等)、中断使能标志等。

- 通过修改SPSR_ELx,软件可以设定处理器在复位后返回时的状态。例如,软件可以设置SPSR_ELx来指示处理器在复位后应该处于哪种模式下执行,以及应该启用哪些中断等。

-

ELR_ELx(Exception Link Register at ELx):

- 这个寄存器保存了异常返回时要跳转到的地址。换句话说,当处理器执行ERET指令时,它会从ELR_ELx中读取地址,并跳转到该地址执行。

- 通过设置ELR_ELx的值,软件可以指定复位后处理器应该跳转到哪个地址执行。这个地址通常是系统启动代码或初始化代码的地址。

-

“ERET”指令:

- ERET(Exception Return)指令用于从异常处理程序中返回。当处理器执行ERET指令时,它会使用SPSR_ELx和ELR_ELx中的值来恢复处理器的状态,并跳转到ELR_ELx中指定的地址执行。

- 在复位异常的情况下,软件可以通过设置SPSR_ELx和ELR_ELx的值,然后执行ERET指令来模拟一个返回操作,使处理器在复位后跳转到指定的地址执行。

需要注意的是,**这种模拟返回操作通常只在特定的场景下使用,例如系统启动或复位时。**在正常的异常处理流程中,处理器会根据异常类型和当前执行状态自动选择返回到的EL和地址。

而在复位异常的情况下,由于复位是一个系统级别的操作,没有上一个执行状态可以返回,因此需要通过软件干预来模拟一个返回操作。

处理ARMv8-A架构复位异常的代码例子

处理ARMv8-A架构复位异常的代码将取决于具体的系统设计和需求。

由于复位异常是系统启动或复位时发生的**,它通常涉及一些低级的初始化任务,如设置内存、配置硬件、初始化中断向量表等。**

以下是一个简化的例子,展示了在ARMv8-A架构中处理复位异常的可能代码结构。请注意,这个例子是为了教学目的而简化的,实际的代码可能会更加复杂,并且会涉及更多细节。

c

// 假设这段代码在EL2执行 // 定义一个复位处理程序的入口点

void reset_handler(void) { // 这里是复位处理程序的代码 // 它可能会包含硬件初始化、内存配置、中断向量表设置等 // 假设我们要返回到EL1的一个特定地址 uint64_t return_address_el1 = 0x40000000; // 这是一个假设的EL1地址 // 修改SPSR_EL2以设置返回时的状态 // 这里的设置取决于你希望处理器在返回时处于什么样的状态 asm volatile ( "msr spsr_el2, %0" : : "r" (0x40000000) // 假设的值,通常需要根据你的需求设置 ); // 设置ELR_EL2为返回地址 asm volatile ( "msr elr_el2, %0" : : "r" (return_address_el1) ); // 执行ERET指令以返回 asm volatile ( "eret" ); // ERET之后,控制权将返回到指定的EL1地址 // 注意:这里的代码实际上不会执行,因为ERET会导致处理器跳转到新的地址

} // 这个函数可能会被放在向量表中,作为复位异常的处理程序

void vector_table_entry(void) { // 跳转到复位处理程序 reset_handler();

} // 实际的向量表可能包含多个条目,每个条目对应一个异常或中断

// 复位异常的向量表条目通常位于地址0,因为这是系统复位时首先执行的地址在这个例子中,reset_handler 函数是复位异常的处理程序。它包含一些初始化代码,并设置SPSR_EL2和ELR_EL2寄存器以准备返回到一个特定的EL1地址。然后,它执行eret指令以返回到该地址。

需要注意的是,这个例子假设复位异常处理程序在EL2执行,并且我们想要返回到EL1。实际的场景可能会有所不同,取决于你的系统配置和需求。

另外,这个例子使用了内联汇编来修改寄存器和执行eret指令。在实际的代码中,你可能需要使用更具体的寄存器名称和值,以及更多的错误检查和异常处理逻辑。此外,你还需要确保你的代码与你的硬件平台和ARMv8-A架构的具体实现兼容。

Exception的处理过程

- Save processor state

- Change processor state for exception

- Execute exception handle

- Return to main application

异常(Exception)的处理过程在计算机系统中是一个关键的部分,用于响应和处理在程序执行期间发生的错误或特殊条件。下面是对异常处理过程的简单概括:

保存处理器状态(Save Processor State):

当异常发生时,处理器首先会保存当前的处理器状态。这包括程序计数器(PC,指示下一条要执行的指令的地址)、栈指针(用于访问函数调用栈)、寄存器状态(包括各种处理器寄存器的值)以及其他与当前程序执行环境相关的信息。保存这些状态是为了在异常处理过程中和之后能够恢复它们,以便程序可以正确地从异常中恢复执行。

改变处理器状态以处理异常(Change Processor State for Exception):

接下来,处理器会更改其状态以进入异常处理模式。这可能包括禁用中断(以防止在处理一个异常时发生另一个异常)、切换到特殊的异常处理栈(用于存放异常处理函数的调用栈)、设置特殊的标志位(指示当前正在处理异常),以及将控制转移到异常处理代码。

执行异常处理(Execute Exception Handler):

处理器会跳转到预定义的异常处理代码(也称为异常处理程序或中断服务例程)。这个代码会根据异常的类型和上下文执行相应的操作。这可能包括识别异常原因、记录错误信息、采取恢复措施(如回滚到之前的稳定状态)、尝试修复错误或执行其他清理和恢复任务。异常处理程序可能还会与操作系统或其他软件组件交互,以获取更高级别的错误处理或报告。

返回主应用程序(Return to Main Application):

一旦异常处理程序完成了其任务,处理器会恢复之前保存的处理器状态。这包括恢复程序计数器、栈指针和寄存器状态,以便程序可以从中断的位置继续执行。然后,处理器会返回到主应用程序,从异常发生时的下一条指令开始继续执行程序。

这个过程确保了程序在遇到异常时能够有序地响应,并在可能的情况下恢复到一个稳定的状态,从而提高了程序的健壮性和可靠性。同时,它也允许程序员和系统设计者通过定义自定义的异常处理程序来定制异常处理行为,以满足特定应用的需求。

Reset的例子:EL3复位后进入EL1的过程

在ARMv8-A架构中,当系统从EL3复位后需要进入EL1执行时,需要进行一系列的配置和状态设置。以下是一个简化的例子来说明这个过程:

Disable EL2

在EL3复位后,首先需要禁用EL2。这个过程涉及将EL2的所有系统寄存器配置为安全值,确保EL2在复位后不会对系统造成影响。具体步骤包括:

- 把SCR_EL3.HCE(Hypervisor Control Enable)设置为0,以禁用HVC(Hypervisor Call)指令。

- 禁用所有指令traps,并禁止异常路由到EL2。

Disable EL3

接下来,需要禁用EL3本身。这通常涉及禁用SMC(Secure Monitor Call)指令和其他与EL3相关的功能。具体步骤包括:

- 把SCR_EL3.SMD(Secure Monitor Disable)设置为1,以禁用SMC指令。

- 禁止异常路由到EL3。

Configure EL1

在禁用EL2和EL3之后,需要配置EL1以使其准备好执行程序。这包括:

- 把VBAR_EL1(Vector Base Address Register at EL1)设置为EL1引导程序的起始地址。

- 配置EL1的执行状态(AArch64或AArch32),通过设置SCR_EL2.RW(Read-Write access to 32-bit EL1 system registers)的值为1或0来实现。

- 配置EL1的安全状态(Secure或Non-secure),通过设置SCR_EL3.NS(Non-secure access to EL3 registers)来实现。

Generate exception return

最后,需要生成一个异常返回,使处理器从EL3返回到配置好的EL1。具体步骤包括:

-

把SPSR_EL3(Saved Program Status Register at EL3)设置为返回到EL1时的相应值,这包括设置处理器状态、模式等。

-

把VBAR_EL1的值赋给ELR_EL3(Exception Link Register at EL3),这是处理器在返回时将跳转到的地址。

-

执行ERET(Exception Return)指令,使处理器从EL3返回到配置好的EL1,并从ELR_EL3中指定的地址开始执行。

这个过程确保了系统在从EL3复位后能够安全、正确地进入EL1并执行程序。需要注意的是,这个过程可能因具体的硬件平台和系统实现而有所不同,但基本的步骤和原理是相似的。

FIQ与IRQ在ARM架构中的差异与特性

FIQ和IRQ是ARM架构中两种重要的中断类型,为了支持这两种中断,ARM提供了相应的处理器模式。ARM总共有7种处理模式,其中FIQ和IRQ是两种中断模式。

1. 中断配置与类型

在中断控制器中,我们可以配置某个中断输入是FIQ还是IRQ。通常,为了快速响应且处理时间较短的中断会设置为FIQ,而其他则设为IRQ。

2. 处理器模式切换

当中断发生时,中断处理器会通过相应的请求线通知ARM。如果是IRQ中断,ARM会切换到IRQ模式运行;如果是FIQ中断,则会切换到FIQ模式。

3. 寄存器处理

ARM的FIQ模式提供了更多的banked寄存器(r8到r14以及SPSR),而IRQ模式则没有这么多。这意味着在IRQ模式下,中断处理程序需要自行保存和恢复这些寄存器,而在FIQ模式下,这些操作由CPU自动完成,从而提高了效率。

4. 优先级与中断处理

FIQ具有比IRQ更高的优先级。如果两者同时发生,FIQ会优先处理。此外,在FIQ模式处理中断时,其他类型的异常或中断(如预取指令异常、未定义指令异常、软件中断等)都会被屏蔽,确保FIQ的快速执行。

5. 入口地址与中断向量

FIQ的入口地址是0x1c,而IRQ的是0x18。FIQ的中断向量地址通常位于0x0000001C,IRQ的则位于0x00000018(也有位于FFFF001C和FFFF0018的情况)。由于FIQ向量表后没有其他中断向量,因此可以直接放置FIQ的中断处理程序,减少了跳转指令的数量。

6. 响应延迟

IRQ的响应延迟相对较大,可能会延迟几个指令周期。而FIQ的响应延迟则相对较短,但具体细节可能因硬件实现而异。

7. 中断延迟的优化

中断延迟是指从外部中断请求信号发出到执行对应的中断服务程序ISR的第一条指令所需要的时间。通过合理的软件设计和中断优先级设置,可以缩短这一延迟。

总结

FIQ和IRQ在ARM架构中具有不同的特性和优先级。FIQ由于其独特的硬件支持和更少的寄存器操作,通常能够更快速地响应和处理中断。这使得FIQ在处理需要快速响应的中断时具有明显优势。

为什么FIQ比IRQ快?

- 更多的Banked寄存器:在ARM的FIQ模式下,r8到r14以及SPSR都有独立的物理寄存器,无需压栈保存。而在IRQ模式下,R8, R9, R10, R11, R12没有独立的Banked寄存器,中断处理程序需要自行保存和恢复这些寄存器的值。

- 自动保存与恢复:在FIQ模式下,当模式切换时,CPU会自动保存这些值到Banked寄存器,并在退出FIQ模式时自动恢复。这减少了手动保存和恢复寄存器的时间。

- 更高的优先级:FIQ具有比IRQ更高的优先级。如果两者同时产生,FIQ会先被处理。

- 中断向量地址:FIQ的中断向量地址是0x1C,而IRQ的是0x18。由于FIQ的中断向量地址后没有其他的中断向量表,所以FIQ的中断处理程序可以直接放在该地址,省去了跳转的时间。

- 响应速度:从Verilog仿真来看,IRQ的响应会延迟几个指令周期。而FIQ的响应速度可能更快,但具体细节可能因硬件实现而异。

FIQ中断处理的高效性:寄存器的利用与节省时间

在ARM架构中,FIQ模式与IRQ模式相比,拥有更多的独立Banked寄存器,包括r8到r14以及SPSR。这些额外的寄存器在FIQ中断处理过程中发挥着重要作用,尤其是当涉及到中断处理程序的编译和优化时。

当ARM编译器处理FIQ中断处理程序时,它会检查这个处理程序是否能够仅使用这些独立的Banked寄存器来完成其工作。如果可以,编译器就会避免将通用寄存器压入栈中。这种避免压栈的行为可以显著节省中断处理过程中的时间,因为压栈和出栈操作通常需要额外的指令周期来执行。

这种优化特别适用于那些简短而高效的中断处理程序。**由于FIQ模式的中断处理程序通常被设计为处理快速且紧急的事件,因此它们往往不需要访问大量的数据或复杂的变量。**这意味着它们可以充分利用FIQ模式的Banked寄存器来完成任务,而无需额外的栈操作。

总之,ARM架构中FIQ模式的独特设计,特别是其额外的独立Banked寄存器,使得FIQ中断处理程序在编译时能够得到优化。通过避免不必要的通用寄存器压栈操作,FIQ中断处理能够更快、更高效地完成其任务,从而提高了整个系统的响应速度和性能。

FIQ与IRQ的中断向量地址差异及其影响

在ARM架构中,当中断发生时,处理器需要知道如何跳转到相应的中断处理程序。中断向量表(也称为中断向量或异常向量表)提供了一个映射,将不同类型的中断或异常映射到相应的处理程序。FIQ和IRQ有不同的中断向量地址,这影响了它们的中断处理流程。

中断向量地址:

- FIQ的中断向量地址通常是0x0000001C(或在某些架构中可能是FFFF001C)。

- IRQ的中断向量地址通常是0x00000018(或FFFF0018)。

这些地址在启动代码时被设定,并且处理器在响应中断时会跳转到这些地址。

中断处理程序的放置:

由于FIQ的中断向量地址后面没有其他的中断向量表,所以FIQ的中断处理程序可以直接放在这个地址处。这意味着当FIQ中断发生时,处理器可以直接跳转到该地址并开始执行处理程序,无需额外的跳转指令。

相比之下,IRQ的中断向量地址0x00000018(或FFFF0018)后面通常会有一个小的跳转指令,该指令会将处理器跳转到实际的中断处理程序。这是因为0x00000018(或FFFF0018)地址通常只足够存放一条跳转指令。

跳转指令的影响:

由于IRQ的中断向量地址后面有跳转指令,这意味着当中断发生时,处理器首先会执行这个跳转指令,然后再跳转到实际的中断处理程序。这个额外的跳转步骤增加了中断处理的延迟。

而对于FIQ,由于中断处理程序直接放在中断向量地址处,因此没有这个额外的跳转步骤,从而减少了中断处理的延迟。

总结:

FIQ和IRQ的中断向量地址差异导致了它们中断处理流程的不同。FIQ由于可以直接在其中断向量地址处放置处理程序,因此通常具有更快的响应速度。而IRQ则需要一个额外的跳转步骤,这增加了中断处理的延迟。

这也是为什么在某些需要快速响应的场景中,FIQ被优先考虑的原因。

IRQ与FIQ的响应延迟差异及其原因

在ARM架构中,IRQ(Interrupt Request)和FIQ(Fast Interrupt Request)的响应延迟确实存在区别。响应延迟是指从外部中断请求信号发出到执行对应的中断服务程序(ISR)的第一条指令所需的时间。

IRQ的响应延迟

IRQ的响应通常不如FIQ快。从Verilog仿真或其他硬件级别的观察中,可以看到IRQ在响应中断时会有一定的延迟。这主要是因为:

- 预取指令的影响:IRQ在响应时可能会等待预取指令执行完毕。预取指令是处理器为了提高性能而预先从内存中取出的指令。当中断发生时,如果处理器正在执行预取指令,它可能需要等待这些指令完成后再跳转到中断向量表。

- 跳转指令的存在:如前所述,IRQ的中断向量地址通常只存放一条跳转指令,这意味着处理器在响应IRQ中断时首先需要执行这条跳转指令,然后再跳转到实际的中断处理程序。这个跳转过程会增加响应延迟。

FIQ的响应延迟

相比之下,FIQ的响应延迟通常较短,甚至可能比IRQ更快。这主要得益于以下几点:

-

独立的物理寄存器:FIQ模式的R8~R14寄存器都是独立的物理寄存器,无需压栈保存。这减少了中断处理过程中的额外操作,从而缩短了延迟。

-

中断向量地址的位置:FIQ的中断向量地址位于向量表的最后一个,这允许将中断服务程序直接放在该地址处。这样,当FIQ中断发生时,处理器可以直接跳转到处理程序,无需额外的跳转指令。

-

较高的优先级:FIQ通常具有比IRQ更高的优先级。这意味着当同时发生多个中断时,FIQ会优先得到处理。这也有助于减少FIQ的响应延迟。

通过软件程序设计缩短中断延迟

虽然硬件设计对中断延迟有很大影响,但软件程序设计也可以在一定程度上缩短中断延迟。其中两种常见的方法是:

- 中断优先级:合理设置中断的优先级,确保重要的中断能够得到优先处理。

- 中断嵌套:允许中断嵌套意味着一个中断处理程序在执行过程中可以被另一个更高优先级的中断打断。这有助于减少高优先级中断的响应延迟。

综上所述,IRQ和FIQ的响应延迟确实存在区别,这主要受到它们硬件设计和中断处理流程的影响。FIQ由于其特殊的硬件设计和优化,通常具有更快的响应速度。

如何缩短中断延迟?

中断延迟是从外部中断请求信号发出到执行对应的中断服务程序ISR的第一条指令所需的时间。为了缩短这个延迟,可以通过软件程序设计来优化中断优先级和中断嵌套。

external abort

external abort来自memory system, 是访问外部memory system产生的异常(当然不是所有的来自memory system的abort都是external abort,例如来自MMU的abort就不是external abort,这里的external是针对processor而非cpu core而言,因此MMU实际上是internal的)。

external abort发生在processor通过bus访问memory的时候(可能是直接对某个地址的读或者写,也可能是取指令导致的memory access),processor在bus上发起一次transaction,在这个过程中发生了abort,abort来自processor之外的memory block、device block或者interconnection block,用来告知processor,搞不定了,你自己看着办吧。

在计算机系统中,当处理器(processor)尝试通过总线(bus)访问外部内存系统(memory system)时,可能会发生多种类型的异常。其中,“external abort”是一种特定的异常类型,它发生在处理器与外部内存系统交互的过程中。

让我们详细解释一下这个概念:

External Abort的来源:

当我们说“external abort来自memory system”时,我们指的是这种异常是由处理器的内存系统外部的因素引起的。这通常涉及到处理器与内存或其他设备之间的通信问题。

与MMU的Abort的区别:

MMU(内存管理单元)是处理器内部的一个组件,它负责处理虚拟到物理地址的转换。当处理器尝试访问一个无效或受保护的内存地址时,MMU会触发一个abort。这种abort通常被认为是“internal abort”,因为它是由处理器内部组件引起的。

相比之下,external abort是由处理器外部的组件或设备引起的。

External Abort的发生场景:

当处理器通过总线与外部内存或设备通信时,它会发起一个事务(transaction)。这个事务可能是一个简单的读或写操作,也可能是执行指令时导致的内存访问。

如果在这个过程中,外部内存系统或与之相连的设备检测到某种错误条件(如无效的地址、设备故障、不支持的操作等),它们会发送一个abort信号到处理器,告知它无法完成这个事务。

Abort信号的作用:

Abort信号的作用是通知处理器,当前的内存访问或事务无法继续执行。处理器在接收到这个信号后,通常会停止当前的操作,并采取一些措施来处理这个异常。这可能包括重试操作、记录错误信息、或者触发一个中断以便操作系统或更高级别的软件来处理。

External的含义:

在这里,“external”一词是相对于处理器而言的。它指的是引起abort的因素位于处理器的外部,而不是处理器内部(如MMU)。这有助于区分是由处理器的内部组件(如MMU)还是外部组件(如内存、设备或总线)引起的异常。

理解这些概念对于调试和优化系统性能至关重要,特别是在嵌入式系统、实时系统或需要高度可靠性和稳定性的应用中。在这些系统中,正确处理external abort等异常情况是确保系统稳定性和可靠性的关键。

SError interrupt是发生了external abort导致的异步异常

“SError interrupt” 通常与硬件异常相关,特别是在嵌入式系统或低级硬件编程中。当我们说“发生了external abort导致的异步异常”时,这通常意味着硬件在执行某些操作时遇到了一个它不能处理或不应该出现的条件。

为了更好地理解这个错误,我们可以将其分解为几个部分:

SError interrupt:这是一个中断,由硬件触发,以通知软件发生了某种错误。中断是计算机系统中用于快速响应特定事件(如硬件错误、键盘输入等)的机制。

External Abort:这通常指的是一个外部硬件或内存访问异常。例如,当CPU尝试从不允许访问的内存地址读取或写入数据时,可能会发生外部中止。这可能是由于硬件故障、错误的内存映射或其他原因导致的。

异步异常:这意味着异常发生的时间不是由程序直接控制的。在同步异常中,程序知道何时可能会发生异常,并且可以(通常)采取措施来预防或处理它。但在异步异常中,异常可能在任何时候发生,而程序通常没有机会预防或预测它。

当硬件检测到外部中止时,它会生成一个中断,以通知操作系统或其他软件层发生了错误。然后,操作系统或软件需要决定如何处理这个错误,例如通过记录错误、尝试恢复或重置系统。

为了调试和解决这个问题,你可能需要查看硬件的文档,了解可能的错误原因,检查硬件连接、内存映射和其他相关设置,以及查看任何相关的日志或错误报告。

相关文章:

CPU处理器模式与异常

ARM架构中的Exception Level(EL) 在ARM架构中,Exception Level(EL)是一个关键概念,它表示了处理器当前处理异常或中断的层次。ARMv8-A架构定义了四个Exception Levels:EL0、EL1、EL2和EL3&…...

Day 53 |● 1143.最长公共子序列 ● 1035.不相交的线 ● 53. 最大子序和

1143.最长公共子序列 class Solution { public:int longestCommonSubsequence(string text1, string text2) {vector<vector<int>> dp(text1.size()1,vector<int>(text2.size()1,0));int res 0;for(int i 1; i < text1.size(); i){for(int j 1; j <…...

ant-desgin charts双轴图DualAxes,柱状图无法立即显示,并且只有在调整页面大小(放大或缩小)后才开始显示

摘要 双轴图表中,柱状图无法立即显示,并且只有在调整页面大小(放大或缩小)后才开始显示 官方示例代码 在直接复制,替换为个人数据时,出现柱状图无法显示问题 const config {data: [data, data],xFiel…...

获取别人店铺的所有商品API接口

使用淘宝淘口令接口的步骤通常包括: 注册成为淘宝开放平台的开发者:在淘宝开放平台网站上注册账号并完成认证。 创建应用以获取API密钥:在您的开发者控制台中创建一个应用,并获取用于API调用的密钥,如Client ID和Clie…...

成都正信:亲戚借了钱一直不还怎么委婉的说

在中国传统文化中,亲情关系往往被视为最为重要和敏感的部分。当亲戚间发生借贷时,若出现拖欠不还的情形,处理起来尤为棘手。面对这样的尴尬局面,采取委婉而有效的沟通方式至关重要。 张华最近就遇到了这样的困扰。他的表弟去年因急…...

Truenas入门级教程

Truenas入门教程 前言:系统相关配置 采用I3 4160,采用了2块500G的硬盘,内存为8G,两个网卡只用了其中一个,系统安装的是core版本 硬件采用DELL3020MT机箱,自带3个SATA网口,后期网口不够&#…...

over(条件))

窗口函数dense() over(条件)

力扣题目连接 https://leetcode.cn/problems/rank-scores/ 在 SQL 中,DENSE_RANK() 是一个窗口函数,用于计算结果集中每行的稠密排名(dense rank)。DENSE_RANK() 函数会为具有相同排序字段值的行分配相同的排名,但不会…...

蓝牙APP开发实现汽车遥控钥匙解锁汽车智能时代

在现代社会,随着科技的不断发展,汽车已经不再是简单的交通工具,而是与智能科技紧密相连的载体。其中,通过开发APP蓝牙程序实现汽车遥控钥匙成为了一种趋势,为车主带来了便捷与安全的体验。虎克技术公司作为行业领先者&…...

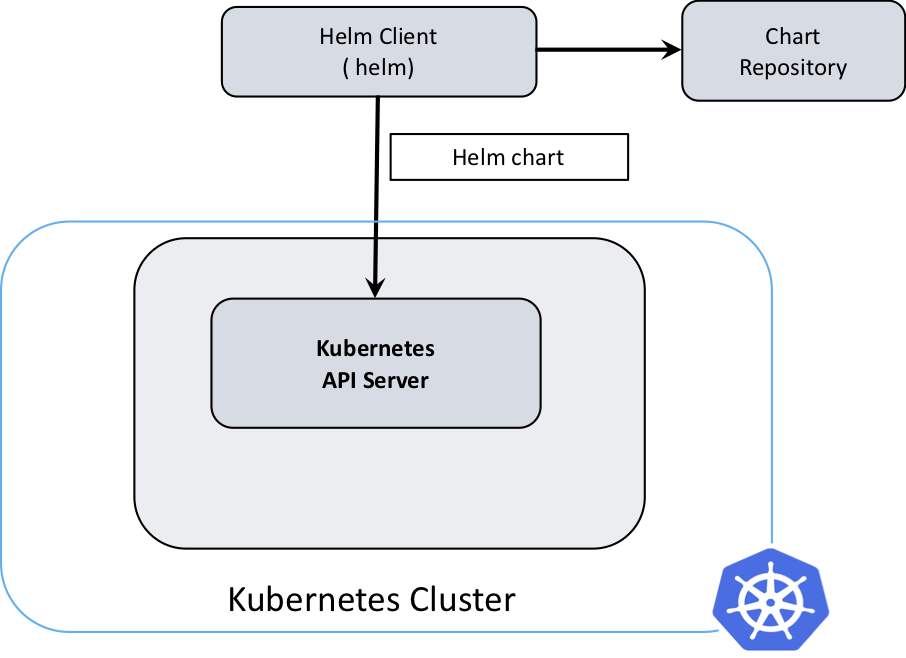

第三天 Kubernetes进阶实践

第三天 Kubernetes进阶实践 本章介绍Kubernetes的进阶内容,包含Kubernetes集群调度、CNI插件、认证授权安全体系、分布式存储的对接、Helm的使用等,让学员可以更加深入的学习Kubernetes的核心内容。 ETCD数据的访问 kube-scheduler调度策略实践 预选与…...

redis小结

1.mysql是数据库,redis是数据库,那么什么时候使用应该使用哪种数据库? redis做缓存是为了缓解mysql的压力,在数据库表数据量上千万,并且访问频繁时,mysql压力增大,在有索引的情况下依旧效果不佳,需要使用…...

PHP伪协议详解

PHP伪协议详解 一、前言1.什么是PHP伪协议?2.什么时候用PHP伪协议? 二、常见的php伪协议php://inputphp://filterzip://与bzip2://与zlib://协议data://phar:// 一、前言 1.什么是PHP伪协议? PHP伪协议是PHP自己支持的一种协议与封装协议,…...

进程:守护进程

一、守护进程的概念 守护进程是脱离于终端控制,且运行在后端的进程。(孤儿进程)守护进程不会将信息显示在任何终端上影响前端的操作,也不会被终端产生的任何信息打断,例如(ctrlc).守护进程独立…...

千里马平台项目管理理念

软件项目的成功和失败和技术关系不大,尤其是应用型软件,不可能有技术难关卡死了项目,大部分问题还是出现在项目管理层面。公司的业务形态是帮助客户构建自己的信息化生态圈,项目管理咨询也是其中的核心内容。 我们的软件项目管理理…...

GB 2312字符集:中文编码的基石

title: GB 2312字符集:中文编码的基石 date: 2024/3/7 19:26:00 updated: 2024/3/7 19:26:00 tags: GB2312编码中文字符集双字节编码区位码规则兼容性问题存储空间优化文档处理应用 一、GB 2312字符集的背景 GB 2312字符集是中国国家标准委员会于1980年发布的一种…...

我的创作周年纪念日

机缘 最初成为创作者的初心:整理自己的知识体系,普及前端知识 实战项目中的经验分享日常工作学习过程中的记录通过文章进行技术交流归纳和整理自己的知识体系 收获 创作的过程中收获: 获得了909粉丝的关注获得了很多正向的反馈,…...

MySQL为什么要用B+树?

二叉树(二叉查找树) 平衡二叉树(B树就是B-树)(解决了二叉查找树的极端情况) Q:具体是怎么解决的呢? A: 树左右两边层数相差不大于1一旦符合条件1的时候,就进行左旋/右…...

今天分享一个好看的输入法皮肤相信每个人心里住着一个少女心我们美化一下她吧

标题: 白日梦皮肤上线,百度输入法助你开启梦幻之旅! 正文: 大家好呀!今天我来给大家安利一款超级梦幻的百度输入法皮肤——“白日梦”系列! 这款皮肤的设计灵感来源于我们内心深处的白日梦,充…...

力扣刷题Days11第二题--141. 环形链表(js)

目录 1,题目 2,代码 2.1快慢指针 2.2,哈希表 3,学习与总结 3.1自己尝试写快慢指针 反思 1,题目 给你一个链表的头节点 head ,判断链表中是否有环。 如果链表中有某个节点,可以通过连续跟踪 next 指针再次到达&…...

微信自动回复的设置

最近有客户来咨询,说是因为做内容引流到微信,所以每天很多人加他,每天要手动通过好友申请后打招呼,每天花费大量的时间去回答重复的问题,很机械的重复这些事。就问我们系统有没有能帮她解决这个烦恼的功能。 我说呀&a…...

SpringBoot整体概述)

SpringBoot源码解读与原理分析(一)SpringBoot整体概述

文章目录 第1章 SpringBoot整体概述1.1 Spring Framework1.1.1 Spring Framework的历史1.1.2 IOC与AOP 1.2 Spring Boot与Spring Framework1.3 Spring Boot的核心特性1.4 Spring Boot的体系 第1章 SpringBoot整体概述 Spring Framework 开发团队 支持不依赖外部容器的Web应用程…...

代码语义可视化架构的突破性实现:MultiHighlight如何将代码理解效率提升300%

代码语义可视化架构的突破性实现:MultiHighlight如何将代码理解效率提升300% 【免费下载链接】MultiHighlight Jetbrains IDE plugin: highlight identifiers with custom colors 🎨💡 项目地址: https://gitcode.com/gh_mirrors/mu/MultiH…...

Nodejs项目接入Taotoken统一大模型API的完整配置指南

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 Nodejs项目接入Taotoken统一大模型API的完整配置指南 1. 准备工作:获取API Key与模型ID 在开始编写代码之前ÿ…...

PPTist:5分钟创建专业演示文稿的免费开源在线PPT制作工具终极指南

PPTist:5分钟创建专业演示文稿的免费开源在线PPT制作工具终极指南 【免费下载链接】PPTist PowerPoint-ist(/pauəpɔintist/), An online presentation application that replicates most of the commonly used features of MS PowerPoint, …...

ECU软件刷写核心:拆解UDS的34/36/37服务,如何像拷贝文件一样传输数据?

ECU软件刷写核心:拆解UDS的34/36/37服务,如何像拷贝文件一样传输数据? 想象一下,你需要将一部高清电影从电脑传输到手机——这个过程需要稳定的连接、合理的分块大小和可靠的数据校验。在汽车电子领域,ECU软件刷写同样…...

LiveSplit速通计时器:5个核心功能提升你的游戏计时效率

LiveSplit速通计时器:5个核心功能提升你的游戏计时效率 【免费下载链接】LiveSplit A sleek, highly customizable timer for speedrunners. 项目地址: https://gitcode.com/gh_mirrors/li/LiveSplit LiveSplit是一款专为游戏速通玩家设计的专业计时器软件&a…...

【效率革命】PolyWindow插件:从多边形到精美窗户的3dMax一键生成秘籍

1. 为什么你需要PolyWindow插件? 如果你经常用3dMax做建筑可视化或室内设计,肯定遇到过这样的烦恼:项目里需要做几十个风格各异的窗户,每个都要手动建模、分格、赋材质,光是想到这个工作量就让人头皮发麻。我去年接的一…...

CANape实战:如何绕过CSMconfig识别问题,用VN5610A的Network模式连接ECAT ADMM模块

CANape高阶实战:绕过CSMconfig限制实现VN5610A与ECAT模块的Network模式直连 当工程师面对CSMconfig无法识别VN5610A网口的报错窗口时,往往会陷入传统配置路径的思维定式。这个看似简单的识别问题背后,实际上隐藏着新旧硬件架构更迭带来的工作…...

AI视频自动化生产:从LLM到MoviePy的全栈技术解析

1. 项目概述:一个能自动“印钞”的AI内容工厂最近在GitHub上看到一个挺有意思的项目,叫“MoneyPrinterAICreate”。光看名字就挺吸引人,直译过来就是“印钞机AI创作”。这可不是什么物理印钞机,而是一个利用人工智能技术ÿ…...

AWS实战|从零搭建高可用Web应用网络架构

1. 为什么需要高可用Web应用架构? 最近帮朋友公司迁移电商平台到AWS时,他们最担心的就是大促期间服务器挂掉。这让我想起三年前自己踩过的坑——当时用单可用区部署的官网,因为一次区域级故障直接宕机8小时。现在回头看,其实只要在…...

解密猫抓:当浏览器成为你的私人视频档案管理员

解密猫抓:当浏览器成为你的私人视频档案管理员 【免费下载链接】cat-catch 猫抓 浏览器资源嗅探扩展 / cat-catch Browser Resource Sniffing Extension 项目地址: https://gitcode.com/GitHub_Trending/ca/cat-catch 你是否曾盯着浏览器中那个精彩的在线讲座…...