【硬件工程师面经整理29_FPGA】

文章目录

- 1 nand nor的区别,速度差异的原因?

- 2 nand驱动方式?

- 3 异步信号处理方法

- 4 异步FIFO的深度是如何计算的

- 5 异步复位同步释放的优缺点

- 6 问了FPGA的内部组成?

- 7 LE中查找表的实现原理?

- 8 IOB的主要组成部分?

- 9 静态、动态时序模拟的优缺点。

- 10 CDC跨时钟域

- 11 全局时钟域与局部时钟的区别?

1 nand nor的区别,速度差异的原因?

逻辑门?/闪存?

闪存的话:

NAND Flash和NOR Flash的区别主要在于它们的存储结构不同。NAND Flash的存储单元是串联的,而NOR Flash的存储单元是并联的。因此,NAND Flash在写入和擦除大量数据时比NOR Flash快得多,两者相差近千倍;但是数据量小的时候,比如几个字节,NOR Flash比NAND Flash擦写速度快。

逻辑门的话:

NAND和NOR是逻辑门的两种基本类型,它们分别表示逻辑的“与非”和“或非”。其主要区别在于它们的逻辑输出和输入之间的关系。

NAND门输出在所有输入都是高电平时为低电平,其余情况为高电平。而NOR门输出在所有输入都是低电平时为高电平,其余情况为低电平。这意味着,在某些情况下,使用NAND门和使用NOR门可以达到相同的逻辑结果,但是它们的输入和输出布尔代数形式不同。

就速度而言,NAND门的速度通常比NOR门快,这是因为NAND门只需要在所有输入都为高电平时输出低电平,而NOR门则需要在所有输入都为低电平时输出高电平。由于CMOS技术通常使用pMOS和nMOS管来实现逻辑门,nMOS管的开关速度要比pMOS管快,因此,NAND门通常比NOR门快。

但是需要注意的是,不同的制造工艺和具体的电路设计可能会导致NAND门和NOR门的速度差异不同,具体速度还需要根据具体情况评估。

2 nand驱动方式?

NAND驱动方式指的是通过对NAND闸极上的电压进行调控来实现NAND Flash存储芯片的读写操作。具体来说,NAND闸极上的电压可以分为四个等级:弱擦除态、强擦除态、保持态和编程态。通过对这四个电压等级的控制,可以实现对NAND Flash存储芯片的读、写、擦除操作。

在读操作时,NAND闸极上的电压被控制为保持态,此时通过对NAND Flash的Word线和Bit线的控制,可以将对应的数据读出。在写操作时,NAND闸极上的电压被控制为编程态,此时通过对Word线和Bit线的控制,可以将待写入的数据写入到NAND Flash中。在擦除操作时,NAND闸极上的电压被控制为强擦除态或弱擦除态,此时通过对整个块的Word线和Bit线的控制,可以将整个块中的数据全部擦除。

NAND驱动方式相比于其他驱动方式具有较高的速度和较低的成本,因此在嵌入式系统中广泛应用。

3 异步信号处理方法

异步信号处理方法是一种在不依赖外部时钟信号的情况下,通过电路自身内部的时序控制来实现数据的处理和传输。常见的异步信号处理方法包括以下几种:

- 双稳态异步电路:这种电路由两个稳态组成,即“0”和“1”状态,可以通过输入信号的改变来实现电路状态的切换,从而实现数据的处理和传输。

- 请求-应答(Request-acknowledge)异步电路:这种电路包括两个部分,即请求端和应答端,请求端发出请求信号,应答端在收到请求信号后进行数据处理并返回应答信号,以完成数据的传输。

- 自校正异步电路:这种电路可以自动进行校正和同步,可以在电路运行时检测和修复错误,从而保证数据传输的可靠性和稳定性。

- 求和异步电路:这种电路可以对多个输入信号进行求和处理,并输出结果。

- 串行传输异步电路:这种电路通过将数据分割成若干个数据包,每个数据包由一个同步标志位和若干个数据位组成,通过发送方和接收方之间的协议来实现数据的传输。

在设计异步信号处理电路时,需要考虑电路的稳定性、功耗、延迟、噪声和误差等因素,以确保电路的性能和可靠性。同时,需要根据具体的应用场景选择合适的异步信号处理方法,并进行相应的优化和调试。

4 异步FIFO的深度是如何计算的

异步FIFO的深度可以通过以下公式计算:

Depth = ceil(log2(N))

其中,N表示异步FIFO的容量,ceil表示向上取整,log2表示以2为底的对数。

异步FIFO的深度与容量之间的关系是一个以2为底的对数函数,因此,当N的值增加一倍时,异步FIFO的深度也会增加1。例如,如果异步FIFO的容量为64字节,则深度为ceil(log2(64))=6。这意味着异步FIFO至少需要6个存储单元才能存储64字节的数据。

需要注意的是,在实际设计中,还需要考虑异步FIFO的读写时序和时钟域之间的异步信号同步等问题,以确保异步FIFO的正确性和可靠性

5 异步复位同步释放的优缺点

异步复位同步释放是指在电路中,当异步复位信号为低电平时,电路会被强制复位,而同步释放是指在时钟上升沿到来时,电路才会被释放。

优点:

- 可以快速、有效地将电路复位到初始状态,避免电路启动时出现未知状态;

- 确保所有信号在复位期间都被置于已知状态,提高了电路的可靠性和稳定性;

- 能够有效避免由于复位信号引起的时序问题,例如复位时序不正确导致的数据错位等问题。

缺点: - 在电路复位过程中,电路中的所有状态信息都被清除,可能会导致数据丢失或临时停机,从而影响系统性能;

- 复位信号本身需要进行正确的电路设计,例如引脚的防抖设计,以确保复位信号的可靠性和稳定性;

- 同步释放时需要添加同步电路,增加了电路复杂度和面积。

6 问了FPGA的内部组成?

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程来实现特定的数字电路功能。FPGA的内部主要由以下几个组成部分:

- 可编程逻辑单元(PLU):PLU是FPGA的主要构成部分,它包含大量的可编程逻辑门和寄存器,可以用于实现各种数字电路功能。PLU通常被组织成多个片区(Tile),每个片区包含多个逻辑单元。

- 输入/输出单元(IOB):IOB是FPGA的输入输出端口,用于与外部电路连接。IOB通常包含输入/输出缓存、电平转换器、时钟管理器等功能模块,可以用于实现不同的输入输出标准。

- 时钟管理单元(Clock Management Unit,CMU):CMU用于产生、分配和管理时钟信号,保证FPGA内部的所有逻辑单元能够按照指定的时序运行。CMU通常包括PLL、DLL、时钟分频器等模块。

- 存储单元:FPGA内部有多种类型的存储单元,包括片上存储器(Block RAM)、分布式存储器、寄存器等。这些存储单元可以用于存储数据、程序或配置信息等。

- 网络互连单元:FPGA内部有大量的互连资源,用于连接各个逻辑单元和存储单元。这些互连资源通常包括可编程的连线、交叉开关、路由器等,可以实现复杂的连接关系。

- 配置存储器:FPGA的配置存储器用于存储逻辑单元的编程信息,它通常包括Flash存储器、EEPROM存储器、SRAM存储器等。配置存储器中存储的编程信息可以决定FPGA内部的逻辑功能,使其实现特定的数字电路功能。

7 LE中查找表的实现原理?

在FPGA中,逻辑元素(LE)是构建数字逻辑电路的基本单元。每个LE由多个可编程逻辑单元(PLU)组成,其中每个PLU又由一个查找表(LUT)和一个触发器组成。LUT是一个小型存储器,用于将输入的布尔函数映射到输出。

查找表通常由一个或多个存储器单元组成。每个存储器单元都包含一个或多个比特,用于存储输入值和相应的输出值。在实际使用中,查找表的输入值会通过选择线路选择其中的一个存储器单元,以便查找表能够执行所需的逻辑操作。因此,LUT的输出结果是根据输入选择线路所选择的存储单元的内容而决定的。

在实际的数字电路中,查找表常常被用来实现逻辑函数。例如,一个3输入的查找表可以用来存储一个8比特的逻辑函数。这样,当输入信号变化时,LUT会通过选择线路选择正确的存储器单元,以便输出正确的逻辑值。

在FPGA中,LUT的大小通常是可编程的,可以根据需要配置。这使得FPGA非常灵活,能够适应各种不同的应用场景。

8 IOB的主要组成部分?

IOB(Input/Output Block)是FPGA中的一种特殊资源,主要用于处理输入/输出的电路资源,其中包括输入/输出引脚、输入/输出寄存器、时钟使能电路等。IOB的主要组成部分包括:

1.输入/输出引脚(I/O Pin):用于将FPGA芯片与外部电路连接,充当FPGA芯片与外部设备的接口。

2.输入/输出寄存器(I/O Register):用于在FPGA芯片与外部设备之间传输数据时进行数据的存储和调整,以达到数据格式转换、数据缓存、时序调整等功能。

3.时钟使能电路(Clock Enable Circuit):用于控制输入/输出寄存器中的时钟信号使能,以实现对输入/输出数据的有效性控制。

9 静态、动态时序模拟的优缺点。

静态时序模拟和动态时序模拟都是数字电路设计中常用的模拟方法,其优缺点如下:

静态时序模拟:静态时序模拟是指通过SPICE等电路仿真软件对电路进行分析和模拟,从而验证电路的时序性能。其主要优点是可以直观地观察电路的工作状态,方便进行设计和调试,且能够较准确地估算电路的时序参数。缺点是其模拟结果并不一定准确,因为它无法考虑电路中各元器件之间的相互影响和互动。

动态时序模拟:动态时序模拟是指通过Verilog等硬件描述语言对电路进行建模,并通过仿真器进行仿真,从而验证电路的时序性能。其主要优点是能够考虑电路中各元器件之间的相互影响和互动,模拟结果相对准确。缺点是相比于静态时序模拟,动态时序模拟对仿真器的要求较高,仿真时间较长,且不方便进行设计和调试。

总的来说,静态时序模拟适合于简单电路和快速验证电路的时序性能,而动态时序模拟适合于复杂电路和精确验证电路的时序性能。

10 CDC跨时钟域

CDC(Clock Domain Crossing)跨时钟域是指将数据信号从一个时钟域(源时钟域)传输到另一个时钟域(目标时钟域)的过程。由于不同的时钟域可能具有不同的时钟频率、时钟相位和时钟偏移等特性,因此数据在跨时钟域传输时可能会发生时序问题,例如数据错位、数据损失或数据错误等

解决方法包括:插入异步FIFO、插入同步FIFO、插入握手协议、其他技术:包括数据同步器、锁相环(PLL)等技术,都可以用来解决CDC跨时钟域问题。

【FIFO是“First-In-First-Out”的缩写,意思是“先进先出”。它是一种常见的数据结构,用于在电子系统中缓存数据并进行数据传输。FIFO通常是由一个读指针和一个写指针组成的,它们分别指向队列中的读和写位置。】

11 全局时钟域与局部时钟的区别?

在数字电路中,时钟信号是非常重要的,用来控制数字系统中各个时序电路的运行,保证数字电路的正确性和稳定性。时钟域就是在一个时钟信号下运行的时序电路的集合。

全局时钟域指的是在整个数字系统中共享同一个时钟信号的时序电路的集合,这个时钟信号通常来自于外部,如一个晶振或者时钟发生器。全局时钟域内的时序电路共享同一个时钟信号,时钟信号的频率和相位是相同的,因此,这些时序电路的运行时间是同步的,相互之间不存在时序差异,这样能够保证整个数字系统的正确性和稳定性。

局部时钟域则是指数字系统中在特定的电路区域内使用的时钟信号。由于局部时钟信号只在局部使用,不会和其他电路的时钟信号相互干扰,因此,局部时钟域内的时序电路的运行时间可以与其他电路的时序不同,即可以实现异步操作,但是,局部时钟域内的时序电路需要满足一些特殊的设计规则,以保证正确性和稳定性。

总之,全局时钟域和局部时钟域都是数字系统中重要的概念,对数字系统的设计和实现都有很大的影响。全局时钟域能够保证数字系统的同步性和稳定性,而局部时钟域则能够实现数字系统的异步操作,但需要注意时序设计规则。

注:

在本文中,我借鉴了互联网上的一些内容,以总结面试经验和技巧。这些内容旨在为读者提供实用的指导和参考。然而,由于个人经验和认知的局限性,本文的总结可能存在不准确或遗漏之处。因此,我真诚地欢迎读者朋友们提出宝贵的意见和建议,以帮助我改进和完善这些内容。

此外,有些知识点参考了其他博主,可能由于疏忽未注明出处。这些借鉴的部分旨在提供更多信息和观点,以丰富和完善文章的主题。在此,我对所借鉴的来源表示感谢。此外,为确保所引用的内容均符合版权规定,以维护知识产权和学术道德。若文中任何内容侵犯了您的合法权益,请相关权益人及时与我联系,我将立即进行核实并采取适当措施,包括但不限于删除相关内容或更新文章以消除影响。

相关文章:

【硬件工程师面经整理29_FPGA】

文章目录 1 nand nor的区别,速度差异的原因?2 nand驱动方式?3 异步信号处理方法4 异步FIFO的深度是如何计算的5 异步复位同步释放的优缺点6 问了FPGA的内部组成?7 LE中查找表的实现原理?8 IOB的主要组成部分࿱…...

Ping工作原理

文章目录 目的ping网络协议 OSIICMP什么是ICMP作用功能报文类型查询报文类型差错报文类型ICMP 在 IPv4 和 IPv6 的封装ICMP 在 IPv4 协议中的封装ICMP 在 IPv6 协议中的封装ICMP 头部日常ping 排除步骤ping 查询报文使用code扩展目的 本文主要是梳理ping的工作原理- 揭开 ICMP…...

python调用jar中java方法 静态类为例

java package test;public class test {// run方法返回当前脚本路径public static String runV1(String s) {return "log: " System.getProperty(s);}}python import jpype from jpype import * import osif __name__ "__main__":print(os.environ[JAV…...

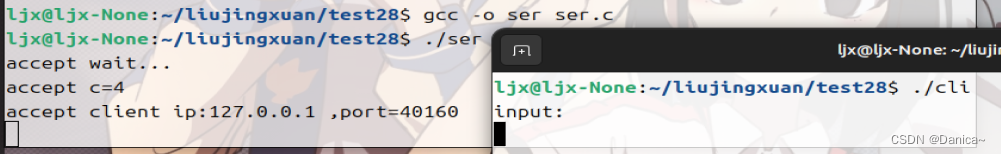

tcp服务器客户端通信(socket编程)

目录 1.编程流程 2.代码演示 2.1 服务器代码 2.2 客户端代码 3.注意 3.1 ping命令 3.2 netstat命令 3.3 为什么memset? 3.4 哪个会阻塞? 3.5 显示连接信息 1.概念 1.1 编程流程 1.2 connect与listen connect方法执行后,会进行三次握手,建立连…...

chatgpt 镜像站汇总

无需登录直接可用的: ChatGPT Web - GPT-3.5-16k免费使用,吐字块,每日20次数,不需要登陆思研AI - 免费时限制每小时6次提问https://chatgpt.nicelinks.site/ - 免费使用频次有限制抱歉,站点已暂停 - 免费由开发者提供A…...

java面试题:为什么 SQL 语句不要过多的 join?

1 考察点 面试官主要想了解面试者对于 SQL 优化的理解以及在实际工作中如何处理 SQL 语句的性能问题。要回答好这个问题,只需要了解 join 操作会带来哪些影响,而这些影响对程序产生什么样的影响就行了。这个问题就是面试官想考察我们是不是平日里善于积…...

JAVA实战开源项目:学生日常行为评分管理系统(Vue+SpringBoot)

目录 一、摘要1.1 项目介绍1.2 项目录屏 二、系统设计2.1 功能模块设计2.2.1 登录注册模块2.2.2 用户管理模块2.2.3 评分项目模块2.2.4 评分数据模块2.2.5 数据字典模块 2.3 可行性设计2.4 用例设计2.5 数据库设计2.5.1 整体 E-R 图2.5.2 用户2.5.3 评分项目2.5.4 评分数据2.5.…...

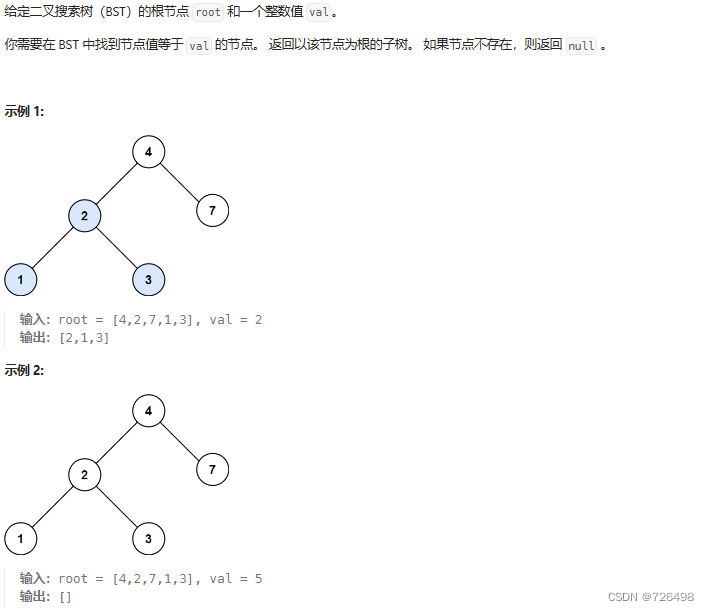

力扣-[700. 二叉搜索树中的搜索]

递归法 确定递归函数的参数和返回值 递归函数的参数传入的就是根节点和要搜索的数值,返回的就是以这个搜索数值所在的节点。 代码如下: public TreeNode searchBST(TreeNode root, int val) 确定终止条件 如果root为空,返回null,…...

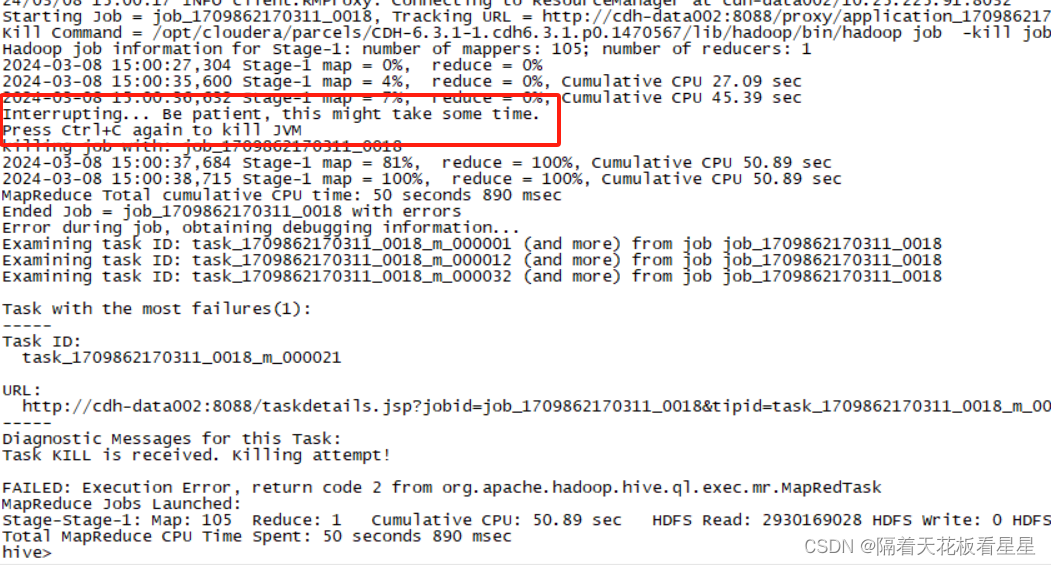

Hive-源码分析一条hql的执行过程

一、源码下载 下面是hive官方源码下载地址,我下载的是hive-3.1.3,那就一起来看下吧 https://dlcdn.apache.org/hive/hive-3.1.3/apache-hive-3.1.3-src.tar.gz 二、上下文 <Hive-源码带你看hive命令背后都做了什么>博客中已经讲到了hive命令执行…...

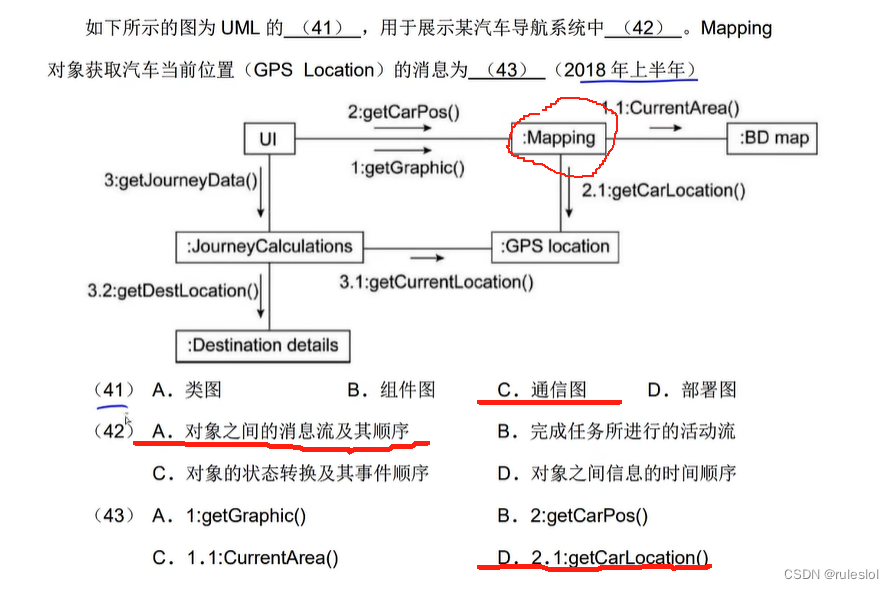

软考71-上午题-【面向对象技术2-UML】-UML中的图2

一、用例图 上午题,考的少;下午题,考的多。 1-1、用例图的定义 用例图展现了一组用例、参与者以及它们之间的关系。 用例图用于对系统的静态用例图进行建模。 可以用下列两种方式来使用用例图: 1、对系统的语境建模;…...

使用hashmap优化时间复杂度,leetcode1577

1577. 数的平方等于两数乘积的方法数 已解答 中等 相关标签 相关企业 提示 给你两个整数数组 nums1 和 nums2 ,请你返回根据以下规则形成的三元组的数目(类型 1 和类型 2 ): 类型 1:三元组 (i, j, k) ÿ…...

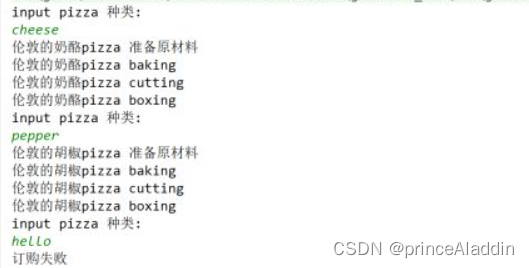

3、设计模式之工厂模式1

工厂模式是什么? 工厂模式是一种创建者模式,用于封装和管理对象的创建,屏蔽了大量的创建细节,根据抽象程度不同,主要分为简单工厂模式、工厂方法模式以及抽象工厂模式。 简单工厂模式 看一个具体的需求 看一个…...

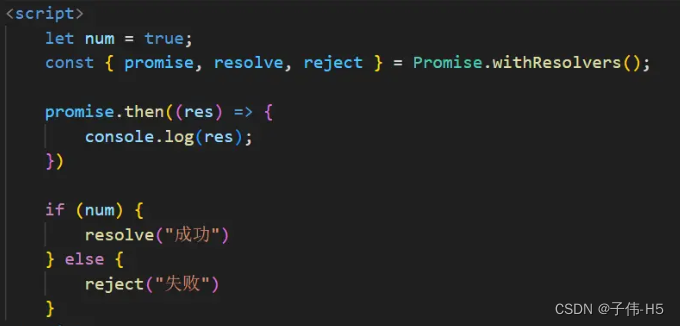

一个Promise全新API

1. 资讯速览 最近,Promise 新出了一个方法,已经进入 Stage 3 (候选阶段) ,相信很快就能达到 Stage 4 (完成阶段),并在项目中广泛使用。 这个方法就是 Promise.withResolvers。它是…...

【力扣hot100】刷题笔记Day25

前言 这几天搞工作处理数据真是类似我也,还被老板打电话push压力有点大的,还好搞的差不多了,明天再汇报,赶紧偷闲再刷几道题(可恶,被打破连更记录了)这几天刷的是动态规划,由于很成…...

webpack5零基础入门-4使用webpack处理less文件

1.安装less npm install less -D 2.创建less文件 .box{width: 100px;height: 100px;background: red; } 3.引入less文件并打包 执行npx webpack 报错无法识别less文件 4.安装less-loader并配置 npm install less-loader9 -D 这里指定一下版本不然会因为node版本过低报错 …...

Python机器学习预测+回归全家桶,新增TCN,BiTCN,TCN-GRU,BiTCN-BiGRU等组合模型预测...

截止到本期,一共发了4篇关于机器学习预测全家桶Python代码的文章。参考往期文章如下: 1.机器学习预测全家桶-Python,一次性搞定多/单特征输入,多/单步预测!最强模板! 2.机器学习预测全家桶-Pythonÿ…...

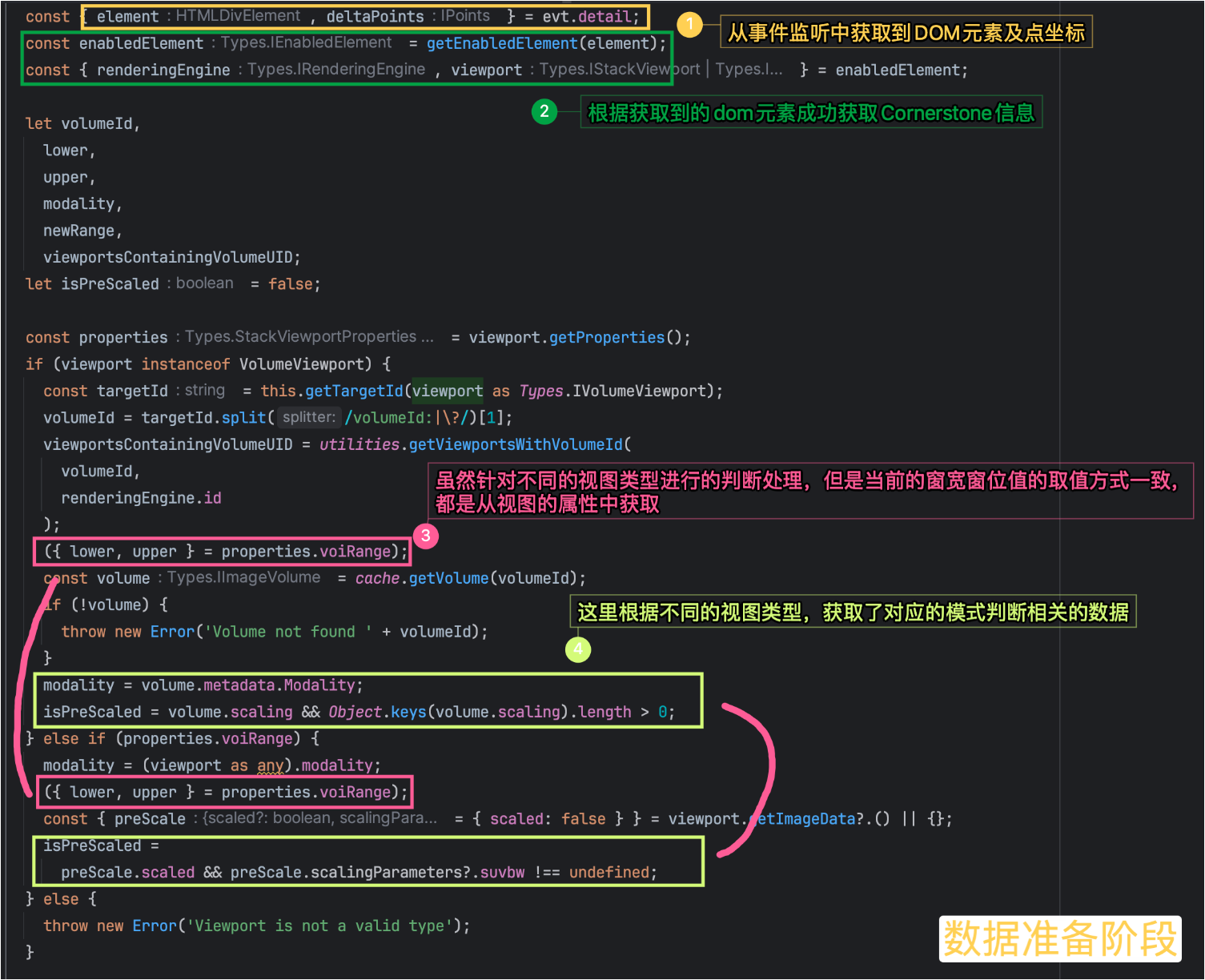

一文了解Cornerstone3D中窗宽窗位的3种设置场景及原理

🔆 引言 在使用Cornerstone3D渲染影像时,有一个常用功能“设置窗宽窗位(windowWidth&windowLevel)”,通过精确调整窗宽窗位,医生能够更清晰地区分各种组织,如区别软组织、骨骼、脑组织等。…...

部署 LVS(nginx)+keepalived高可用负载均衡集群

目录 一、集群的概述 1、什么是集群 2、普通集群与负载均衡集群 2.1 普通集群(Regular Cluster) 2.2 负载均衡集群(Load Balancing Cluster) 2.3 高可用集群(High Availability Cluster) 2.4 区别 …...

Qt/QML编程之路:fork、vfork、exec、clone的对比及使用(46)

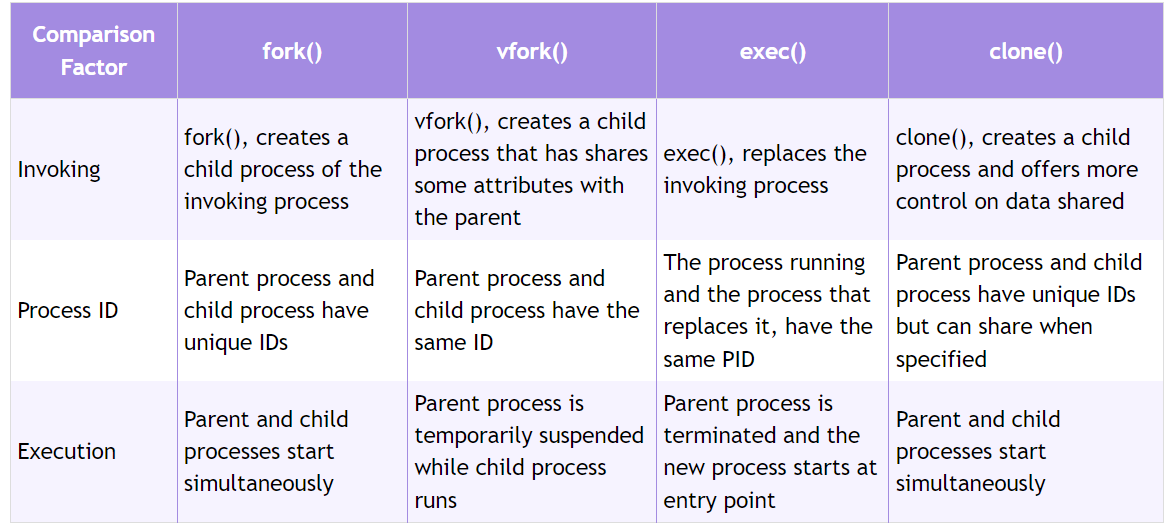

前言: 系统调用system call是OS提供的服务提供接口。系统调用fork()、vfork()、exec()和clone()都用于创建和操作进程。Linux下Qt编程也会用到vfork进行多进程间通信。让我们看一下以下每个系统调用的概述和比较: fork()、vfork()和clone()的工作原理相似,但在处…...

Go语言框架路由Controller控制器设计思路gin路由根据控制器目录分层生成路由地址

Controller设计好处 框架设计用controller分请求路由层级,应用从app目录开始对应请求url路由地址,这样设计师方便开发时候通过请求地址层级快速定位接口方法对应的代码位置。 例如api接口请求路径为:http://localhost:8110/busines…...

Figma中文插件:设计师必备的界面汉化神器,让设计效率提升50%

Figma中文插件:设计师必备的界面汉化神器,让设计效率提升50% 【免费下载链接】figmaCN 中文 Figma 插件,设计师人工翻译校验 项目地址: https://gitcode.com/gh_mirrors/fi/figmaCN 还在为Figma的英文界面而苦恼吗?FigmaCN…...

【FastAPI】Swagger UI 静态资源本地化部署:从CDN依赖到自给自足

1. 为什么需要本地化部署Swagger UI? 当你用FastAPI开发完一个接口服务,第一件事可能就是打开/docs页面测试接口。但有没有遇到过这种情况:公司内网服务器突然断网,Swagger页面变成空白;或是海外CDN加载缓慢ÿ…...

Hermes Agent vs OpenClaw:我花了一周对比,说说真实感受

先说结论Hermes Agent 的核心卖点是"会自己变聪明"——完成任务后会自动提炼技能、积累记忆,用得越久越好用。OpenClaw 的核心卖点是"生态大"——50 平台接入、13000 社区技能,开箱即用。两个都是 MIT 开源。选哪个,取决…...

靶场练习-BUUCTF-Misc 1~8

BUUCTF-Misc题单 1~8 BUUCTF-Misc 第一题 签到 题目描述:签到题 flag{buu_ctf} 工具:无 题目直接给出 取得flag flag为 flag{buu_ctf} 第二题 题目名字被ban了 题目描述:注意:得到的 flag 请包上 flag{} 提交 工具࿱…...

低空经济新蓝海:海事监测无人机技术全解析与应用展望

低空经济新蓝海:海事监测无人机技术全解析与应用展望 引言 大家好!随着“低空经济”被正式列为国家战略性新兴产业,无人机技术的应用版图正以前所未有的速度从我们熟悉的陆地,向更为广阔的海洋延伸。在这片“新蓝海”中࿰…...

OpenClaw多模态探索:Qwen3-14b_int4_awq解析截图内容

OpenClaw多模态探索:Qwen3-14b_int4_awq解析截图内容 1. 为什么需要截图解析能力 上周我在整理项目文档时遇到一个典型场景:需要将十几个软件界面的操作步骤整理成图文教程。传统做法是手动截图后,用OCR识别文字再人工编写说明——这个过程…...

亲测有效!雪女-斗罗大陆-造相Z-Turbo生成角色细节展示:服装、发型、神态都很到位

亲测有效!雪女-斗罗大陆-造相Z-Turbo生成角色细节展示:服装、发型、神态都很到位 作为一名长期关注AI绘画技术的创作者,我最近深度体验了"雪女-斗罗大陆-造相Z-Turbo"这款专为《斗罗大陆》风格角色设计的文生图模型。经过上百次生…...

LangChain重构多Skill Agent系统:智能工具集成实战

LangChain*重构的完整多Skill Agent系统 目录 LangChain*重构的完整多Skill Agent系统 一、LangChain 版本优势 二、完整可运行代码 三、各部分作用解释 1. 工具定义(`@tool` 装饰器) 2. 提示词模板(`ChatPromptTemplate`) 3. Agent 创建与执行器 4. 工具内部调用 LLM(`s…...

Swoole 5.0适配踩坑实录,深度解析协程生命周期变更、内存管理新规与RPC协议不兼容问题

第一章:Swoole 5.0升级适配全景概览Swoole 5.0 是一次面向现代化 PHP 协程生态的重大演进,彻底移除对传统同步阻塞 API 的兼容包袱,全面拥抱协程原生化设计。其核心变化涵盖事件循环重构、协程调度器强化、HTTP/Server 接口标准化,…...

C#/.NET/.NET Core优秀项目和框架2026年3月简报

前言 公众号每月定期推广和分享的C#/.NET/.NET Core优秀项目和框架(每周至少会推荐两个优秀的项目和框架当然节假日除外),公众号推文中有项目和框架的详细介绍、功能特点、使用方式以及部分功能截图等(打不开或者打开GitHub很慢的…...