Verilog 学习第八节(数码管段码显示)

共阴极数码管:低电平端接的都是0,高电平端哪里设置为1 ,哪里就亮~

共阳极数码管与之相反~

视觉暂留:

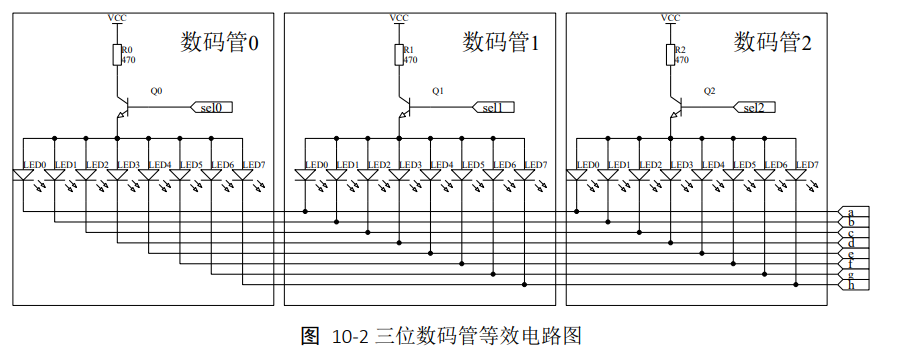

对于三位的共阴极数码管

第0.01s:让数码管0的a段亮,其他数码管全灭

Sel0为高电平,sel1和sel2为低电平

A段为低电平

第0.02s:让数码管1的b、c段亮,其他数码管全灭

Sel1为高电平,sel0和sel2为低电平

B和C段为低电平

第0.03s:让数码管2的e段亮,其他数码管全灭

Sel2为高电平,sel0和sel1为低电平

E段为低电平

数码管动态扫描

所以,通过这种方式,可以节约引脚~

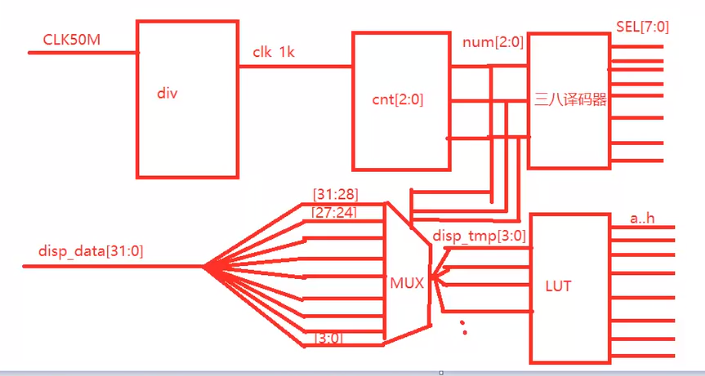

抽象原理图:

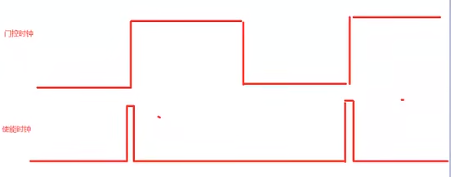

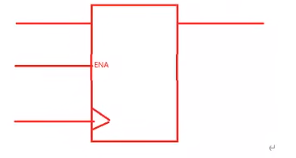

在fpga设计中尽量使用使能时钟去驱动寄存器,而不是门控时钟,因为门控时钟的质量非常差

使用门控时钟,将门控时钟直接作为DFF的工作时钟,没有ENA的情况下忽略ENA

使用使能时钟的情况,DFF的工作时钟继续全局高质量时钟,而将使能时钟作为DFF的使能信号使用

在能使用时序逻辑的情况下,尽量使用时序逻辑

顶层模块:

module hex8_test(input Clk,input Reset,output [7:0]SEL,output [7:0]SEG);wire [31:0]Disp_Data;hex8_2 hex8_2(Clk,Reset,Disp_Data,SEL,SEG);assign Disp_Data=32'h12359bdf;endmodule主模块

module hex8(input Clk,input Reset,input [31:0]Disp_Data,output reg [7:0]SEL,output reg [7:0]SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);reg clk_1k;reg [14:0]div_cnt;always@(posedge Clk or negedge Reset)beginif(!Reset)div_cnt<=0;else if(div_cnt>=25000-1)div_cnt<=0;elsediv_cnt<=div_cnt+1;endalways@(posedge Clk or negedge Reset)beginif(!Reset)clk_1k<=0;else if(div_cnt>=25000-1)clk_1k<=~clk_1k;endreg[2:0]reg_num;always@(posedge clk_1k or negedge Reset)beginif(!Reset)reg_num<=0;else if(reg_num>=7)reg_num<=0;elsereg_num<=reg_num+1;endalways@(*)begincase(reg_num)0:SEL=8'b0000_0001;1:SEL=8'b0000_0010;2:SEL=8'b0000_0100;3:SEL=8'b0000_1000;4:SEL=8'b0001_0000;5:SEL=8'b0010_0000;6:SEL=8'b0100_0000;7:SEL=8'b1000_0000;endcaseendreg[3:0] disp_temp;always@(*)begincase(reg_num)7:disp_temp=Disp_Data[31:28];6:disp_temp=Disp_Data[27:24];5:disp_temp=Disp_Data[23:20];4:disp_temp=Disp_Data[19:16];3:disp_temp=Disp_Data[15:12];2:disp_temp=Disp_Data[11:8];1:disp_temp=Disp_Data[7:4];0:disp_temp=Disp_Data[3:0];endcaseendalways@(*)begincase(disp_temp)0:SEG=8'hc0;1:SEG=8'hf9;2:SEG=8'ha4;3:SEG=8'hb0;4:SEG=8'h99;5:SEG=8'h92;6:SEG=8'h82;7:SEG=8'hf8;8:SEG=8'h80;9:SEG=8'h90;4'ha:SEG=8'h88;4'hb:SEG=8'h83;4'hc:SEG=8'hc6;4'hd:SEG=8'ha1;4'he:SEG=8'h86;4'hf:SEG=8'h8e;endcaseend

endmodule

改进后的主模块

module hex8_2(input Clk,input Reset,input [31:0]Disp_Data,output reg [7:0]SEL,output reg [7:0]SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);reg clk_1k;reg [15:0]div_cnt;always@(posedge Clk or negedge Reset)beginif(!Reset)div_cnt<=0;else if(div_cnt>=50000-1)div_cnt<=0;elsediv_cnt<=div_cnt+1;endalways@(posedge Clk or negedge Reset)beginif(!Reset)clk_1k<=0;else if(div_cnt>=50000-1)clk_1k<=1;elseclk_1k<=0;endreg[2:0]reg_num;always@(posedge Clk or negedge Reset)beginif(!Reset)reg_num<=0;else if(clk_1k)reg_num<=reg_num+1;elsereg_num<=reg_num;endalways@(posedge Clk)begincase(reg_num)7:SEL=8'b0000_0001;6:SEL=8'b0000_0010;5:SEL=8'b0000_0100;4:SEL=8'b0000_1000;3:SEL=8'b0001_0000;2:SEL=8'b0010_0000;1:SEL=8'b0100_0000;0:SEL=8'b1000_0000;endcaseendreg[3:0] disp_temp;always@(posedge Clk)begincase(reg_num)0:disp_temp=Disp_Data[31:28];1:disp_temp=Disp_Data[27:24];2:disp_temp=Disp_Data[23:20];3:disp_temp=Disp_Data[19:16];4:disp_temp=Disp_Data[15:12];5:disp_temp=Disp_Data[11:8];6:disp_temp=Disp_Data[7:4];7:disp_temp=Disp_Data[3:0];endcaseendalways@(posedge Clk)begincase(disp_temp)0:SEG=8'hc0;1:SEG=8'hf9;2:SEG=8'ha4;3:SEG=8'hb0;4:SEG=8'h99;5:SEG=8'h92;6:SEG=8'h82;7:SEG=8'hf8;8:SEG=8'h80;9:SEG=8'h90;4'ha:SEG=8'h88;4'hb:SEG=8'h83;4'hc:SEG=8'hc6;4'hd:SEG=8'ha1;4'he:SEG=8'h86;4'hf:SEG=8'h8e;endcaseend

endmodule测试模块

`timescale 1ns / 1psmodule hex8_tb();reg Clk;reg Reset;reg [31:0]Disp_Data;wire [7:0]SEL;wire [7:0]SEG;hex8 hex8(Clk,Reset,Disp_Data,SEL,SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);initial Clk=0;always#10 Clk=!Clk;initial beginReset=0;Disp_Data=32'h0000_0000;#201Reset=1;#2000Disp_Data=32'h1234_5678;#10000000Disp_Data=32'h9abc_def0;#10000000$stop;end

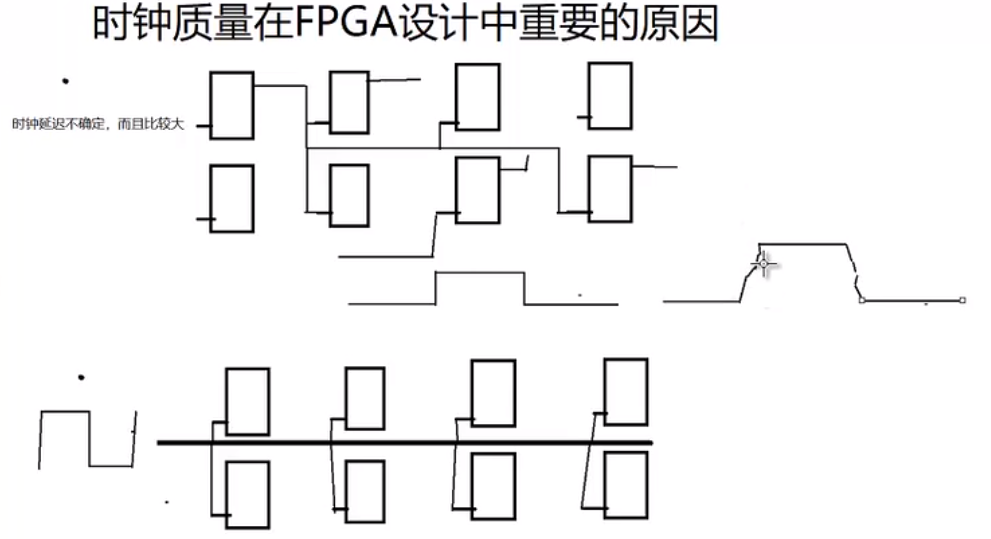

endmodule时钟质量在FPGA设计中重要的原因

1:时钟延迟不确定,而且比较大

2:使得时钟的波形变差

3:驱动能力

相关文章:

Verilog 学习第八节(数码管段码显示)

共阴极数码管:低电平端接的都是0,高电平端哪里设置为1 ,哪里就亮~ 共阳极数码管与之相反~ 视觉暂留: 对于三位的共阴极数码管 第0.01s:让数码管0的a段亮,其他数码管全灭 Sel0为高电平,sel1和sel…...

方案开发|快递吊钩电子秤方案

物流的发展为我们提供了生活的便利,足不出户仍可以感受天南地北的美食的特产,在现在这个时代已经是现实并发展成为常态的事情了。在物流发展的每一个环节中,吊钩电子秤也是它必不可缺的一环。人们在寄出物品前需要通过吊钩电子秤称量过重量&a…...

Spring-IOC容器初始化过程

Spring IOC容器的初始化过程:Resource定位,BeanDefinition载入,向IOC容器注册BeanDefinition。整个过程由refresh()方法触发,三个过程由不同的模块完成,使用户更加灵活的对这三个过程剪裁和扩展。 BeanDefinition 就是POJO对象在IOC容器中的抽象。通过BeanDefinition 这个…...

AspCms标签手册

网站通用标签{aspcms:sitepath} 网站终极目录(可放在二级目录,其它语言则在三级目录){aspcms:languagepath} 语言目录{aspcms:siteurl} 网站地址{aspcms:sitelogo} LOGO地址{aspcms:sitetitle} 网站标题{aspcms:additiontitle} 网站附加标题{aspcms:sitekeywords} 网站关键词{a…...

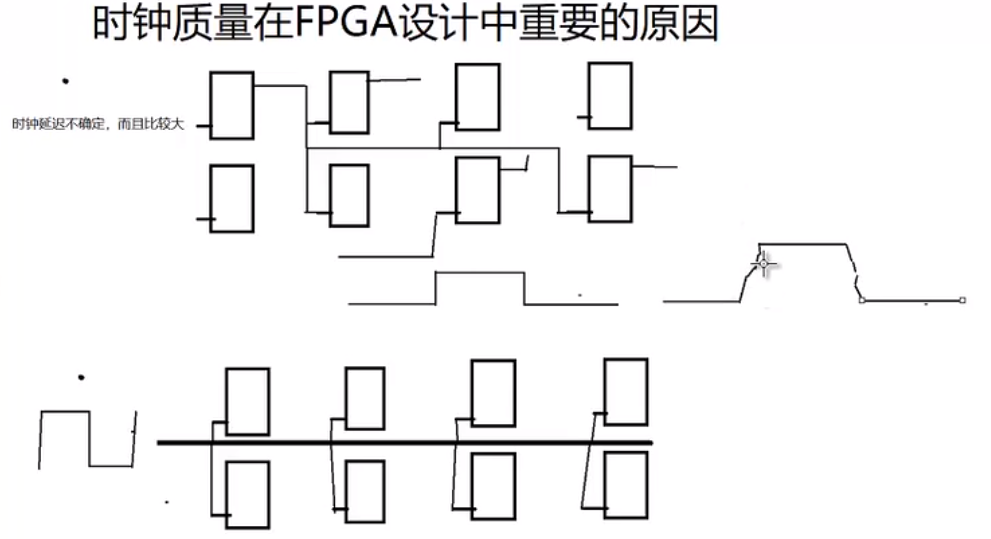

什么是Netty

一.Netty介绍 1.什么是netty Netty 是由 JBOSS 提供的一个 Java 开源框架。Netty 提供异步的、基于事件驱动的网络应用程序框架,用以快速开发高性能、高可靠性的网络 IO 程序,是目前最流行的 NIO 框架,Netty 在互联网领域、大数据分布式计算…...

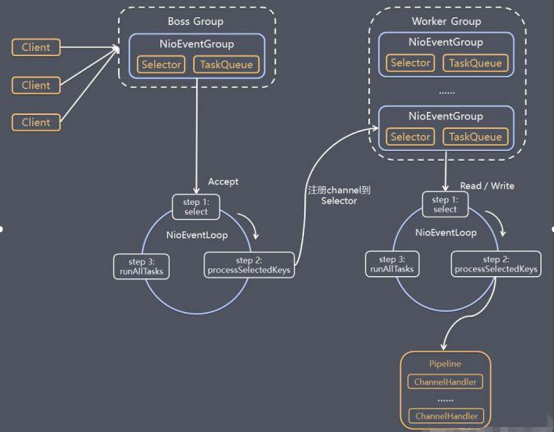

SpringCloud:统一网关Gateway

目录 1、网关介绍 2、搭建网关服务 3、路由断言工厂 4、路由过滤器 5、全局过滤器GlobalFilter 6、过滤器执行顺序 7、跨域问题处理 1、网关介绍 网关(Gateway)又称网间连接器、协议转换器。网关在网络层以上实现网络互连,是复杂的网络互 连设备࿰…...

)

【独家】华为OD机试 - 最差产品奖(C 语言解题)

最近更新的博客 华为od 2023 | 什么是华为od,od 薪资待遇,od机试题清单华为OD机试真题大全,用 Python 解华为机试题 | 机试宝典【华为OD机试】全流程解析+经验分享,题型分享,防作弊指南)华为od机试,独家整理 已参加机试人员的实战技巧文章目录 最近更新的博客使用说明本期…...

力扣解法汇总1599. 经营摩天轮的最大利润

目录链接: 力扣编程题-解法汇总_分享记录-CSDN博客 GitHub同步刷题项目: https://github.com/September26/java-algorithms 原题链接:力扣 描述: 你正在经营一座摩天轮,该摩天轮共有 4 个座舱 ,每个座舱…...

MySQL-常见的五种索引

什么是索引? 百度百科:在关系数据库中,索引是一种单独的、物理的对数据库表中一列或多列的值进行排序的一种存储结构,它是某个表中一列或若干列值的集合和相应的指向表中物理标识这些值的数据页的逻辑指针清单。索引的作用相当于…...

Linux学习第二十三节-压缩和解压缩和tar打包工具

1.压缩与解压缩(不常用)①Linux独有压缩格式及命令工具: gzip---> .gz bzip2---> .bz2 xz---> .xz②压缩命令格式: 压缩命令:gzip [选项] 文件名 常用选项:-d 解压缩 压缩命令:bzip2 [选项] 文件名…...

没有钱怎么创业?一分钱没有如何能创业成功?

限制人创业成功的从来都不是资金,而是能力,这个道理很多人都可能不懂,多数人习惯了庸庸碌碌、日复一日地打工行为,却不知如何创业,那么,没有钱怎么创业?一分钱没有如何能创业成功呢?…...

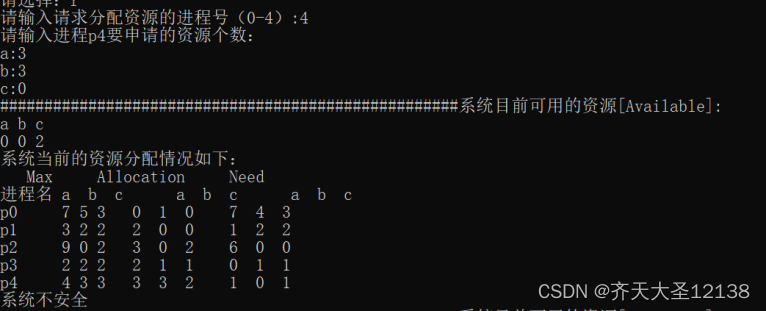

【操作系统原理实验】银行家算法模拟实现

选择一种高级语言如C/C等,编写一个银行家算法的模拟实现程序。1) 设计相关数据结构;2) 实现系统资源状态查看、资源请求的输入等模块;3) 实现资源的预分配及确认或回滚程序;4) 实现系统状态安全检查程序;5) 组装各模块…...

java医院云HIS系统:融合B/S版电子病历系统 能与公卫、PACS等各类外部系统融合

医院HIS系统源码 云HIS系统源码:SaaS运维平台完整文档 有源码,有演示 java基层医院云his系统 融合B/S版电子病历系统,支持电子病历4级 拥有自主知识产权。 看演示及源码可私信我哦! 一、系统概述 一款满足二甲医院、基层医疗机构…...

单线激光雷达(SICK)驱动安装及时空标定

一、引言 1、AGV需要同时具备定位、避障与导航的功能,其中避障对于雷达本身的分辨率、精度要求并不是很高,只需要能够根据预设定的雷达扫描范围准确避开障碍物即可,故本文以TIM240(SICK激光类雷达)为例介绍实现多雷达…...

Java IO流

Java IO流 文章目录Java IO流什么是IO流InputStreamFlieInputStream示例OutputStream示例字符的读取与写入READER方法WRITER方法利用Scanner和PrintWriter简化字符的读写ScannerPrintWriter什么是IO流 前面我们介绍了Java中对文件的操作以及file类的了解,但是file类…...

LeetCode - 1653 使字符串平衡的最少删除次数

目录 题目来源 题目描述 示例 提示 题目解析 算法源码 题目来源 1653. 使字符串平衡的最少删除次数 - 力扣(LeetCode) 题目描述 给你一个字符串 s ,它仅包含字符 a 和 b 。 你可以删除 s 中任意数目的字符,使得 …...

【微信小程序】-- 页面事件 - 上拉触底 - 案例(二十七)

💌 所属专栏:【微信小程序开发教程】 😀 作 者:我是夜阑的狗🐶 🚀 个人简介:一个正在努力学技术的CV工程师,专注基础和实战分享 ,欢迎咨询! &…...

)

《超导电子技术及其应用》学习日志(二)

约瑟夫森效应 约瑟夫森理论 约瑟夫森方程 (1)每一个库柏对都可视为质量为2m、电量为2e的复合载流子,定向运动速度v就是库柏相对质心的速度。处于超导态的库柏对凝聚于同一量子态,运载电流时具有完全相同的动量P。用微观波函数来…...

微信小程序this指向问题

前言 最近在开发微信小程序时不时会遇到一个很奇怪的问题,有些情况下用 this.setData 可以改变视图显示,有些情况下使用 this.setData 无效,这又是为什么呢? 问题描述 在解释这个问题前,我们先来看两段代码࿱…...

【报错】paddle相关报错和处理方法

1 报错 😱😱😱 ModuleNotFoundError: No module named paddle 2 解决方法 💉💉💉 pip --default-timeout=100 install paddlepaddle -i http://pypi.douban.com/simple --trusted-host pypi.douban.com 🎉🎉🎉🎉🎉🎉 1 报错 😱😱😱 from paddl…...

构建AI助手持久记忆系统:Rekall项目实践与MCP协议应用

1. 项目概述:为你的AI助手构建一个“第二大脑”如果你和我一样,日常重度依赖 Claude Code、Cursor 这类AI编程助手,那你一定遇到过这个痛点:每次开启一个新的会话,AI助手就像得了“健忘症”,对之前讨论过的…...

Windows平台即时通讯消息保留技术深度解析:RevokeMsgPatcher企业级解决方案完全手册

Windows平台即时通讯消息保留技术深度解析:RevokeMsgPatcher企业级解决方案完全手册 【免费下载链接】RevokeMsgPatcher :trollface: A hex editor for WeChat/QQ/TIM - PC版微信/QQ/TIM防撤回补丁(我已经看到了,撤回也没用了) …...

计算机视觉导航评估框架:从算法指标到用户体验的完整闭环

1. 项目概述:为什么我们需要一个“导航评估框架”?在计算机视觉辅助视障人士导航这个领域,我见过太多“实验室里的英雄”和“现实中的矮子”。一个算法在精心布置的走廊里识别障碍物准确率高达99.9%,但一到人潮涌动的火车站广场&a…...

5个让你在Windows电脑上畅玩安卓应用的神奇场景

5个让你在Windows电脑上畅玩安卓应用的神奇场景 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否曾想过,在Windows电脑的大屏幕上玩手机游戏ÿ…...

RedwoodJS熔断器:构建高可用应用的熔断机制与故障隔离终极指南 [特殊字符]

RedwoodJS熔断器:构建高可用应用的熔断机制与故障隔离终极指南 🔧 【免费下载链接】redwood RedwoodGraphQL 项目地址: https://gitcode.com/gh_mirrors/re/redwood 在当今微服务架构盛行的时代,应用的高可用性成为了开发者的首要关注…...

Flutter + 开源鸿蒙实战 | 极简记账本 Day1:项目初始化 + 底部导航框架搭建

🔥 Flutter 开源鸿蒙实战 | 极简记账本 Day1:项目初始化 底部导航框架搭建欢迎加入开源鸿蒙跨平台社区:https://openharmonycrossplatform.csdn.net 系列项目:极简记账本(6 天完结)环境:Flutt…...

)

别再折腾Windows了!用Mac或Linux搞定ACM LaTeX模板的字体难题(附保姆级配置流程)

跨平台LaTeX写作:为什么macOS和Linux是ACM模板的最佳选择 第一次接触ACM LaTeX模板的研究人员,往往会在字体兼容性问题上耗费大量时间——特别是Windows用户。当你反复尝试安装Libertine字体、解决各种编译错误时,是否想过问题可能出在操作系…...

如何快速解决Funannotate数据库安装失败:终极完整指南

如何快速解决Funannotate数据库安装失败:终极完整指南 【免费下载链接】funannotate Eukaryotic Genome Annotation Pipeline 项目地址: https://gitcode.com/gh_mirrors/fu/funannotate Funannotate作为一款强大的真核生物基因组注释流程工具,其…...

PiliPlus:如何用第三方B站客户端解锁终极观影体验?

PiliPlus:如何用第三方B站客户端解锁终极观影体验? 【免费下载链接】PiliPlus PiliPlus 项目地址: https://gitcode.com/gh_mirrors/pi/PiliPlus 你是否厌倦了官方B站客户端的广告轰炸?是否想要更纯净、更流畅的观影体验?P…...

现代Web应用特性管理:从概念到工程实践

1. 项目概述:一个面向现代Web开发的特性管理工具 如果你和我一样,长期在Web应用开发的一线摸爬滚打,那你一定对“特性开关”这个概念不陌生。简单来说,它就像你家里电灯的总闸,可以随时控制某个功能是“亮”还是“灭”…...