XILINX 10G PCS PMA IP核使用

文章目录

- 一、设计框图

- 二、模块设计

- 三、IP核配置

- 四、上板验证

- 五、总结

一、设计框图

关于GT高速接口的设计一贯作风,万兆以太网同样如此,只不过这里将复位逻辑和时钟逻辑放到了同一个文件ten_gig_eth_pcs_pma_0_shared_clock_and_reset当中。如果是从第一篇高速接口设计看到现在,应该很熟悉了。

二、模块设计

ten_gig_eth_pcs_pma_0_shared_clock_and_reset模块将输入的用户复位信号i_rst进行同步然后产生相应的复位信号给到IP核,同时也根据IP核输出的txoutclk产生一系列用户时钟,与之前的高速接口设计不同的是,万兆以太网的用户时钟不再是txusrclk2,而是coreclk。

module TEN_GIG_ETH_PCSPMA(input i_gt_refclk ,input i_sys_clk ,input i_rst ,input i_qplllock ,input i_qplloutclk ,input i_qplloutrefclk ,output o_qpllreset ,output txp ,output txn ,input rxp ,input rxn ,input i_sim_speedup_control ,output o_xgmii_clk , input [63 : 0] i_xgmii_txd ,input [7 : 0] i_xgmii_txc ,output [63 : 0] o_xgmii_rxd ,output [7 : 0] o_xgmii_rxc ,output o_block_sync ,output o_rst_done ,output o_pma_link ,output o_pcs_rx_link ,output o_tx_disable

);wire coreclk ;

wire txusrclk ;

wire txusrclk2 ;

wire txoutclk ;

wire areset_coreclk ;

wire gttxreset ;

wire gtrxreset ;

wire txuserrdy ;

wire reset_counter_done ;

(* MARK_DEBUG = "TRUE" *)wire tx_resetdone ;

(* MARK_DEBUG = "TRUE" *)wire rx_resetdone ;wire [7 :0] core_status ;

wire [447:0] status_vector ;

wire [535:0] configuration_vector ;

wire drp_req ;assign o_xgmii_clk = coreclk;

assign o_block_sync = core_status[0];

assign o_rst_done = tx_resetdone & rx_resetdone;

assign o_pma_link = status_vector[18];

assign o_pcs_rx_link = status_vector[226];

assign configuration_vector[399:384] = 16'h4C4B;

assign configuration_vector[535:400] = 136'd0;

assign configuration_vector[383:1] = 384'd0;

assign configuration_vector[0:0] = 0;//PMA LOOPBACKten_gig_eth_pcs_pma_0_shared_clock_and_reset ten_gig_eth_pcs_pma_shared_clock_reset_block

(.areset (i_rst ),.refclk (i_gt_refclk ),.coreclk (coreclk ),.txoutclk (txoutclk ),.qplllock (i_qplllock ),.areset_coreclk (areset_coreclk ),.gttxreset (gttxreset ),.gtrxreset (gtrxreset ),.txuserrdy (txuserrdy ),.txusrclk (txusrclk ),.txusrclk2 (txusrclk2 ),.qpllreset (o_qpllreset ),.reset_counter_done (reset_counter_done )

);ten_gig_eth_pcs_pma_0 ten_gig_eth_pcs_pma_u0 (.rxrecclk_out ( ), // output wire rxrecclk_out.coreclk (coreclk ), // input wire coreclk.dclk (i_sys_clk ), // input wire dclk.txusrclk (txusrclk ), // input wire txusrclk.txusrclk2 (txusrclk2 ), // input wire txusrclk2.areset (i_rst ), // input wire areset.txoutclk (txoutclk ), // output wire txoutclk.areset_coreclk (areset_coreclk ), // input wire areset_coreclk.gttxreset (gttxreset ), // input wire gttxreset.gtrxreset (gtrxreset ), // input wire gtrxreset.txuserrdy (txuserrdy ), // input wire txuserrdy.qplllock (i_qplllock ), // input wire qplllock.qplloutclk (i_qplloutclk ), // input wire qplloutclk.qplloutrefclk (i_qplloutrefclk ), // input wire qplloutrefclk.reset_counter_done (reset_counter_done ), // input wire reset_counter_done.txp (txp ), // output wire txp.txn (txn ), // output wire txn.rxp (rxp ), // input wire rxp.rxn (rxn ), // input wire rxn.sim_speedup_control (i_sim_speedup_control ), // input wire sim_speedup_control.xgmii_txd (i_xgmii_txd ), // input wire [63 : 0] xgmii_txd.xgmii_txc (i_xgmii_txc ), // input wire [7 : 0] xgmii_txc.xgmii_rxd (o_xgmii_rxd ), // output wire [63 : 0] xgmii_rxd.xgmii_rxc (o_xgmii_rxc ), // output wire [7 : 0] xgmii_rxc.configuration_vector (configuration_vector ), // input wire [535 : 0] configuration_vector.status_vector (status_vector ), // output wire [447 : 0] status_vector.core_status (core_status ), // output wire [7 : 0] core_status.tx_resetdone (tx_resetdone ), // output wire tx_resetdone.rx_resetdone (rx_resetdone ), // output wire rx_resetdone.signal_detect (1 ), // input wire signal_detect.tx_fault (0 ), // input wire tx_fault.drp_req (drp_req ), // output wire drp_req.drp_gnt (drp_req ), // input wire drp_gnt.drp_den_o ( ), // output wire drp_den_o.drp_dwe_o ( ), // output wire drp_dwe_o.drp_daddr_o ( ), // output wire [15 : 0] drp_daddr_o.drp_di_o ( ), // output wire [15 : 0] drp_di_o.drp_drdy_o ( ), // output wire drp_drdy_o.drp_drpdo_o ( ), // output wire [15 : 0] drp_drpdo_o.drp_den_i (0 ), // input wire drp_den_i.drp_dwe_i (0 ), // input wire drp_dwe_i.drp_daddr_i (0 ), // input wire [15 : 0] drp_daddr_i.drp_di_i (0 ), // input wire [15 : 0] drp_di_i.drp_drdy_i (0 ), // input wire drp_drdy_i.drp_drpdo_i (0 ), // input wire [15 : 0] drp_drpdo_i.tx_disable (o_tx_disable ), // output wire tx_disable.pma_pmd_type (3'b101 ) // input wire [2 : 0] pma_pmd_type

);endmodule

三、IP核配置

整个IP核配置页面和使用都非常简单。难点在于后续基于此IP核进行万兆以太网MAC层的设计,该部分内容将在后续更新。

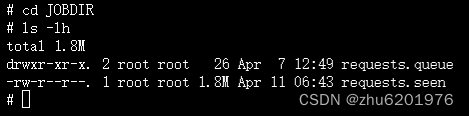

四、上板验证

这里写的用户逻辑很简单,我们不做关注,后续会进行完整的设计,这里主要看主机网卡发送过来的数据是否正常。

大家需要准备一张万兆网卡,与FPGA进行连接。

五、总结

初步打通了万兆以太网高速接口,后续将基于此进行完整的MAC层设计。

相关文章:

XILINX 10G PCS PMA IP核使用

文章目录 一、设计框图二、模块设计三、IP核配置四、上板验证五、总结 一、设计框图 关于GT高速接口的设计一贯作风,万兆以太网同样如此,只不过这里将复位逻辑和时钟逻辑放到了同一个文件ten_gig_eth_pcs_pma_0_shared_clock_and_reset当中。如果是从第…...

Scrapy框架内存泄漏问题及解决

说明:仅供学习使用,请勿用于非法用途,若有侵权,请联系博主删除 作者:zhu6201976 一、问题背景及原因 官方文档:Debugging memory leaks — Scrapy 2.11.1 documentation Scrapy是一款功能强大的网络爬虫框…...

app 创建快捷入口 在手机上面多个icon

activity-alias详解及应用-CSDN博客 Android动态修改应用图标最佳实践 - 简书 AndroidManifest.xml 中 <activity-aliasandroid:name"包名.ui.mine.SecondActivityAlias"android:label"快捷入口"android:icon"mipmap/collection_one"andro…...

【网安小白成长之路】6.pkachu、sql-lbas、upload-lbas靶场搭建

🐮博主syst1m 带你 acquire knowledge! ✨博客首页——syst1m的博客💘 🔞 《网安小白成长之路(我要变成大佬😎!!)》真实小白学习历程,手把手带你一起从入门到入狱🚭 &…...

vue 项目中添加DES加密

vue 项目中添加DES加密 由于现在项目使用http协议,且登录界面是明文传输,项目真正上线后基本的密码传输都很不安全。 决定用前端框架加密后再进行传输,以提高密码传输过程中的安全性。 crypto-js 是一个流行的 JavaScript 加密库࿰…...

【记录问题】如何测试虚拟机已经可以连接网络

如何测试虚拟机已经可以连接网络 要测试虚拟机是否已经连接网络,可以采取以下步骤: 检查虚拟网络编辑器 使用管理员权限打开虚拟网络编辑器,检查NAT方式下的虚拟子网网段。 确保虚拟机的网络设置与虚拟子网网段相匹配。检查虚拟机网络设置 …...

MySQL数据库的详解(1)

DDL(数据库操作) 查询 查询所有数据库:show databases;当前数据库:select database(); 创建 创建数据库:create database [ if not exists] 数据库名 ; 使用 使用数据库:use 数据库名 ; 删除 删除数…...

Python 网络爬虫技巧分享:优化 Selenium 滚动加载网易新闻策略

简介 网络爬虫在数据采集和信息获取方面发挥着重要作用,而滚动加载则是许多网站常用的页面加载方式之一。针对网易新闻这样采用滚动加载的网站,如何优化爬虫策略以提高效率和准确性是一个关键问题。本文将分享如何利用 Python 中的 Selenium 库优化滚动…...

Apache SeaTunnel 社区 3 月月报

各位热爱 SeaTunnel 的小伙伴们,SeaTunnel 社区 3 月月报来啦!这里将记录 SeaTunnel 社区每个月的重要更新,并评选出月度之星,欢迎关注。 SeaTunnel 月度 Merge Stars 感谢以下小伙伴 3 月为 Apache SeaTunnel 做的精彩贡献&…...

ElasticSearch 的 ConstantScoreQuery 的理解

ConstantScoreQuery的定义: A query that wraps another query and simply returns a constant score equal to 1 for every document that matches the query. It therefore simply strips of all scores and always returns 1. 结合DisMaxQueryBuilder可以查找所…...

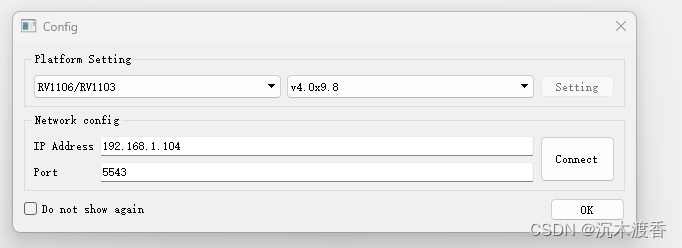

【RV1106的ISP使用记录之一】基础环境搭建

公司缺少ISP工程师,做为图像算法工程师的我这就不就给顶上来了么,也没给发两份工资,唉~ 先写个标题,占一个新坑,记录RK平台的传统ISP工作。 一、基础环境的硬件包括三部分: 1、相机环境,用于采…...

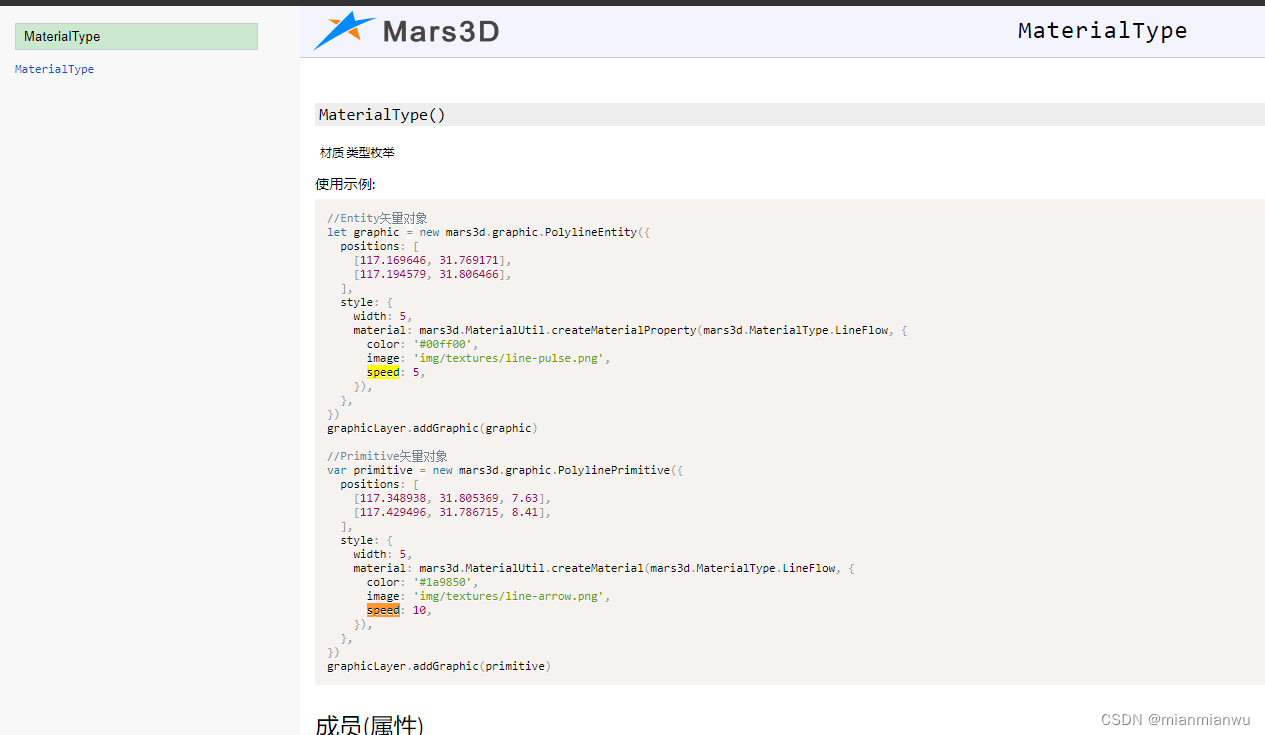

mars3d.MaterialType.Image2修改配置面状:图片2的speed数值实现动画效果说明

摘要: mars3d.MaterialType.Image2修改配置面状:图片2的speed数值实现动画效果说明 前提: 1.在示例中,尝试给mars3d.MaterialType.Image2材质的图片加上speed参数,实现动画效果,但是没有看到流动效果说明…...

Elasticsearch部署安装

环境准备 Anolis OS 8 Firewall关闭状态,端口自行处理 Elasticsearch:7.16.1(该版本需要jdk11) JDK:11.0.19 JDK # 解压 tar -zxvf jdk-11.0.19_linux-x64_bin.tar.gz# 编辑/etc/profile vim /etc/profile# 加入如下…...

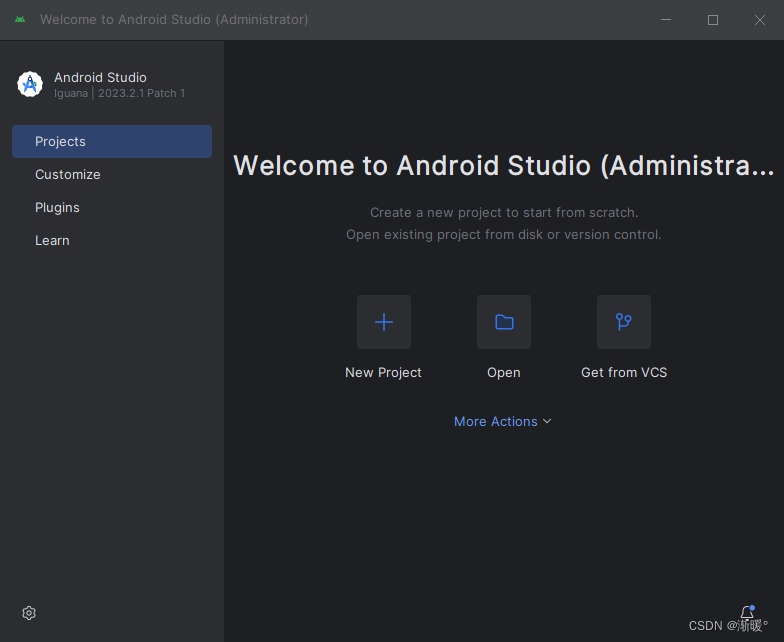

Android零基础入门(一)配置环境和安装Android Studio

闲来无事学一下Android,本人目前java为主,jdk的环境就不赘述了 配置环境 Java JDK5 或 以后版本 Android SDK Java运行时环境(JRE) Android Studio 你可以从 Oracle 的 Java 网站:JDKJava SE下载下载最新版本的 Jav…...

Golang编译优化——消除Copy指令

一、优化概述 以下是Go编译器对某个代码段编译生成的SSA IR摘选,对于Golang SSA IR的介绍我写了文章,但是在犹豫要不要发。 b1:-... Plain → b2 (5)b2: ← b1 b4-v9 (5) Phi <int> v8 v16 (i[int])v22 (8) Phi <int> v7 v14 (r[int])v1…...

Java IO流对象流实操

ATM的io对象流: package com.jsu.atm; import com.jsu.atm.Serializable; public class Account implements Serializable{//私有数据成员private String UserName; // 用户名称private String PassWord; // 用户密码private double RemainMoney; // 用户余额…...

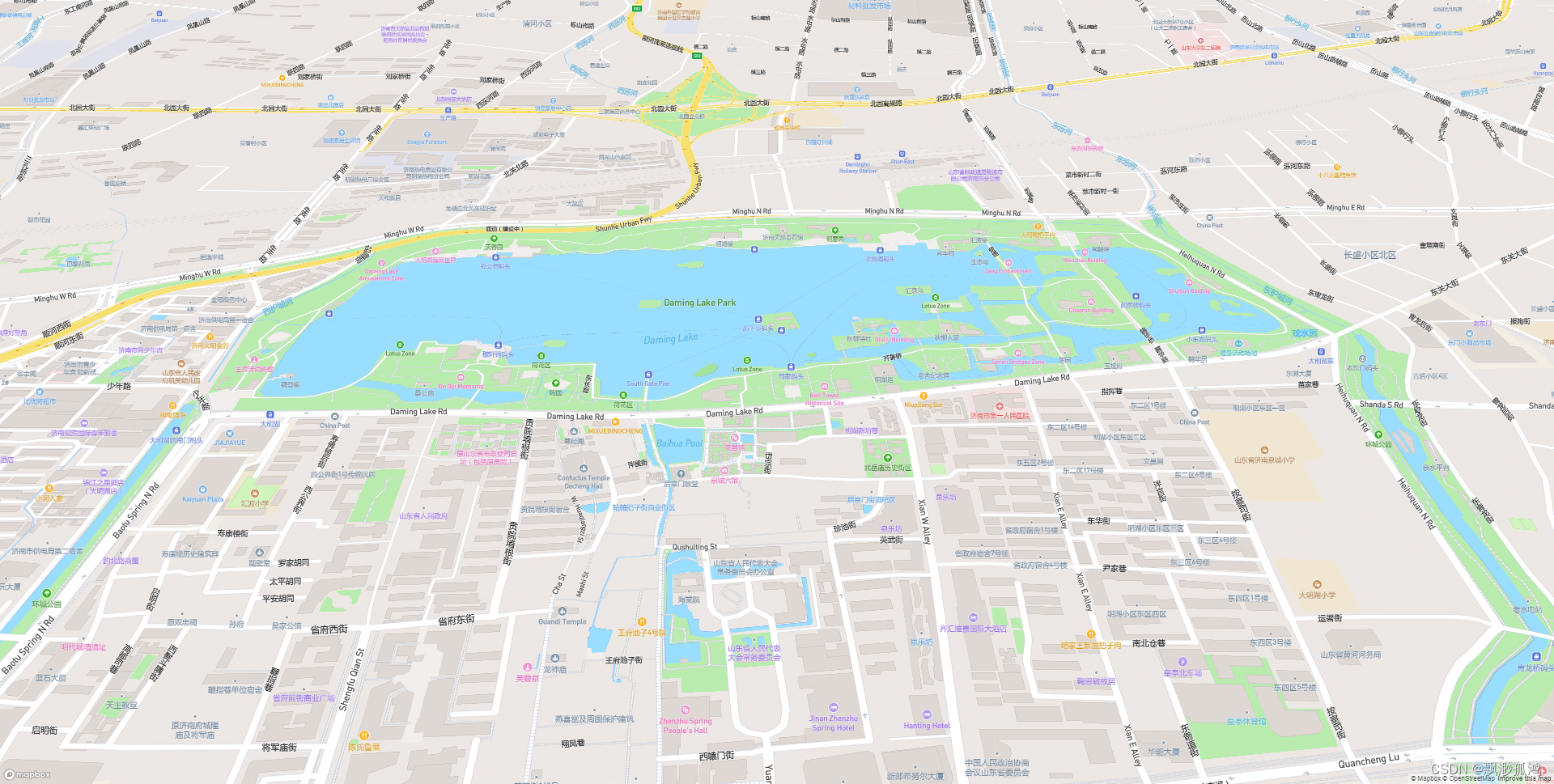

Mapbox教程:一个简单Demo

近期工作中准备把Mapbox用起来,准备发几个教程,把Mapbox再熟悉熟悉。工作中也用过不少的Web GIS组件,在这里说一下我对这些WebGIS组件的印象。 Leaflet 代码简洁,插件丰富,相比于其大小,功能也挺强大&#…...

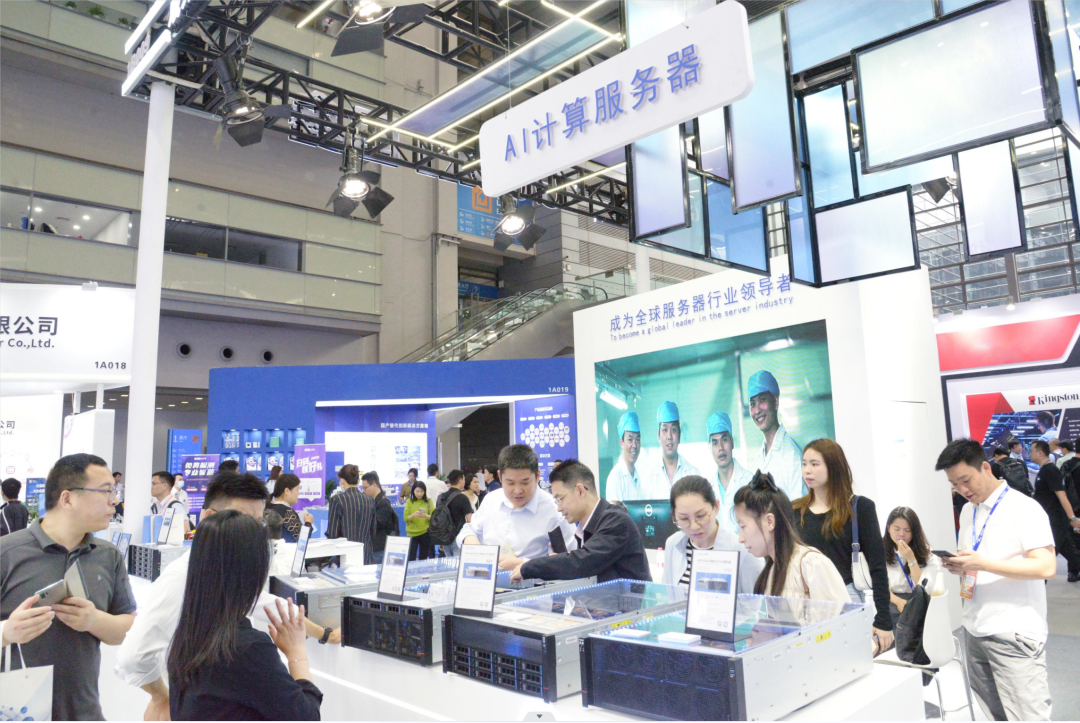

看AI赋能数智化 | Gooxi AI服务器闪耀CITE 2024

4月9日“中国电子信息博览会暨2024 AI算力产业大会”在深圳如期开展,Gooxi携最新产品、行业应用全栈解决方案出席盛会,全面展示Gooxi回应数智新时代下机遇与挑战的丰富AI创新实践成果。 All in AI,奔赴新质生产力 作为中国领先的服务器解决…...

大话设计模式——21.中介者模式(Mediator Pattern)

简介 用一个中介对象来封装一系列的对象交互。中介者使各对象不需要显式地相互引用,从而使其耦合松散,而且可以独立地改变它们之间的交互 UML图 应用场景 大量的连接使得一个对象不可能在没有其他对象的支持下工作,系统表现为一个不可分割的…...

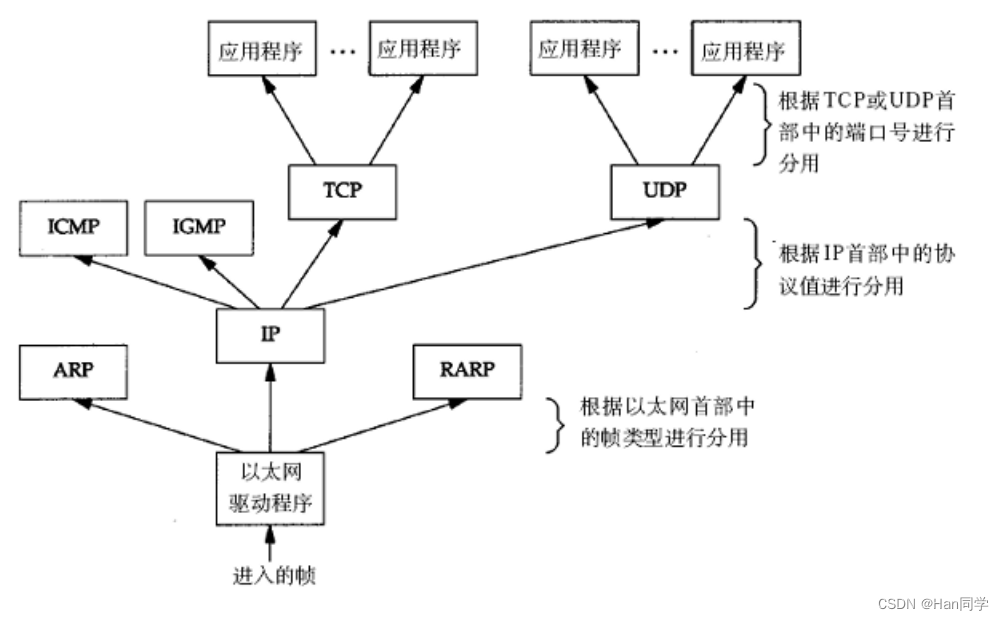

Linux 计算机网络

目录 一、网络协议 1、 "协议" 是一种约定 2、协议分层 二、网络模型 1、OSI七层模型 2、TCP/IP五层(或四层)模型 三、网络传输基本流程 四、数据包封装和分用 五、网络中的地址管理 六、网络编程套接字 1、理解源IP地址和目的IP地址 2、端口号 理解 &q…...

ClawLite:一键简化OpenClaw AI Agent框架的安装与成本优化

1. 项目概述:ClawLite,让OpenClaw的安装与上手变得简单 如果你对AI Agent(智能体)感兴趣,尤其是听说过OpenClaw这个强大的开源项目,但又被它复杂的命令行安装、环境配置和晦涩的文档劝退,那么Cl…...

DroidCam OBS插件:如何将手机摄像头变成专业直播设备?

DroidCam OBS插件:如何将手机摄像头变成专业直播设备? 【免费下载链接】droidcam-obs-plugin DroidCam OBS Source 项目地址: https://gitcode.com/gh_mirrors/dr/droidcam-obs-plugin 还在为直播设备预算不足而发愁?想让手机摄像头发…...

AGENTS.md:为AI编码助手定制的项目说明书,提升人机协作效率

1. 项目概述:为什么你的项目需要一个“AI专属说明书”?如果你最近在尝试用GitHub Copilot、Cursor或者Claude Code来辅助开发,大概率遇到过这样的场景:你满怀期待地给AI下达一个指令,比如“帮我给这个React组件添加一个…...

月薪2万+,2026年AI智能体工程师,这个岗位火了

AI智能体工程师负责设计、搭建、调优和维护AI智能体系统,让AI能自主感知环境、做出决策并执行动作。该岗位需求大,薪资高,适合具备逻辑拆解能力、Prompt工程能力和工具链认知的人。文章建议从体验AI智能体产品、学习相关课程和尝试搭建mini智…...

量子支持向量机原理与硬件优化实践

1. 量子支持向量机基础原理与硬件挑战量子支持向量机(QSVM)是传统支持向量机在量子计算框架下的扩展,其核心创新点在于利用量子态空间的高维特性构建核函数。与传统核方法相比,量子核映射通过量子电路将经典数据编码到希尔伯特空间…...

Windows on ARM:从技术预言到生态重塑的十年架构演进

1. 项目概述:一次重塑计算格局的“联姻”2010年,当业界还在消化Windows 7带来的变化时,一则关于“Windows 8将支持ARM架构”的传闻,在半导体和操作系统领域投下了一颗重磅炸弹。这不仅仅是关于一个新操作系统的功能更新࿰…...

FPGA电源系统设计与线性/开关稳压器应用指南

1. FPGA电源系统设计基础在数字系统设计中,FPGA因其可编程性和高性能已成为现代电子系统的核心器件。随着工艺技术进步,当代FPGA集成了数百万逻辑门、高速收发器、锁相环和专用处理单元,这些复杂模块对供电系统提出了严苛要求。一个典型的Xil…...

【DeepSeek+Grafana可视化实战指南】:20年SRE亲授5大避坑法则与实时指标监控黄金配置

更多请点击: https://intelliparadigm.com 第一章:DeepSeekGrafana可视化实战导论 DeepSeek 系列大模型(如 DeepSeek-V2、DeepSeek-Coder)在推理服务中产生丰富的运行时指标——包括 token 吞吐量、P99 延迟、GPU 显存占用、请求…...

github拆分小批量上传文件

Windows端1.把项目重置干净Remove-Item -Recurse -Force tool/.git2.打开文件夹3.把里面所有东西 全部剪切移到桌面只留 1 个小小的文件 就行4.回到终端,依次运行git initPS D:\soft\github\tool> git init Initialized empty Git repository in D:/soft/github/…...