verilog基础语法之数据类型

verilog基础语法之数据类型

- 1、 wire类型

- 2、 reg类型

- 3、向量

Verilog最常用的数据类型有两种:线网(wire)和寄存器(reg)。其中,wire 类型表示硬件单元之间的物理连线,reg用来表示存储单元。

1、 wire类型

wire类型是信号在不同元器件之间传递的媒介,用于表示硬件电路单元之间的物理连线,由其连接的器件的输出端连续驱动。如果没有驱动元件连接到wire型变量,或者存在冲突的驱动(即多个驱动源同时驱动同一个wire),那么该变量的值默认为"High-Impedance"(高阻态),通常表示为"Z"。高阻态是一种不驱动信号的状态,相当于该信号线上没有电流流动。“驱动”是指信号源对连线施加的电平,这个信号源可以是一个逻辑门、触发器、缓冲器、驱动元件或者任何其他可以产生信号的硬件实体。

另外,wire型变量的值可以由连续赋值(使用=操作符)或非阻塞赋值(在always块中使用<=操作符)决定。连续赋值类似于组合逻辑,它描述了输入变量和输出变量之间的直接关系,而输出值会随着输入值的变化而立即变化。

示例:

wire signal_wire; // 声明一个wire类型的信号线

assign signal_wire = some_driver; // some_driver是一个驱动源,可以是门、触发器等

在这个例子中,assign语句定义了一个连续赋值,some_driver是驱动signal_wire的驱动源。如果some_driver是一个逻辑门的输出,那么signal_wire将根据该逻辑门的输入而变化。

wire gnd = 1'b0;//创建一个名为 gnd 的全局地线信号,它被赋予了一个逻辑0(二进制值0)的初始值,地线通常在电路中表示参考点或0电平。

这行代码定义了一个名为 gnd 的 wire 类型的信号,并初始化为逻辑值 0。在某些情况下,设计者可能会使用 wire 类型来定义一个常量,即使用 wire 来表示一个始终为特定值的信号,但更常见的做法是使用 parameter 或 localparam 关键字来定义常量。对于地线,一般不需要在代码中显式定义,因为地线通常在FPGA的物理设计中是预定义的,并在布局时连接到相应的电源和地引脚。

需要特别说明的是,wire型变量通常用于表示模块的端口或者作为信号的传递媒介。它们不应当在always块内部被赋值,因为wire代表着连线,其值由外部信号源决定,而非由always块内的逻辑产生。如果试图在always块中对wire型变量使用<=操作符,这将导致编译错误,因为wire不允许在always块内部赋值。 然而,wire型变量可以在always块中被用作非阻塞赋值表达式中的一个源(source),但这只出现在一个模块的输出端口被另一个模块的输入端口所驱动的情况下。在这种情况下,wire实际上是连接两个模块的信号线。

以下是一个简单的示例,演示了如何在模块间使用wire型变量进行非阻塞赋值:

module d_flip_flop(input wire clk, // 时钟信号input wire data_in, // 数据输入output reg data_out // 数据输出

);`在这里插入代码片`// 使用非阻塞赋值在时钟上升沿捕获data_in的值

always @(posedge clk) begindata_out <= data_in;endendmodule// 测试模块,实例化d_flip_flop

module testbench();wire clk;wire data_in;wire data_out;// 实例化d_flip_flop模块d_flip_flop u_d_flip_flop(.clk(clk),.data_in(data_in),.data_out(data_out));// 驱动测试信号initial beginclk = 0;forever #10 clk = ~clk; // 产生时钟信号endinitial begindata_in = 0;#20 data_in = 1; // 在时间20ns处改变输入数据#20 data_in = 0;end// 监视输出变化initial begin$monitor("Time = %t, clk = %b, data_in = %b, data_out = %b", $time, clk, data_in, data_out);endendmodule

在这个例子中,data_out是一个reg型变量,它在d_flip_flop模块的always块中使用非阻塞赋值从data_in获得值。clk和data_in是wire型变量,它们在测试模块testbench中被驱动,并且连接到d_flip_flop模块的相应端口。请注意,尽管data_out是reg类型并且可以使用非阻塞赋值,但data_in和clk作为wire类型,它们的值是由测试模块生成的信号所驱动的,而不是在d_flip_flop模块内部的always块中赋值。在这个示例的always块中,data_in的值在时钟边沿被采样,并在data_out中保持,直到下一个时钟边沿到来。

总结来说,在Verilog中,“驱动”指的是信号源对连线施加的电平,而驱动源是产生这些信号的任何硬件元件。如果没有驱动源,wire型变量将呈现高阻态"Z"。

2、 reg类型

reg用来表示存储单元,它是一种可以存储数据并保持其状态的硬件元素。在仿真环境中,reg类型的变量行为与实际硬件中的寄存器类似,用于模拟寄存器的行为。在硬件实现中,reg声明的变量将被映射到FPGA或ASIC中的相应寄存器结构。与wire不同,reg不是用于连接模块的物理线,而是用于表示可以存储状态的寄存器。以下是reg类型的一些关键特性和用法:

-

状态保持:reg类型的变量可以保持它们的值,直到它们被新的赋值语句更新。这种特性使得reg类型非常适合用于建模需要记忆先前值的硬件寄存器和触发器。

-

非阻塞赋值:reg类型的变量通常与非阻塞赋值(使用 <=操作符)一起使用,这在时序逻辑中非常重要。非阻塞赋值确保了多个寄存器可以在同一时钟边沿更新,而不会产生竞态条件。

-

时序控制:在always块中,当指定了时钟信号(例如 posedge clk 或 negedgeclk),reg变量的赋值将与时钟信号的边沿同步。

-

初始化:可以在声明时初始化reg变量,但这种初始化仅在仿真开始时有效,实际硬件实现中寄存器的初始状态取决于其物理实现或配置过程。

-

并发与顺序:reg变量可以用于顺序逻辑(在always块中)和并发逻辑(在连续赋值语句之外声明)。

示例一:使用<=操作符在always块中对reg型变量赋值的示例:

module flip_flop(input wire clk, // 时钟信号input wire reset, // 复位信号input wire data_in, // 数据输入output reg data_out // 数据输出

);// 触发器行为的always块

always @(posedge clk or posedge reset) beginif (reset) begin// 异步复位:当reset为高时,data_out被清零data_out <= 1'b0;end else begin// 时钟边沿触发的数据锁存:data_out在每个clk的上升沿捕获data_in的值data_out <= data_in;end

endendmodule

在这个例子中,data_out是一个reg型变量,它在always块中使用<=操作符进行赋值。当reset信号为高时,data_out被清零;否则,在clk的每个上升沿,data_out将捕获data_in的值。

示例二:使用reg变量进行并发逻辑赋值的示例:

module combinatorial_logic(input wire [3:0] a,input wire [3:0] b,output reg [3:0] c

);// 并发赋值:输出端口c的值由输入a和b的当前值决定

// 这个always块没有时钟信号,因此它在仿真期间是并发执行的

always @(a or b) beginc = a + b;

endendmodule

在这个例子中,模块combinatorial_logic有一个4位宽的输入a和b,以及一个8位宽的输出c。输出c被声明为reg类型,并且它的值是由输入a和b的当前值决定的。这里的reg变量可以用于并发赋值,当reg变量在连续赋值语句之外声明,并且赋值不是发生在时钟边沿的always块中时,它们可以用于描述并发逻辑。这种用法通常在描述组合逻辑时看到,其中reg变量的赋值不是基于时序信号,而是基于其他信号的变化。尽管,使用了always块,但由于缺少时钟信号或复位信号,这个always块实际上定义了并发逻辑。当仿真环境中a或b的值发生变化时,c的值会立即更新,这与连续赋值的行为类似。

请注意,这种使用reg进行并发赋值的方式并不常见,因为它可能会隐藏逻辑的时序特性,使得设计难以验证和理解。在实际的硬件设计中,我们通常使用assign语句来创建组合逻辑的连续赋值,而使用带有时钟信号的always块来创建顺序逻辑。

此外,当设计被综合到实际的硬件时,没有时钟信号的always块可能会被优化掉,因为综合工具会认为这是一个恒定的赋值,而不是一个需要时序控制的寄存器赋值。在大多数情况下,如果你发现自己需要使用reg来创建并发逻辑,你应该重新考虑设计,并可能使用assign语句来代替。

3、向量

在Verilog中,向量数据类型是一种复合数据类型,是Verilog中用于表示多位宽信号的一种数据结构,它允许你将多个数据位组合成一个单一的实体。Verilog中的向量可以是单比特的集合,也可以是多位的集合,它们在硬件描述中非常有用,因为它们可以表示多比特的信号、总线或寄存器、内存等。向量的索引是从高位到低位递减的,即[7:0]表示从位7(最高位)到位0(最低位)。这种索引方式与常见的十进制计数方式相反,需要特别注意以避免混淆。向量在Verilog中非常有用,因为它们允许对多位宽的信号进行统一的操作和管理。以下是Verilog中向量数据类型的一些关键点:

-

位宽(Bit-width):向量数据类型具有明确的位宽,定义了向量中包含的位数。位宽在声明时指定,使用方括号[]表示。

-

线网(Wires):wire类型的向量是最常用的,用于表示多个位的连接,如数据总线或地址总线。

-

寄存器(Registers):reg类型的向量用于表示需要存储的多位信号,通常在时序逻辑中使用。

-

索引(Indexing):向量可以被索引,允许访问向量中的单个位或位的子集。索引从0开始,到位宽减一结束。

-

部分选择(Part Selection):可以基于起始位和结束位选择向量的一部分,用于创建子向量。

-

拼接(Concatenation):可以使用{a, b}的语法将两个或多个向量拼接成一个新的向量。

-

重复(Repetition):可以使用大括号和数字的组合,如{n{element}},来创建一个包含n个重复元素的向量。

-

位选择和部分选择操作符:位选择:使用方括号加索引,如vector[3]选择向量vector的第4位(索引从0开始)。部分选择:使用方括号加索引范围,如vector[3:1]选择从第4位到第2位的子向量。

-

向量赋值:可以对整个向量进行赋值,也可以对向量的一部分进行赋值。

另外,以下是声明向量的两种基本方式:

- 使用方括号:在声明时,使用方括号[]来指定位宽,其中包含两位数字,分别表示向量的高(MSB)和低(LSB)位索引。

- 单比特声明:如果向量的所有位都是单独声明的,然后通过拼接(concatenation)操作符{}来组合成一个向量。

以下是一些使用向量的示例:

module vector_example(input wire [7:0] data_in, // 8位宽的输入向量output reg [15:0] data_out, // 16位宽的输出向量output reg [3:0] flags // 4位宽的输出向量,用于标志位

);// 向量拼接

always @(data_in) begindata_out = {data_in, data_in}; // 将data_in拼接到自身,形成16位的向量

end// 向量部分选择

always @(data_out) beginflags = data_out[15:12]; // 选择data_out的高4位作为标志位

endendmodule

在这个例子中,data_in是一个8位宽的线网向量,可以表示一个字节的数据。data_out是一个16位宽的输出向量,而flags是一个4位宽的的寄存器向量,可以表示4个控制信号。通过使用向量和相关的操作符,可以方便地对多位信号进行操作。

另外,当位宽大于 1 时,wire 或 reg 即可声明为向量的形式。例如:

reg [3:0] counter ; //声明4bit位宽的寄存器counter

wire [32-1:0] gpio_data; //声明32bit位宽的线型变量gpio_data

wire [8:2] addr ; //声明7bit位宽的线型变量addr,位宽范围为8:2

reg [0:31] data ; //声明32bit位宽的寄存器变量data, 最高有效位为0

对于上面的向量,我们可以指定某一位或若干相邻位,作为其他逻辑使用。例如:

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1'b1 ;

参考资料:

编码宝库:Verilog 数据类型

相关文章:

verilog基础语法之数据类型

verilog基础语法之数据类型 1、 wire类型2、 reg类型3、向量 Verilog最常用的数据类型有两种:线网(wire)和寄存器(reg)。其中,wire 类型表示硬件单元之间的物理连线,reg用来表示存储单元。 1、…...

ansible部署lamp架构

搭建参考:ansible批量运维管理-CSDN博客 定义ansible主机清单 [rootansible-server ~]# vim /etc/hosts 192.168.200.129 host01 192.168.200.130 host02 [rootansible-server ~]# vim /etc/ansible/hosts [webserver] host01 host02 在ansible端编写index.html…...

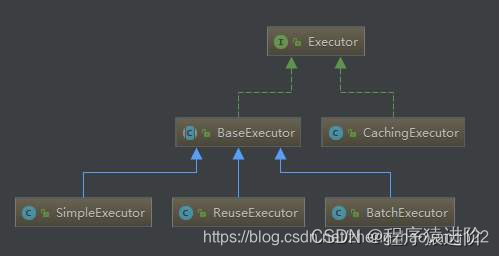

Java面试——MyBatis

优质博文:IT-BLOG-CN 一、MyBatis 与 JDBC 的区别 【1】JDBC 是 Java 提供操作数据库的 API;MyBatis 是一个持久层 ORM 框架,底层是对 JDBC 的封装。 【2】使用 JDBC 需要连接数据库,注册驱动和数据库信息工作量大,每…...

Ubuntu-22.04使用systemd.mount挂载本地磁盘

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、systemd.mount是什么?二、使用步骤1.增加mount文件2.测试mount文件 三、补充说明总结 前言 挂载磁盘方式我们都知道很多人喜欢在/etc/fstab里面…...

【Qt】界面定制艺术:光标(cursor)、字体(font)、提示(toolTip)、焦点(focusPolicy)与样式表(styleSheet)的深度探索

文章目录 前言:1. cursor: 设置按钮的光标2. front:设置字体3. toolTip: 鼠标悬停提示4. focusPolicy:设置控件获取到焦点的策略5. styleSheet : 样式表总结: 前言: 在现代软件开发中,用户界面(UI)的设计和…...

Python GraphQL服务器实现库之tartiflette使用详解

概要 Tartiflette是一个为Python编写的GraphQL服务器实现,它建立在现代异步编程库如asyncio之上,提供了高性能的GraphQL执行环境。Tartiflette专注于提供最佳的开发者体验,支持最新的GraphQL特性。 安装 安装Tartiflette相对简单,但需要依赖于一些系统级的库。 首先,需…...

面试官:请介绍类加载过程,什么是双亲委派模型?

🚀类加载过程是指在 Java 程序运行时,将类的字节码文件加载到内存中并转换为 Class 对象的过程。Java 类加载器负责加载类,其主要任务是在运行时查找和装载类文件,以生成对应的 Class 对象。 Java的类加载过程一般可以分为以下几个…...

mysql 细分

索引选择性 索引列的唯一值数量 / 表中的总行数 mysql如何优化-CSDN博客 批量问题 批处理默认是逐条发送 SQL 到数据库的,没有充分利用数据库提供的原生批处理能力,需要额外的配置来启用真正的批处理支持,如使用ExecutorType.BATCH 自定…...

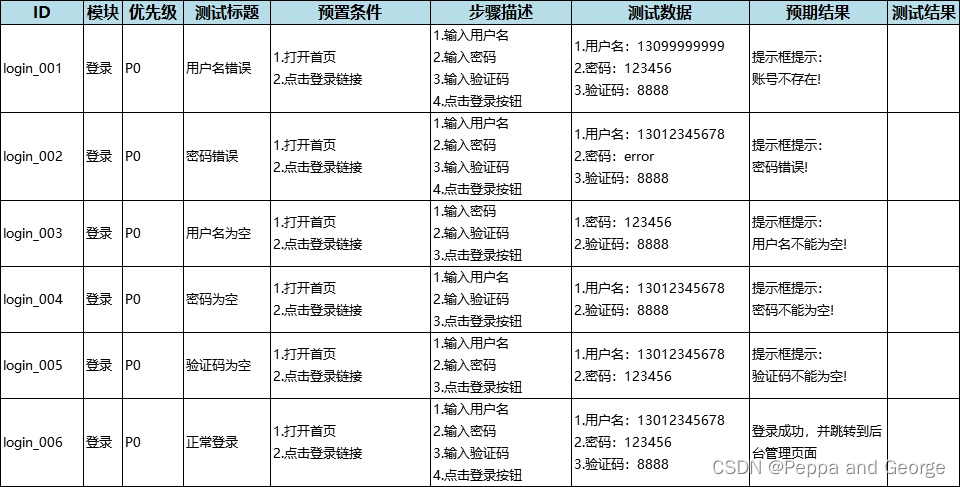

数据驱动实战二

目标 掌握数据驱动的开发流程掌握如何读取JSON数据文件巩固PO模式 1. 案例 对TPshop网站的登录模块进行单元测试 1.1 实现步骤 编写测试用例采用PO模式的分层思想对页面进行封装编写测试脚本定义数据文件,实现参数化 1.2 用例设计 1.3 数据文件 {"login…...

解决参考文献自动生成标号,换行时自动缩进

问题如下图所示,红色方框部分应该填充内容,但自动生成标号时不会填充: 解决方案: 1. 选中内容: 2. 找到布局-段落: 3. 选择“无”,即可。...

网络安全专业岗位详解+自学学习路线图

很多网安专业同学一到毕业就开始迷茫,不知道自己能去做哪些行业?其实网络安全岗位还是蛮多的,下面我会介绍一些网络安全岗位,大家可以根据自身能力与喜好决定放哪个方向发展。 渗透测试/Web安全工程师 主要是模拟黑客攻击&#…...

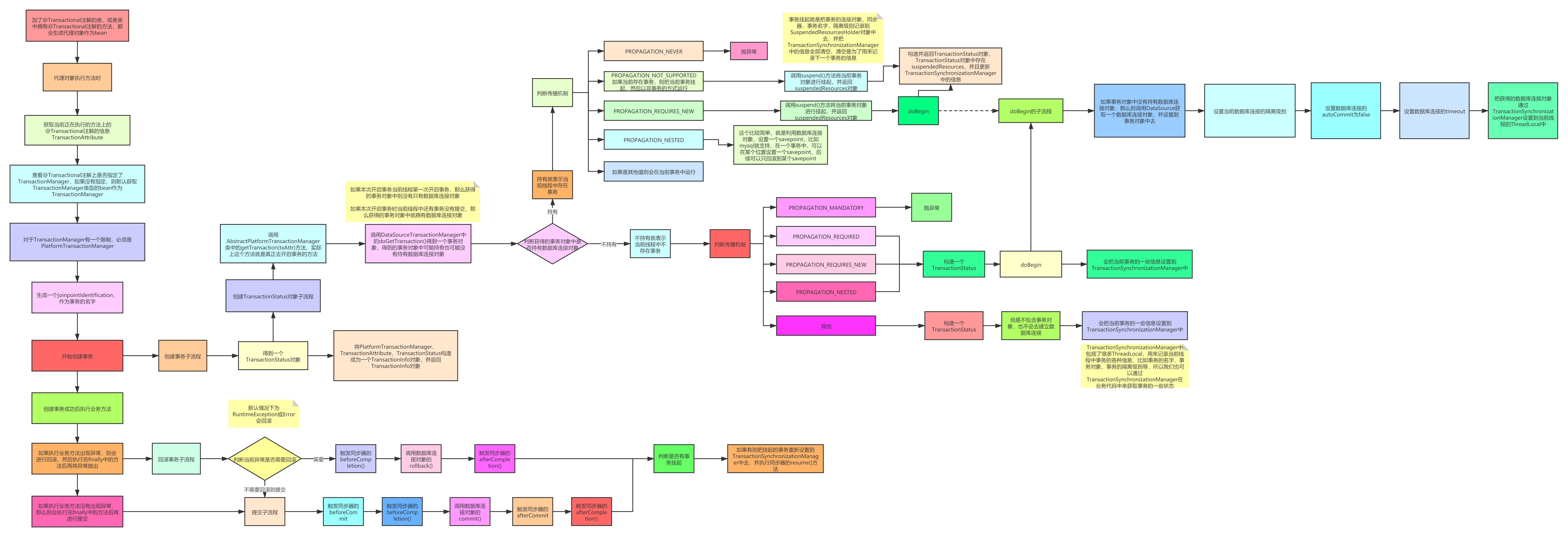

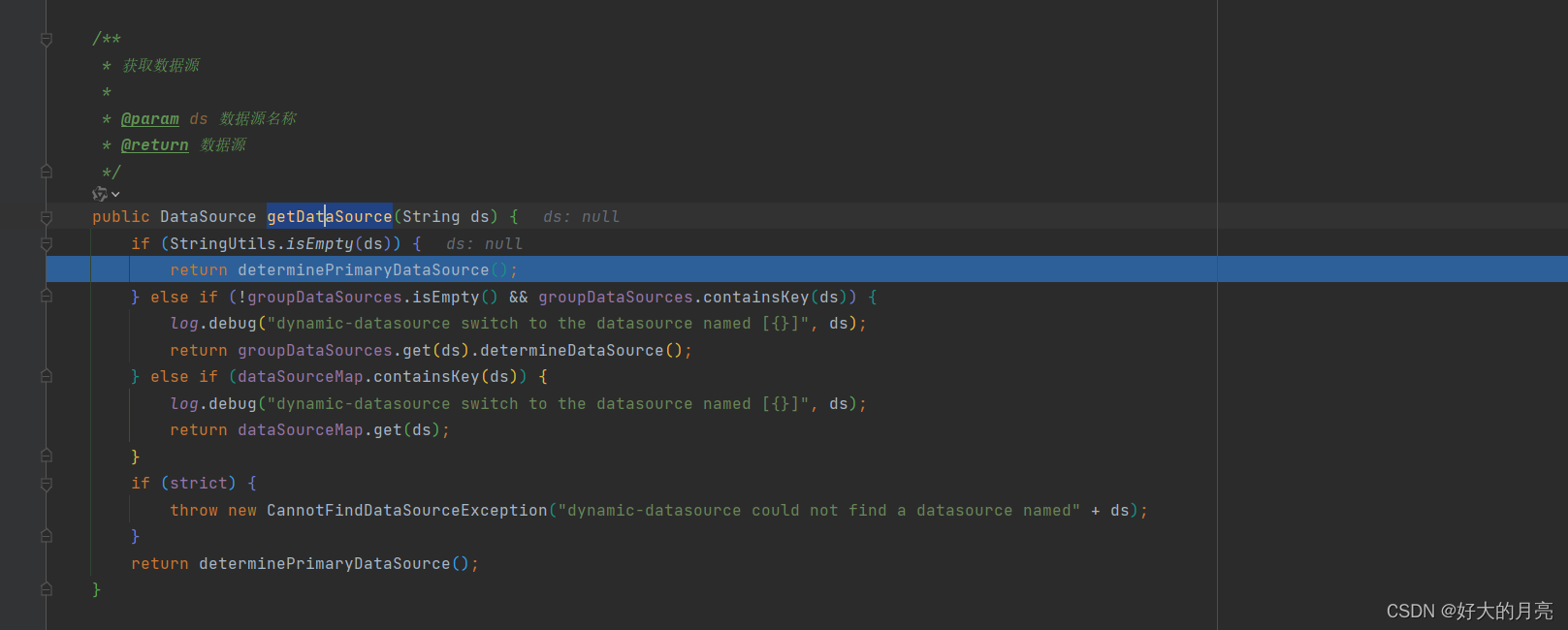

mybatisPlus一个事务中切换数据源概述

概述 在多数据源的配置下,业务中经常遇到在一个被本地事务包裹的save/edi方法中需要查询另一个数据源的数据; 直接查询会提示table不存在,这是因为一个事务和一个mysql连接是绑定的,mysql的连接背后包含了数据库信息,…...

如何在Android手机上恢复已删除的视频?

有时,由于不同的原因,可能会发生意外的数据丢失灾难。 那么如何在Android手机内存或没有计算机的情况下恢复已删除的视频呢?本文将给你一个答案。 如何在Android上恢复已删除的视频? 不要惊慌!您可以在Android手机上恢…...

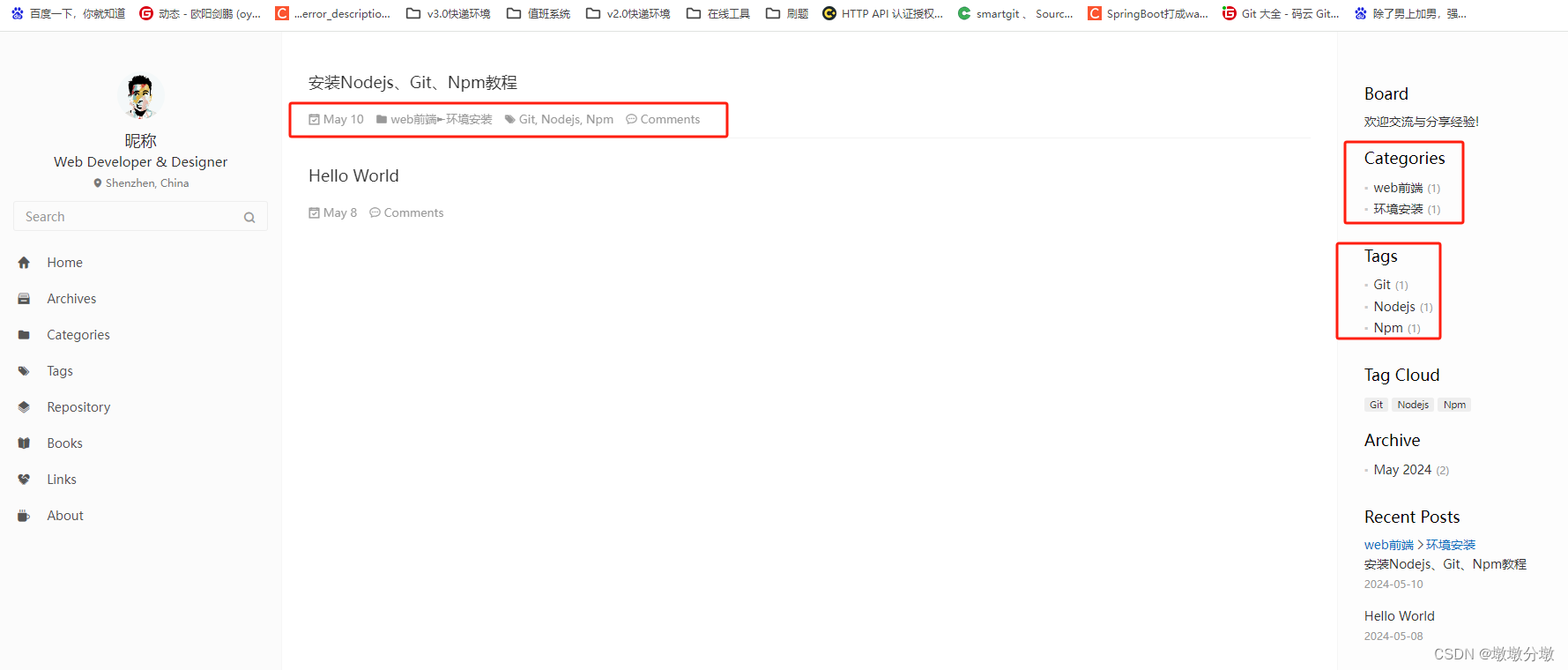

【项目实战】使用Github pages、Hexo如何10分钟内快速生成个人博客网站

文章目录 一.准备工作1.安装git2.安装node安装 cnpm 3.使用 GitHub 创建仓库,并配置 GitHub Pages0.Github Pages是什么1. 在 GitHub 上创建一个新仓库2. 创建您的静态网站3. 启用 GitHub Pages4. 等待构建完成5. 访问您的网站 二. Hexo1.什么是Hexo2.安装Hexo1. 安…...

)

大数据中服役新数据节点和退役旧节点步骤(hive,hadoop)

1- 节点上线操作 当要新上线数据节点的时候 ,需要把数据节点的名字追加在 dfs.hosts (1)关闭新增节点的防火墙 (2)在 NameNode 节点的 hosts 文件中加入新增数据节点的 hostname (3)在每个新…...

数论:不定方程的引入

研究的对象:不定方程 文章目录 研究的对象:不定方程不定方程引入:裴蜀定理证明:欧几里得算法证明:充分性证明:必要性证明: 战术总结: 不定方程引入: 不定方程࿰…...

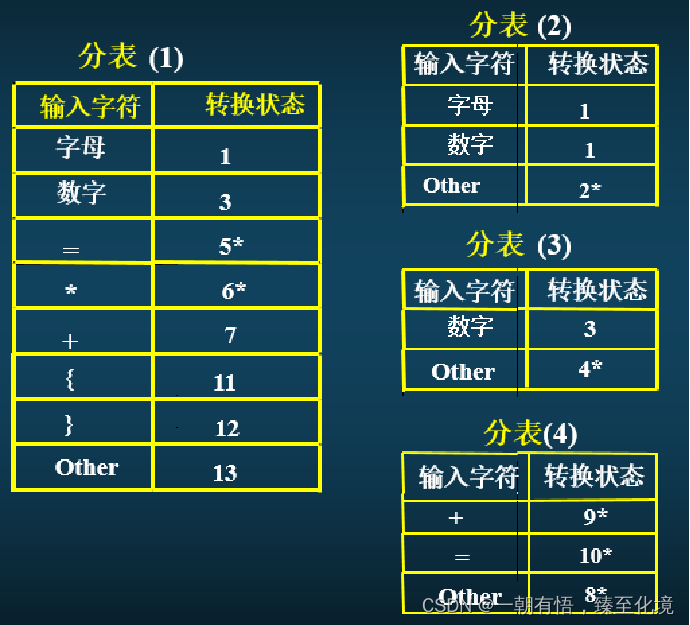

数据中心法

数据中心法是实现词法分析器的结构化方法。通过设计主表和子表分开存储状态转移信息,实现词法分析器的控制逻辑和数据结构分离。 主要解决了状态爆炸、难以维护和复杂性的问题。 状态爆炸是指当状态和转移较多时,单一使用一个表来存储所有的信息的话会导…...

pdffactory pro8.0虚拟打印机(附注册码)

PdfFactory pro是一款非常受欢迎的PDF虚拟打印机,可以帮助用户将你的其他文档保存为PDF格式。请为用户提供打印/发送/加密等多种实用功能,以及一套完善的PDF打印方案。 使用说明 下载pdfFactory Pro压缩包,解压后,双击exe文件&am…...

处理用户输入

目录 一、传递参数 1.1 读取参数 1.2 读取脚本名 二、跟踪参数 三、移动参数 四、处理选项 4.1 查找选项 4.1.1 处理简单选项 4.1.2 分离参数和选项 4.1.3 处理含值的选项 五、选项标准化 5.1 使用 getopt 命令 5.1.1 命令格式 5.1.2 在脚本中使用getopt 5.2 使用…...

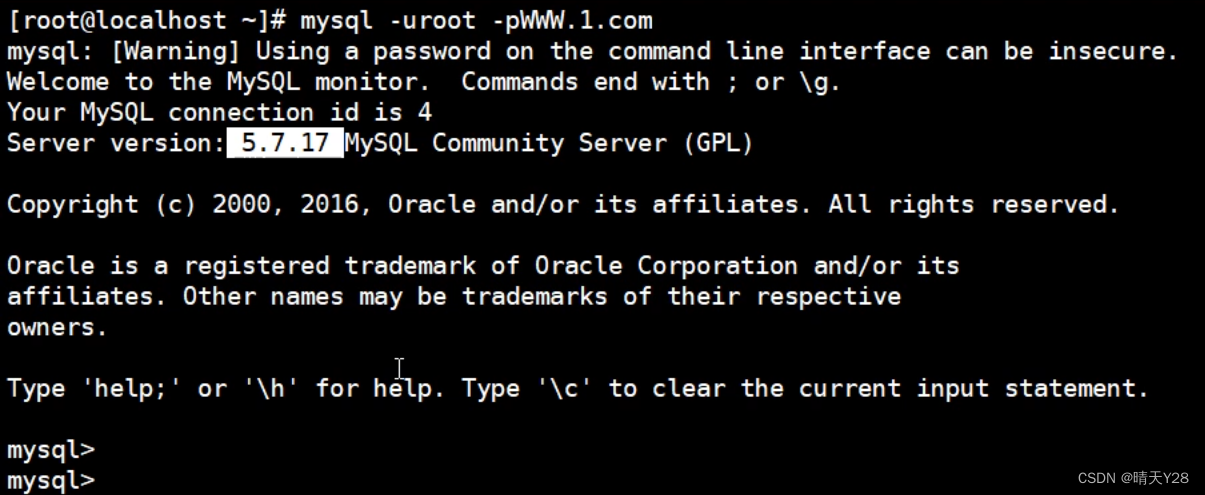

在装有centOS7的虚拟机上进行MySQL的安装部署

1.MySQL数据库介绍 1.开源的,跨平台的,社区版免费 2.支持多种存储引擎 3.支持多种主从复制 MySQL版本:5.6 5.7 8.0 https://www.mysql.com MySQL官网 2.安装MySQL5.7 1.配置MySQL仓库 2.安装MySQL服务端软件 3.启动MySQL服务 s…...

HRNet代码逐行解析:从BasicBlock到HighResolutionNet,手把手教你读懂多分辨率融合

HRNet代码深度解析:从基础模块到多分辨率融合实战 在计算机视觉领域,HRNet(High-Resolution Network)因其独特的并行多分辨率架构而备受关注。与传统的串行降采样网络不同,HRNet在整个前向传播过程中始终保持高分辨率表…...

SpringBoot整合ANIMATEDIFF PRO:企业级API网关设计

SpringBoot整合ANIMATEDIFF PRO:企业级API网关设计 动画生成服务在企业级应用中面临高并发挑战,如何构建稳定可靠的API网关成为关键问题 1. 企业级动画生成服务的挑战与需求 在现代企业应用中,AI动画生成服务已经成为内容创作、营销推广、教…...

)

Android开发者必看:知乎Matisse图片选择器实战教程(附Glide/Picasso配置对比)

Android图片选择器深度实战:Matisse与Glide/Picasso的终极配置指南 每次看到微信那个丝滑的图片选择界面,你是不是也想过在自己的App里实现类似效果?作为知乎开源的明星项目,Matisse确实能帮你快速搭建专业级图片选择功能。但真正…...

FUTURE POLICE语音对齐系统:MySQL数据库集成与结果分析实战

FUTURE POLICE语音对齐系统:MySQL数据库集成与结果分析实战 1. 语音对齐数据管理的挑战与解决方案 语音识别与对齐技术正在改变我们处理音频内容的方式。FUTURE POLICE系统凭借其毫秒级精度的强制对齐能力,为语音数据处理树立了新标准。然而࿰…...

避坑指南:vsftpd服务重启后仍报530?检查这5个隐藏配置项

避坑指南:vsftpd服务重启后仍报530?检查这5个隐藏配置项 当你已经按照常规流程检查了vsftpd服务状态、用户列表和基础配置文件,却依然遭遇"530 Permission denied"的顽固错误时,问题往往隐藏在那些容易被忽略的配置细节…...

Vitis HLS避坑指南:hls::stream深度设置不当,你的FPGA设计可能卡死

Vitis HLS实战:如何避免hls::stream深度配置引发的硬件死锁 在FPGA加速器开发中,数据流设计是最常见的性能优化手段之一。Vitis HLS提供的hls::stream模板类,让C代码能够直接映射到高效的硬件数据流结构。但许多开发者都遇到过这样的困境&…...

解决Windows HEIC预览难题:让iPhone照片在资源管理器中一目了然

解决Windows HEIC预览难题:让iPhone照片在资源管理器中一目了然 【免费下载链接】windows-heic-thumbnails Enable Windows Explorer to display thumbnails for HEIC files 项目地址: https://gitcode.com/gh_mirrors/wi/windows-heic-thumbnails 当摄影爱好…...

)

Python农业物联网开发必踩的5个致命坑,第3个让某省级智慧农场损失87万元(含Grafana+InfluxDB实时告警配置模板)

第一章:Python农业物联网开发必踩的5个致命坑,第3个让某省级智慧农场损失87万元(含GrafanaInfluxDB实时告警配置模板)传感器数据时间戳漂移导致历史分析全盘失效 Python中若直接使用time.time()或datetime.now()采集温湿度传感器数…...

虚拟机自动化新范式:CUA Computer SDK十分钟入门指南

虚拟机自动化新范式:CUA Computer SDK十分钟入门指南 【免费下载链接】cua Create and run high-performance macOS and Linux VMs on Apple Silicon, with built-in support for AI agents. 项目地址: https://gitcode.com/GitHub_Trending/cua/cua 在当今的…...

.NET校招真实面经:手写代码、项目深挖、算法到底考什么

文章目录写在前面:校招面试就像相亲,你得先过了"眼缘"这一关第一部分:手写代码——别做"嘴强王者",要做"手速达人"1.1 面试官为啥非要你手写代码?1.2 .NET校招手写代码到底考啥…...