HDLBits: 在线学习 SystemVerilog(二十三)-Problem 158-162(找BUG)

HDLBits: 在线学习 SystemVerilog(二十三)-Problem 158-162(找BUG)

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

SV:SystemVerilog

从今天开始新的一章-时序电路,包括触发器、计数器、移位寄存器、状态机等。

Finding bugs in code 这一节中,将找出给的电路中的bug,有一双找bug的眼睛。

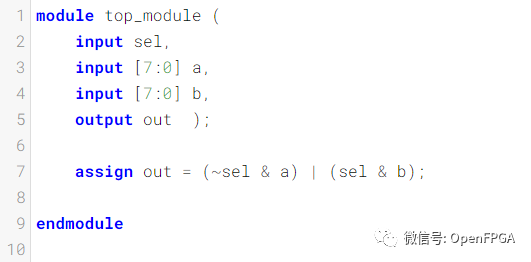

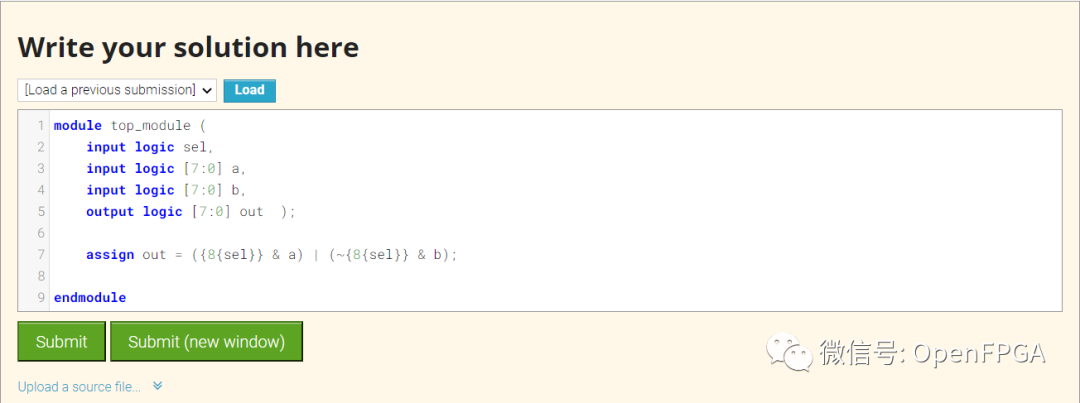

Problem 158-Bugs_mux2

题目说明

这个 8 位宽的 2 对 1 多路复用器不起作用。修复错误。

模块端口声明

module top_module (input sel,input [7:0] a,input [7:0] b,output [7:0] out );题目解析

sel的位宽不够,补到8位即可。

module top_module (input logic sel,input logic [7:0] a,input logic [7:0] b,output logic [7:0] out );assign out = ({8{sel}} & a) | (~{8{sel}} & b);endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

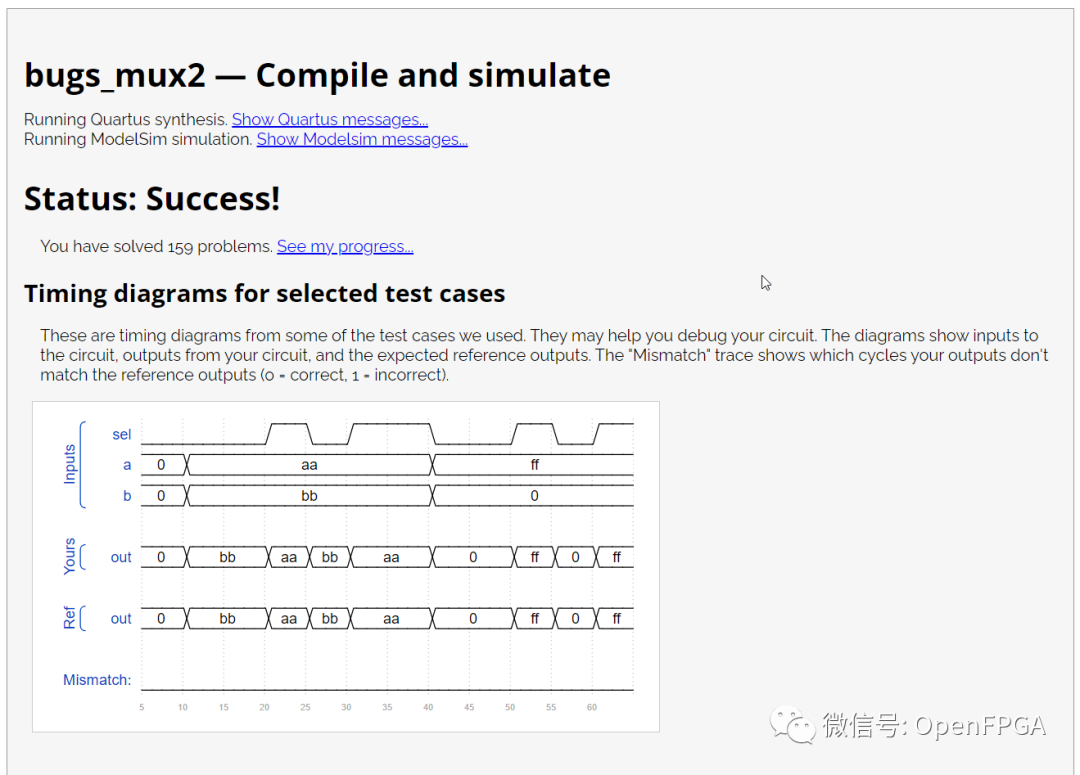

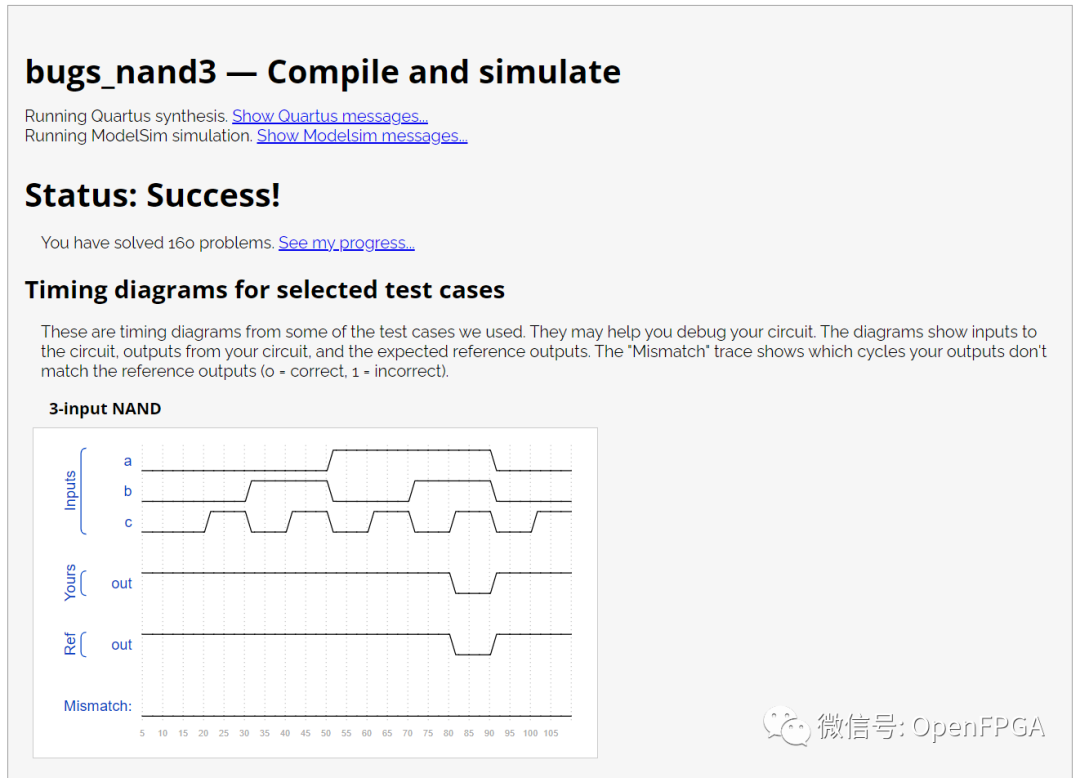

Problem 159-Bugs_nand3

题目说明

本题中的三输入与非门不工作了,找出并修正 BUG。

读者必须使用提供的 5 输入与门来实现这个与非门。

模块端口声明

module top_module (input a, input b, input c, output out);题目解析

原题中只使用了与门~

module top_module (input logic a, input logic b, input logic c, output logic out);//var logic out_temp ;andgate inst1 (.out(out_temp) ,.a(a),.b(b), .c(c),.d(1'd1),.e(1'd1));assign out = ~out_temp ;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

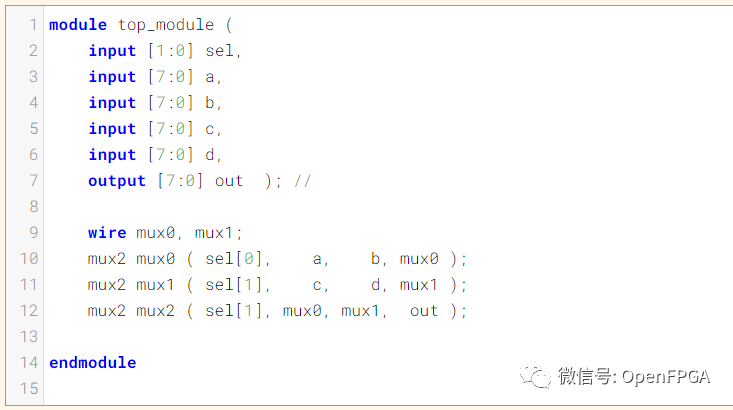

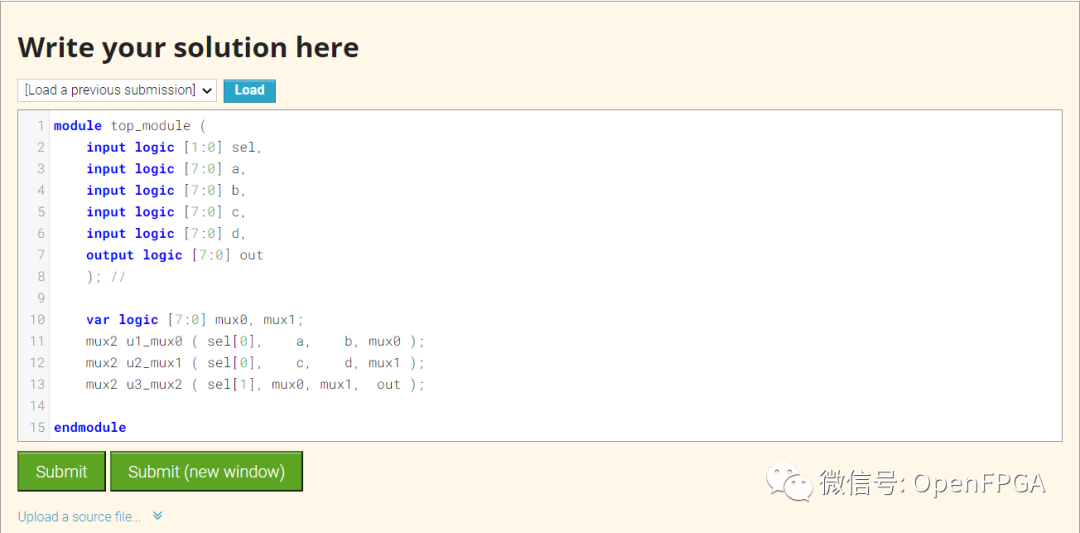

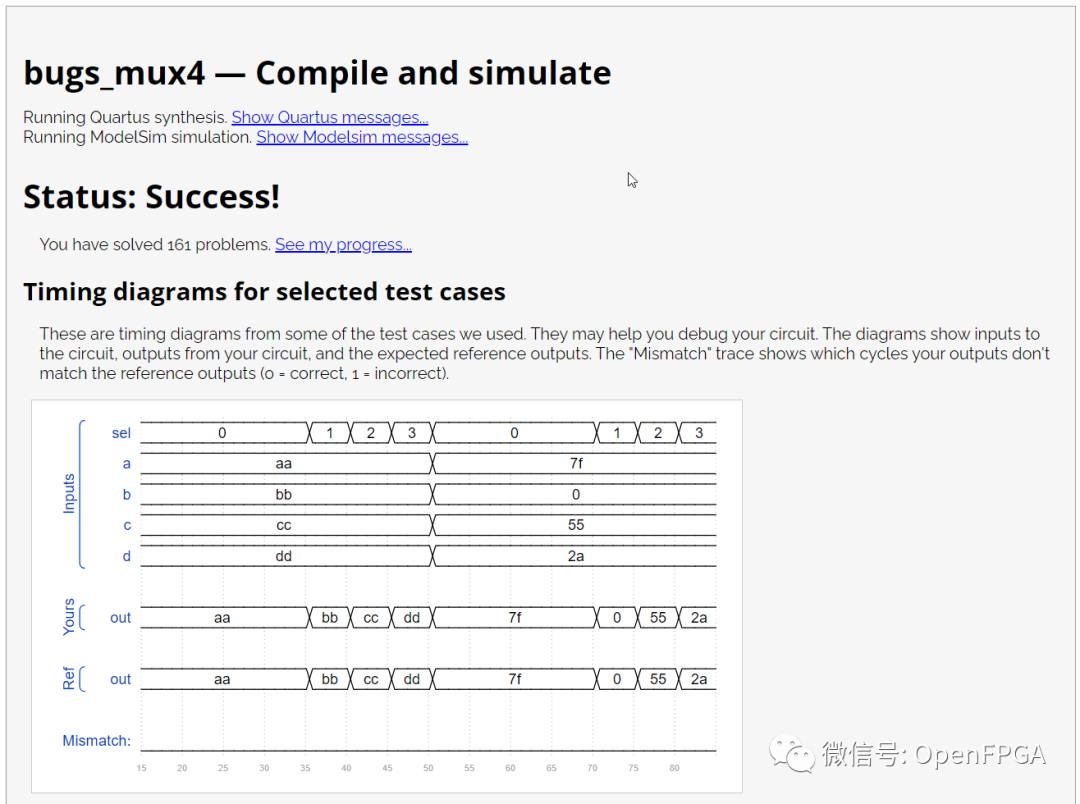

Problem 160-Bugs_mux4

题目说明

这个 4 对 1 多路复用器不起作用。修复错误。

下面无错误的 2 对 1 多路复用器:

module mux2 (input sel,input [7:0] a,input [7:0] b,output [7:0] out

);

模块端口声明

module top_module (input [1:0] sel,input [7:0] a,input [7:0] b,input [7:0] c,input [7:0] d,output [7:0] out );题目解析

没啥大问题,还是变量位宽问题。

module top_module (input logic [1:0] sel,input logic [7:0] a,input logic [7:0] b,input logic [7:0] c,input logic [7:0] d,output logic [7:0] out ); //var logic [7:0] mux0, mux1;mux2 u1_mux0 ( sel[0], a, b, mux0 );mux2 u2_mux1 ( sel[0], c, d, mux1 );mux2 u3_mux2 ( sel[1], mux0, mux1, out );endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

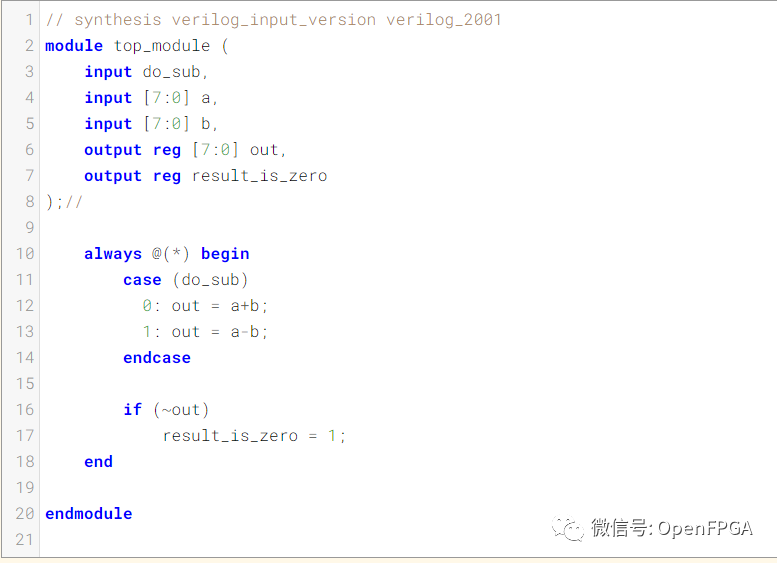

Problem 161-Bugs_addsubz

题目说明

继续找BUG

图片来自HDLBits

图片来自HDLBits模块端口声明

module top_module ( input do_sub,input [7:0] a,input [7:0] b,output reg [7:0] out,output reg result_is_zero

);题目解析

out条件举例不足。

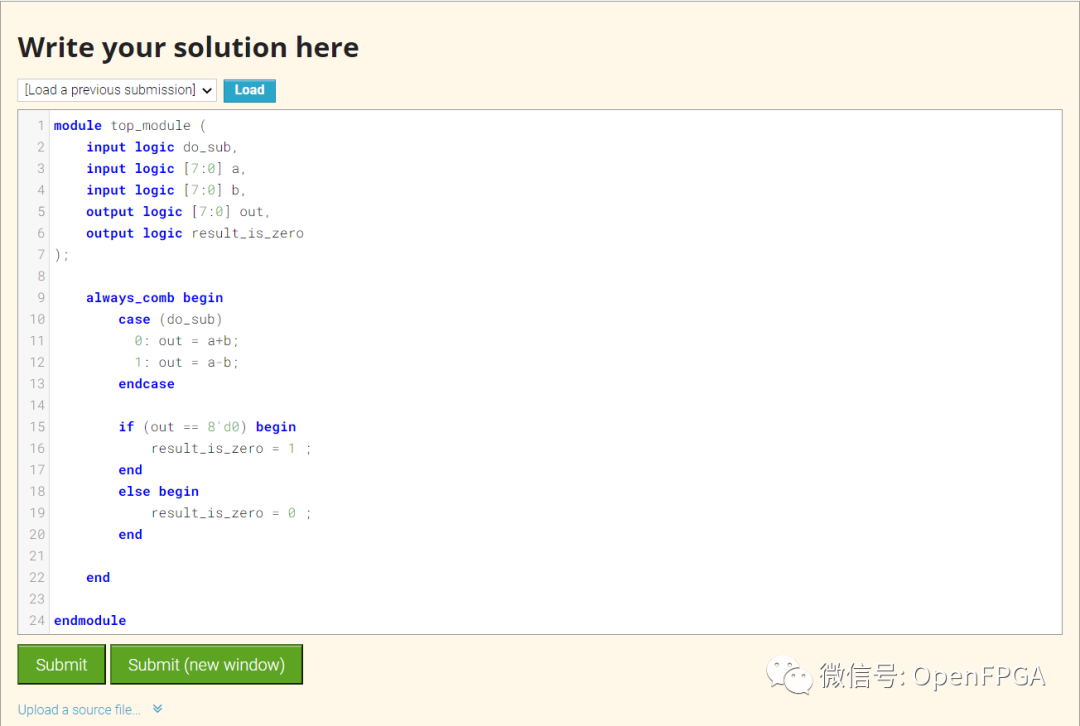

module top_module ( input logic do_sub,input logic [7:0] a,input logic [7:0] b,output logic [7:0] out,output logic result_is_zero

);always_comb begincase (do_sub)0: out = a+b;1: out = a-b;endcaseif (out == 8'd0) beginresult_is_zero = 1 ;endelse beginresult_is_zero = 0 ;endendendmodule

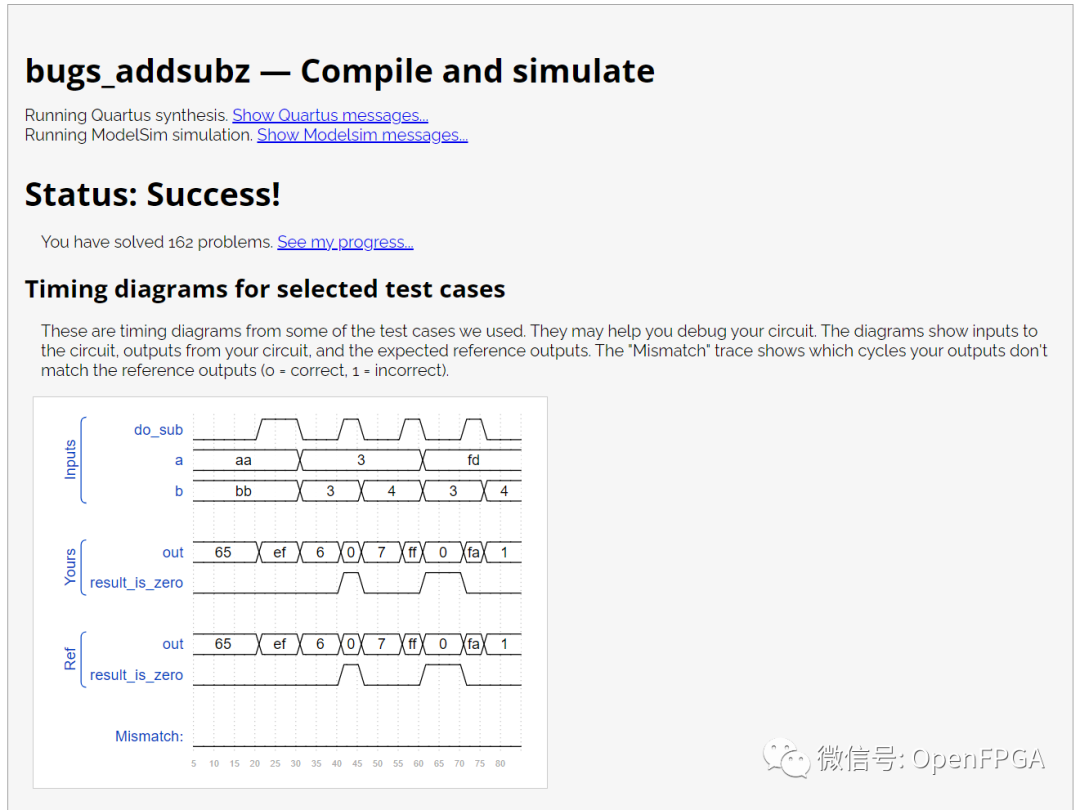

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

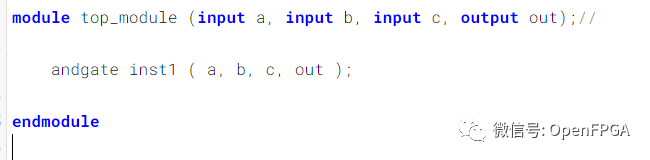

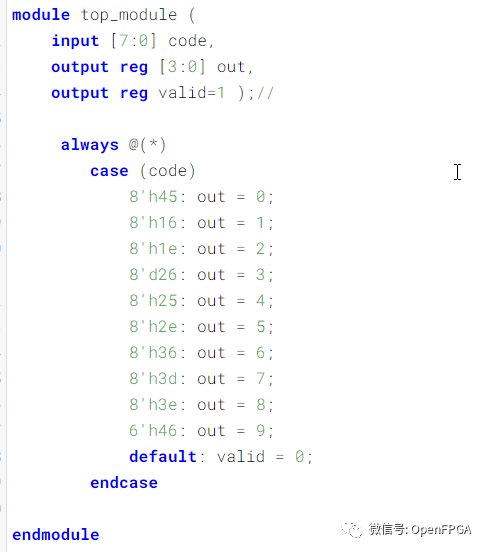

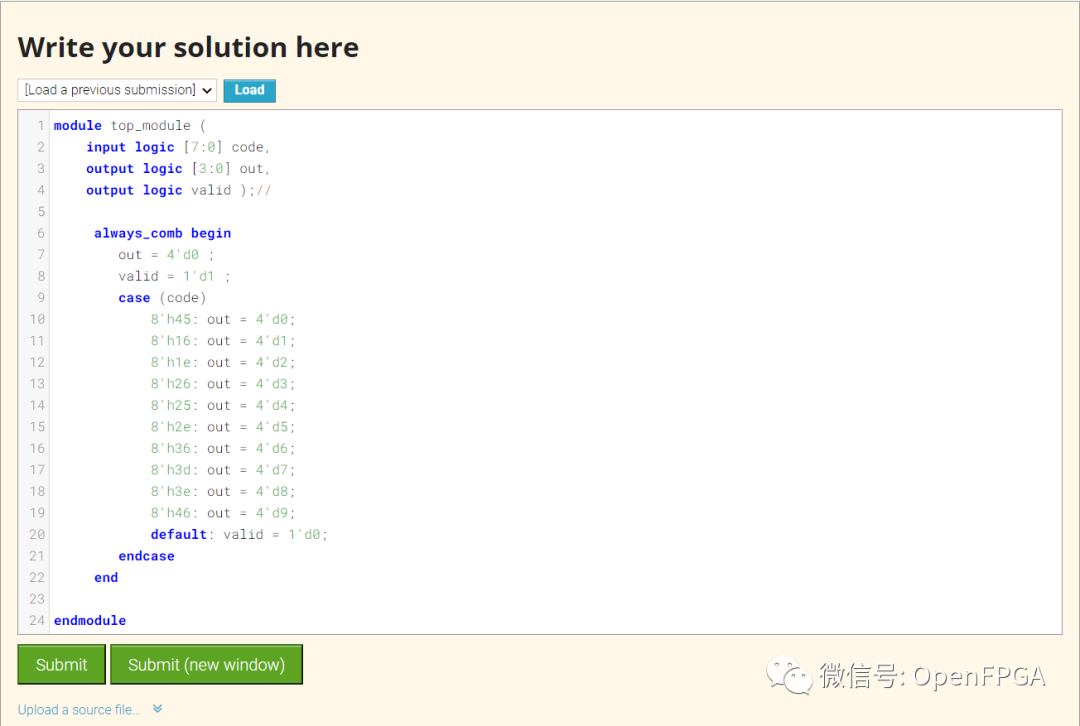

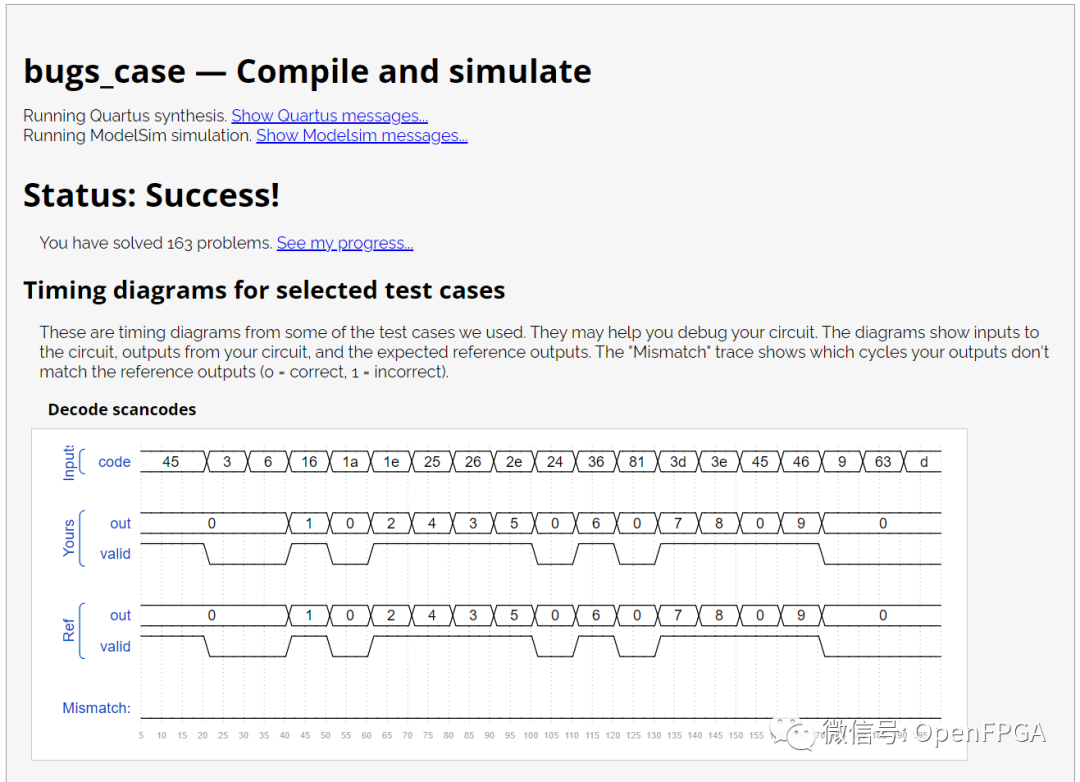

Problem 162-Bugs_case

题目说明

这个组合电路应该识别键 0 到 9 的 8 位键盘扫描码。它应该指示是否识别了 10 种情况中的一种(valid),如果是,则检测到哪个键。修复错误。

模块端口声明

module top_module (input [7:0] code,output reg [3:0] out,output reg valid=1 );题目解析

信号定义时不能赋值,case最后一个选项位宽不对。

module top_module (input logic [7:0] code,output logic [3:0] out,output logic valid );//always_comb beginout = 4'd0 ;valid = 1'd1 ;case (code)8'h45: out = 4'd0;8'h16: out = 4'd1;8'h1e: out = 4'd2;8'h26: out = 4'd3;8'h25: out = 4'd4;8'h2e: out = 4'd5;8'h36: out = 4'd6;8'h3d: out = 4'd7;8'h3e: out = 4'd8;8'h46: out = 4'd9;default: valid = 1'd0;endcaseendendmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

总结

今天的几道题就结束了,找bug开不开心~

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

相关文章:

HDLBits: 在线学习 SystemVerilog(二十三)-Problem 158-162(找BUG)

HDLBits: 在线学习 SystemVerilog(二十三)-Problem 158-162(找BUG)HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~网址如下:https://hdlbits.01xz.ne…...

国外SEO升级攻略:如何应对搜索引擎算法变化?

搜索引擎优化(SEO)是一个动态的领域,搜索引擎的算法经常会发生变化,这意味着SEO专业人员需要保持更新的技术知识和策略, 以适应变化并提高网站的排名。 以下是一些应对搜索引擎算法变化的升级攻略: 创造…...

X.509证书

证书格式ASN.1是一种抽象的数据结构,描述了复杂的对象,以及对象之间的关系。证书本质上是一个文件,需要一种专门的格式,才能在互联网中传输,证书需要通过一个规则将ASN.1转换为二进制文件,这就需要对证书以…...

高等数学——微分方程

文章目录概念一阶微分方程可降阶的微分方程高阶线性微分方程线性微分方程解的结构常系数齐次线性微分方程常系数非齐次线性微分方程概念 微分方程:含有未知函数的导数或微分的方程称为微分方程。微分方程的阶:微分方程中所出现的未知函数最高阶导数的阶…...

JAVA小记-生成PDF文件

项目场景: 例如:项目中需要生成PDF文件 项目使用情况 1、引入pom.xml <!--pdf相关依赖--> <dependency><groupId>com.itextpdf</groupId><artifactId>itextpdf</artifactId><version>5.5.13</version> </dependency>…...

Noah-MP陆面过程模型建模方法与站点、区域模拟

陆表过程的主要研究内容以及陆面模型在生态水文研究中的地位和作用 熟悉模型的发展历程,常见模型及各自特点; Noah-MP模型的原理 Noah-MP模型所需的系统环境与编译环境的搭建方法您都了解吗?? linux系统操作环境您熟悉吗&…...

全国青少年软件编程(Scratch)等级考试一级真题——2019.9

青少年软件编程(Scratch)等级考试试卷(一级)分数:100 题数:37一、单选题(共25题,每题2分,共50分)1.小明在做一个采访的小动画,想让主持人角色说“大家好!”3秒…...

第十四届蓝桥杯三月真题刷题训练——第 6 天

目录 第 1 题:星期计算 问题描述 运行限制 代码: 第 2 题:考勤刷卡 问题描述 输入格式 输出格式 样例输入 样例输出 评测用例规模与约定 运行限制 代码: 第 3 题:卡片 问题描述 输入格式 输出格式 样…...

安装MySQL数据库8.0服务实例

前言 之前尝试去安装了MySQL5.7的社区版本,今天来安装MySQL8.0的版本,并且以两种方式进行安装,一个是通过RPM包的安装,另一个则是编译的方式。 一. 前期准备 查看服务器IP [rootlocalhost ~]# hostname -I 192.168.161.166 19…...

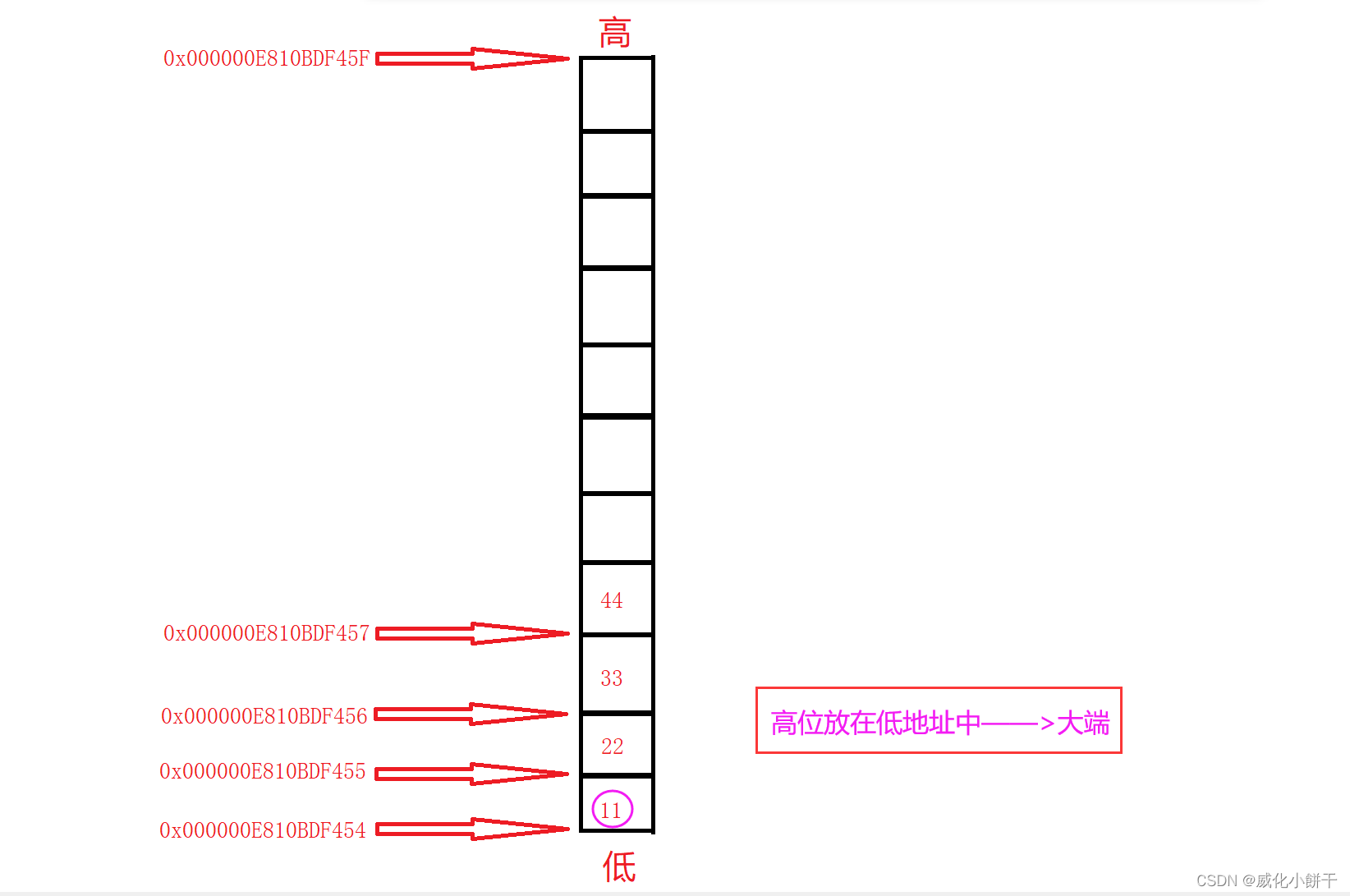

数据的存储--->【大小端字节序】(Big Endian)(Little Endian)

⛩️博主主页:威化小餅干📝系列专栏:【C语言】藏宝图🎏 ✨绳锯⽊断,⽔滴⽯穿!一个编程爱好者的学习记录!✨前言计算机硬件有两种存储数据的方式:大端字节序——Big Endian小端字节序——Little …...

软件测试备战近三银四--面试心得

自信即巅峰,对待面试官就像和儿子一样,耐心!耐心!耐心!...

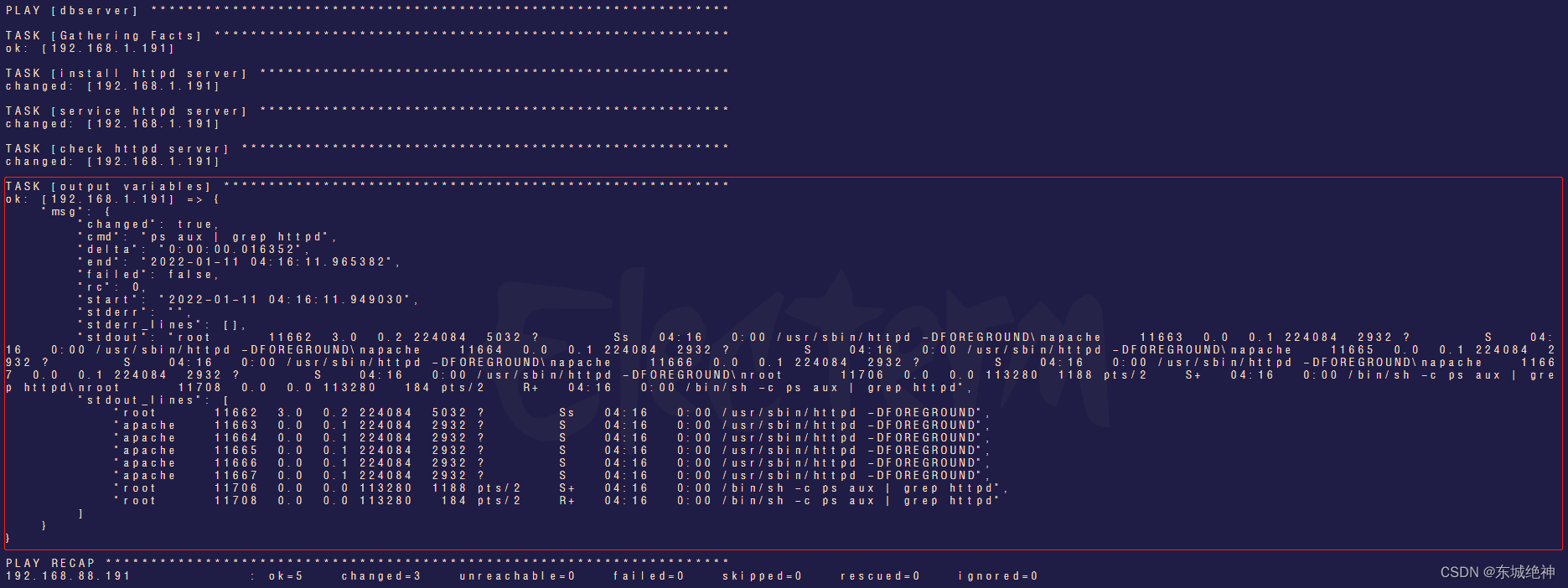

《Linux运维实战:ansible中的变量定义及以及变量的优先级》

一、配置文件优先级 Ansible配置以ini格式存储配置数据,在Ansible中⼏乎所有配置都可以通过Ansible的Playbook或环境变量来重新赋值。在运⾏Ansible命令时,命令将会按照以下顺序查找配置⽂件。 # ⾸先,Ansible命令会检查环境变量,…...

监听 Form表单变化)

useEffect 通过 form.getFieldValue(‘xxx‘) 监听 Form表单变化

场景 子组件中,某一个表格的数据需要依赖于上级组件的某一个表单元素值进行计算。 毫无疑问,首先想到的肯定是监听 form 表单中元素的值,使用 useEffect 监听表单的变化,当值发生变化时,重新计算渲染。 首先说下我的…...

【晓龙oba出品 - 黑科技解题系列】- 最小操作次数使数组元素相等

思路 算法归根到底就是找规律的游戏,我们首先来看一个现象: 以数组nums [1,2,3,4,5]为例 当我们将数组排序后,可以知道最小值为1,最大值为5,此时我们需要四次运算可以使最小值与最大值相等: 第一次:2,3,4,…...

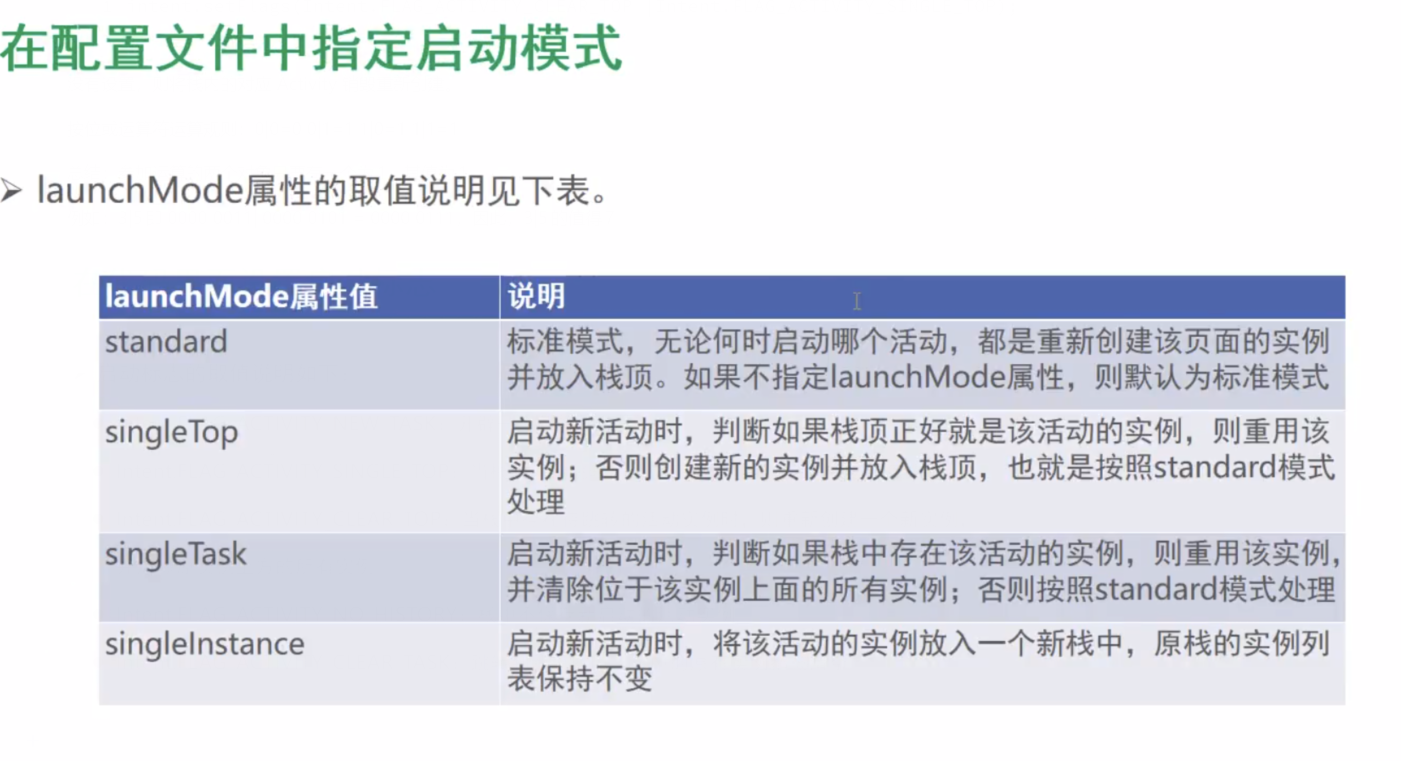

Activity的启动和结束

onCreate:创建活动。此时会把页面布局加载进内存,进入了初始状态。onStart:开启活动。此时会把活动页面显示在屏幕上,进入了就绪状态。onResume:恢复活动。此时活动页面进入活跃状态,能够与用户正常交互&am…...

利用业务逻辑+OB分布式特性优化SQL

最近某人社局核心数据库上了OB,经常出现性能问题 某人社与我司合作多年,非常信任我司在数据库的专业能力,邀请我司过去看看能否提供帮助 与OB驻场工程师合作,抓取了一天的TOP SQL,跑得慢的SQL有几十条(注意只是某一天的…...

哈希表

文章目录什么是哈希问题引入哈希函数直接定址法除留余数法 (常用、重点)哈希冲突哈希冲突的解决方法闭散列开散列unordered_map && unordered_set 封装实现哈希的应用位图布隆过滤器哈希经典面试题哈希切分位图应用布隆过滤器什么是哈希 在上一…...

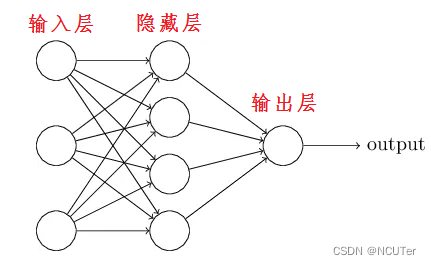

基于Halcon的MLP(多层感知神经网络)分类器分类操作实例

一、介绍 人工神经网络(Artificial Neural Network,ANN)简称神经网络(Neural Network,NN)或类神经网络,是一种模仿生物神经网络的结构和功能的数学模型或计算模型,用于对函数进行估计或近似。 MLP神经网络是一种基于神经网络、动态的分类器。MLP分类器使用神经…...

VR全景博物馆,打造7*24小时的线上参访体验

导语:博物馆作为人们了解历史、文化和艺术的重要场所,现在可以通过VR全景技术来进行展览,让参观者身临其境地感受历史文化的魅力。本文将介绍博物馆VR全景的特点、优势,以及如何使用VR全景技术来丰富博物馆的展览和教育活动。什么…...

Go 数据类型

基础数据类型 类型长度(字节)默认值说明bool1falsebyte10uint8,取值范围[0,255]rune40Unicode Code Point,int32int,uint4或者8032位或64位操作系统int8,uint810-128~127,0-255int16,uint1620-32768~32767,…...

IPv6支持不足?选用双栈兼容IP离线库,平滑过渡

上个月,我接手了一个线上报修:某客户的内网监控系统突然查不到部分IP的归属地了。登录服务器一看,日志里全是这种报错: Error: IP format not supported: 240e:3a0:xxxx::1 查代码发现,这套系统三年前上线时嵌了一个…...

5大突破性功能:重新定义Mac微信体验的终极指南

5大突破性功能:重新定义Mac微信体验的终极指南 【免费下载链接】WeChatExtension-ForMac Mac微信功能拓展/微信插件/微信小助手(A plugin for Mac WeChat) 项目地址: https://gitcode.com/gh_mirrors/we/WeChatExtension-ForMac 你是否曾因微信消息被撤回而错…...

TrollInstallerX终极指南:一键在iOS设备上安装TrollStore的完整教程

TrollInstallerX终极指南:一键在iOS设备上安装TrollStore的完整教程 【免费下载链接】TrollInstallerX A TrollStore installer for iOS 14.0 - 16.6.1 项目地址: https://gitcode.com/gh_mirrors/tr/TrollInstallerX 您是否一直在寻找一种简单可靠的方法&am…...

小白也可以安装成功!)

【2026 最新】 MySQL 数据库安装教程(超详细图文版-纯享版)小白也可以安装成功!

一、前言 MySQL 作为开源关系型数据库的标杆,广泛应用于 Web 开发、数据分析等场景,是程序员必备的基础工具之一。很多新手安装MySQL时都会陷入“版本选择困难症”——版本太高怕兼容出问题,版本太低又缺功能、不支持主流框架,甚…...

RTX4090D优化版Qwen3-32B+OpenClaw:3小时搞定AI办公自动化

RTX4090D优化版Qwen3-32BOpenClaw:3小时搞定AI办公自动化 1. 为什么选择本地部署方案 去年冬天,当我第17次被飞书机器人返回的"API配额不足"提示打断工作流时,终于下定决心寻找替代方案。作为一个小型技术团队的负责人࿰…...

为什么头部金融科技公司已在2026 Q1全面切换Python AOT?——基于百万行代码仓库的构建耗时、镜像体积、安全扫描通过率真实数据复盘

第一章:Python 原生 AOT 编译方案 2026 对比评测报告Python 社区在 2025 年底迎来关键演进:CPython 官方正式将原生 AOT(Ahead-of-Time)编译能力纳入 3.14 开发主线,并以“Project Graviton”为代号推动落地。2026 年初…...

)

运筹优化算法工程师入门指南:从数学基础到实战项目(附学习资源清单)

运筹优化算法工程师入门指南:从数学基础到实战项目(附学习资源清单) 运筹优化(Operations Research)作为一门融合数学建模与工程实践的学科,正在供应链管理、智能制造、交通调度等领域展现出不可替代的价值…...

Unity入门:从零开始认识Unity编辑器界面

Unity入门:从零开始认识Unity编辑器界面📚 本章学习目标:深入理解从零开始认识Unity编辑器界面的核心概念与实践方法,掌握关键技术要点,了解实际应用场景与最佳实践。本文属于《Unity工程师成长之路教程》Unity入门篇&…...

Windows平台Docker部署Home Assistant全攻略:从零配置到智能家居控制

1. 环境准备与Docker安装 想在Windows上玩转智能家居中枢?DockerHome Assistant组合绝对是新手友好方案。我去年给父母家改造智能家居时就用的这套方案,实测稳定运行一年多没出过问题。先说说基础环境搭建,这里会手把手带你避开我踩过的坑。 …...

Qwen2.5-72B-Instruct-GPTQ-Int4镜像定制:添加自定义工具函数与插件

Qwen2.5-72B-Instruct-GPTQ-Int4镜像定制:添加自定义工具函数与插件 1. 模型简介与部署验证 Qwen2.5-72B-Instruct-GPTQ-Int4是通义千问大模型系列的最新版本,在多个关键能力上实现了显著提升: 知识量与专业能力:特别强化了编程…...