第一篇 逻辑门(与门、或门、非门、异或门)

一、实验目的

-

了解DE1-SOC开发板一些外设。

-

掌握常用组合逻辑门电路的基本原理。

-

学习Verilog HDL的基本语法。

-

学习使用ModelSim工具对设计的电路进行仿真,包括编写Testbench仿真代码,以及ModelSim工具的使用。

-

熟悉使用Quartus软件从创建Quartus工程到最终配置FPGA并观察实验现象的流程。

二、逻辑门电路介绍

逻辑门电路是数字电路中最基本的单元电路,是构成各种逻辑功能电路的基本电路。常用的逻辑门电路在逻辑功能上有与门、或门、非门、与非门、或非门、异或门。本实验主要介绍其中的与门、或门、非门和异或门。

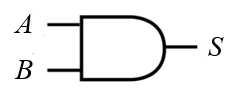

1. 与门

与门又称逻辑与电路,是执行与运算的基本逻辑门电路,有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

如下表1.1所示为二输入与门的真值表。

表1.1 二输入与门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

下图所示为二输入与门逻辑符号。

以上二输入与门用逻辑运算表达式可表示为S = A&B,用Verilog HDL描述该与门的代码语句为:

assign S = A & B;2. 或门

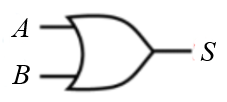

或门又称逻辑或电路。如果几个条件中,只要有一个条件得到满足,某事件就会发生,这种关系叫做或逻辑关系。或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑1),输出就为高电平(逻辑1);只有当所有的输入全为低电平(逻辑0)时,输出才为低电平(逻辑0)。

如下表1.2所示为二输入或门的真值表。

表1.2 二输入或门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

下图所示为二输入或门逻辑符号。

以上二输入或门用逻辑运算表达式可表示为S = A + B,用Verilog HDL描述该或门的代码语句为:

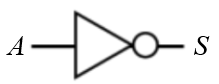

assign S = A | B;3. 非门

非门实现逻辑代数非的功能,即输出始终和输入保持相反。当输入端为高电平(逻辑1)时,输出端为低电平(逻辑0);反之,当输入端为低电平(逻辑0)时,输出端则为高电平(逻辑1)。

如下表1.3所示为非门的真值表。

表1.3 非门真值表

| 输入A | 输出S |

|---|---|

| 0 | 1 |

| 1 | 0 |

下图所示为非门逻辑符号。

非门用逻辑运算表达式可表示为S= ~A,用Verilog HDL描述该非门的代码语句为:

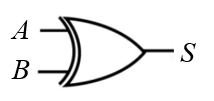

assign S = ~ A;4. 异或门

异或门是数字逻辑中实现逻辑异或的逻辑门,有多个输入端、一个输出端。若输入端的电平不同,则输出为高电平1;若输入端的电平都相同,则输出为低电平0。

如下表1.4所示为二输入异或门的真值表。

表1.4 异或门真值表

| 输入A | 输入B | 输出S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

下图所示为二输入异或门逻辑符号。

以上二输入异或门用逻辑运算表达式可表示为S = A xor B ,用Verilog HDL描述该异或门的代码语句为:

assign S = A ^ B;也可以用以下代码语句表示:

assign S = (~A & B) | (A & ~B);三、逻辑门实验任务

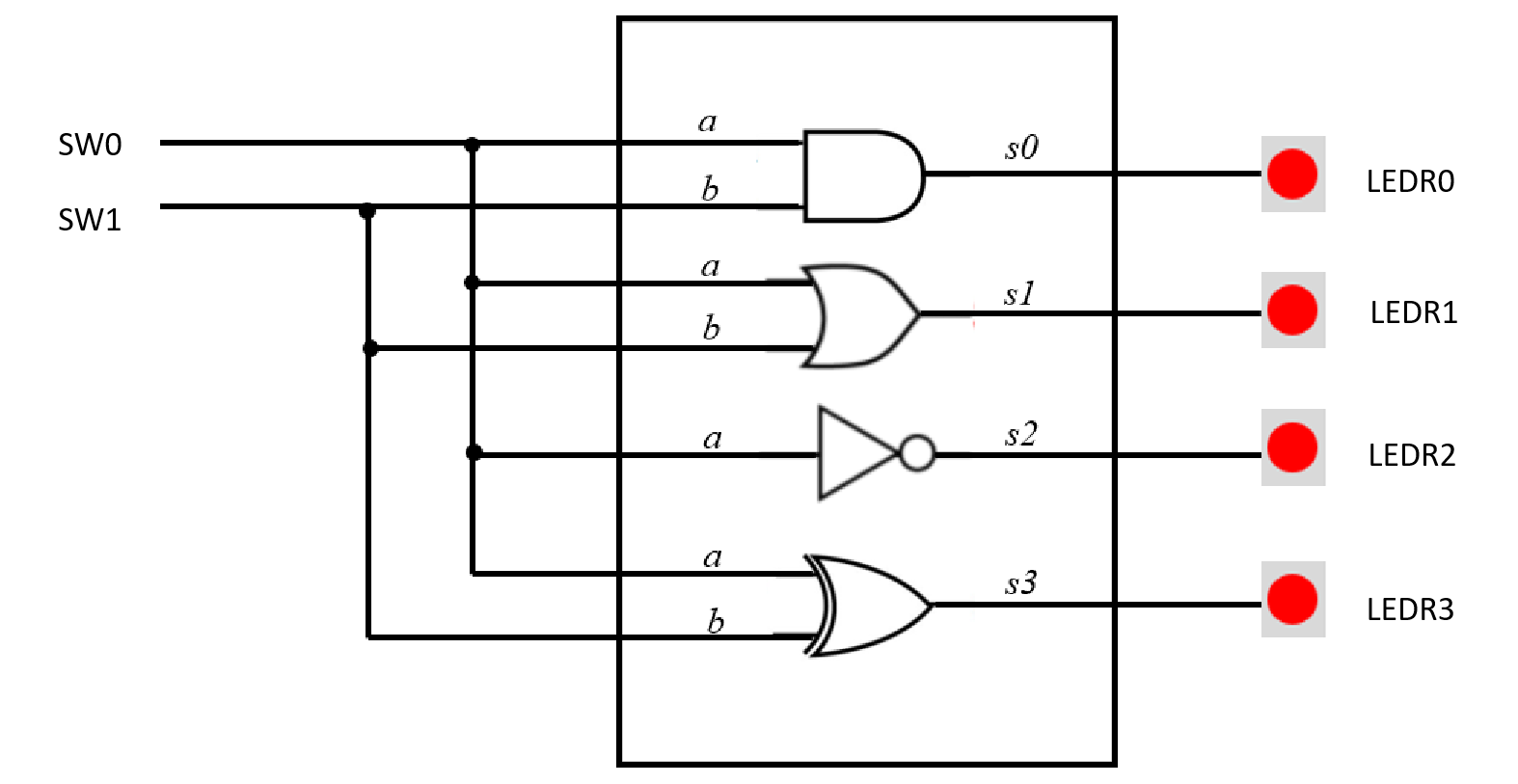

设计并实现二输入与门、或门、异或门以及非门电路,两个操作数用DE1-SOC的滑动开关控制,并将该四个门电路的输出结果显示在DE1-SOC开发板的4个LED上,通过操作SW滑动开关观察LED相应的变化来验证所设计电路的正确性。

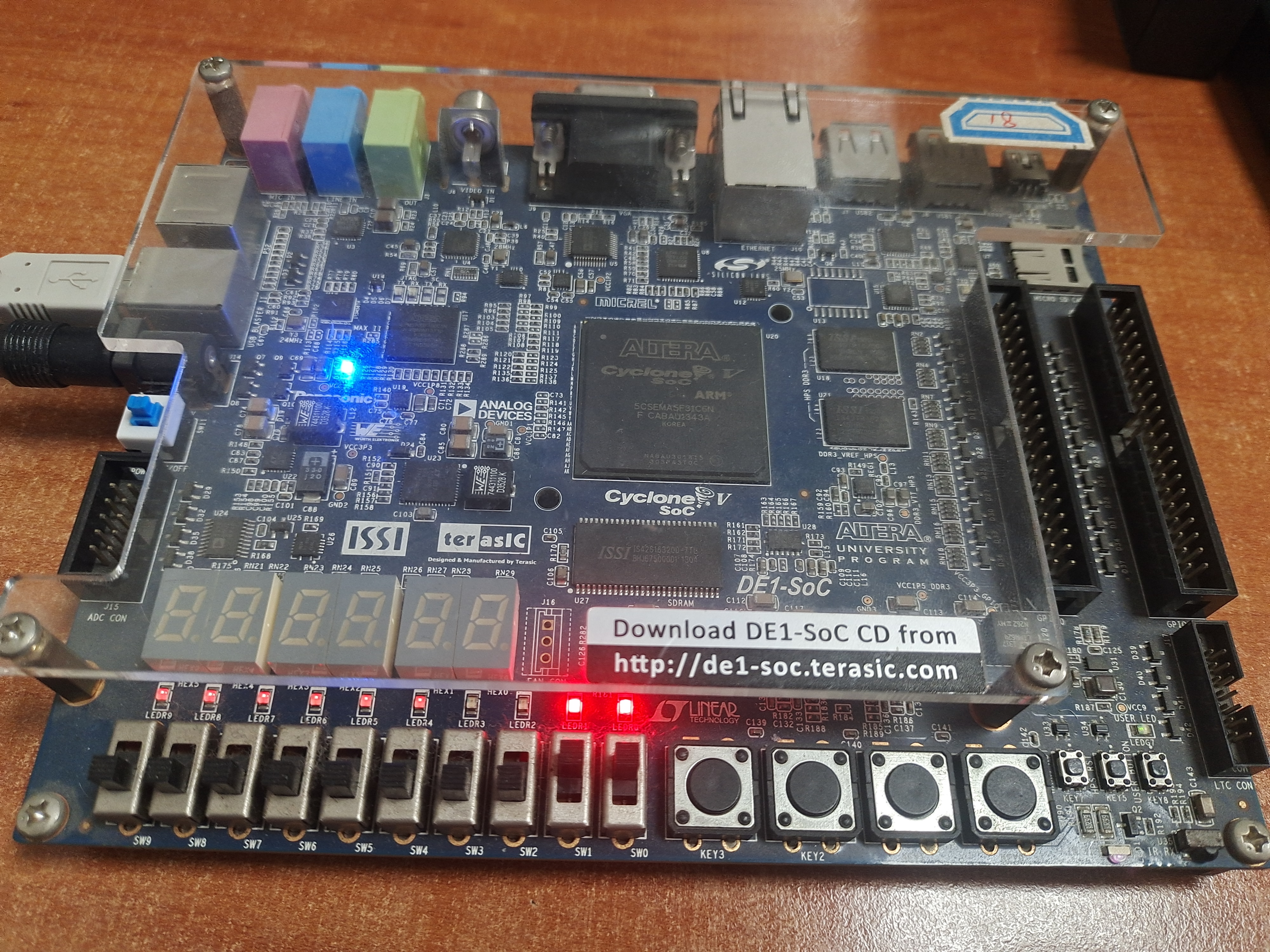

1. 硬件介绍

滑动开关

如下图所示,DE1-SOC开发板上有10个滑动开关,可在电路中用作电平触发的数据输入。每个滑动开关都连接到Cyclone V FPGA对应的一个引脚,当某个滑动开关拨到向上(up)的位置时,会产生一个高电平到FPGA;当拨到向下(down)的位置时,会产生一个低电平到FPGA。

LED

如下图所示,DE1-SOC开发板上有10个红色LED。每个LED连接到Cyclone V FPGA对应的一个引脚,将这些引脚输出设置为高电平1即可点亮对应的LED,反之设置低电平0$即可使对应的LED熄灭。

2. 设计思路

本实验所实现的电路,包含了与门、或门、非门以及异或门。与门、或门以及异或门的输入为a和b,而输出分别为s0,s1和s2。非门的输入为a,输出为s3。在DE1-SOC实现该电路时,将SW[0]和SW[1]作为输入a和b,将LEDR[3]~LEDR[0]作为输出s3~s0。

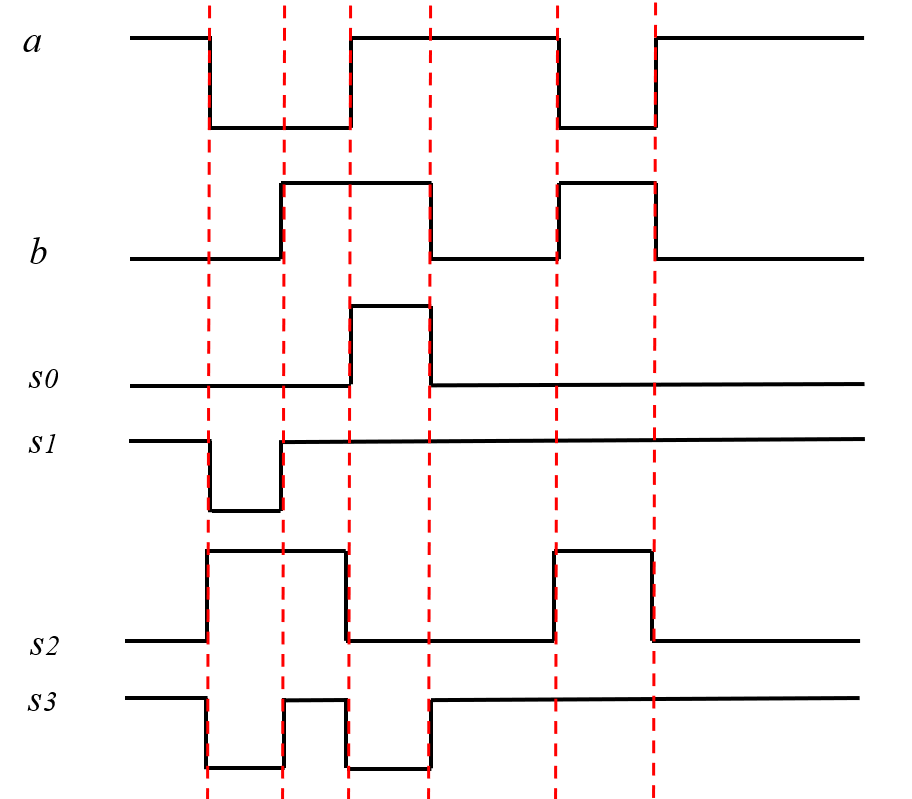

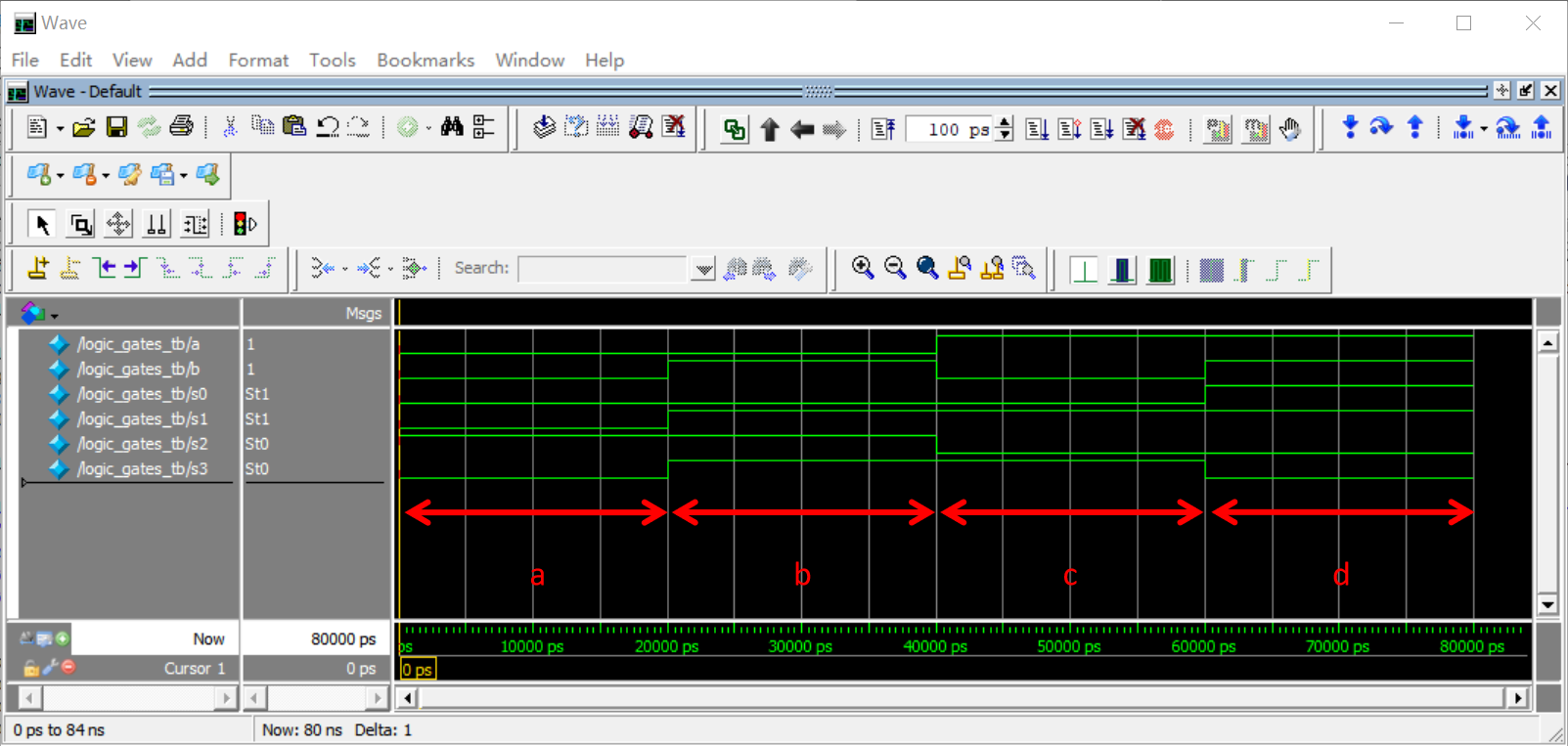

如下图举例显示了该逻辑门电路的波形图。

四、逻辑门电路设计

1. 创建一个新Quartus工程

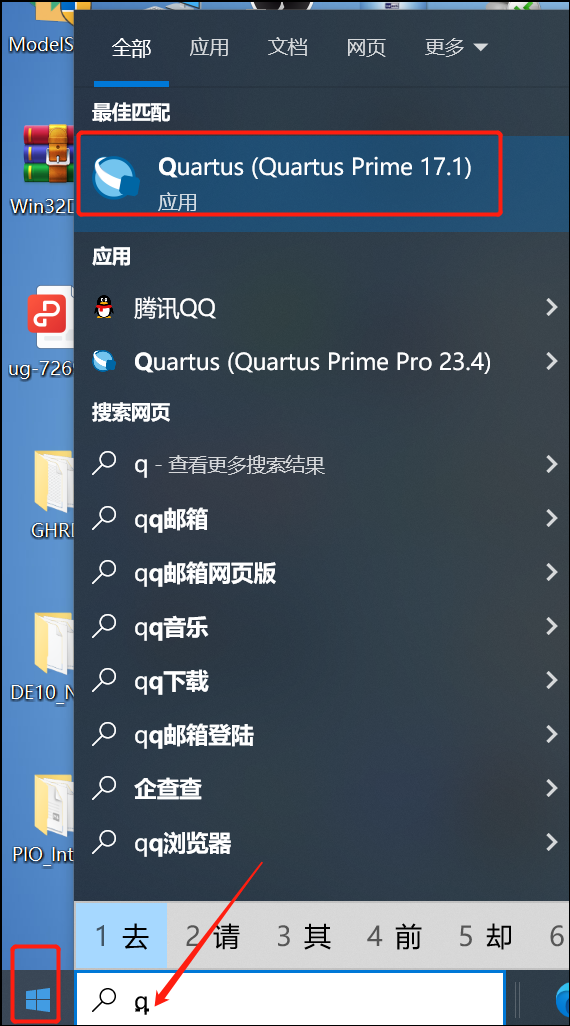

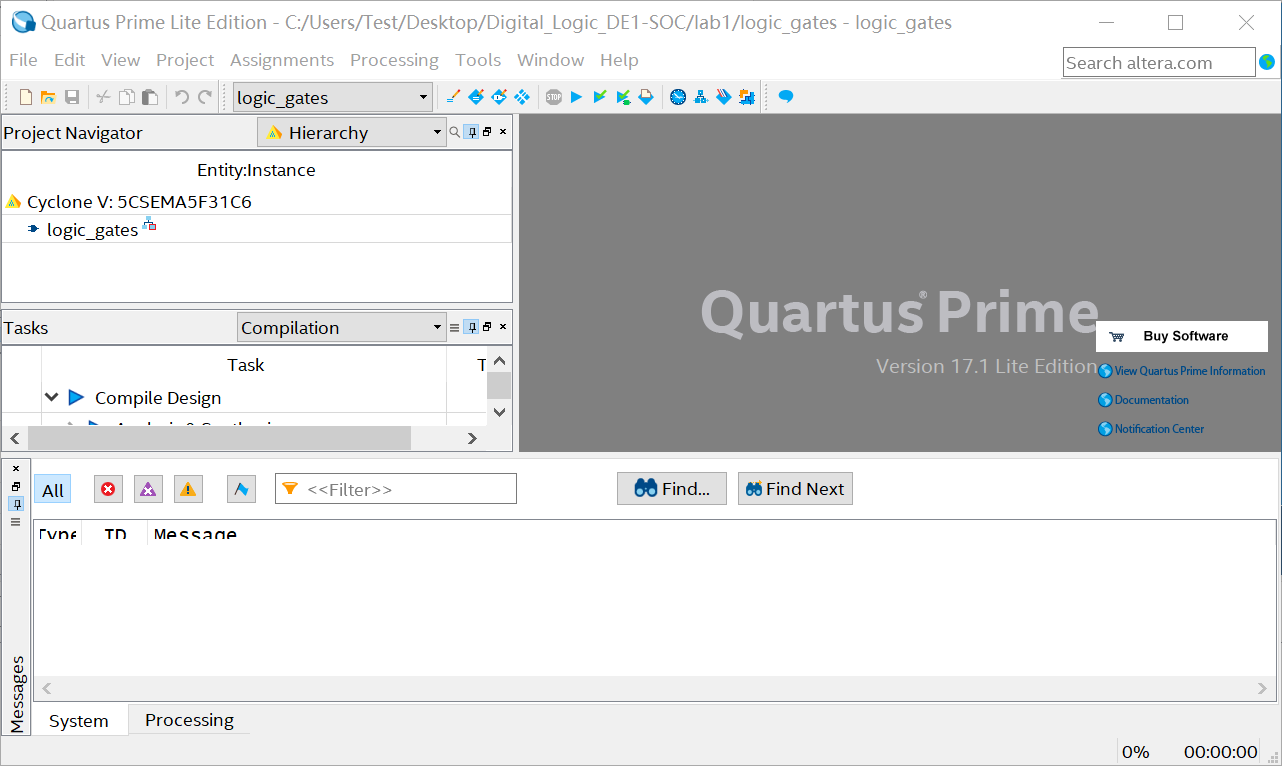

(1) 点击电脑右下角的开始菜单找到Quartus软件,双击Quartus (Quartus Prime 17.1)打开Quartus Prime软件。

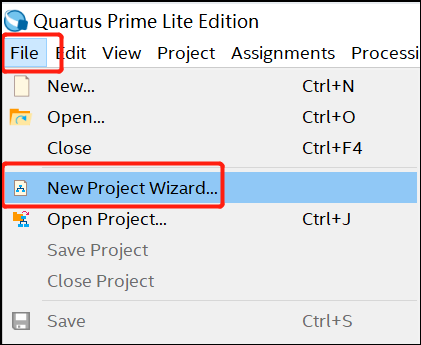

点击菜单File-->New Project Wizard弹出工程创建的对话框。

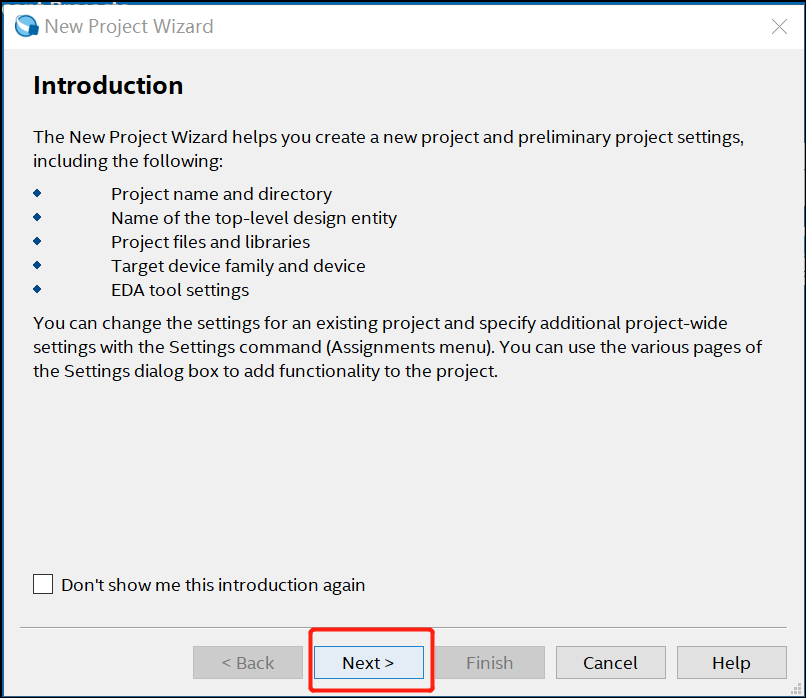

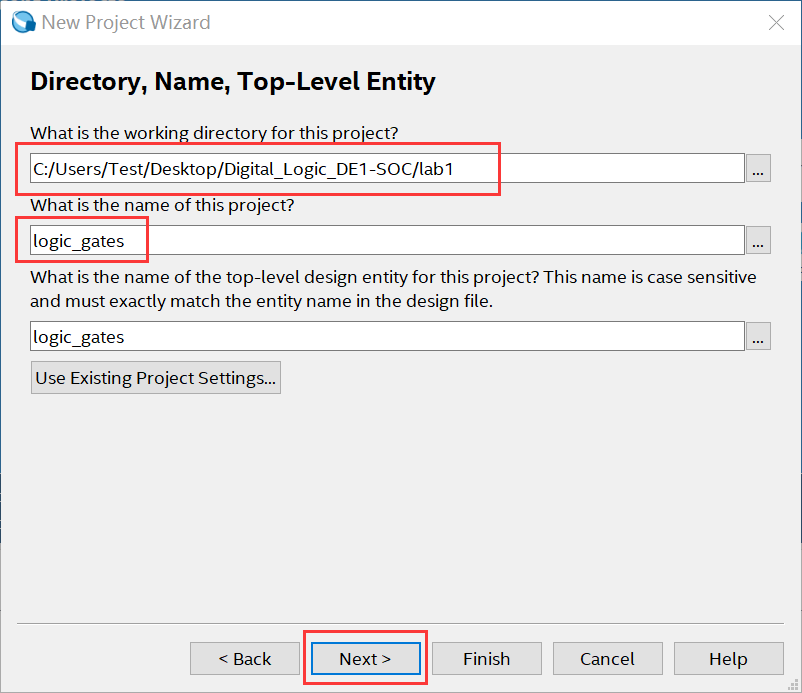

(2)在弹出的对话框中点击Next。

(3)在您的DE1-SOC 工作文件夹下创建一个lab1的文件夹,并将工程路径指向该文件夹,且工程的名称也命名lab1。

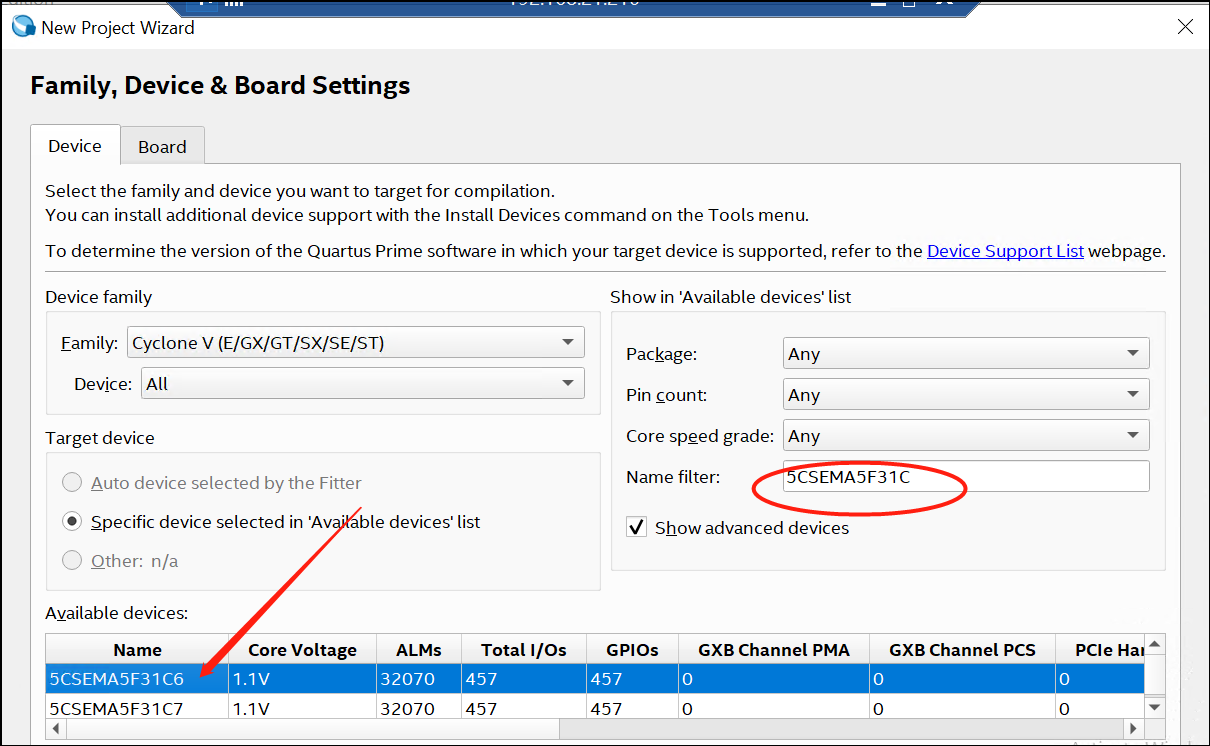

(4)连续点击3次Next得到如下界面,通过器件过滤器筛选选中DE1-SoC的Cyclone V 5CSEMA5F31C6器件。

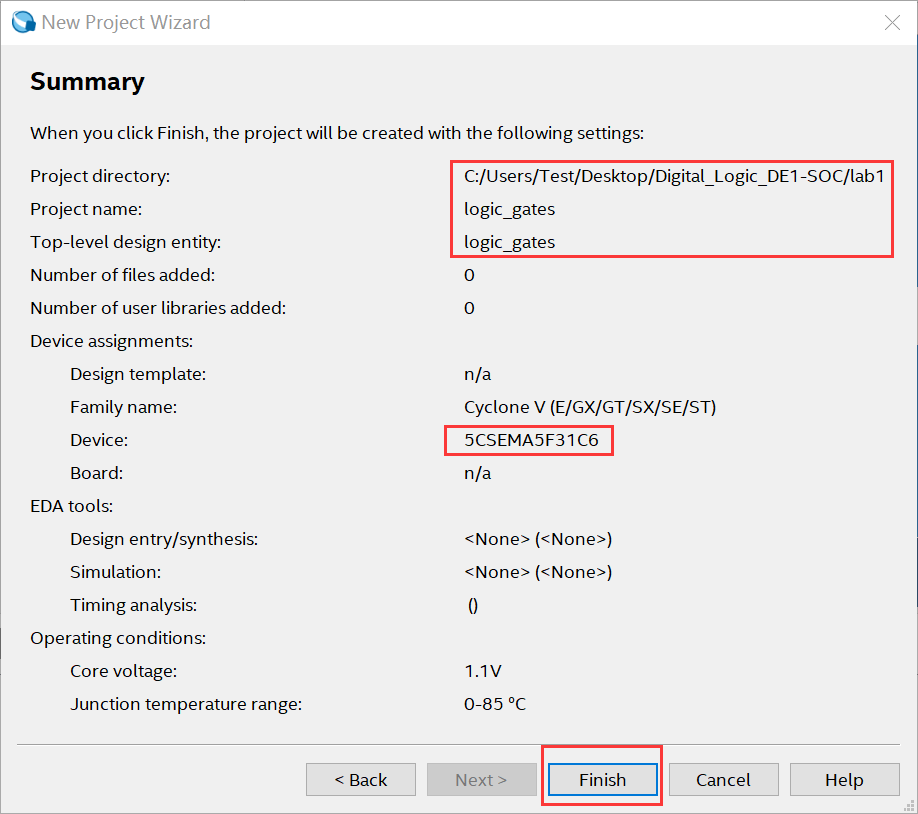

(5)点击Next两次后得到工程的生成报告窗口,检查无误后点击Finish完成工程创建。

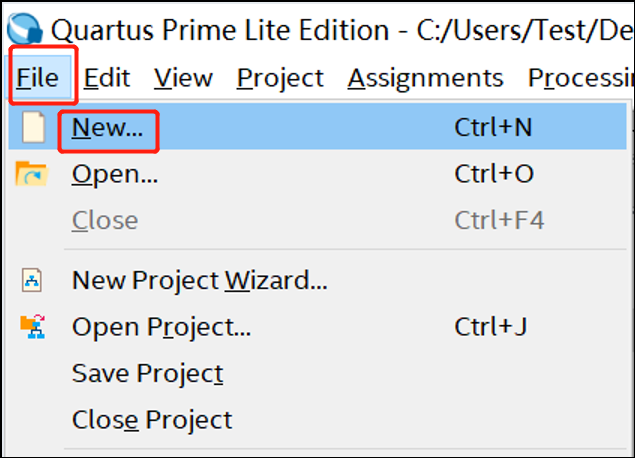

(6)点击Quartus菜单File——New新建一个.v文件。

(7)选择Verilog HDL File,然后点击OK完成top文件.v文件的创建。

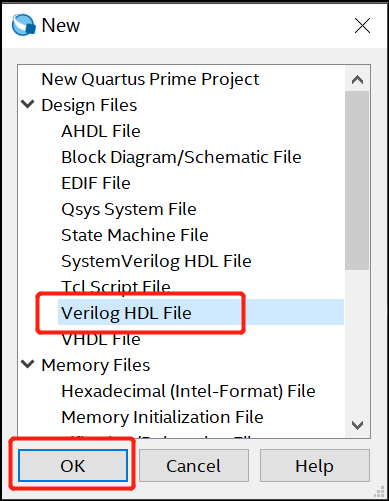

(8)在新建的空白.v文件敲入如下Verilog代码,然后点击保存,文件名保持默认的logic_gates.v即可。

module logic_gates( //模块开头以module开始,模块命名为logic_gates

input a, //1位数据输入信号a

input b, //1位数据输入信号b

output s0, //1位输出信号s0

output s1, //1位输出信号s1

output s2, //1位输出信号s2

output s3 //1位输出信号s3

);

assign s0 = a & b; //将与逻辑运算结果赋值给输出信号s0

assign s1 = a | b; //将或逻辑运算结果赋值给输出信号s1

assign s2 = ~ a; //将非逻辑运算结果赋值给输出信号s2

assign s3 = a ^ b; //将异或逻辑运算结果赋值给输出信号s3

endmodule //模块以endmodule结束

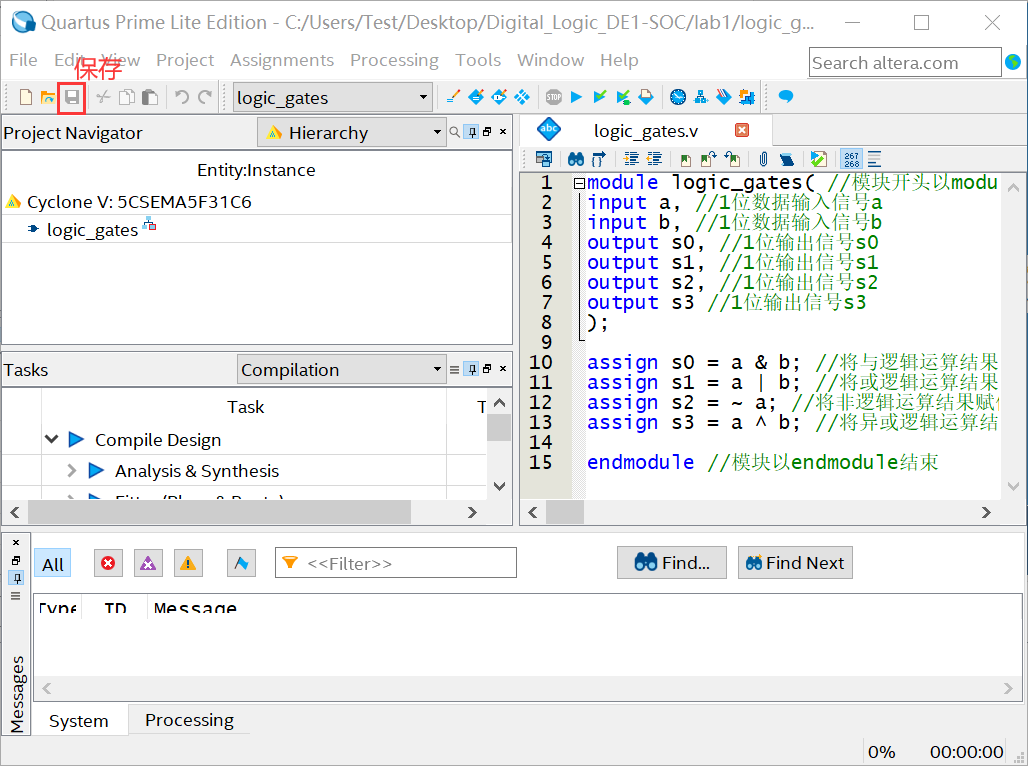

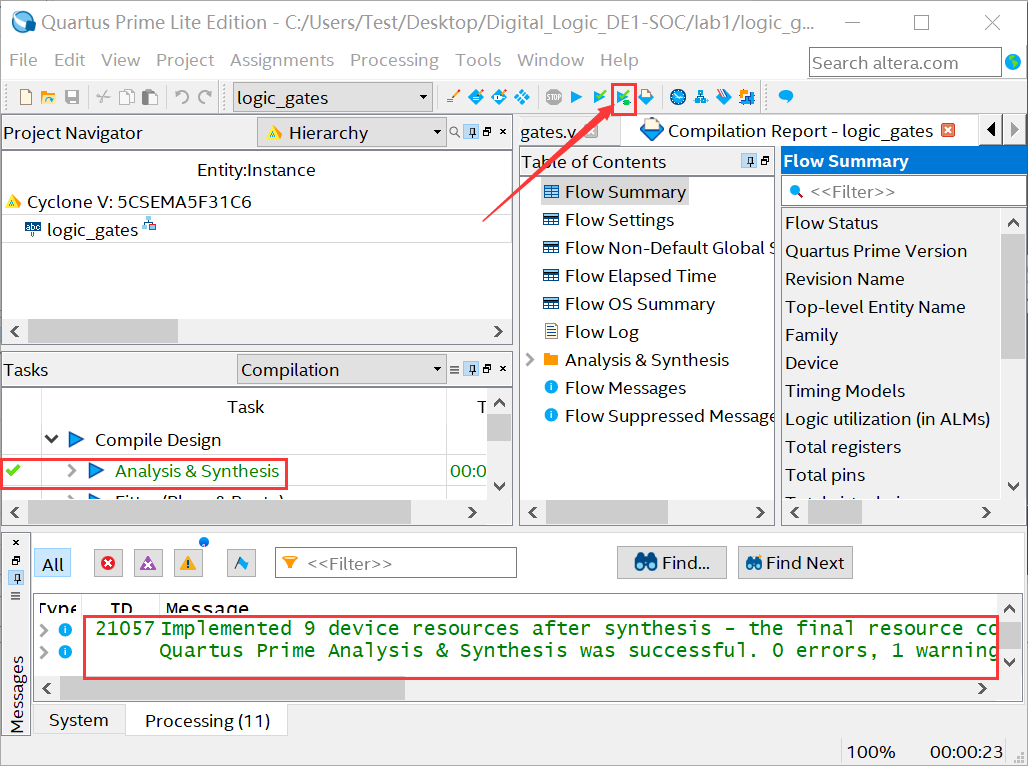

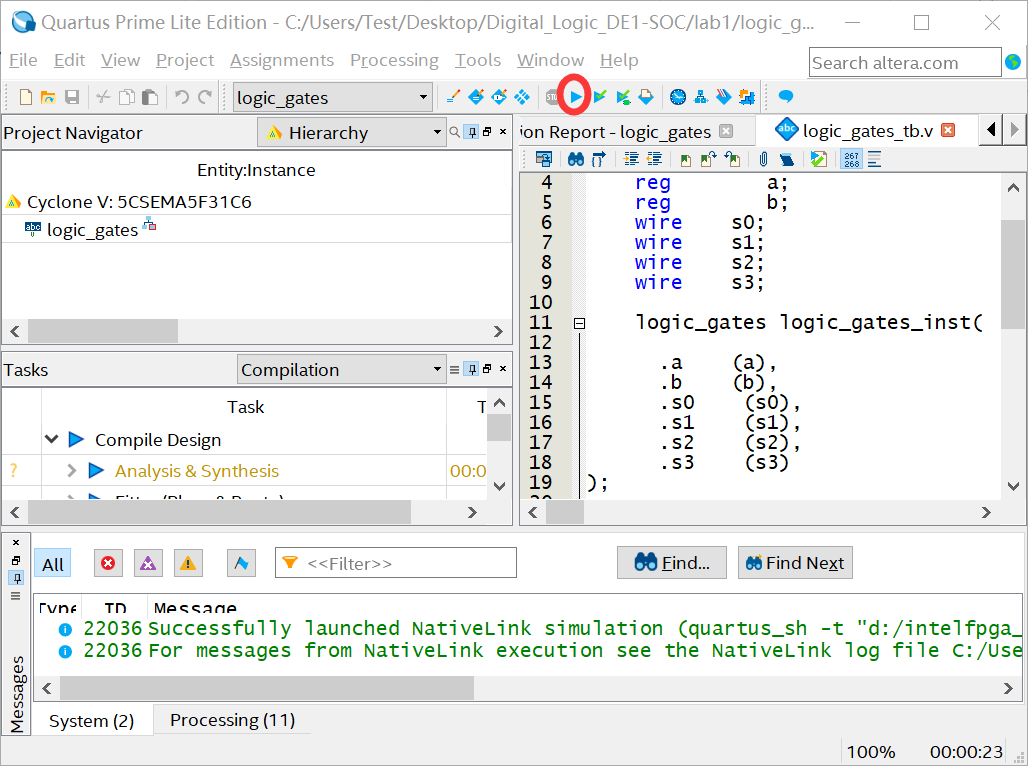

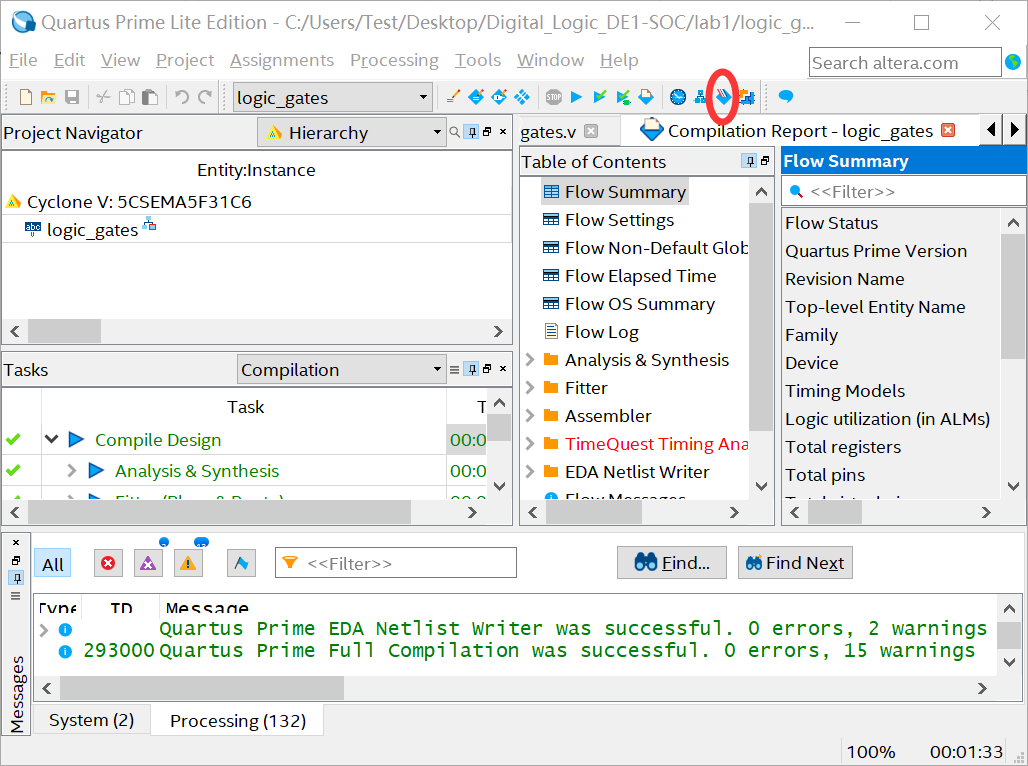

(9)点击Quartus软件工具栏的Processing --> Start --> Start Analysis & Synthesis或点击

![]()

按钮对Verilog HDL代码执行语法检查和综合,该过程成功完成之后在Quartus软件窗口的Tasks页面中,Analysis & Synthesis旁边将显示一个绿色勾型标记,如下图所示。如果在该过程中提示有错误,请检查Verilog HDL代码语法,确保与上述代码块完全一致。

2. 对电路进行仿真

对Verilog HDL代码进行语法分析与综合确认无误之后,就可以对设计进行功能仿真(也称之为前仿真)了,这个操作是为了验证电路逻辑功能是否符合设计要求。通过功能仿真可以及时发现设计中的错误,在系统设计前期即可完成修改,提高设计可靠性。

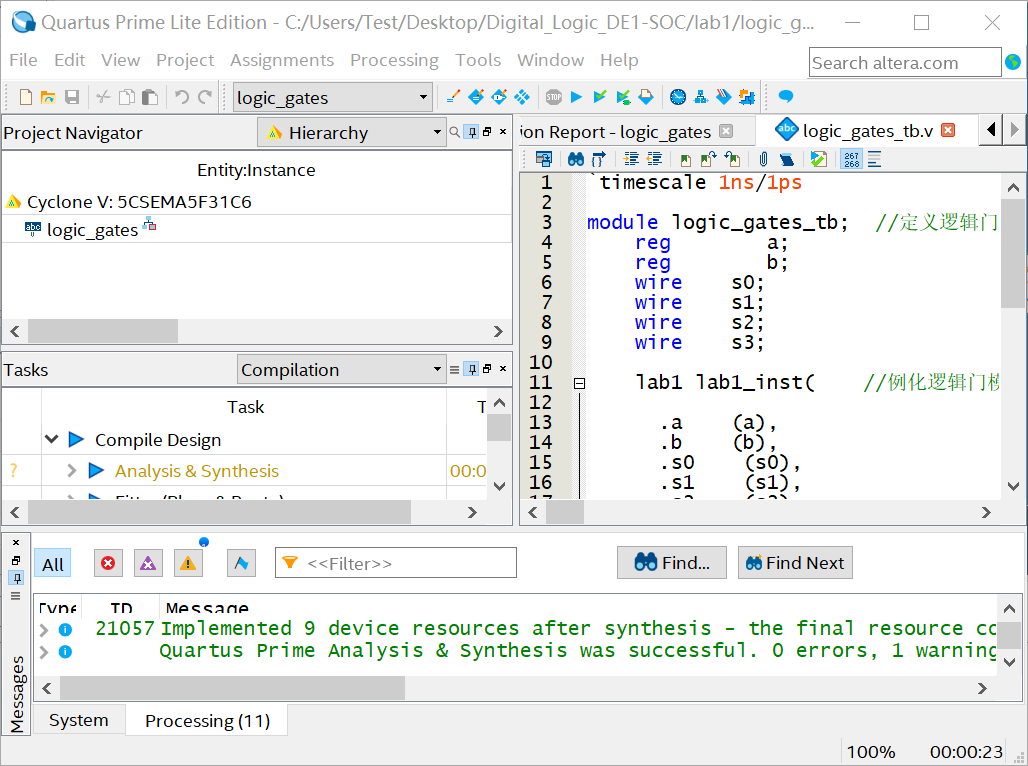

(1) 点击Quartus软件工具栏的File --> New --> Verilog HDL File,点击OK,这样就新建了一个空白Verilog HDL文件,再点击File --> Save As ...保存,命名为logic_gates_tb.v。然后将如下仿真代码保存到logic_gates_tb.v文件中。

`timescale 1ns/1ps

module logic_gates_tb; //定义逻辑门测试仿真模块,包含输入信号a,b以及输出信号s0,s1,s2,s3reg a;reg b;wire s0;wire s1;wire s2;wire s3; logic_gates logic_gates_inst( //例化逻辑门模块

.a (a),.b (b),.s0 (s0),.s1 (s1), .s2 (s2), .s3 (s3)

);

initial begin //设置输入信号a,b的四种不同输入组合// a = 1'b0;b = 1'b0;# 20;// a = 1'b0;b = 1'b1;# 20;//a = 1'b1;b = 1'b0;# 20;//a = 1'b1;b = 1'b1;# 20;end

endmodule

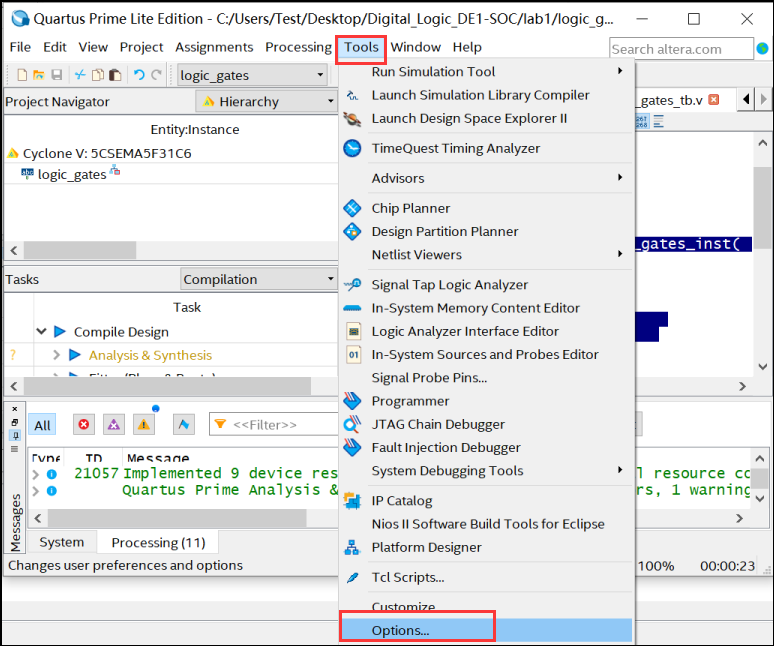

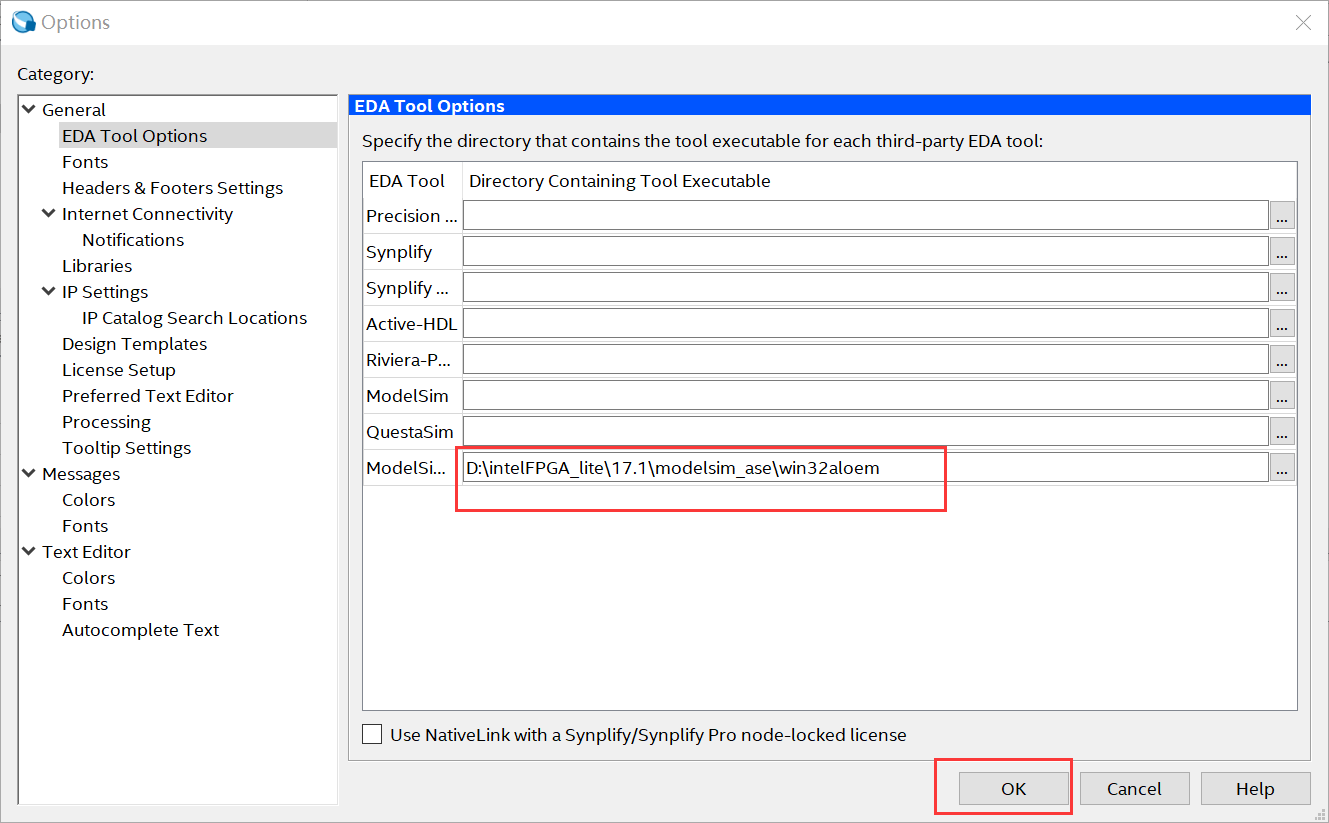

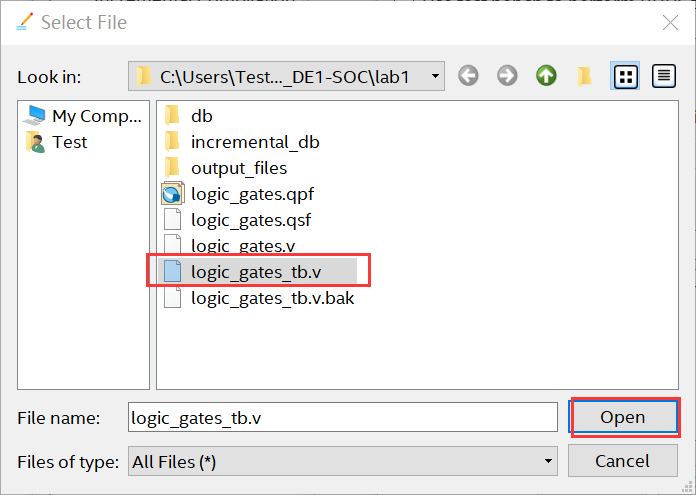

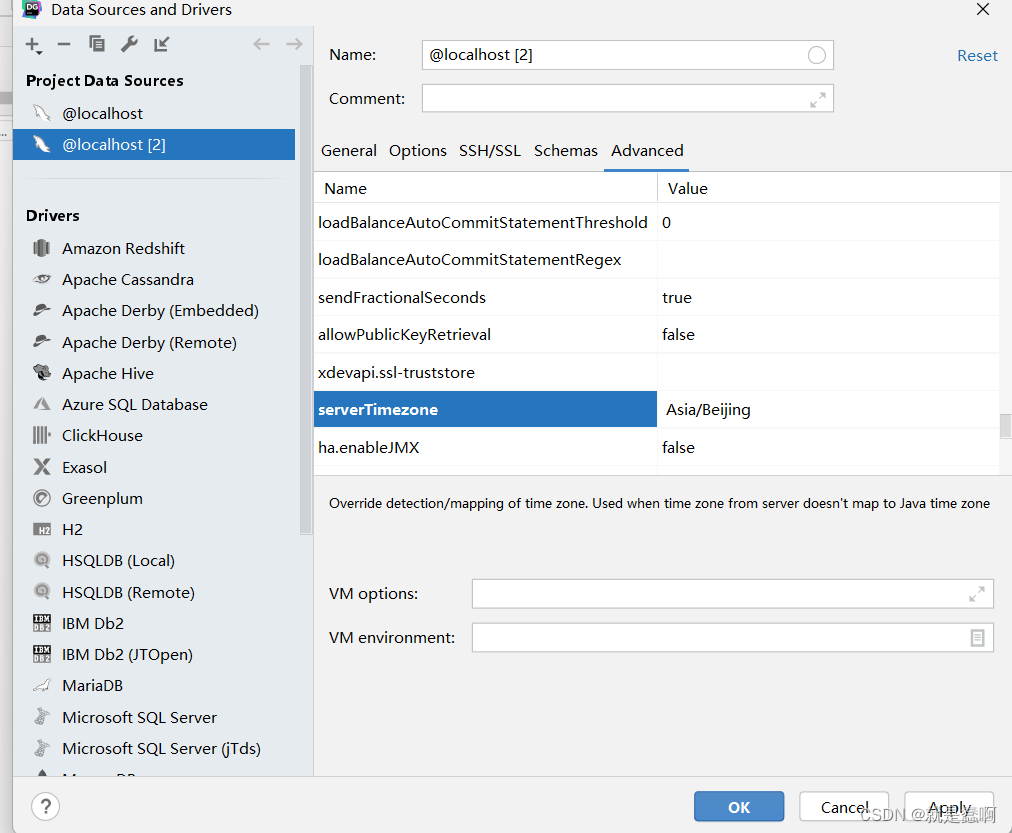

(2)要先将Modelsim 的安装路径设置一下,然后Quartus系统才可以自动调用指定的仿真工具。依次点击Quartus菜单Tools——Options...

将仿真工具路径指定到...intelFPGA_lite\17.1\modelsim_ase\win32aloem。

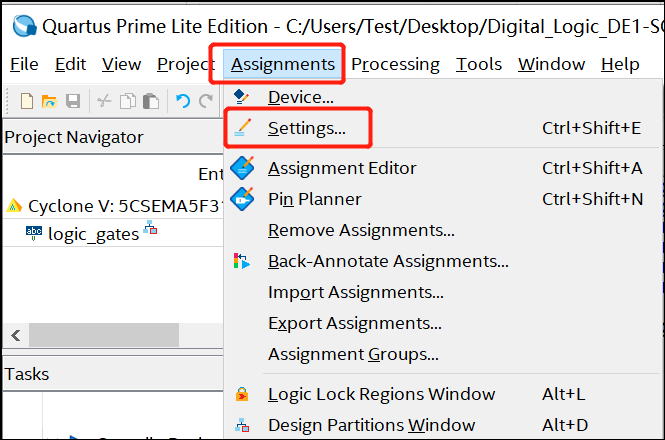

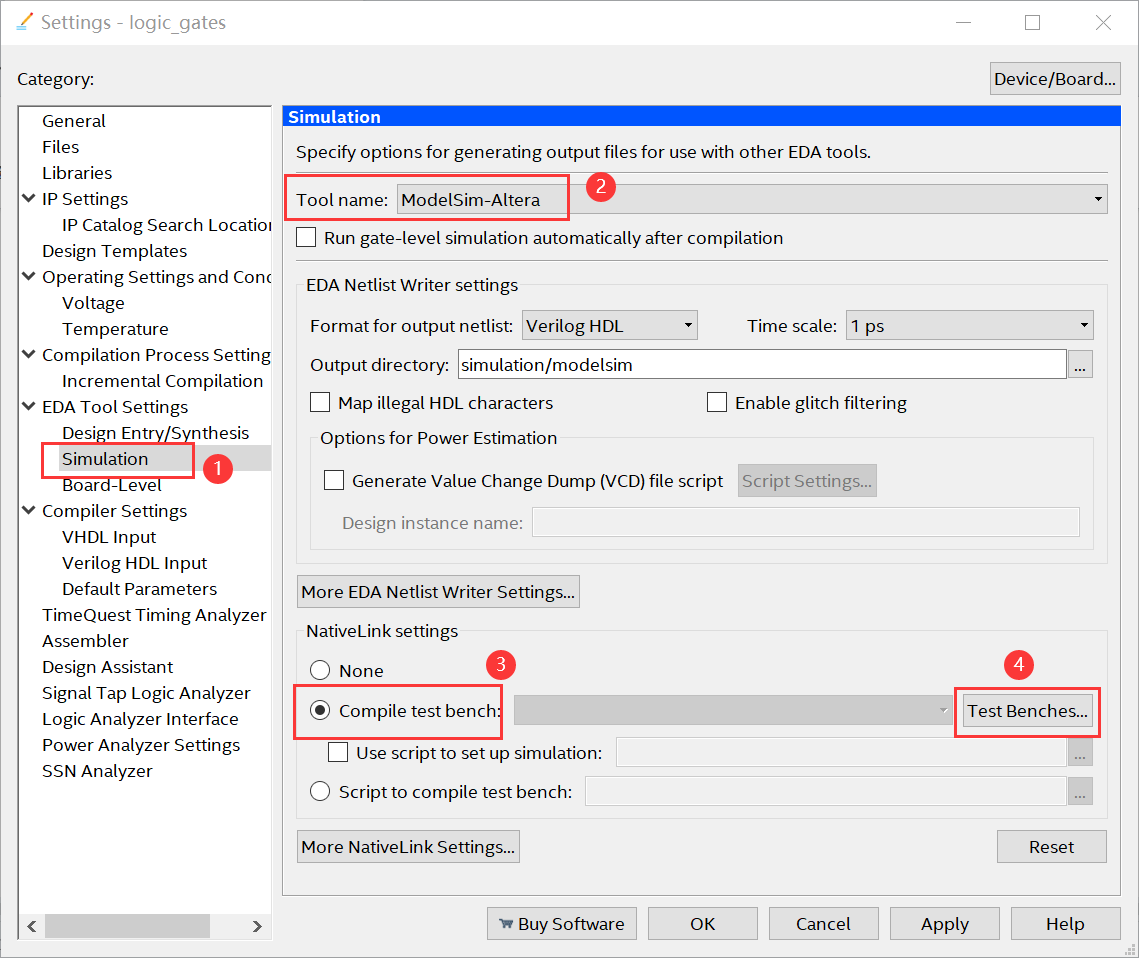

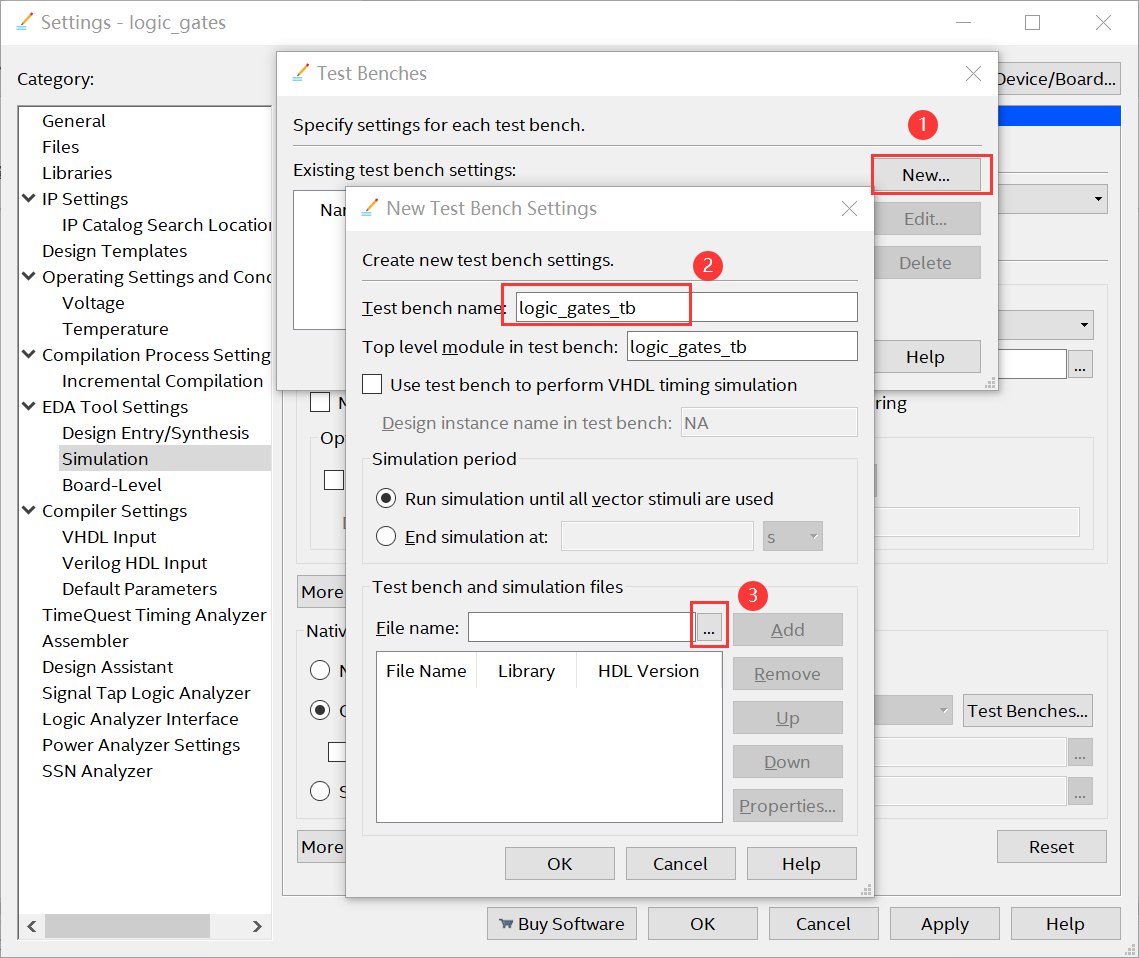

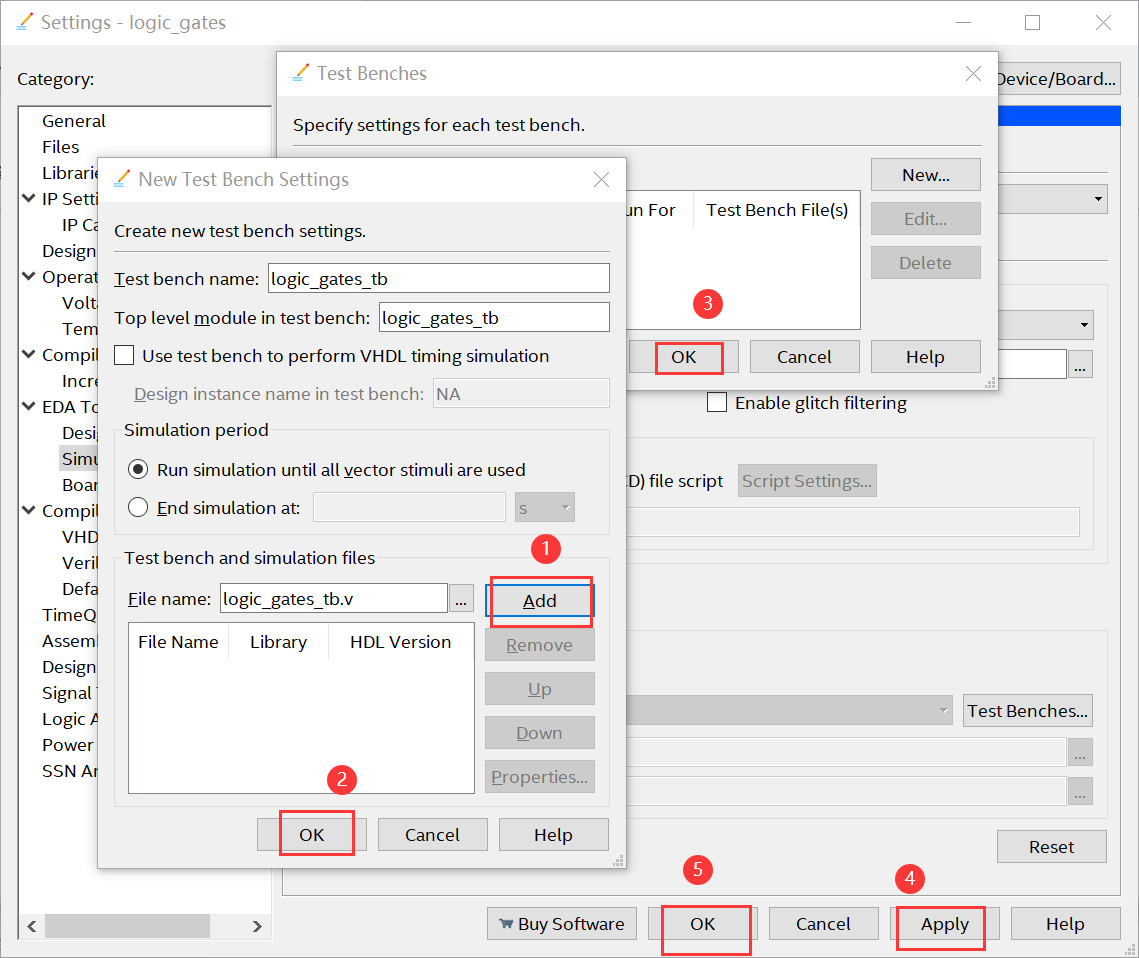

(3)点击Quartus软件工具栏的Assignments --> Settings,在弹出的Settings窗口中,选中Simulation栏,Tool name选择ModelSim-Altera,设置Quartus自动调用ModelSim。然后选择添加Test Bench文件。

点击Add和OK后,再点击OK、Aplly和OK完成仿真工具和仿真文件的设置。

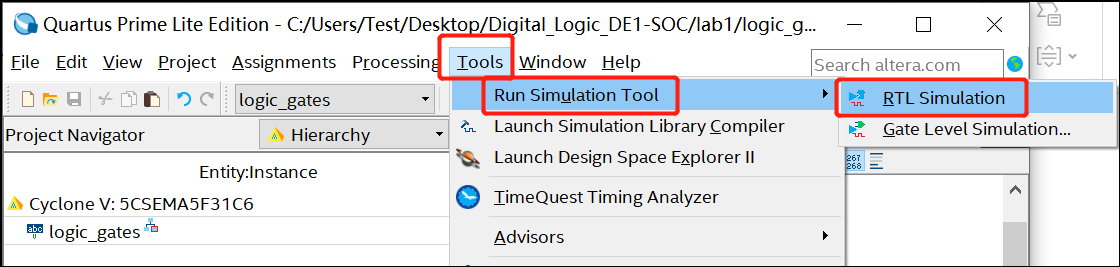

(4)击Quartus软件工具栏的Tools --> Run Simulation Tool --> RTL Simulation启动ModelSim仿真。

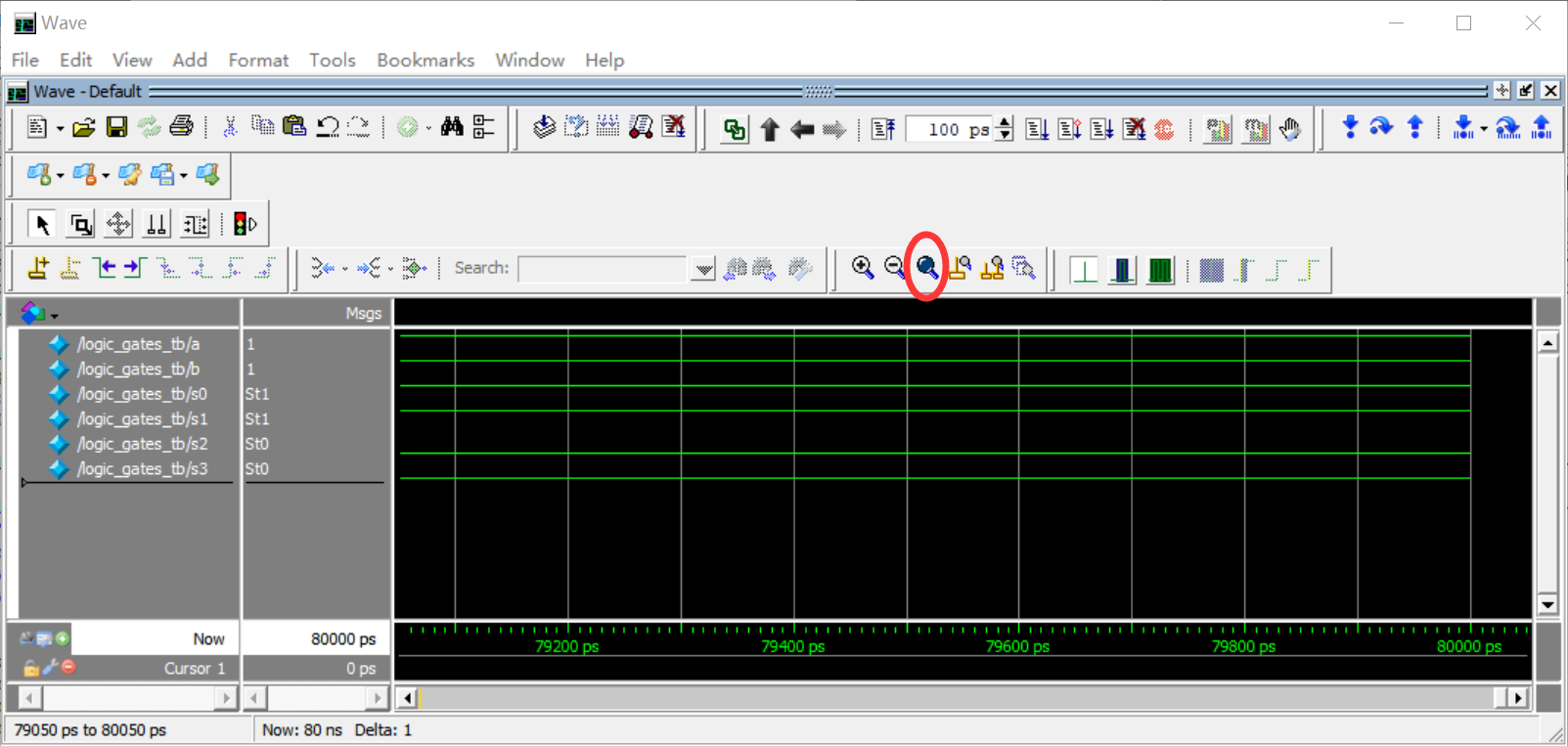

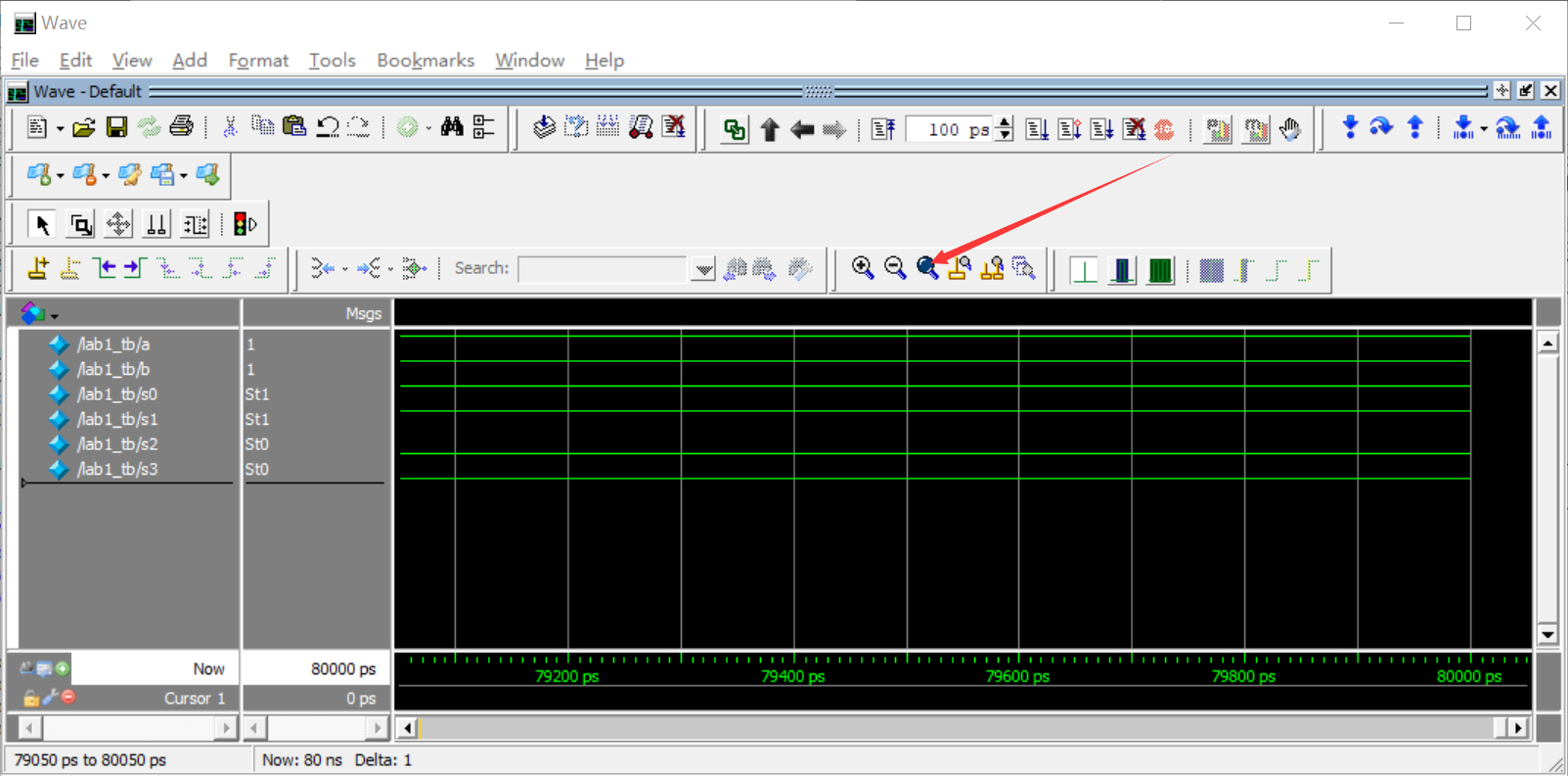

(5)点击Wave选项卡切换到仿真波形窗口此时还看不到完整的仿真波形,可以通过点击下图所示的Zoom Full按钮来显示完整的波形。

从上面波形图可以看出:

a. 当输入a=0,b=0时,四个输出分别为s0=0,s1=0,s2=1,s3=0;

b. 当输入a=0,b=1时,四个输出分别为s0=0,s1=1,s2=1,s3=1;

c. 当输入a=1,b=0时,四个输出分别为s0=0,s1=1,s2=0,s3=1;

d. 当输入a=1,b=1时,四个输出分别为s0=1,s1=1,s2=0,s3=0。

结果与预期一致,说明本实验要求的逻辑门电路已实现。

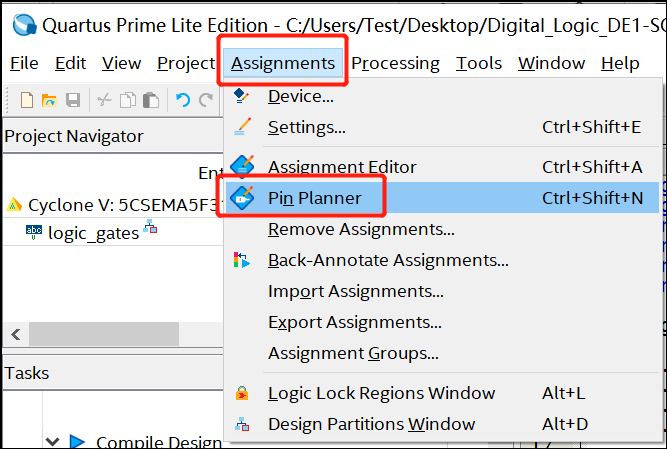

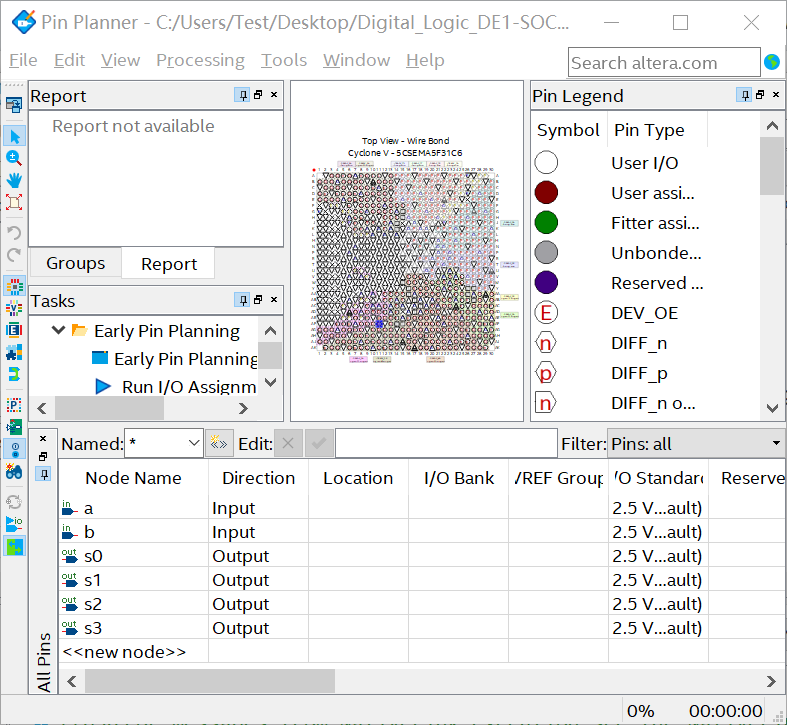

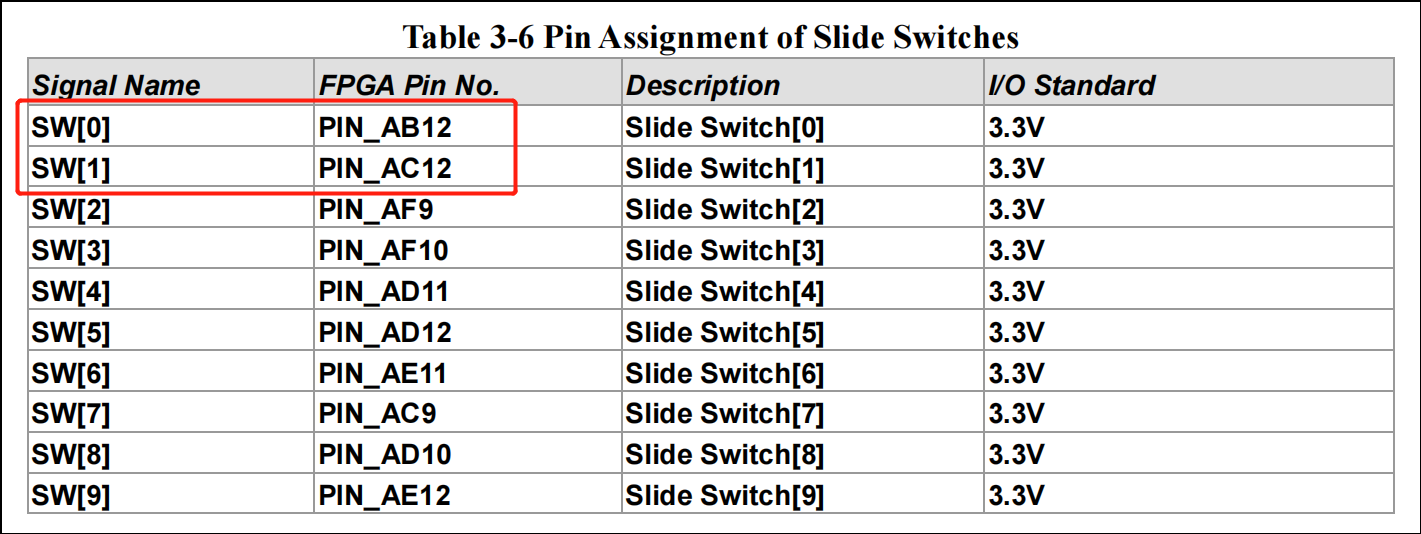

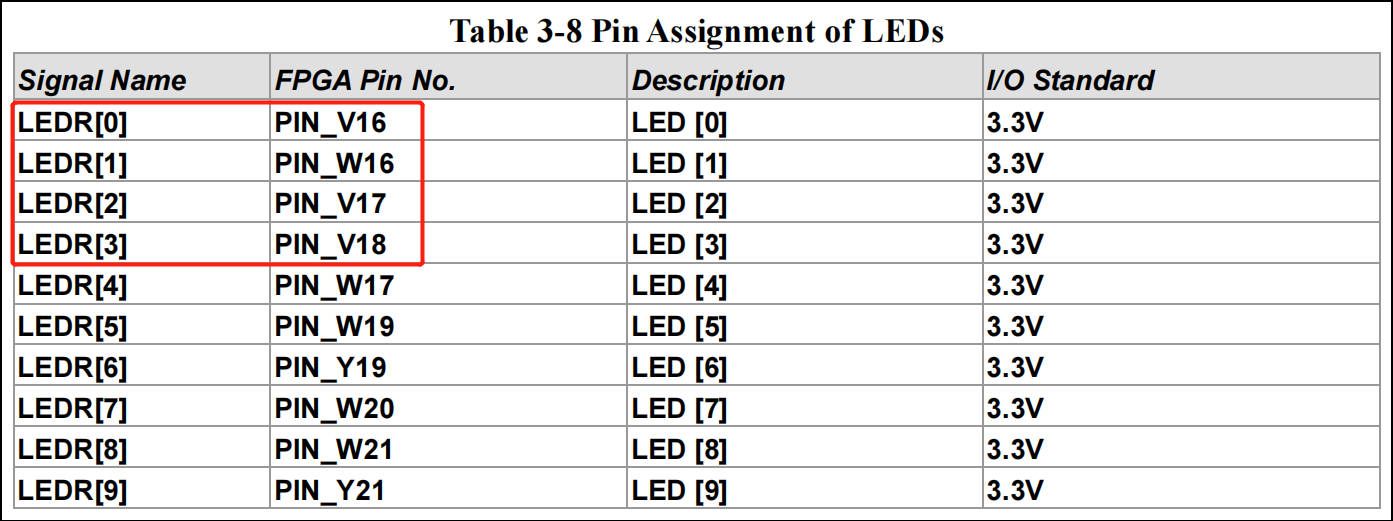

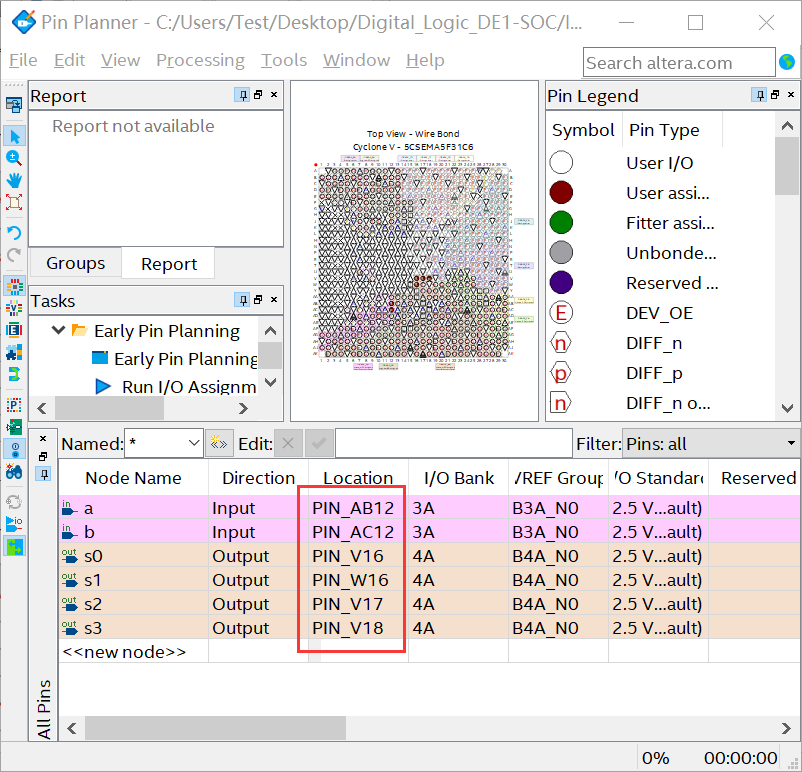

3. 引脚分配和全编译

一般功能仿真也可以跳过不做,在分析和综合的步骤完成以后,就可以进行FPGA引脚分配了。点击Assignments——Pin Planner弹出引脚分配窗口,按照DE1-SOC 用户手册或者电路图进行引脚分配。

关于引脚分配信息可以查看DE1-SoC_v.5.1.3_HWrevF.revG_SystemCD\UserManual\DE1-SoC_User_manual.pdf第 25、26页或者E:\CD_Package\01-DE1-SoC\DE1-SoC_v.5.1.3_HWrevF.revG_SystemCD\Schematic\DE1-SoC.pdf的第3页。

这里,a和b两个操作数可以通过拨码开关SW0、SW1来控制,s0到s3信号分别输出到LEDR0到LEDR3。

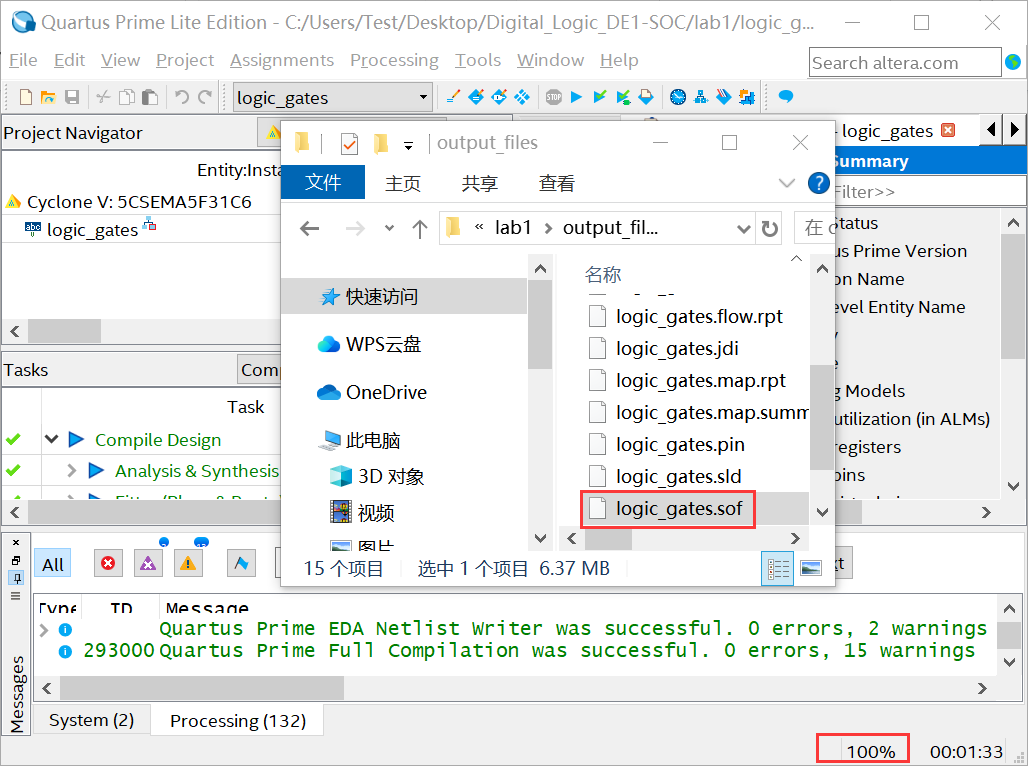

关闭Pin Planner窗口,点击如下按钮进行工程的全编译。

如果编译成功,Quartus窗口右下角会显示100%,同时会在...lab1\output_files文件夹下生成一个logic_gates.sof文件。

4. 下板测试

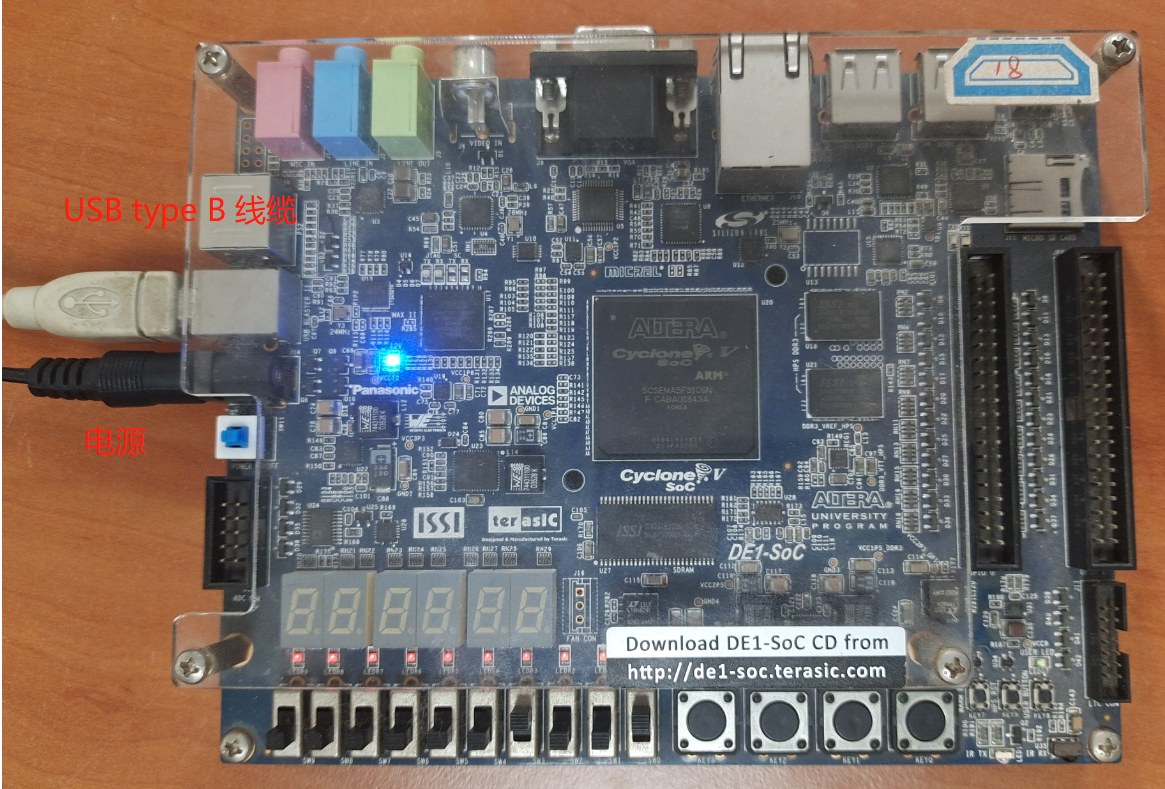

(1)将DE1-SOC开发板和电脑用板子自带的白色USB type B 线缆连接起来。给DE1-SOC插上电源并按SW11按键进行开机。

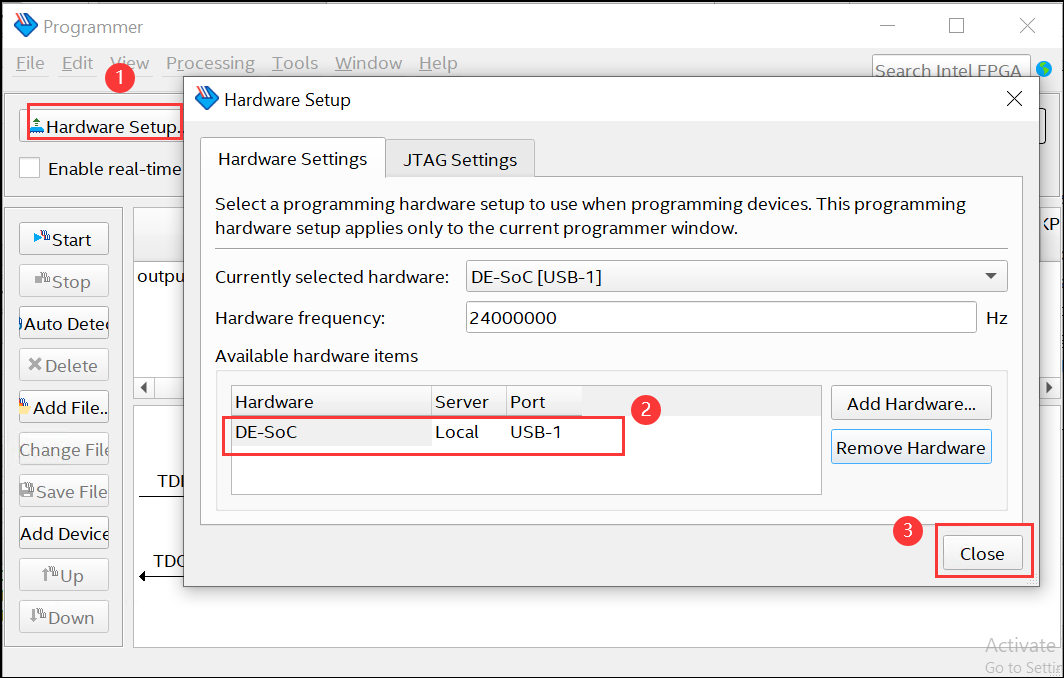

(2)打开Quartus的Programmer工具,点击Hardware Setup,选择DE-SOC[USB-1]端口。

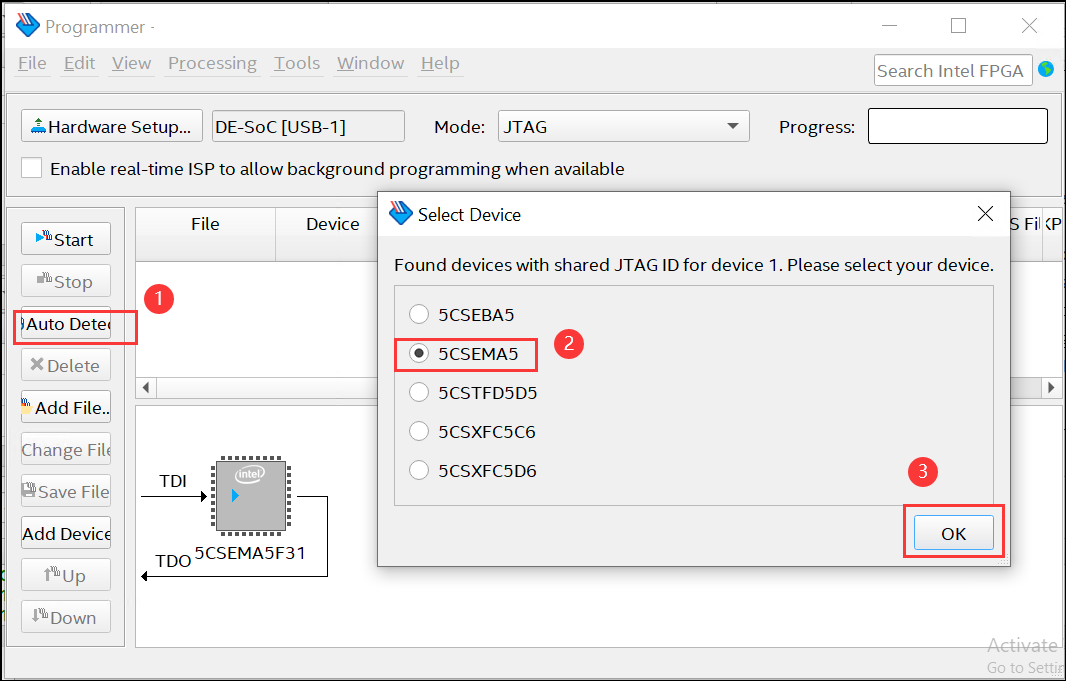

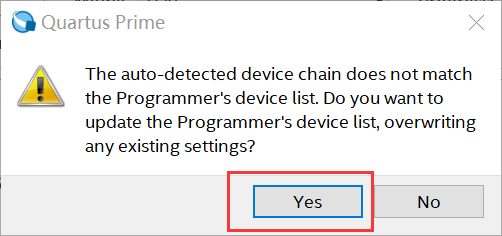

(3)点击Auto Detect,选择DE1-SOC对应的FPGA器件5CSEMA5。

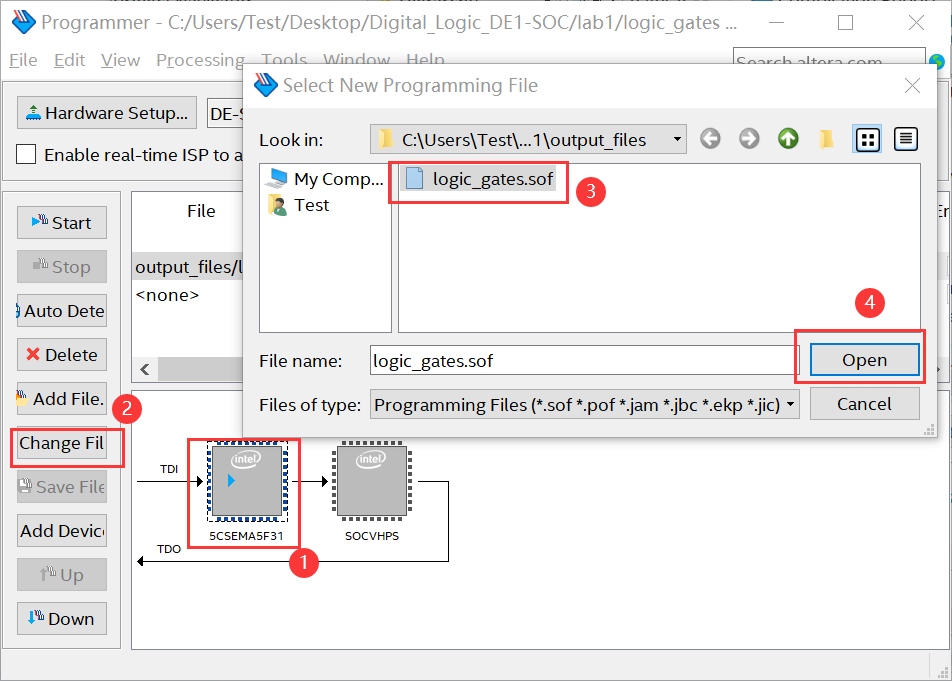

(4)这时会出现两个器件(5CSEMA5和SOCHPS),右击器件5CSEMA5,选择Change File...,然后选择...\lab1\output_files路径下的logic_gates.sof文件。

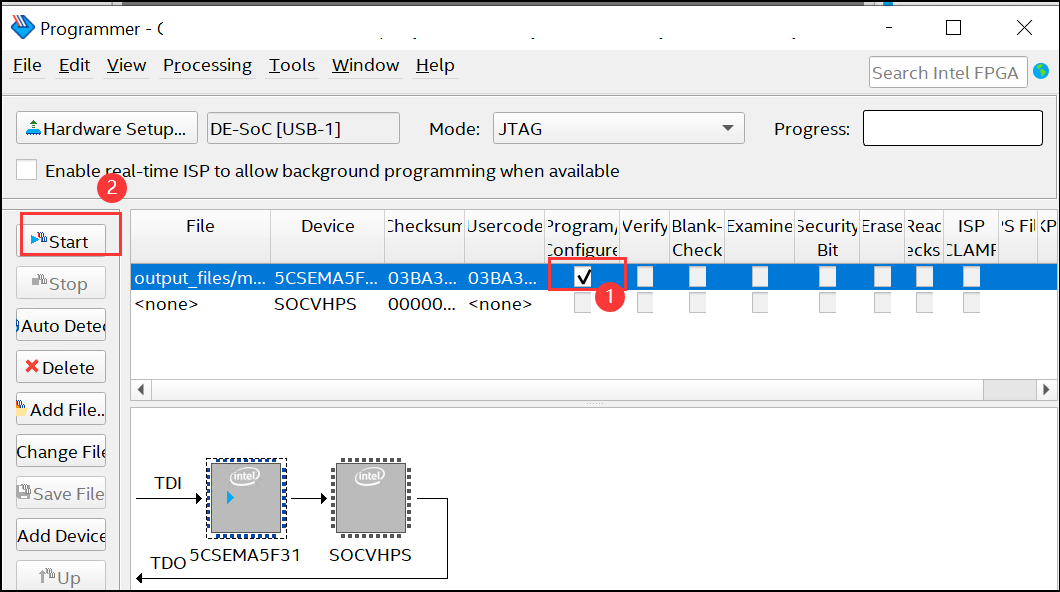

(5) 然后勾选Program/Configure复选框,点击Start按钮开始配置FPGA。

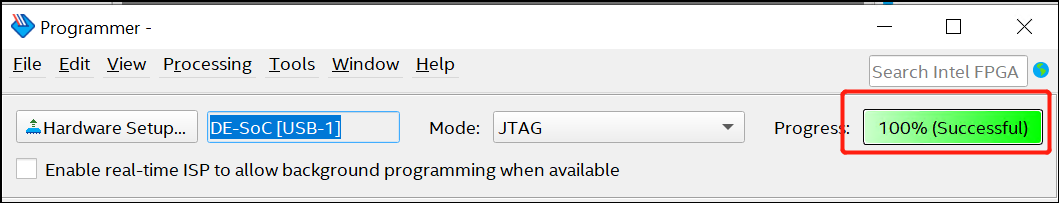

进度条显示100%代表FPGA 配置成功。

(6)拨动SW0和SW1观察LEDR0-3的现象。

SW1、SW0分别为00:

SW1、SW0分别为01:

SW1、SW0分别为10:

SW1、SW0分别为11:

相关文章:

第一篇 逻辑门(与门、或门、非门、异或门)

一、实验目的 了解DE1-SOC开发板一些外设。 掌握常用组合逻辑门电路的基本原理。 学习Verilog HDL的基本语法。 学习使用ModelSim工具对设计的电路进行仿真,包括编写Testbench仿真代码,以及ModelSim工具的使用。 熟悉使用Quartus软件从创建Quartus工…...

车牌号码智能监测识别摄像机

车牌号码智能监测识别摄像机是一项革命性的技术,为交通管理和安全提供了全新的解决方案。这种摄像机利用先进的人工智能和图像识别技术,能够实时监测道路上的车辆,并准确识别车辆的车牌号码,为交通管理和安全提供了强有力的支持。…...

Python局部变量:深入探索与实战应用

Python局部变量:深入探索与实战应用 在Python编程中,局部变量是一个至关重要的概念。它们被定义在函数或方法内部,并且只在定义它们的那个特定的代码块中可见。然而,局部变量的使用并不总是那么简单明了,尤其是当涉及…...

Java面试八股之怎么降低锁竞争

怎么降低锁竞争 减少锁的持有时间: 尽量缩短线程持有锁的时间,只在必要时才获取锁,一旦操作完成立即释放锁。可以通过将同步代码块的范围缩小到最小必要程度来实现,避免在锁保护的代码块中执行耗时操作或等待操作,比如…...

数组的操作方法

数组的操作方法 forEach 循环 数组的私有方法 7个内置操作方法 1.push 尾部添加 2.pop 尾部删除 3.shift 头部删除 4.unshift 头部添加 5.splice 删除 替换 插入(本质是删除 返回的是删除的元素组成的数组[因为可以删除多个…...

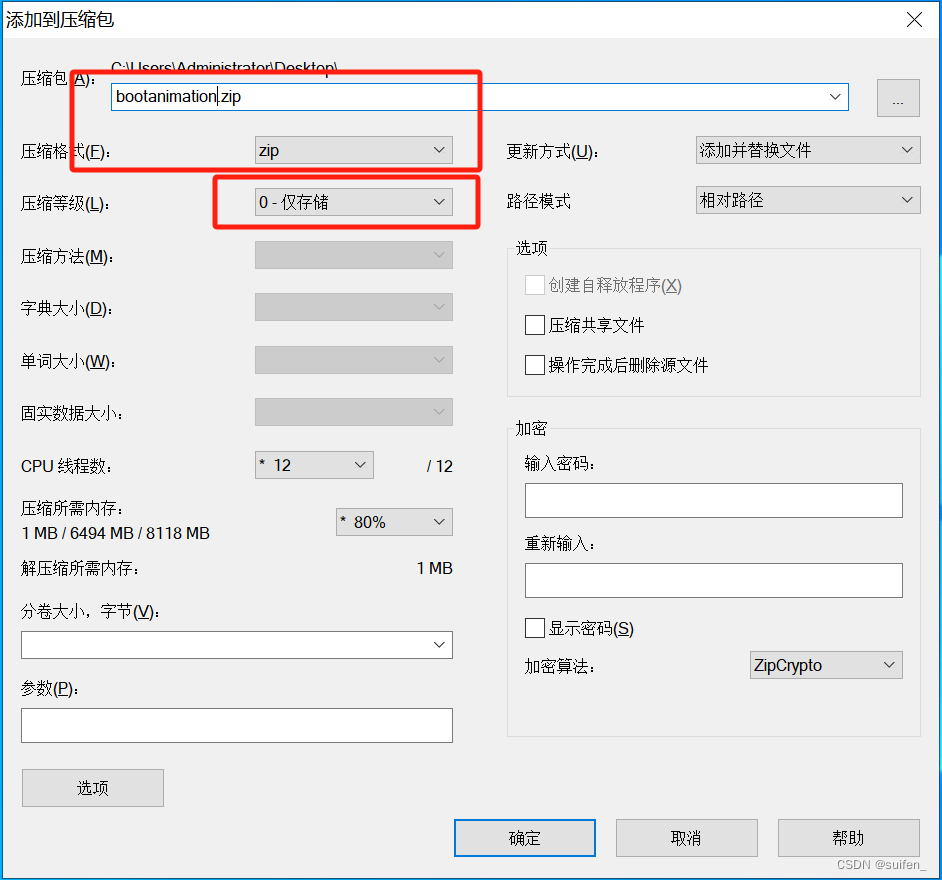

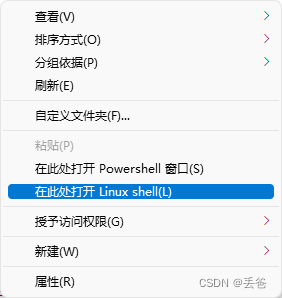

RK3588 Android13添加开机logo或开机动画

wzhlenkeng-HP-Pro-Tower-ZHAN-99-G9-Desktop-PC:/media/extern_sda/wzh/rk3588_android/device/rockchip/rk3588$ git show commit e8da2099dccfed7f7b348c2e324d9c3d3e555d39 (HEAD) Author: wzh <wuzenghonglenkeng.com> Date: Tue Jun 4 09:53:48 2024 0800添加开…...

JVM学习-监控工具(一)

使用数据说明问题,使用知识分析问题,使用工具处理问题 无监控,不调优! 命令行工具 在JDK安装目录下,可以查看到相应的命令行工具,如下图 jps(Java Process Status) 显示指定系统内所有的Hotpot虚拟机…...

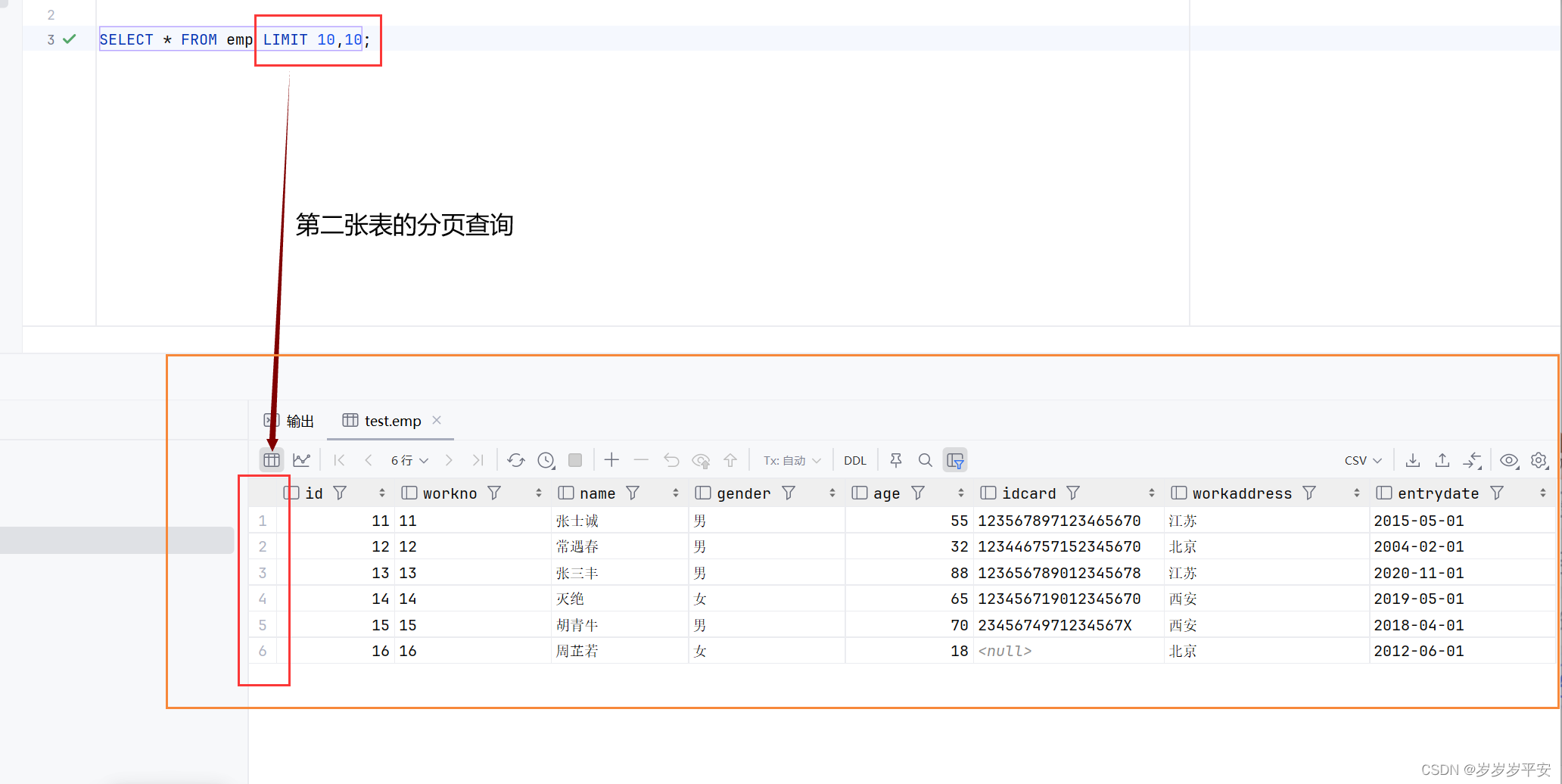

基础—SQL—DQL(数据查询语言)分页查询

一、引言 上一篇博客学习了排序查询,这次来讲查询的最后一个部分:分页查询。 涉及到的关键字是:LIMIT 。 二、DQL—分页查询 对于分页,不管以后做的是传统的管理系统还是做互联网的项目,基本上都会遇到分页查询的操…...

独立开发者通过这100种方式赚钱

独立开发者可以通过多种方式赚钱: 销售游戏:独立开发者可以通过 Steam、Itch.io 和 App Store 等平台直接向消费者销售他们的游戏。 他们还可以在自己的网站上出售游戏的实体副本或数字下载。 提供游戏内购买:一些游戏包括微交易或游戏内购…...

gitlab服务器迁移(亲测有效)

描述:最近公司迁移gitlab,我没有迁移过,经过网上查找资料最终完成迁移,途中也遇到挺多坑和两个问题,希望能帮到你。 新服务器安装gitlab 注意:新服务器gitlab版本也需要和旧版本一致。 首先查看原Gitlab…...

【刷题(12)】图论

一、图论问题基础 在 LeetCode 中,「岛屿问题」是一个系列系列问题,比如: 岛屿数量 (Easy)岛屿的周长 (Easy)岛屿的最大面积 (Medium)最大人工岛 (Hard&…...

FASTGPT:可视化开发、运营和使用的AI原生应用

近年来,随着人工智能(AI)技术的迅猛发展,AI的应用逐渐渗透到各行各业。作为一种全新的开发模式,AI原生应用正逐步成为行业的焦点。在这方面,FASTGPT无疑是一款颇具代表性的产品。本文将详细介绍FASTGPT的设…...

代码随想录-Day27

39. 组合总和 给你一个 无重复元素 的整数数组 candidates 和一个目标整数 target ,找出 candidates 中可以使数字和为目标数 target 的 所有 不同组合 ,并以列表形式返回。你可以按 任意顺序 返回这些组合。 candidates 中的 同一个 数字可以 无限制重…...

TalkingData数据统计:洞察数字世界的关键工具

TalkingData数据统计:洞察数字世界的关键工具 在数字化时代,数据已成为推动社会进步和商业决策的核心动力。TalkingData作为国内领先的移动数据服务平台,为众多企业提供了全面、精准的数据统计服务。本文将深入探讨TalkingData数据统计的应用…...

printf 一次性写

PWN里printf漏洞感觉很小,可发现居然理解的不全。 一般情况下,当buf不在栈内时,就不能直接写指针。这时候需要用到rbp链或者argv链。一般操作是第一次改指针,第二次改数值。 DAS昨天这里只给了一次机会然后就exit了。今天ckyen给…...

【Axure高保真原型】切换查看大图列表

今天和大家分享切换查看大图列表的原型模板,我们可以点击列表里的图片查看对应的大图,点击左右箭头可以切换切换上一页或下一页,如果是首页会自动禁用左箭头,末尾页会自动禁用右箭头。这个原型模板是用中继器制作的,所…...

Ant-Design-Vue动态表头并填充数据

Ant-Design-Vue动态表头并填充数据 Ant-Design-Vue 是一个基于 Vue.js 的前端UI框架,它继承了 Ant Design 的优秀设计理念,并针对 Vue.js 进行了深度优化。在实际开发过程中,我们经常需要处理各种复杂的表格数据,而 Ant-Design-V…...

Python-匿名函数

一、概念 匿名函数造出来的是一个内存地址,且内存地址没有绑定任何名字,很快被当做垃圾清理掉。所以匿名函数只需要临时调用一次,而有名函数永久使用; 匿名函数一般和其他函数配合使用; # 有名函数def func(x, y):…...

探索Web3工具:正确使用区块链平台工具的秘诀

在当今日新月异的数字时代,区块链技术正以惊人的速度改变着我们的生活和工作方式。尤其对于那些想要踏入区块链世界的人来说,正确使用区块链平台工具至关重要。本文将向您介绍一些关键的Web3工具,并以TestnetX.com为例,展示如何利…...

器利而事善——datagrip 的安装以及连接mysql

一,安装 下载:直接到官网下载即可, 破解:这是破解连接:https://pan.baidu.com/s/11BgOMp4Z9ddBrXwCVhwBng ,提取码:abcd; 下载后,选择倒数第三个文件,打开da…...

Tensorflow-Cookbook高级特性解析:Partial Conv、Pixel Shuffle与Spectral Norm

Tensorflow-Cookbook高级特性解析:Partial Conv、Pixel Shuffle与Spectral Norm 【免费下载链接】Tensorflow-Cookbook Simple Tensorflow Cookbook for easy-to-use 项目地址: https://gitcode.com/gh_mirrors/te/Tensorflow-Cookbook Tensorflow-Cookbook是…...

AWPortrait-Z问题解决:图像模糊、速度慢?常见问题一键搞定

AWPortrait-Z问题解决:图像模糊、速度慢?常见问题一键搞定 1. 快速诊断:你的问题属于哪一类? 在使用AWPortrait-Z生成人像时,最常见的问题可以归纳为三类: 图像质量问题:模糊、失真、细节不足…...

)

CPS实战:如何用树莓派+传感器搭建你的第一个信息物理系统(附代码)

CPS实战:如何用树莓派传感器搭建你的第一个信息物理系统(附代码) 信息物理系统(CPS)听起来像是高科技实验室里的复杂装置,但实际上,你完全可以用手边的树莓派和几十元的传感器搭建一个功能完整的…...

Spark依赖管理二选一:spark.yarn.archive和spark.yarn.jars到底怎么选?

Spark依赖管理深度抉择:spark.yarn.archive与spark.yarn.jars的架构师级决策指南 当你在凌晨三点被集群告警惊醒,发现数百个Spark作业因依赖加载超时而堆积,那一刻你会明白:依赖管理策略的选择绝非配置文件中的简单参数调整&#…...

前有张雪峰,后有张雪——这难道是天意-他们的成功最大的特点就是把事情做到极致,你只要坚持,就可能会成功!-你不坚持,不热爱,不可能会成功!-为什么摩托车发动机可以弯道超车,汽车不可以?到底中国汽车的发

前有张雪峰,后有张雪——这难道是天意-他们的成功最大的特点就是把事情做到极致,你只要坚持,就可能会成功!-你不坚持,不热爱,不可能会成功!-为什么摩托车发动机可以弯道超车,汽车不可以?到底中国汽车的发动机质量如何? 前有张雪峰,后有张雪——这难道是天意-他们的成…...

Retinaface+CurricularFace与STM32的结合:边缘设备人脸识别

RetinafaceCurricularFace与STM32的结合:边缘设备人脸识别 1. 引言 想象一下这样的场景:一个智能门禁系统能够准确识别每一位住户,无需连接云端服务器,响应速度极快,而且完全保护用户隐私。或者一个工业质检设备&…...

Qwen2.5-72B大模型实战指南:GPTQ-Int4量化+128K上下文+Chainlit可视化交互全流程

Qwen2.5-72B大模型实战指南:GPTQ-Int4量化128K上下文Chainlit可视化交互全流程 1. 模型简介 Qwen2.5-72B-Instruct-GPTQ-Int4是Qwen大型语言模型系列的最新版本,代表了当前开源大模型领域的顶尖水平。这个72.7B参数的模型经过GPTQ 4-bit量化处理&#…...

万字长文带你深入Redis底层数据结构

在技术领域,我们常常被那些闪耀的、可见的成果所吸引。今天,这个焦点无疑是大语言模型技术。它们的流畅对话、惊人的创造力,让我们得以一窥未来的轮廓。然而,作为在企业一线构建、部署和维护复杂系统的实践者,我们深知…...

SecGPT-14B+OpenClaw联调指南:解决模型响应超时问题

SecGPT-14BOpenClaw联调指南:解决模型响应超时问题 1. 问题背景与场景定位 上周在尝试用OpenClaw调用SecGPT-14B分析一份12万字的网络安全报告时,遭遇了令人头疼的响应超时问题。这个场景很典型——当我们需要处理长文本安全分析时,模型推理…...

网站主域名和子域名的seo优化有何不同

网站主域名和子域名的SEO优化有何不同 在现代网络环境中,网站的SEO优化已经成为了提升网站流量、吸引潜在客户的关键环节。无论是网站主域名还是子域名,其在SEO优化中都有着不同的重要性和作用。本文将详细探讨网站主域名和子域名在SEO优化中的不同&…...