电子设计入门教程硬件篇之集成电路IC(二)

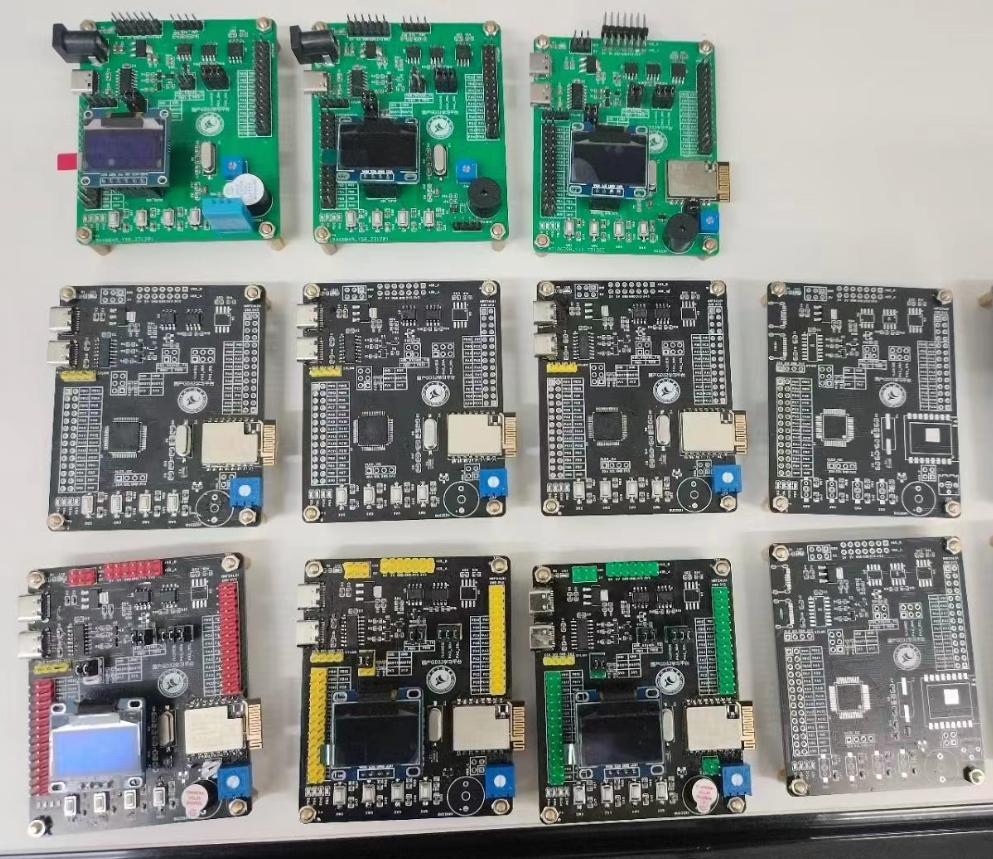

前言:本文为手把手教学的电子设计入门教程硬件类的博客,该博客侧重针对电子设计中的硬件电路进行介绍。本篇博客将根据电子设计实战中的情况去详细讲解集成电路IC,这些集成电路IC包括:逻辑门芯片、运算放大器与电子零件。电子设计中存在的集成电路IC是嵌入式工程师工作中必须接触的事物,希望这篇博文能给读者朋友的工程项目给予些许帮助,Respect!

一、集成电路IC

1.1 集成电路概述

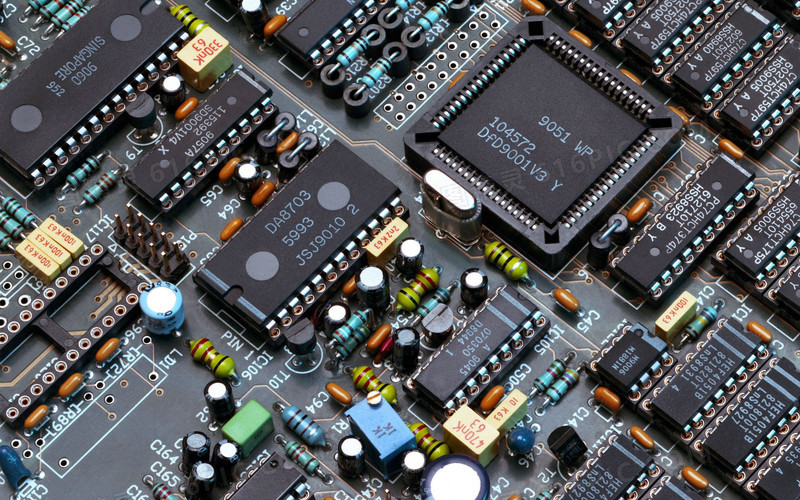

集成电路(Integrated Circuit,IC)是一种将大量的电子元件(如晶体管、二极管、电阻器、电容器等)集成在单个半导体芯片上的微型电子器件。集成电路的发明是电子技术发展史上的一个重要里程碑,它极大地提高了电子设备的性能、降低了成本、缩小了体积、简化了设计和生产过程。

集成电路的分类

模拟集成电路:处理模拟信号的集成电路,如运算放大器、比较器、模拟乘法器等。

数字集成电路:处理数字信号的集成电路,包括逻辑门、触发器、计数器、微处理器等。

混合信号集成电路:结合模拟和数字电路的集成电路,如模拟-数字转换器(ADC)和数字-模拟转换器(DAC)。

功率集成电路:用于功率控制和管理的高电压、高电流集成电路,如电源管理IC、MOSFET驱动器等。

微波集成电路:用于高频、高速通信的集成电路,如射频放大器、混频器、滤波器等。

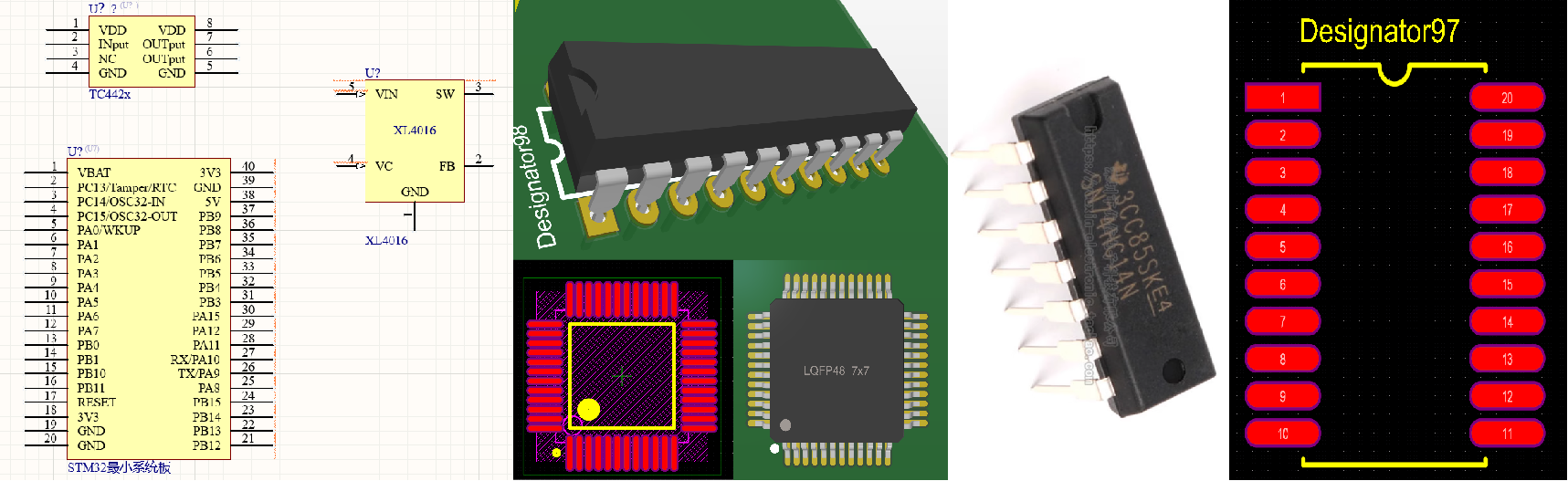

管脚读取方法:调制芯片顺序,让小圆凹槽在左下角,那么从左下往右数, 依次是1,2,3,4.......

逆时针读取 或者是把半圆凹槽放到左边,读取方法一样。

1.2 集成电路应用

集成电路广泛应用于各种电子设备中,包括计算机、手机、家用电器、医疗设备、汽车电子、工业控制系统等。集成电路的发展推动了现代信息技术的革命,使得电子设备变得更加智能、高效和便携。

集成电路的设计和制造是一个高度专业化的领域,需要跨学科的知识和技术,包括电子工程、材料科学、物理学、计算机科学等。随着技术的发展,集成电路的集成度和性能不断提高,其在未来的科技发展中将继续扮演关键角色。

嵌入式工程师是属于硬件研发分支的,日常的核心工作就是与芯片这些集成电路打交道的,我们工程项目中接触到的 STM32、CH32、GD32 与 TI 等微控制器芯片都属于集成电路。当然,工程项目中出现的运放、逻辑门芯片也属于集成电路,在摩尔定律的推动下,如今的集成电路越做越小,集成电路的算力越来越强,已经普及到了各行各业中。

# 输入阻抗和输出阻抗

反映了电路从电源或信号源处最多能分得多少电压的能力 电源或信号源都是有内阻的,用电设备并不能得到100%的电压VCC,而是VCC* 10K/(0.01+10K) 对电源或信号源而言,如果它的输出阻抗很低,那么它所驱动的后级电路能够获得的电压也就越高,驱动能力强 对于负载或设备而言,如果它的输入阻抗很高,那么它能够从供电设备或信号源获得的电压也就越高,

例:比如由三极管搭建的音频放大电路,将话筒输出的微弱音频信号放大,再驱动音响喇叭发声, 那么我们就希望这个音频放大电路的输入阻抗很高,这样就能接近100%的获得全部的音频信号; 同时希望这个电路的输出阻抗很低,这样就能它的输出音频电压接近100%的加在喇叭上。

二、逻辑门芯片

逻辑门芯片是集成电路的一种,用于实现基本的逻辑运算。逻辑门是数字电路的基础,它们执行逻辑操作,如与(AND)、或(OR)、非(NOT)、异或(XOR)等。这些逻辑门可以单独存在于芯片中,也可以在单个芯片中集成多个不同的逻辑门。

常见的逻辑门芯片包括:

与门(AND Gate): 仅当所有输入都为高电平时,输出才为高电平。

或门(OR Gate): 当任一输入为高电平时,输出为高电平。

非门(NOT Gate): 也称为反相器,它将输入的电平反转,即输入高电平时输出低电平,输入低电平时输出高电平。

与非门(NAND Gate): 与门和非门的组合,先进行与操作,然后对结果取反。

或非门(NOR Gate): 或门和非门的组合,先进行或操作,然后对结果取反。

异或门(XOR Gate): 当输入电平不相同时,输出为高电平。

同或门(XNOR Gate): 异或门和非门的组合,当输入电平相同时代输出高电平。

2.1 与门(AND Gate)

与门(英语:AND gate)又称“与电路”、逻辑“积”、逻辑“与”电路。是执行“与”运算的基本逻辑门电路。有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

与门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)、DIN符号(DIN 40700)。

2.2 或门(OR Gate)

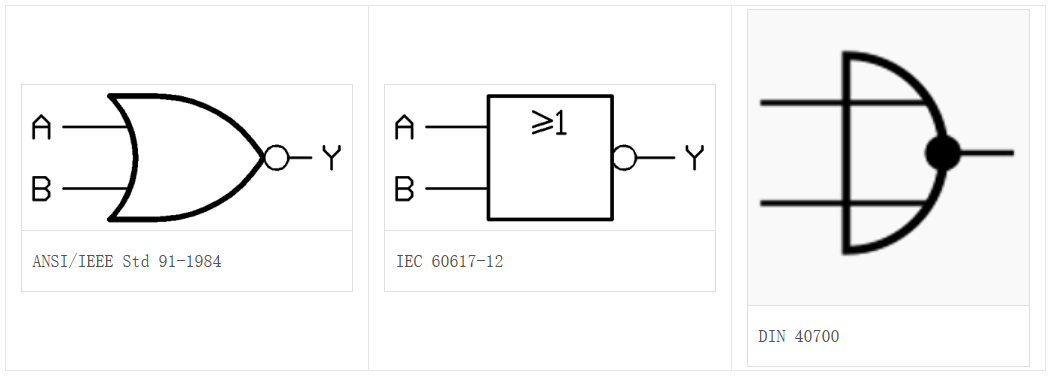

或门(OR gate),又称或电路、逻辑和电路。如果几个条件中,只要有一个条件得到满足,某事件就会发生,这种关系叫做“或”逻辑关系。具有“或”逻辑关系的电路叫做或门。或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑“1”),输出就为高电平(逻辑“1”);只有当所有的输入全为低电平(逻辑“0”)时,输出才为低电平(逻辑“0”)。

或门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)和DIN符号(DIN 40700),以二输入或门为例,逻辑符号如图所示:

2.3 非门(NOT Gate)

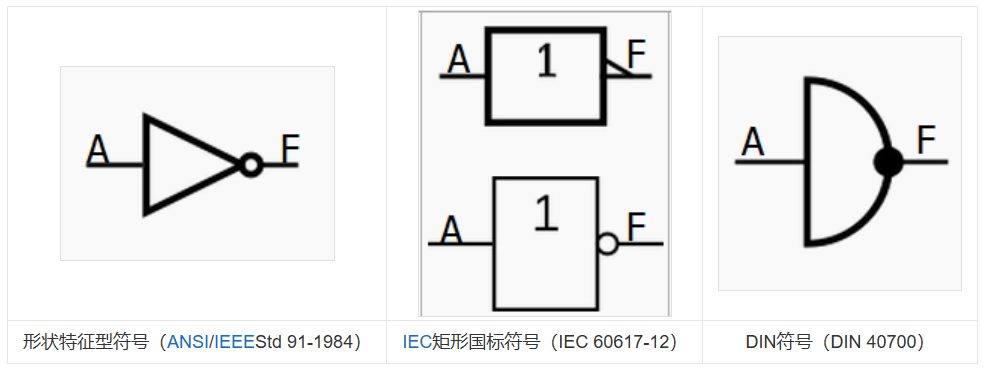

非门(英文:NOT gate)又称非电路、反相器、倒相器、逻辑否定电路,简称非门,是逻辑电路的基本单元。非门有一个输入和一个输出端。当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。也就是说,输入端和输出端的电平状态总是反相的。非门的逻辑功能相当于逻辑代数中的非,电路功能相当于反相,这种运算亦称非运算。

非门共有3种逻辑符号:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)和DIN符号(DIN 40700),分别如下图所示:

2.4 与非门(NAND Gate)

与非门是与门和非门的结合,先进行与运算,再进行非运算。与非门是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。

以下是与非门的符号与真值表:

2.5 或非门(NOR Gate)

或非门(英语:NOR gate)是数字逻辑电路中的基本元件,实现逻辑或非功能。有多个输入端,1个输出端,多输入或非门可由2输入或非门和反相器构成。只有当两个输入A和B为低电平(逻辑0)时输出为高电平(逻辑1)。也可以理解为任意输入为高电平(逻辑1),输出为低电平(逻辑0)。

或非门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)和DIN符号(DIN 40700),以二输入或门为例,逻辑符号如图所示:

2.6 异或门(XOR Gate)

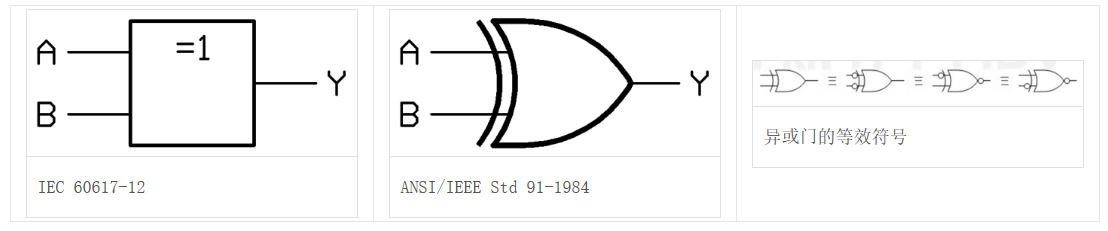

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入异或门构成。若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。即如果两个输入不同,则异或门输出高电平1。

异或门的常用逻辑符号如下图1所示。对异或门的任何2个信号(输入或输出)同时取反,而不改变结果的逻辑功能。在“圈到圈”的设计中,我们选用最能表达要实现的逻辑功能的符号。

2.7 同或门(XNOR Gate)

同或门(英语:XNOR gate或equivalence gate)也称为异或非门,在异或门的输出端再加上一个非门就构成了异或非门,是数字逻辑电路的基本单元,有2个输入端、1个输出端。当2个输入端中有且只有一个是低电平(逻辑0)时,输出为低电平。亦即当输入电平相同时,输出为高电平(逻辑1)。

下列包括逻辑门的2种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)。

三、电子零件

3.1 导线

导线是一种用于传输电能或信号的电气元件,通常由导电材料(如铜、铝或其他金属)制成。导线可以是有绝缘层的单根线,也可以是多根线的电缆。导线在电路中起着连接、传输和分配电能或信号的重要作用。

细导线:只能通过小电流,适合电路板飞线和测试用

粗导线:可通过大电流,作为电机线和电源线买 0.5 平方以上的

3.2 接线端子

接线端子是一种用于连接导线与导线、导线与电器设备或其他电气元件的电子元器件。它允许在不直接焊接的情况下快速、方便地建立电路连接。接线端子广泛应用于电力系统、电子设备、控制系统和家用电器等领域。

常见的脚距:2.54mm、5mm、5.08mm、9.5mm、10mm等

3.3 开关

开关是一种电气控制元件,用于打开或关闭电路,从而控制电流的通断。开关在各种电气设备和控制系统中都发挥着重要作用,它们可以是手动的,也可以是自动的。

开关的类型和种类有很多,但是很简单,大家选购的时候看一下开关规格是否符合电路标准!

相关文章:

电子设计入门教程硬件篇之集成电路IC(二)

前言:本文为手把手教学的电子设计入门教程硬件类的博客,该博客侧重针对电子设计中的硬件电路进行介绍。本篇博客将根据电子设计实战中的情况去详细讲解集成电路IC,这些集成电路IC包括:逻辑门芯片、运算放大器与电子零件。电子设计…...

Unity3D测量面积和角度实现方法(二)

系列文章目录 unity工具 文章目录 系列文章目录👉前言👉一、unity测量面积👉1-1 视频效果👉1-2 先创建预制体👉1-3 在创建LineRenderer预制体👉1-4 代码如下 👉二、测量平面和测量空间切换&…...

vite 配置 typescript 环境

要在 Vite 项目中配置 TypeScript 环境,你需要遵循几个步骤来确保 TypeScript 被正确设置并可以与 Vite 一起工作。以下是一个基本的指南: 初始化项目 如果你还没有初始化项目,可以使用 npm 或 yarn 初始化一个新的项目: npm i…...

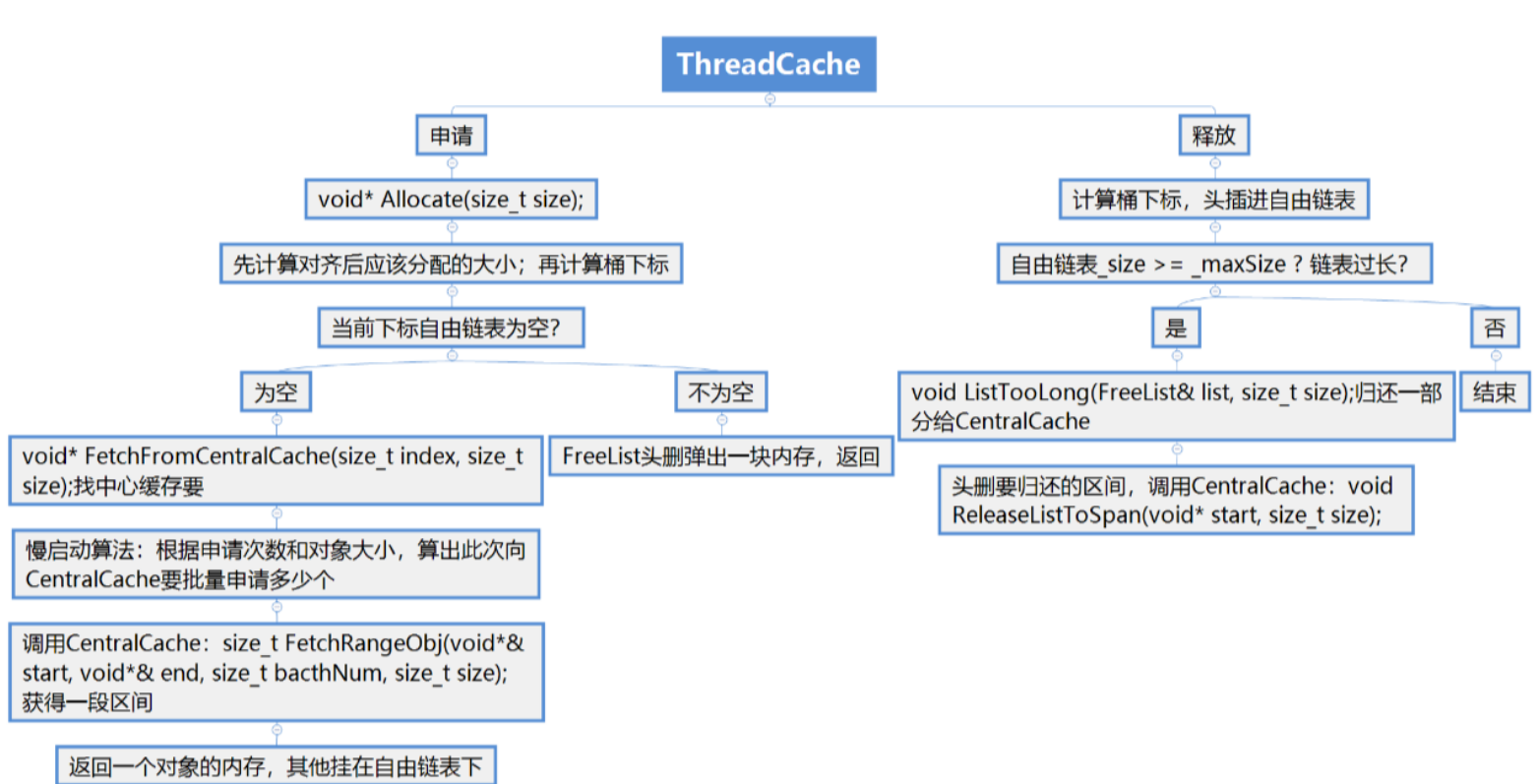

ThreadCache线程缓存

一.ThreadCache整体结构 1.基本结构 定长内存池利用一个自由链表管理释放回来的固定大小的内存obj。 ThreadCache需要支持申请和释放不同大小的内存块,因此需要多个自由链表来管理释放回来的内存块.即ThreadCache实际上一个哈希桶结构,每个桶中存放的都…...

转 UTexture)

UE5_加载本地图片(jpg, png) 转 UTexture

UE5_加载图片到UTexture __Desc使用方式源码 __Desc __Time__: 2024-06-05 16:30 __Author__: Yblackd __Desc__: UE5.2 加载本地图片 转 UTexture2D, 给材质 和 UMG 使用使用方式 新建继承BlueprintFunctionLibrary c 类复制下面源码,修改类名实测加载 jpg,jpeg,…...

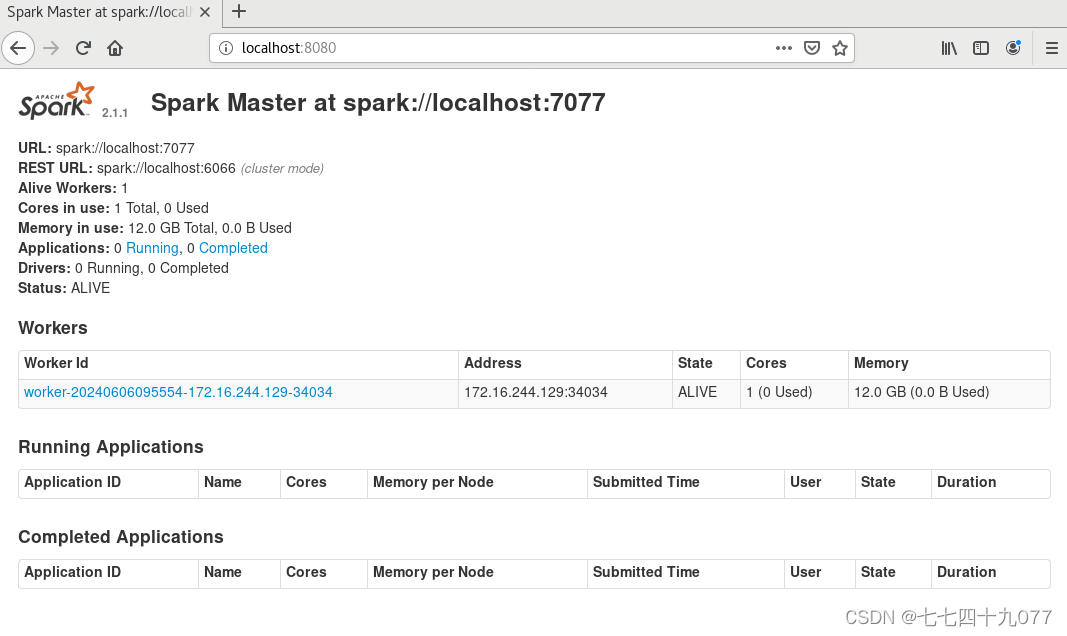

Linux操作系统:Spark在虚拟环境下的安装及部署

将Spark安装到指定目录 // 通过wget下载Spark安装包 $ wget https://d3kbcqa49mib13.cloudfront.net/spark-2.1.1-bin-hadoop2.7.tgz // 将spark解压到安装目录 $ tar –zxvf spark-2.1.1-bin-hadoop2.7.tgz –C /usr/local/ // 重命名 $ mv /usr/local/spark-2.1.1-bin-hado…...

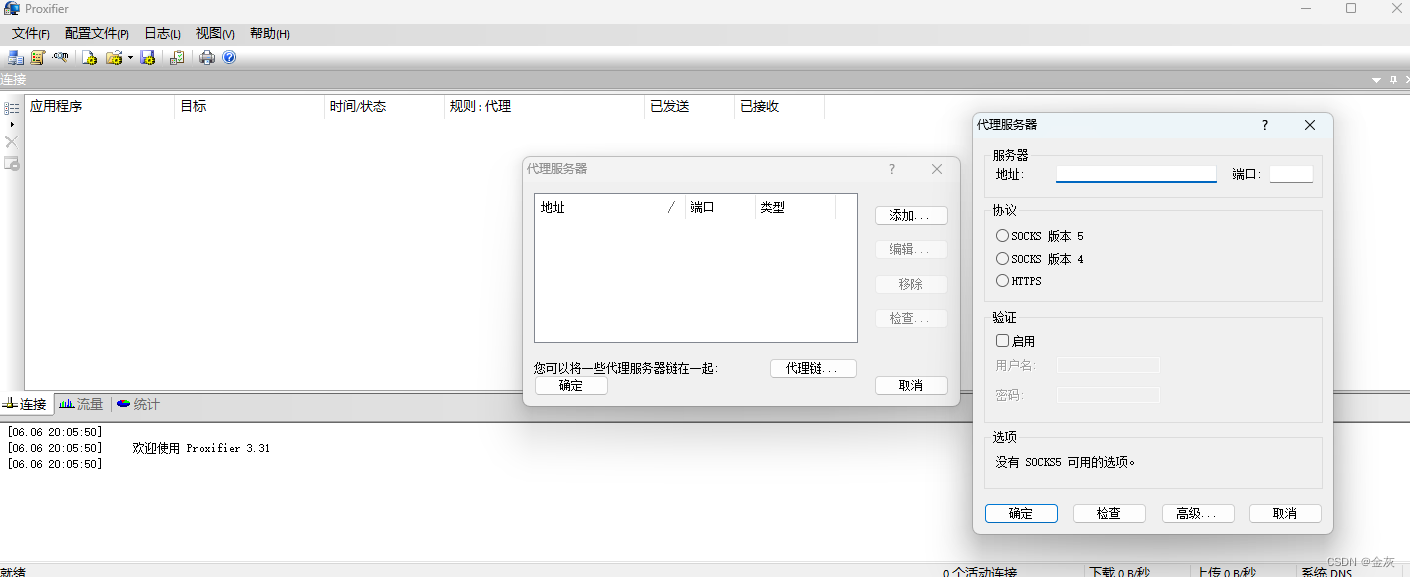

内网安全--隧道技术代理技术

注:本文仅做技术交流,请勿非法破坏... 目录 项目: 1-Ngrok 用法 2-Frp 用法 3-Nps 用法 4-Spp 用法 工具: windows下: Proxifier(推荐~) Sockscap ccproxy Linux下: Proxychains 用法 http://t.csdnimg.cn/88Ew7 隧道技术:解决不出网协议上线的问…...

彩虹易支付最新版源码

源码简介 彩虹易支付最新版源码,更新时间为5.1号 2024/05/01: 1.更换全新的手机版支付页面风格 2.聚合收款码支持填写备注 3.后台支付统计新增利润、代付统计 4.删除结算记录支持直接退回商户金额 安装环境 1.PHP版本>7.4 2.Mysql数据库 安装教…...

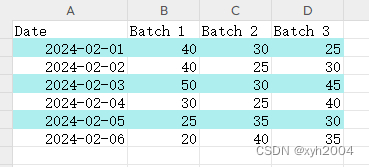

python生成excel数据并实现隔行变色

代码 from openpyxl import Workbook from datetime import date from openpyxl.styles import PatternFilldef create_excel():wb Workbook()sh wb.activerows [[Date, Batch 1, Batch 2, Batch 3],[date(2024, 2, 1), 40, 30, 25],[date(2024, 2, 2), 40, 25, 30],[date(…...

IEEE754 十进制数转32位浮点数格式

为了将十进制数37.25转换为IEEE 754短浮点数格式(32位),我们需要按照以下步骤进行: IEEE 754标准结构 IEEE 754标准的单精度浮点数(32位)格式如下: 1位符号位(S)8位指…...

JVM内存分析之JVM分区与介绍

JVM(Java Virtual Machine)作为Java平台的核心组件,为Java应用程序的运行提供了一个虚拟的计算机环境。为了更好地理解和优化Java应用程序的性能,对JVM的内存管理进行深入分析是至关重要的。本文将详细介绍JVM的内存分区及其功能。…...

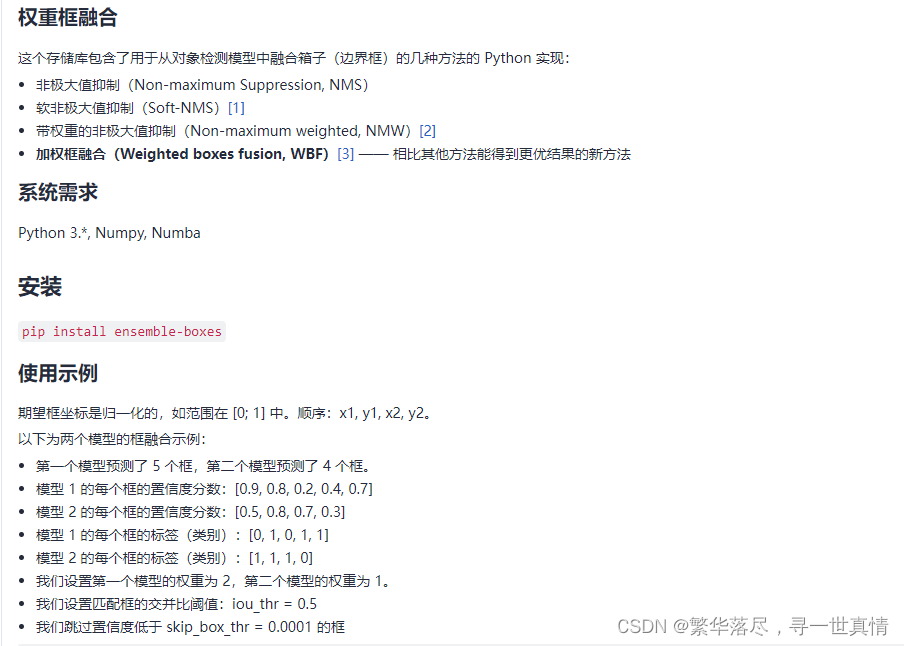

多目标检测模型加权框集成

优秀项目推荐:https://gitcode.com/ZFTurbo/Weighted-Boxes-Fusion/overview 参考链接: 目标检测加权框融合 WBF原理讲解 https://blog.csdn.net/YXD0514/article/details/132574588 目标检测加权框融合 WBF原理讲解(Weighted Boxes Fusion&…...

转型AI产品经理(6):“ 序列位置效应”如何应用在Chatbot产品中

序列位置效应是心理学中的一个记忆现象,指的是人们对一系列信息的记忆效果受到信息在序列中位置的影响。具体来说,人们通常更容易记住列表的开头和结尾部分的项目,而对中间部分的项目记忆较差。这个效应可以进一步分为“首因效应”和“近因效…...

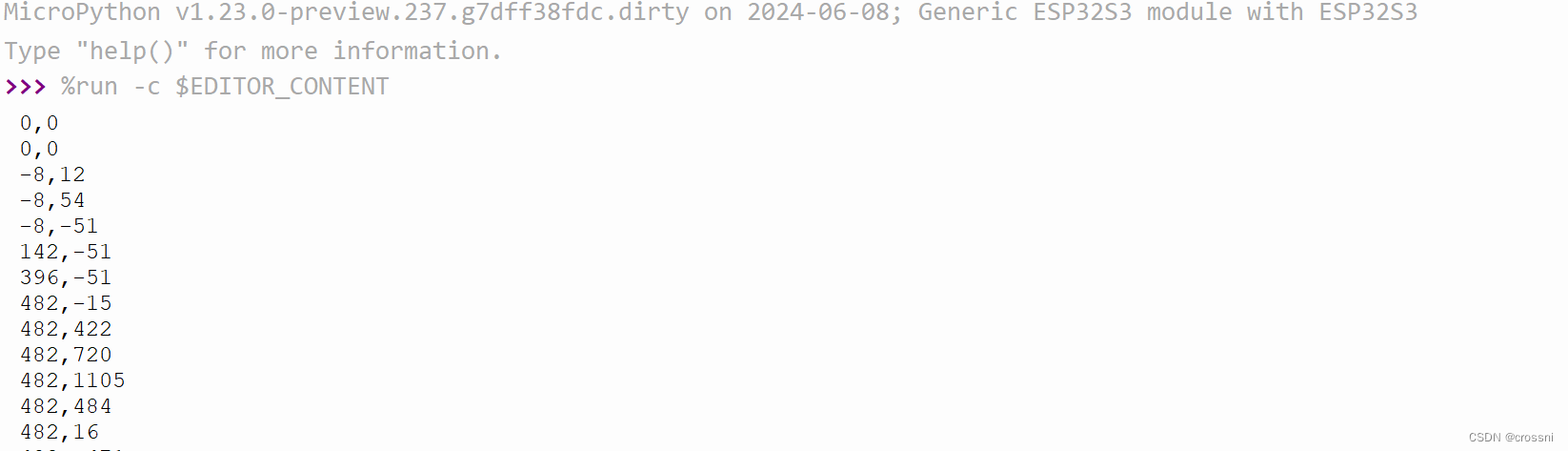

ESP32:往MicroPython集成PCNT以支持硬件正交编码器

背景 官方发布的1.23依然没有在ESP32中集成PCNT功能。考虑到硬件的PCNT模块可以提供4倍的编码精度(对比使用PIn IRQ),还能提供硬件去毛刺。 还是自己集成一下吧。 实际上Github上早在2022年1月的时候就已经有人建议了将PCNT加入正式版本的功…...

Unity基础实践小项目

项目流程: 需求分析 开始界面 选择角色面板 排行榜面板 设置面板 游戏面板 确定退出面板 死亡面板 UML类图 准备工作 1.导入资源 2.创建需要的文件夹 3.创建好面板基类 开始场景 开始界面 1.拼面板 2.写脚本 注意事项:注意先设置NGUI的分辨率大小&…...

Set up a WordPress blog with Nginx

CentOS7 配置Nginx域名HTTPS Here is the revised guideline for setting up a WordPress blog with Nginx: Step 1: Install Nginx, MySQL, and PHP (LEMP Stack) Install Nginx: sudo yum install nginx sudo systemctl start nginx sudo systemctl enable nginxInstall MyS…...

Facebook开户|Facebook广告设计与测试优化

早上好家人们~今天Zoey给大家伙带来的是Facebook广告设计与测试优化,需要的家人们看过来啦! 一、避免复杂用图和过多的文字 根据Facebook的数据显示,用户平均浏览一个贴文的时间在手机上仅花1.7秒、在电脑上则为2.5秒。因此,广告…...

)

vite获取所有环境变量(env)

0.环境变量文件 API_URL8888888 VITE_API_URL99999991.定义环境变量 默认情况下,vite只获取以VITE_为前缀的环境变量。 为了防止意外地将一些环境变量泄漏到客户端,只有以 VITE_ 为前缀的变量才会暴露给经过 vite 处理的代码 但如果你觉得你是进击的巨人…...

【算法】常用排序算法(插入排序、希尔排序、堆排序、选择排序、冒泡排序、快速排序、归并排序、计数排序)超详细

排序算法是数据结构相关知识中非常重要的一节,相信很多小伙伴对这部分知识一知半解。那么接下来,小编就要带领大家一起来进行对排序算法的深入剖析学习,希望本篇文章能够使你有所收获! 一.常见的排序算法 排序算法有很多种&#…...

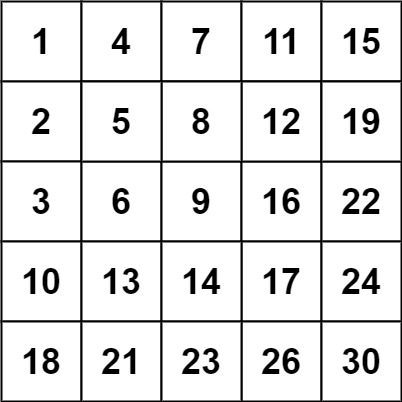

力扣 240.搜素矩阵II

题目描述: 编写一个高效的算法来搜索 m x n 矩阵 matrix 中的一个目标值 target 。该矩阵具有以下特性: 每行的元素从左到右升序排列。每列的元素从上到下升序排列。 示例 1: 输入:matrix [[1,4,7,11,15],[2,5,8,12,19],[3,6,9…...

淘金币全自动脚本终极指南:3分钟搞定淘宝每日任务,解放双手的简单教程

淘金币全自动脚本终极指南:3分钟搞定淘宝每日任务,解放双手的简单教程 【免费下载链接】taojinbi 淘宝淘金币自动执行脚本,包含蚂蚁森林收取能量,芭芭农场全任务,解放你的双手 项目地址: https://gitcode.com/gh_mir…...

Jellyfin智能片头检测解决方案:Intro Skipper插件技术指南

Jellyfin智能片头检测解决方案:Intro Skipper插件技术指南 【免费下载链接】intro-skipper Fingerprint audio to automatically detect and skip intro sequences in Jellyfin 项目地址: https://gitcode.com/gh_mirrors/in/intro-skipper Intro Skipper是一…...

Simplefolio构建优化终极指南:Tree Shaking与代码分割实战

Simplefolio构建优化终极指南:Tree Shaking与代码分割实战 【免费下载链接】simplefolio ⚡️ A minimal portfolio template for Developers 项目地址: https://gitcode.com/gh_mirrors/si/simplefolio Simplefolio是一个为开发者设计的极简个人作品集模板&…...

告别环境报错!保姆级教程:从JRE到STM32CubeMX 6.10.0的完整安装与配置

从零搭建STM32开发环境:CubeMX 6.10.0避坑全指南 刚拿到STM32开发板时的兴奋,往往在环境配置阶段就被各种报错消磨殆尽。作为过来人,我深刻理解那种看着红色错误提示却无从下手的挫败感。本文将带你用最稳妥的方式完成从Java环境到CubeMX的全…...

开源创意资产管理平台Buddy:设计团队协作与版本控制实践

1. 项目概述:一个为创意协作而生的开源平台如果你在团队里负责过创意项目,无论是UI设计、视频剪辑还是产品原型开发,大概率都经历过这样的混乱:设计稿的版本号从V1.0一路飙升到V12_final_really_final.psd;开发同学在群…...

国标通气帽、DN200通气帽与市政管道通气帽怎么选?

我第一次接触通气帽这玩意儿,是在一个闷热的下午。工地上尘土飞扬,师傅递给我一个金属罩子,说:“这是通气用的,别小看它。”我当时还纳闷:不就是个帽子嘛,能有多大讲究?后来才明白&a…...

给文科生的NetLogo入门指南:不用写代码,5分钟看懂‘种族隔离’模型背后的逻辑

给文科生的NetLogo入门指南:不用写代码,5分钟看懂‘种族隔离’模型背后的逻辑 当你第一次听说"用计算机模拟社会现象"时,脑海中浮现的可能是复杂的数学公式和令人望而生畏的代码行。但NetLogo这款工具彻底颠覆了这种认知——它让社…...

Deep SORT:如何用深度关联度量实现95%+准确率的实时多目标追踪?

Deep SORT:如何用深度关联度量实现95%准确率的实时多目标追踪? 【免费下载链接】deep_sort Simple Online Realtime Tracking with a Deep Association Metric 项目地址: https://gitcode.com/gh_mirrors/de/deep_sort 在计算机视觉领域ÿ…...

3个维度重新定义Cursor使用体验:如何突破免费试用限制

3个维度重新定义Cursor使用体验:如何突破免费试用限制 【免费下载链接】cursor-free-vip [Support 0.45](Multi Language 多语言)自动注册 Cursor Ai ,自动重置机器ID , 免费升级使用Pro 功能: Youve reached your tri…...

OpenClaw vs Hermes Agent,谁是 2026 年 AI Agent 最优解?

OpenClaw+Hermes 全集成,一键调用所有 AI 技能:https://ai-skills.ai/?inviteCode=S2JV3NCK 前言 2026 年,AI Agent 已从 “实验玩具” 迈入 “工程化落地” 关键期。GitHub 上 OpenClaw 与 Hermes Agent 两大开源项目热度飙升,均宣称解决大模型 “失忆、弱执行、难沉淀”…...