Xilinx FPGA:vivado实现乒乓缓存

一、项目要求

1、用两个伪双端口的RAM实现缓存

2、先写buffer1,再写buffer2 ,在读buffer1的同时写buffer2,在读buffer2的同时写buffer1。

3、写端口50M时钟,写入16个8bit 的数据,读出时钟25M,读出8个16bit 的数据。

二、信号转换图:

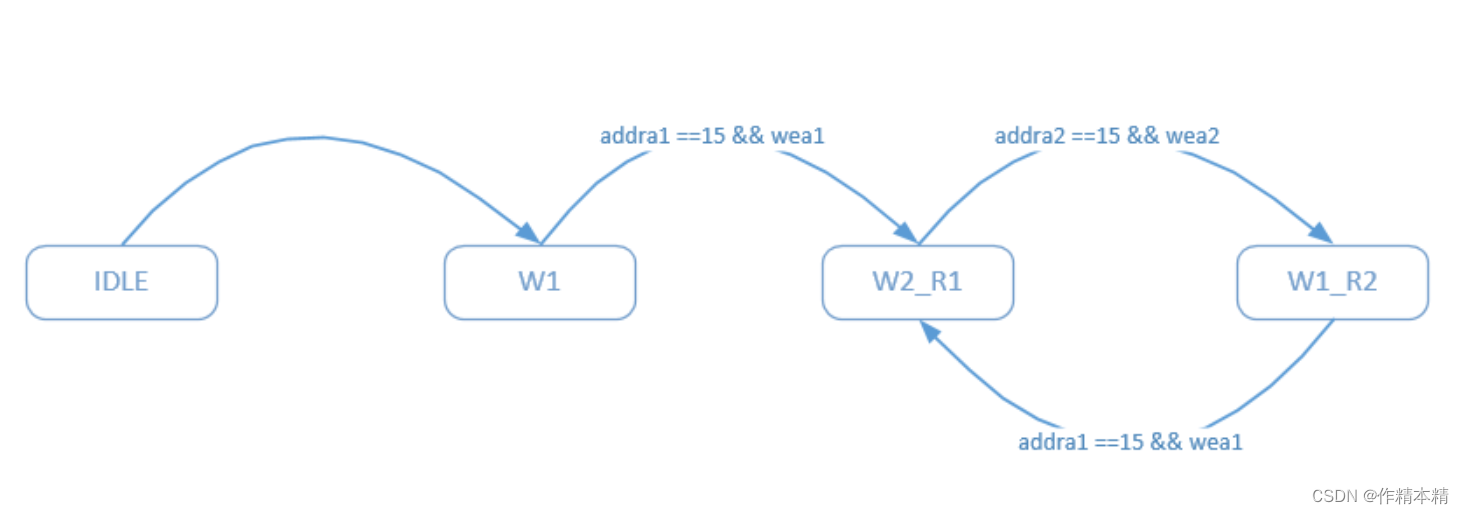

三、状态转换图:

四、程序设计:

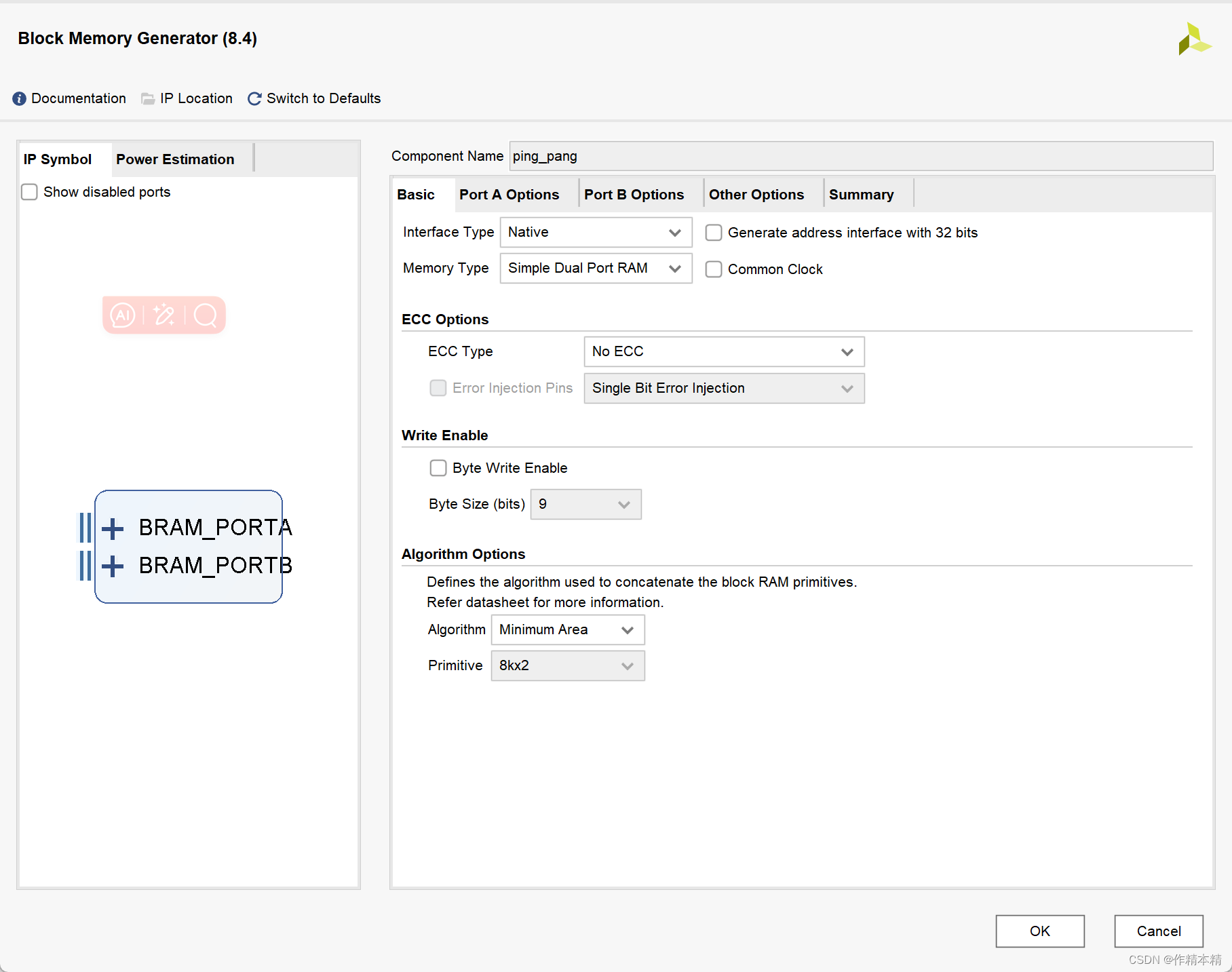

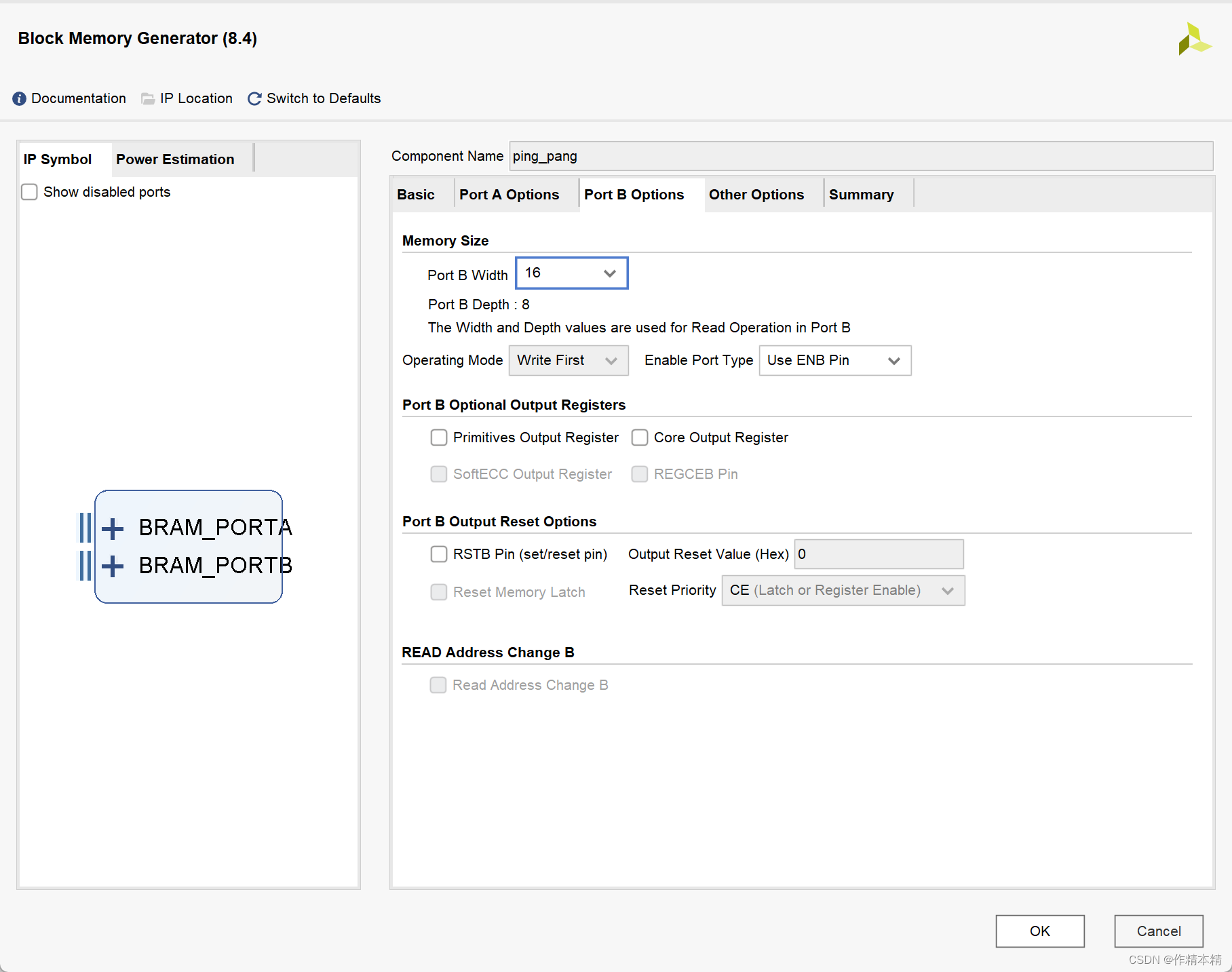

先配置IP:

`timescale 1ns / 1ps

module ping_pang_1(input sys_clk ,input rst_n ,output wire [15 : 0] doutb1 ,output wire [15 : 0] doutb2 );

wire clk_50M ;

wire clk_25M ;

wire locked ;

wire en ;

assign en = locked & rst_n;clk_wiz_0 instance_name(// Clock out ports.clk_50M(clk_50M), // output clk_out1.clk_25M(clk_25M), // output clk_out2// Status and control signals.resetn(rst_n), // input resetn.locked(locked), // output locked// Clock in ports.sys_clk(sys_clk)); // input clk_in1

ram1

reg wea1 ;

reg [3 : 0] addra1 ;

reg [7 : 0] dina1 ;

reg enb1 ;

reg [2 : 0] addrb1 ;ping_pang ram1 (.clka(clk_50M), // input wire clka.ena(1), // input wire ena.wea(wea1), // input wire [0 : 0] wea.addra(addra1), // input wire [3 : 0] addra.dina(dina1), // input wire [7 : 0] dina.clkb(clk_25M), // input wire clkb.enb(enb1), // input wire enb.addrb(addrb1), // input wire [2 : 0] addrb.doutb(doutb1) // output wire [15 : 0] doutb

);

ram2

reg wea2 ;

reg [3 : 0] addra2 ;

reg [7 : 0] dina2 ;

reg enb2 ;

reg [2 : 0] addrb2 ;ping_pang ram2 (.clka(clk_50M), // input wire clka.ena(1), // input wire ena.wea(wea2), // input wire [0 : 0] wea.addra(addra2), // input wire [3 : 0] addra.dina(dina2), // input wire [7 : 0] dina.clkb(clk_25M), // input wire clkb.enb(enb2), // input wire enb.addrb(addrb2), // input wire [2 : 0] addrb.doutb(doutb2) // output wire [15 : 0] doutb

);

/状态机

localparam IDLE = 3'd0;

localparam W1 = 3'd1;

localparam W2_R1 = 3'd2;

localparam W1_R2 = 3'd3;

reg [2:0] cur_state,next_state;

always@(posedge clk_50M)if(!rst_n)cur_state <= IDLE;else if(en)cur_state <= next_state;elsecur_state <= IDLE;

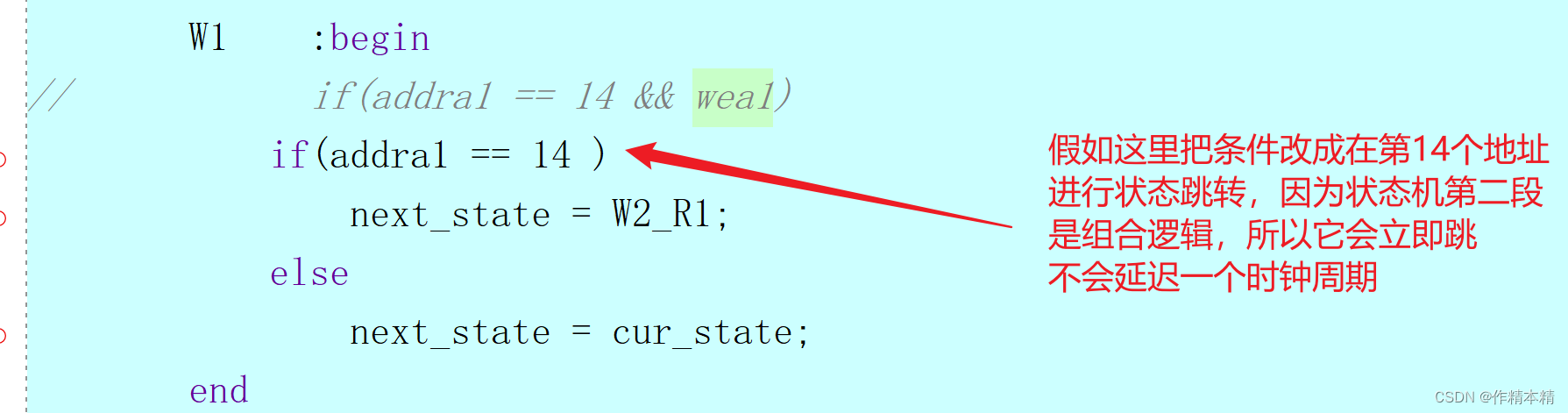

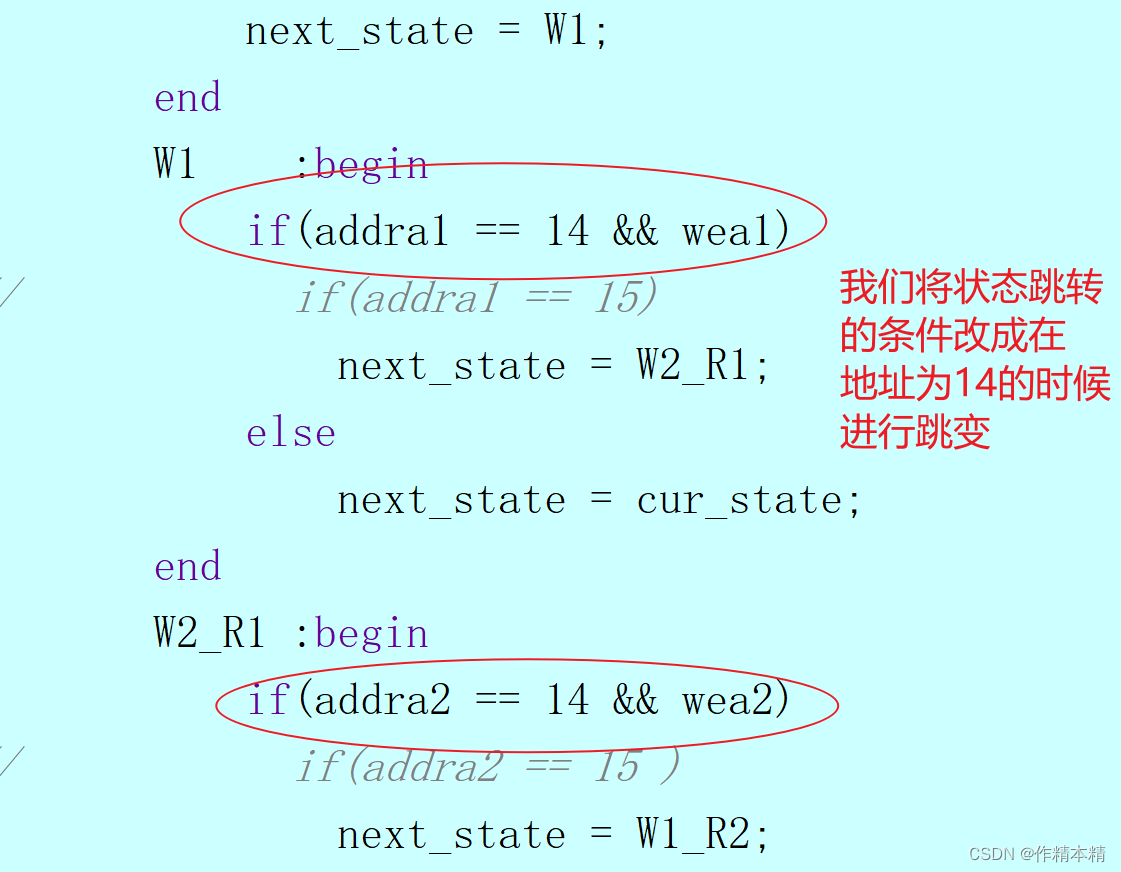

always@(*)case(cur_state)IDLE :beginnext_state = W1; end W1 :beginif(addra1 == 14 && wea1)next_state = W2_R1;elsenext_state = cur_state;endW2_R1 :beginif(addra2 == 14 && wea2)next_state = W1_R2;elsenext_state = cur_state;endW1_R2 :beginif(addra1 == 14 && wea1)next_state = W2_R1;elsenext_state = cur_state;enddefault:;endcase

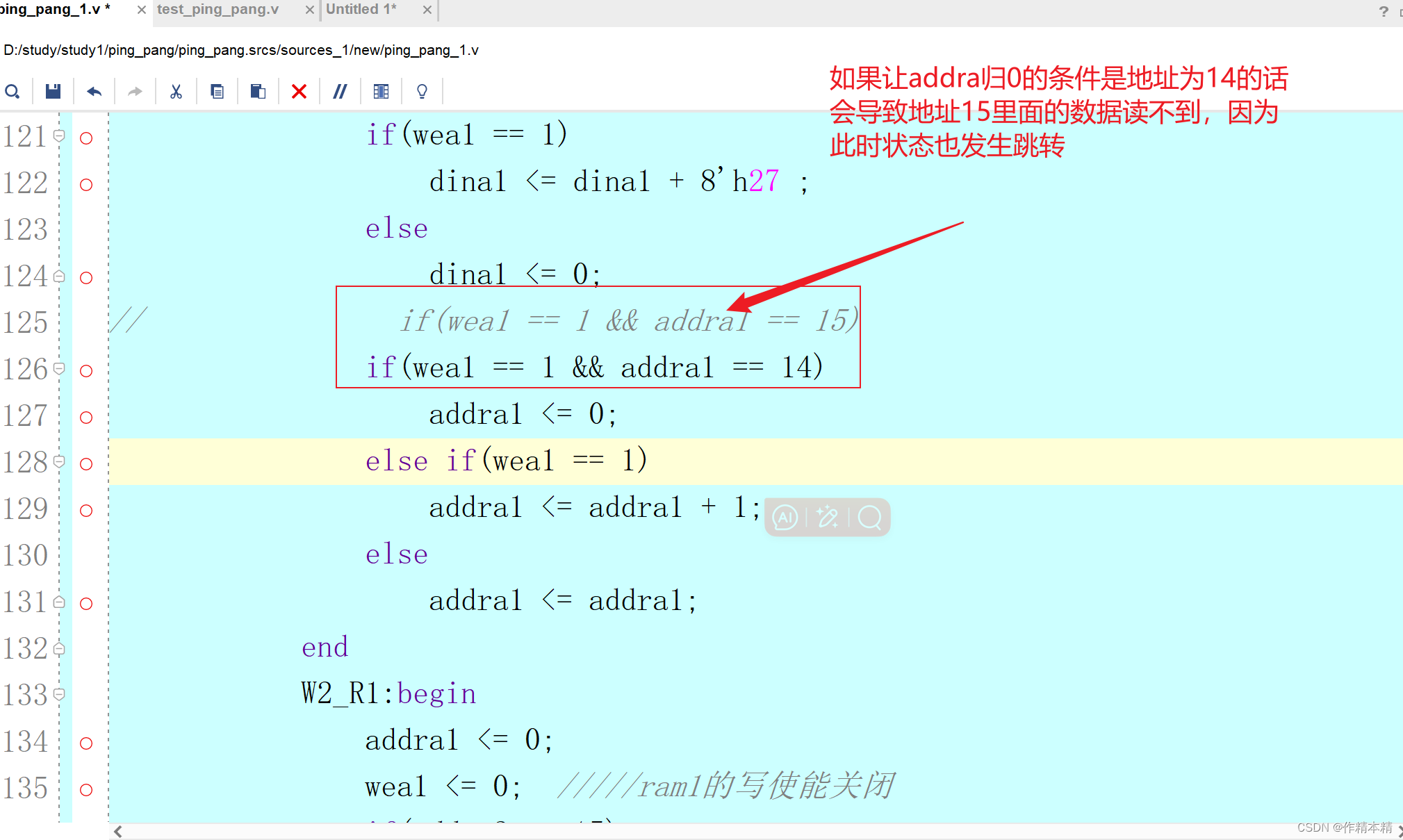

/写状态机

always@(posedge clk_50M)if(!rst_n)beginwea1 <= 0; addra1 <= 0;dina1 <= 0;wea2 <= 0; addra2 <= 0;dina2 <= 0; endelsecase(cur_state)IDLE :beginend W1 :beginif(addra1 == 15)wea1 <= 0;elsewea1 <= 1; if(wea1 == 1)dina1 <= dina1 + 8'h27 ;elsedina1 <= 0;if(wea1 == 1 && addra1 == 15)addra1 <= 0;else if(wea1 == 1) addra1 <= addra1 + 1;elseaddra1 <= addra1; endW2_R1:beginaddra1 <= 0;wea1 <= 0; /ram1的写使能关闭if(addra2 == 15)wea2 <= 0;elsewea2 <= 1; if(wea2 == 1)dina2 <= dina2 + 8'h19 ;elsedina2 <= 0;if(wea2 == 1 && addra2 == 15)addra2 <= 0;else if(wea2 == 1) addra2 <= addra2 + 1;elseaddra2 <= 0; endW1_R2:beginwea2 <= 0;addra2 <= 0; if(addra1 == 15)wea1 <= 0;elsewea1 <= 1; if(wea1 == 1)dina1 <= dina1 + 8'h27 ;elsedina1 <= 0;if(wea1 == 1 && addra1 == 15)addra1 <= 0;else if(wea1 == 1) addra1 <= addra1 + 1;elseaddra1 <= 0; enddefault:;endcase

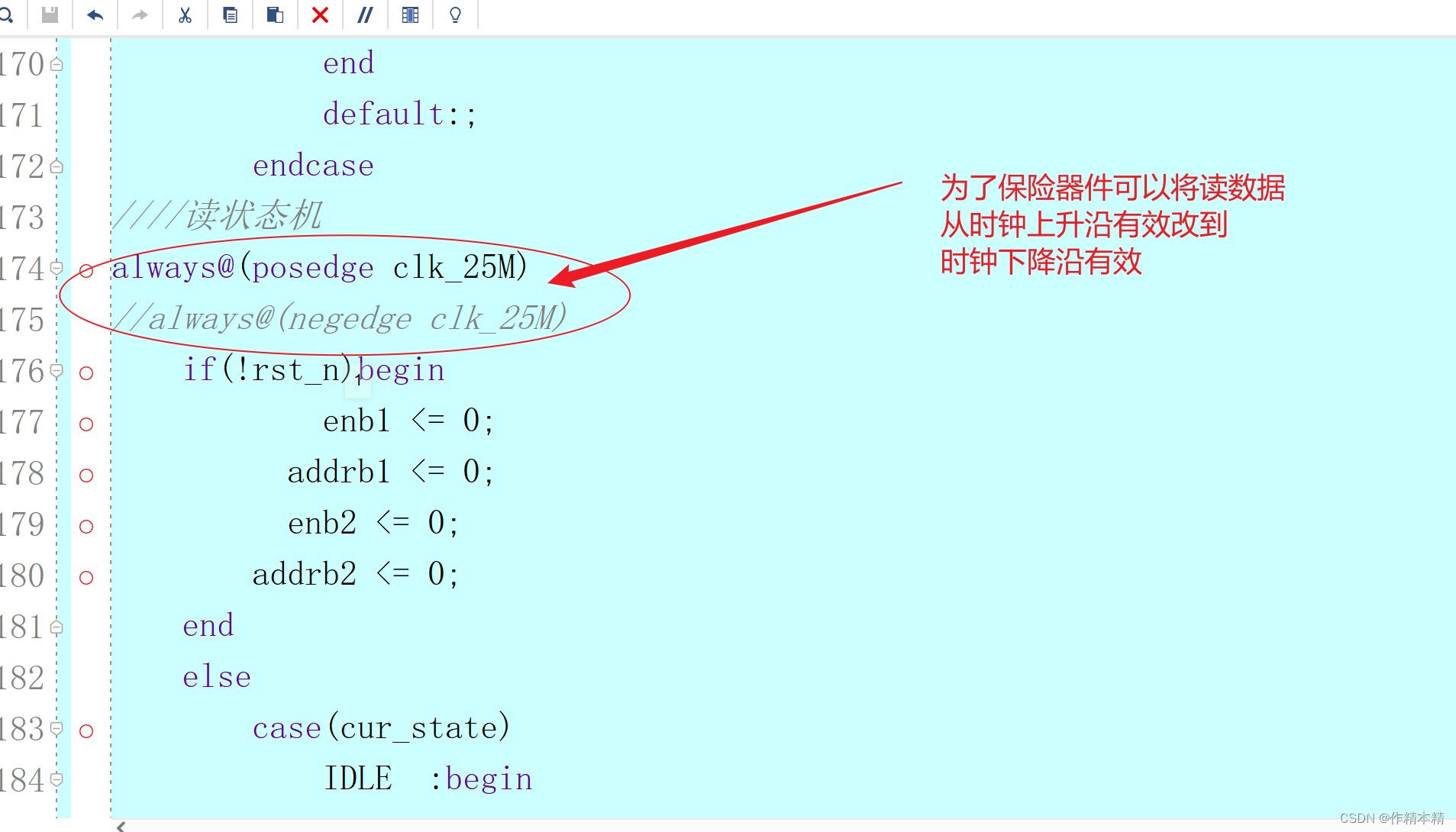

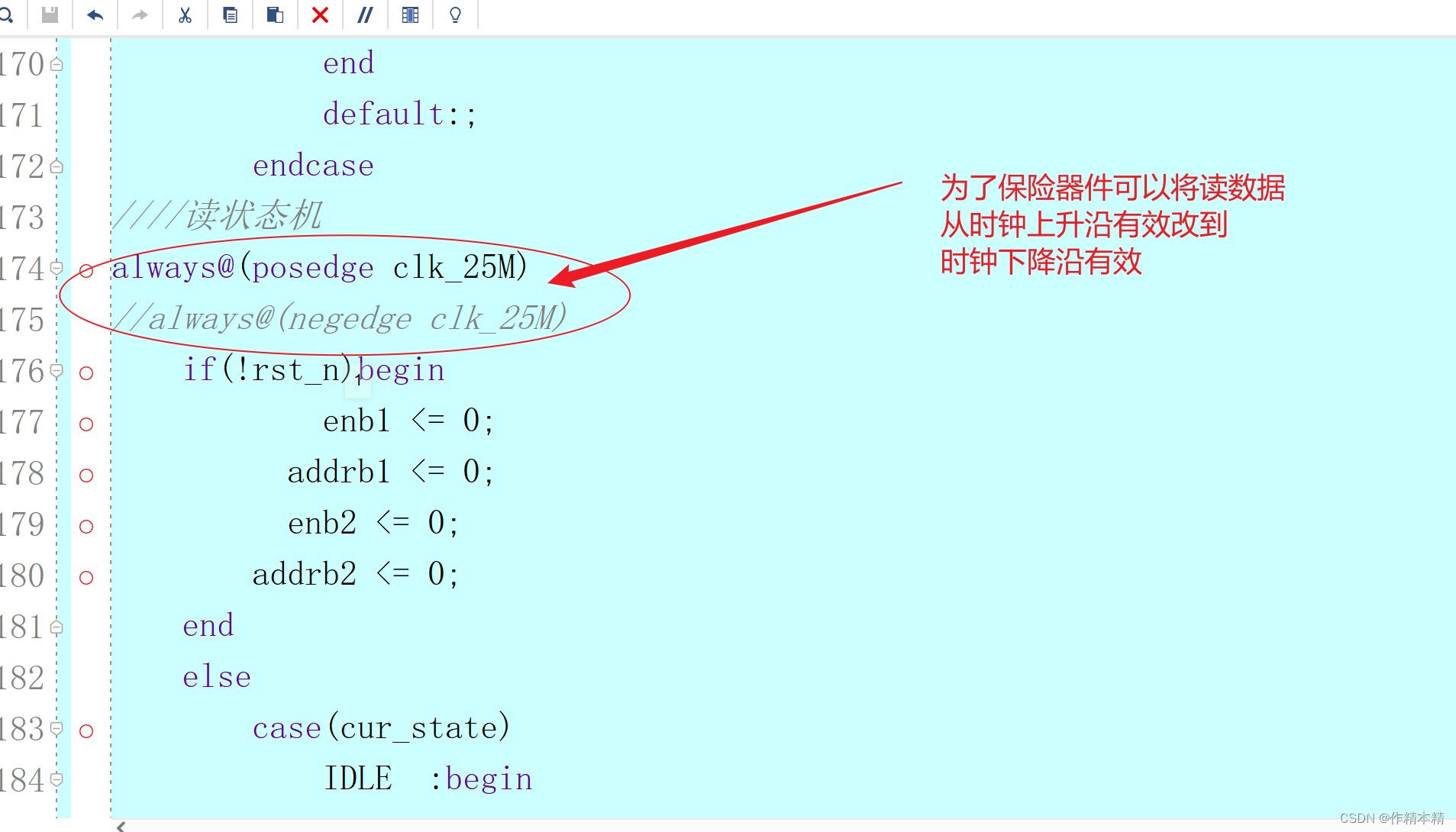

读状态机

always@(negedge clk_25M)if(!rst_n)beginenb1 <= 0; addrb1 <= 0;enb2 <= 0; addrb2 <= 0; endelsecase(cur_state)IDLE :beginend W1 :beginendW2_R1 :beginenb2 <= 0; addrb2 <= 0;if(addrb1 == 7 && enb1)enb1 <= 0;elseenb1 <= 1;if(enb1 == 1 && addrb1 == 7)addrb1 <= 0;else if(enb1)addrb1 <= addrb1 + 1;elseaddrb1 <= 0; endW1_R2 :beginaddrb1 <= 0; enb1 <= 0;if(addrb2 == 7)enb2 <= 0;elseenb2 <= 1;if(enb2 == 1 && addrb2 == 7)addrb2 <= 0;else if(enb2)addrb2 <= addrb2 + 1;elseaddrb2 <= 0; enddefault:;endcaseendmodule 五、仿真设计

`timescale 1ns / 1ps

module test_ping_pang( );reg sys_clk ;reg rst_n ;wire[15:0] doutb1 ;wire[15:0] doutb2 ;initialbeginsys_clk = 0 ;rst_n = 0 ;#10rst_n = 1 ;end always #1 sys_clk = ~sys_clk ; ping_pang_1 ping_pang_1_1(. sys_clk ( sys_clk ) ,. rst_n ( rst_n ) , . doutb1 (doutb1 ) ,. doutb2 (doutb2 ) );endmodule

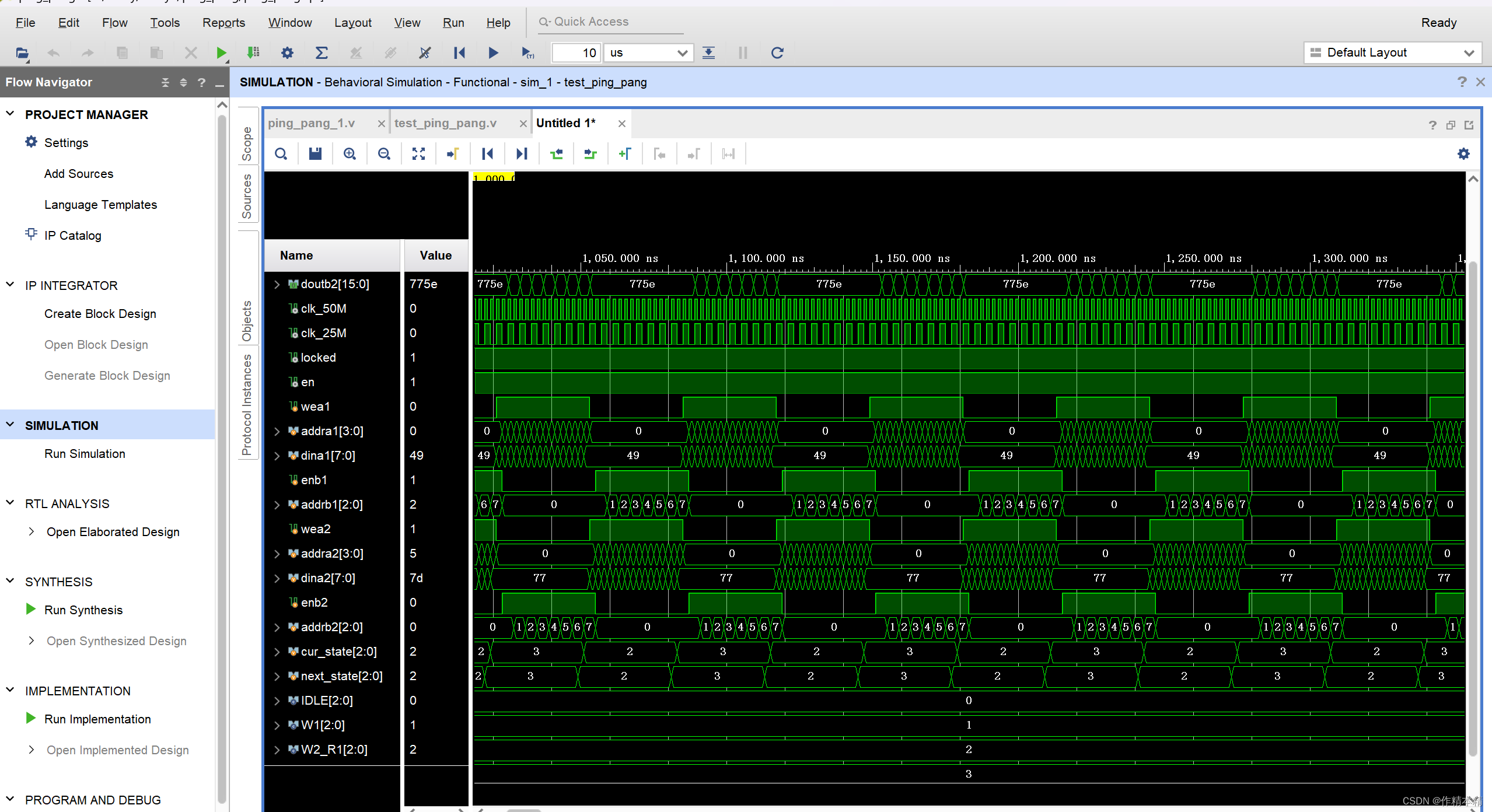

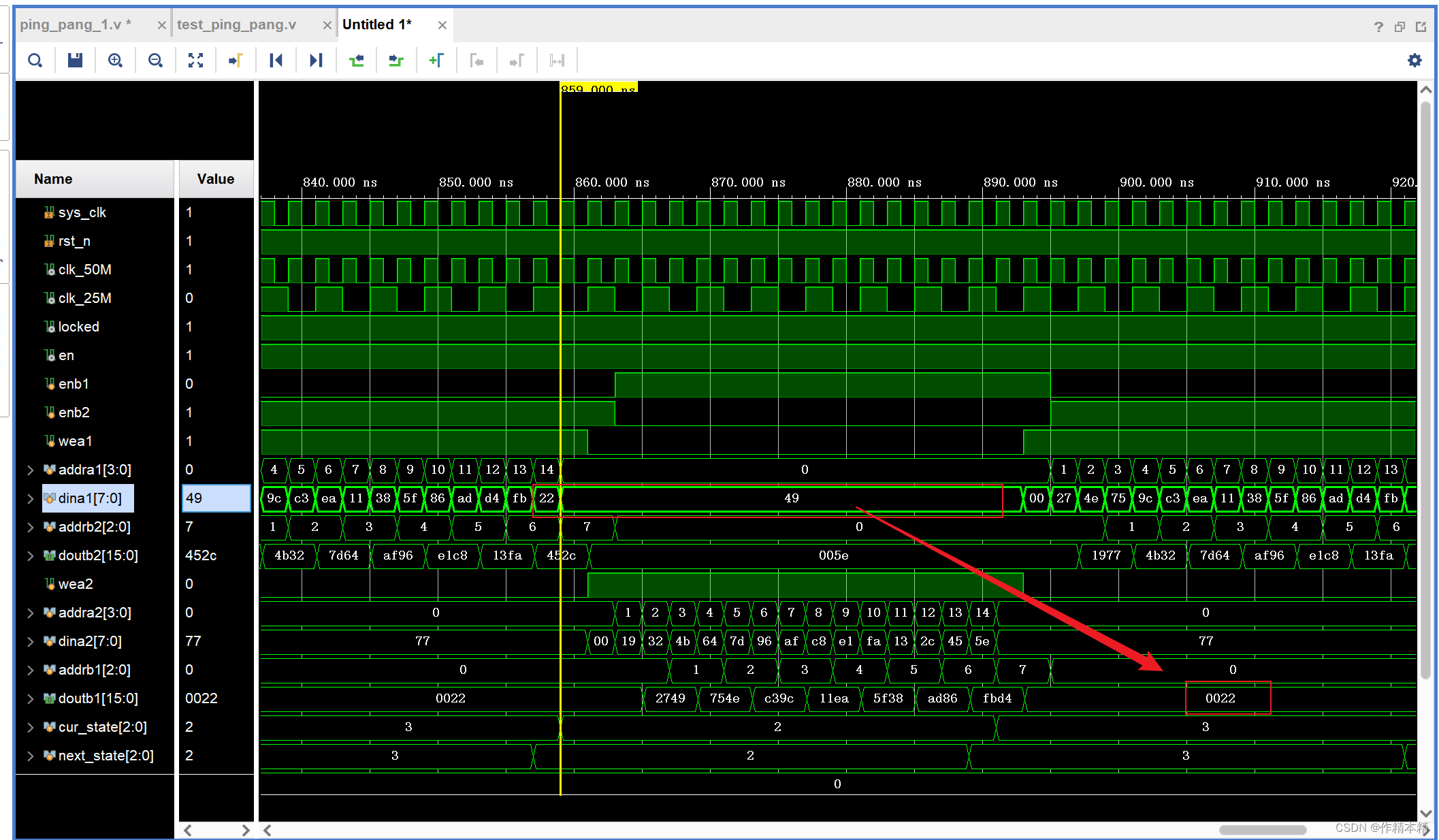

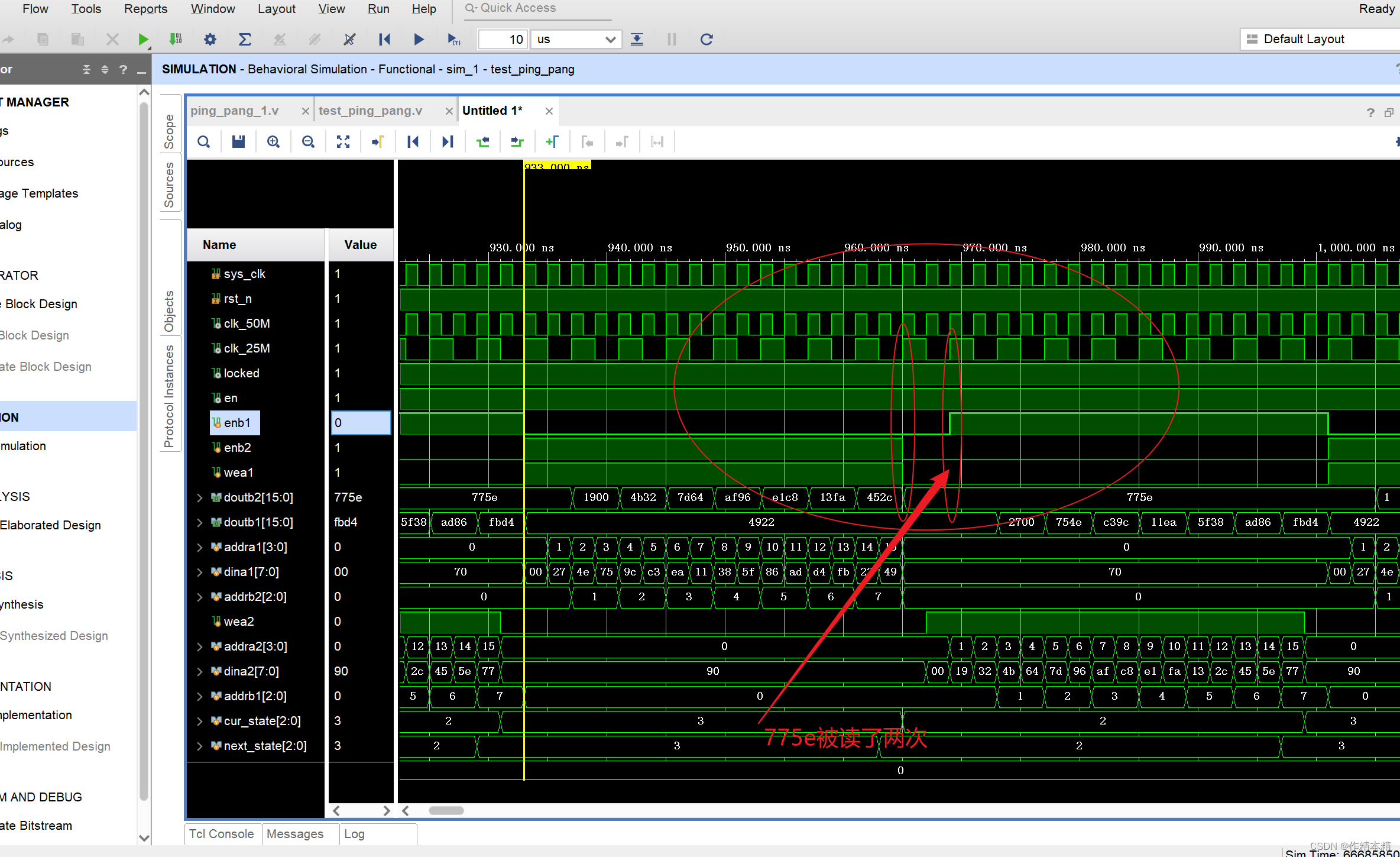

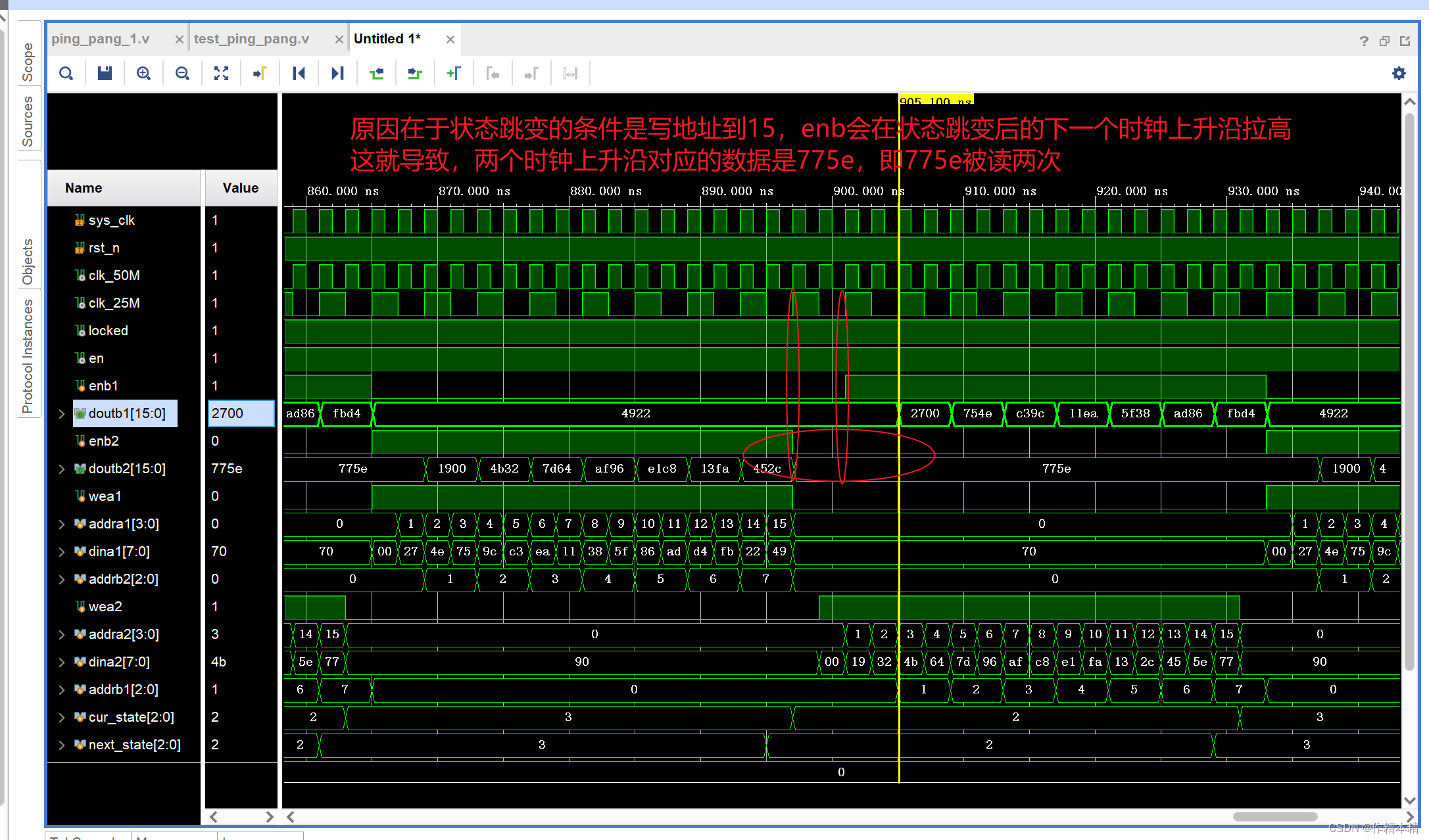

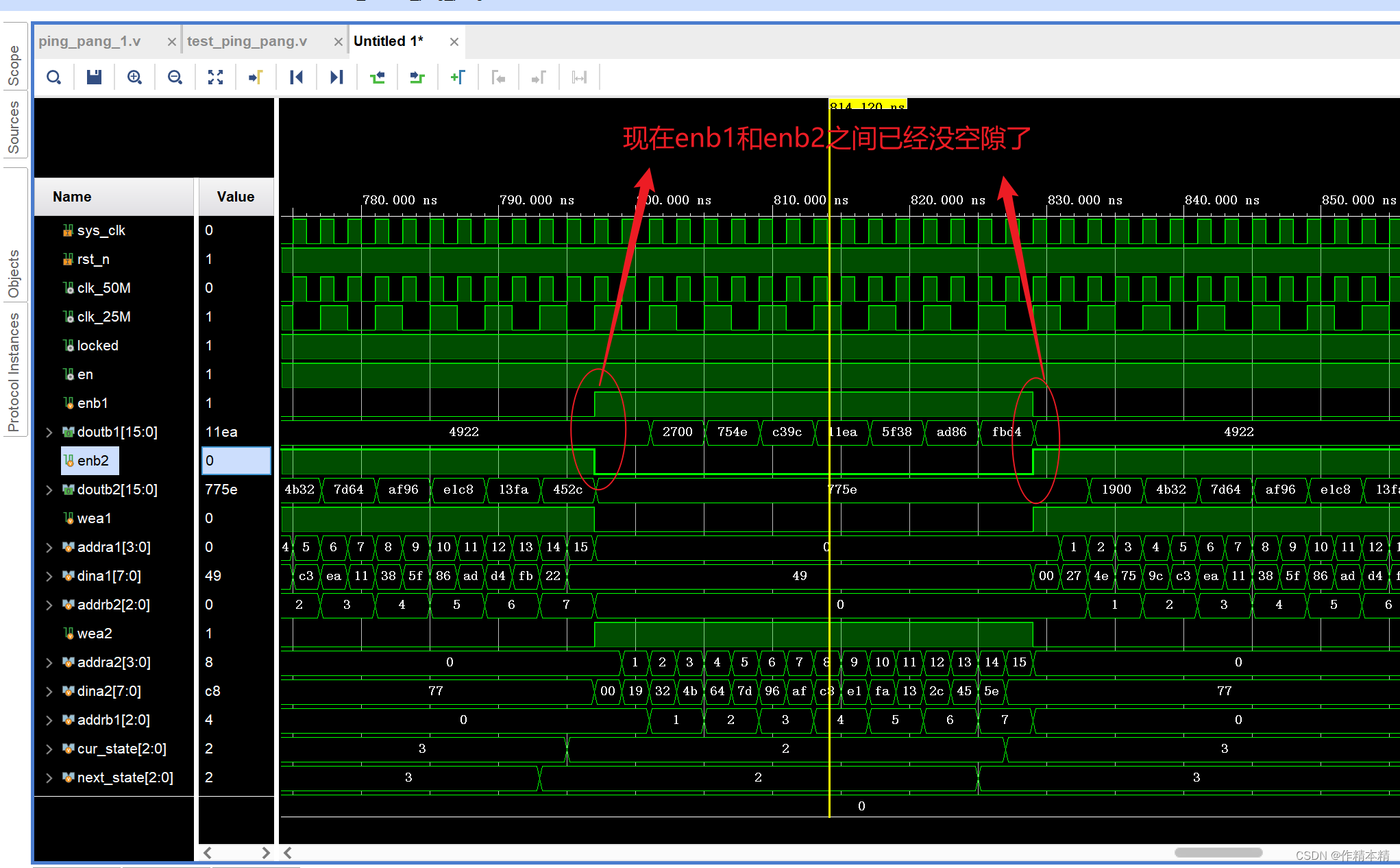

五、仿真结果

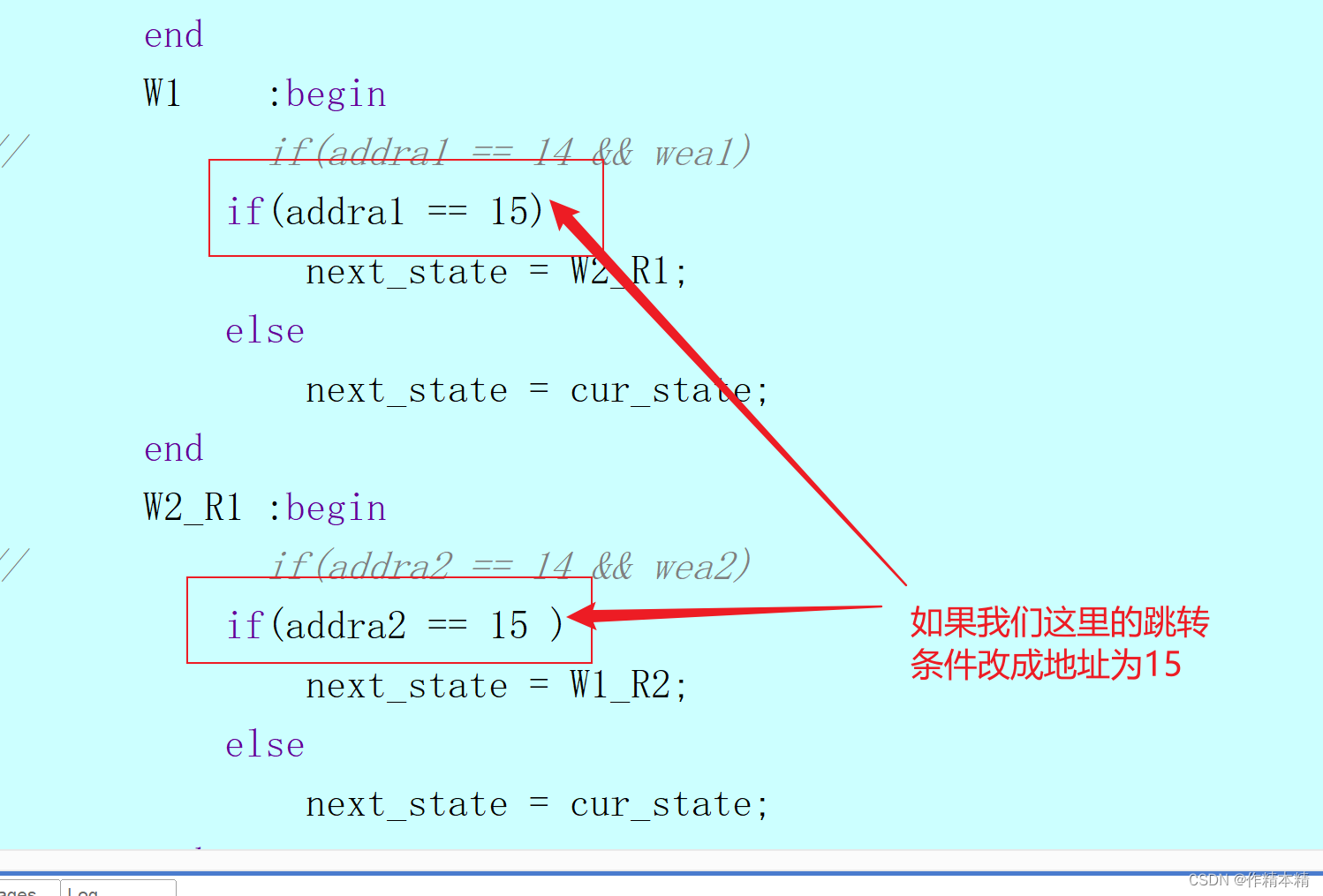

六、记录一些小问题:

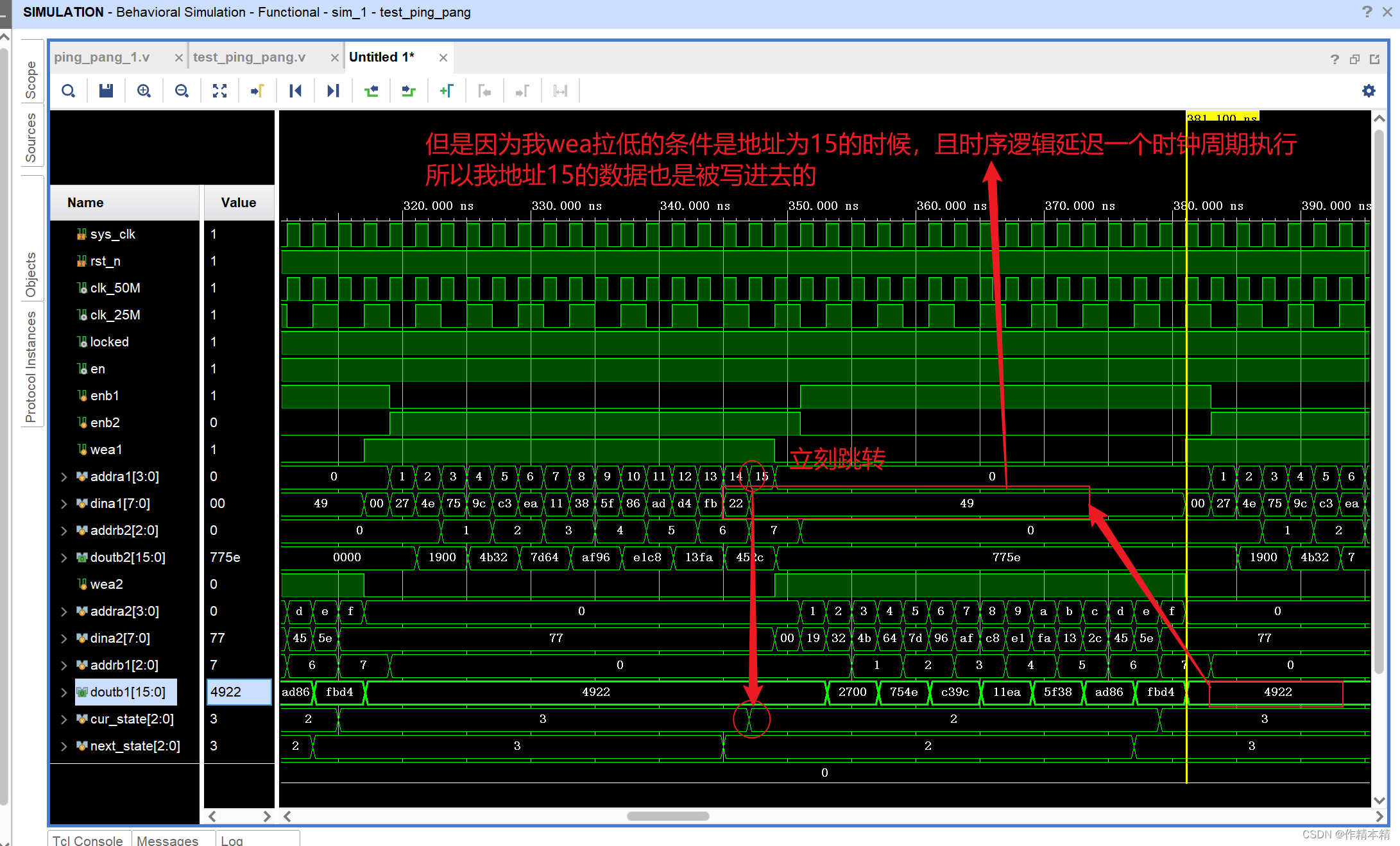

(2)

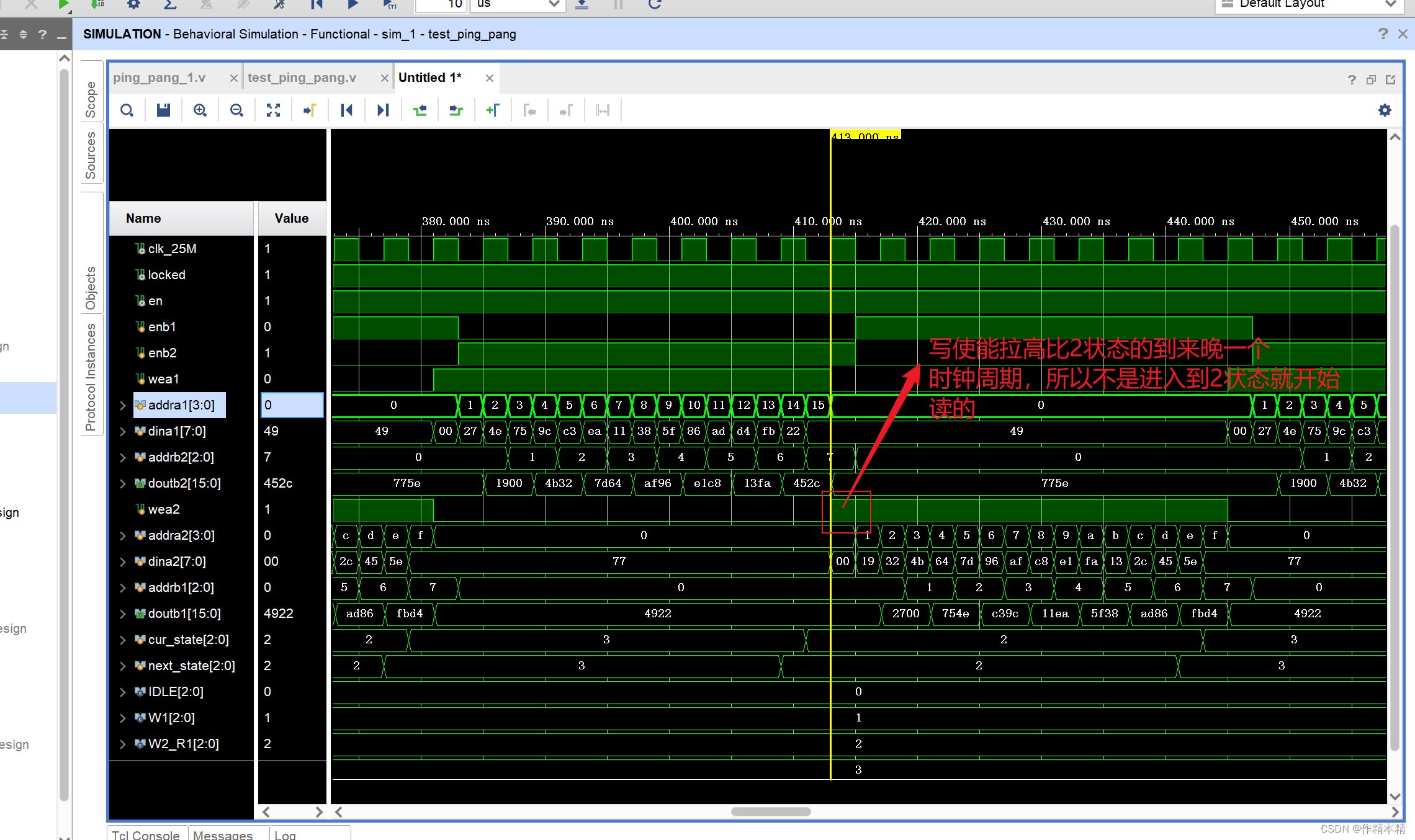

(3)

所以修改思路就是尽量让enb1和enb2之间没有空隙,在时序上是衔接着的

相关文章:

Xilinx FPGA:vivado实现乒乓缓存

一、项目要求 1、用两个伪双端口的RAM实现缓存 2、先写buffer1,再写buffer2 ,在读buffer1的同时写buffer2,在读buffer2的同时写buffer1。 3、写端口50M时钟,写入16个8bit 的数据,读出时钟25M,读出8个16…...

解决 VM 虚拟机网络连接异常导致的 Finalshell 无法连接及 ifconfig 中 ens33 丢失问题

在使用 VM 虚拟机的过程中,遇到了一个颇为棘手的网络连接问题。平时虚拟机都能够正常启动并使用,但昨天在启用虚拟机时更换了一下网络节点,结果今天打开虚拟机后。Finalshell 无法连接上虚拟机,并且输入 ifconfig 命令后也没有 en…...

)

深入Django(三)

Django视图(Views)详解 引言 在前两天的博客中,我们介绍了Django的基本概念和模型系统。今天,我们将深入探讨Django的视图(Views),它们是处理用户请求和返回响应的地方。 什么是Django视图&a…...

观测云赋能「阿里云飞天企业版」,打造全方位监控观测解决方案

近日,观测云成功通过了「阿里云飞天企业版」的生态集成认证测试,并荣获阿里云颁发的产品生态集成认证证书。作为监控观测领域的领军者,观测云一直专注于提供统一的数据视角,助力用户构建起全球范围内的端到端全链路可观测服务。此…...

51单片机第27步_单片机工作在睡眠模式

重点学习51单片机工作在睡眠模式。 1、进入“睡眠模式”的方法 通过将PCON寄存器中的PDWN置1,则CPU会进入“睡眠模式”。在“睡眠模式”中,晶振将停止工作,因此,定时器和串口都将停止工作,只有外部中断继续工作。如果单片机电源…...

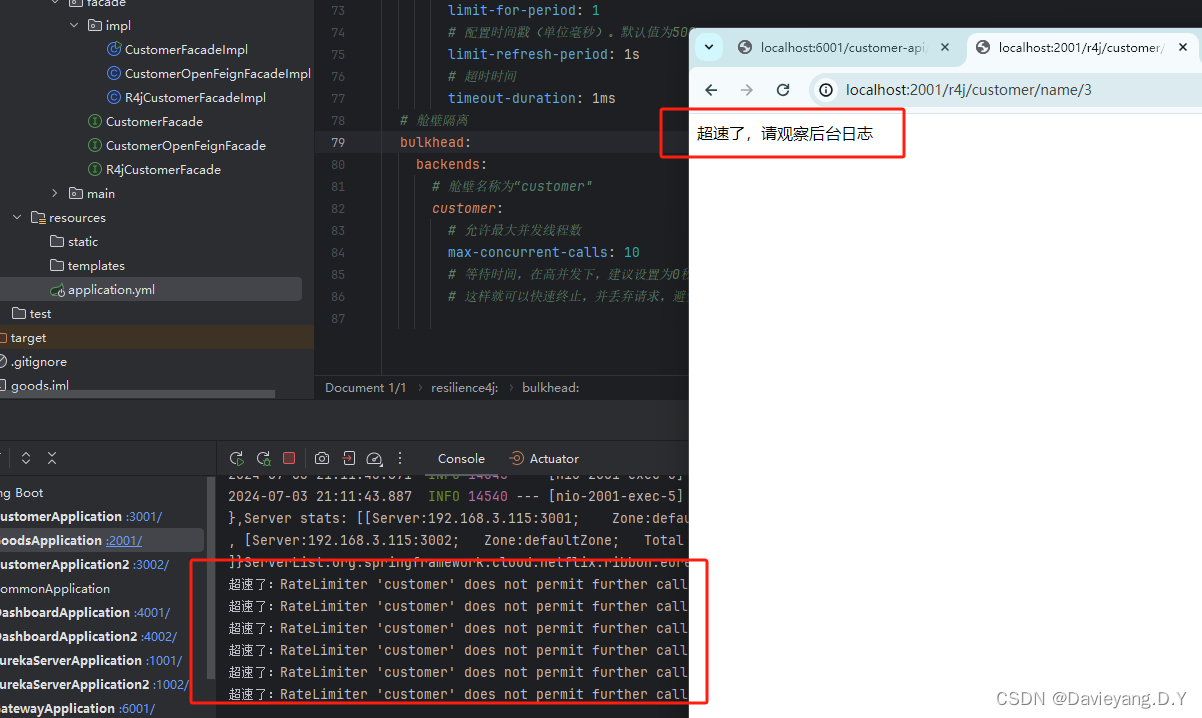

互联网应用主流框架整合之SpringCloud微服务治理

微服务架构理念 关于微服务的概念、理念及设计相关内容,并没有特别严格的边界和定义,某种意义上说,适合的就是最好的,在之前的文章中有过详细的阐述,微服务[v1.0.0][Spring生态概述]、微服务[设计与运行]、微服务[v1.…...

超快的 Python 包管理工具「GitHub 热点速览」

天下武功,无坚不破,唯快不破! 要想赢得程序员的欢心,工具的速度至关重要。仅需这一优势,即可使其在众多竞争对手中脱颖而出,迅速赢得开发者的偏爱。以这款号称下一代极速 Python 包管理工具——uv 为例&…...

网络基础:OSPF 协议

OSPF(Open Shortest Path First)是一种广泛使用的链路状态路由协议,用于IP网络中的内部网关协议(IGP)。OSPF通过在网络中的所有路由器之间交换路由信息,选择从源到目的地的最优路径。OSPF工作在OSI模型的第…...

1456.定长子串中元音的最大数目

思路: 首次是滑动窗口, 然后遍历子字符串,这样复杂度太高,没过测试 改进,滑动窗口先求出第一个窗口中元音数量, 然后利用滑动式,一进一出方式判断首尾是否是原因即可 给你字符串 s 和整数 k 。 …...

基于xilinx FPGA的GTX/GTH/GTY位置信息查看方式(如X0Y0在bank几)

目录 1 概述2 参考文档3 查看方式4查询总结: 1 概述 本文用于介绍如何查看xilinx fpga GTX得位置信息(如X0Y0在哪个BANK/Quad)。 2 参考文档 《ug476_7Series_Transceivers》 《pg156-ultrascale-pcie-gen3-en-us-4.4》 3 查看方式 通过…...

JAVA小知识30:JAVA多线程篇1,认识多线程与线程安全问题以及解决方案。(万字解析)

来 多线程,一个学起来挺难但是实际应用不难的一个知识点,甚至在很多情况下都不需要考虑,最多就是写测试类的时候模拟一下并发,现在我们就来讲讲基础的多线程知识。 一、线程和进程、并发与并行 1.1、线程和进程 线程&am…...

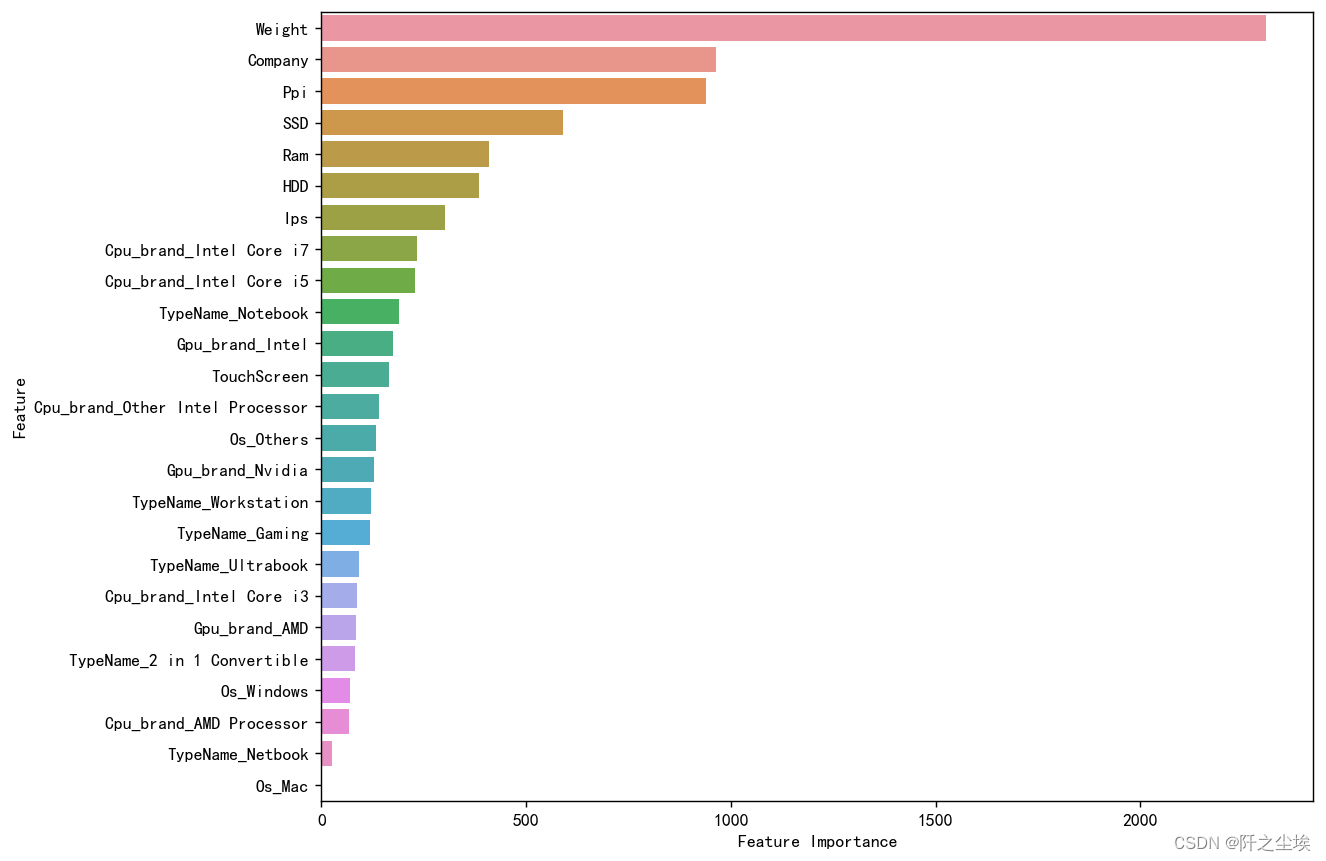

Python数据分析案例47——笔记本电脑价格影响因素分析

案例背景 博主对电脑的价格和配置一直略有研究,正好最近也有笔记本电脑相关的数据,想着来做点分析吧,写成一个案例。基本上描述性统计,画图,分组聚合,机器学习,交叉验证,搜索超参数…...

【加密与解密】【09】GPG Client签名流程

什么是GPG客户端 GPG客户端是实现PGP加密协议的一套客户端程序,可用于加密或签名 下载GPG客户端 建议安装命令行工具,图形工具一般不具备完整功能 https://gnupg.org/download/index.html生成私钥 此时会要求你输入名称,邮箱,…...

“2024软博会” 为软件企业提供集展示、交流、合作一站式平台

随着全球科技浪潮的涌动,软件行业正迎来前所未有的发展机遇,成为了全球新一轮竞争的“制高点”,以及未来经济发展的“增长点”。在当前互联网、大数据、云计算、人工智能、区块链等技术加速创新的背景下,数字经济已经渗透到经济社…...

【Zoom安全解析】深入Zoom的端到端加密机制

标题:【Zoom安全解析】深入Zoom的端到端加密机制 在远程工作和在线会议变得越来越普及的今天,视频会议平台的安全性成为了用户关注的焦点。Zoom作为全球领先的视频会议软件,其端到端加密(E2EE)功能保证了通话的安全性…...

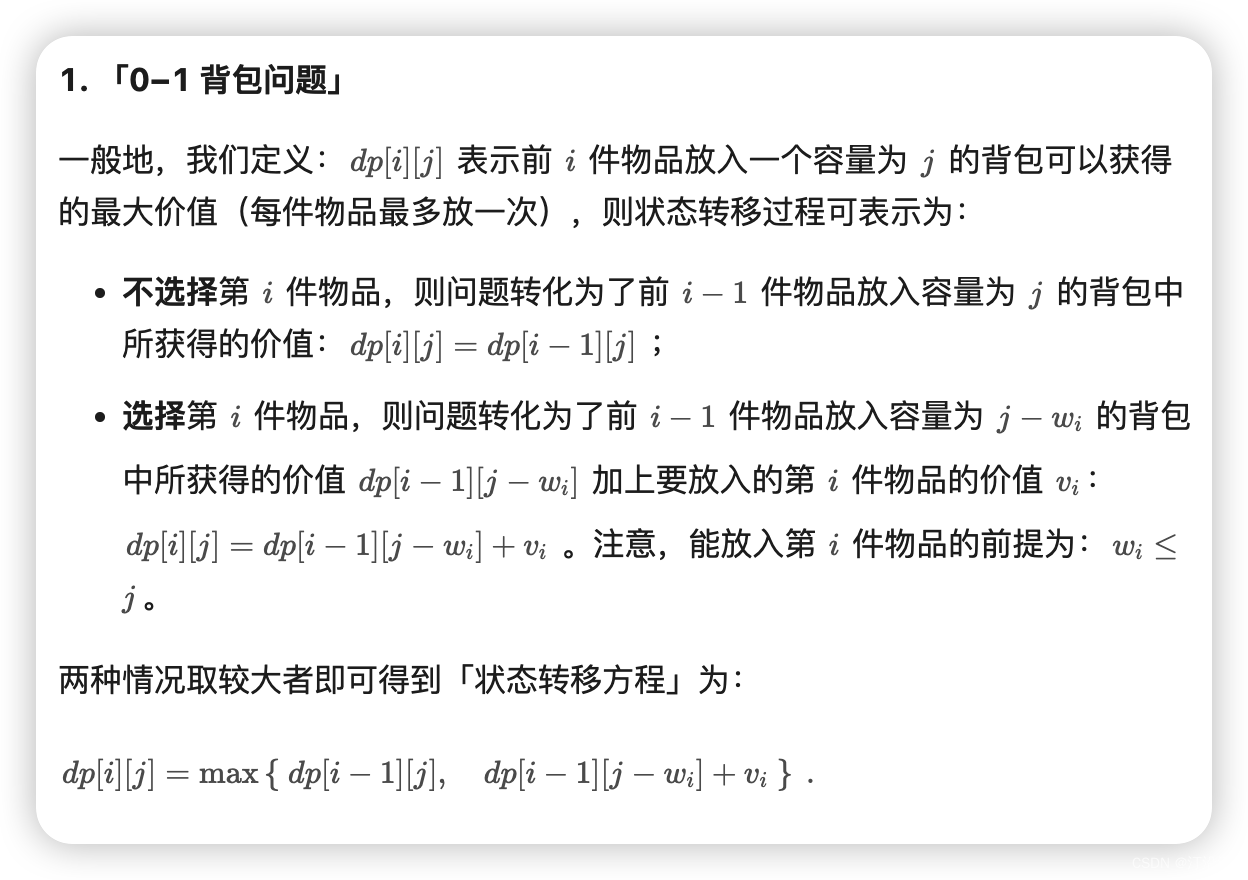

7 动态规划

下面的例子不错: 对于动态规划,能学到不少东西; 你要清楚每一步都在做什么,划分细致就能够拆解清楚! xk. - 力扣(LeetCode) labuladong的算法笔记-动态规划-CSDN博客 动态规划是…...

.net 快速开发框架开源

DF.OpenAPI开源系统 前后端分离,开箱即用,java经典功能.net也具备 系统介绍 DF.OpenAPI是基于Admin.NET二开的,是一个开源的多租户后台管理系统。采用前后端分离技术(前端使用vue.js,后端使用.net 3~.net6ÿ…...

《昇思25天学习打卡营第06天|网络构建》

网络构建 神经网络模型由神经网络层和Tensor操作构成 #实验环境已经预装了mindspore2.2.14,如需更换mindspore版本,可更改下面mindspore的版本号 !pip uninstall mindspore -y !pip install -i https://pypi.mirrors.ustc.edu.cn/simple mindspore2.2.…...

【链表】- 两两交换链表中的节点

1. 对应力扣题目连接 两两交换链表中的节点 2. 实现案例代码 public class ExchangeLinkedListsPairwise {public static void main(String[] args) {// 示例链表:[1, 2, 3, 4]ListNode head new ListNode(1);head.next new ListNode(2);head.next.next new L…...

——抽象工厂模式)

java设计模式(四)——抽象工厂模式

一、模式介绍 改善在工厂方法模式中,扩展时新增产品类、工厂类,导致项目中类巨多的场面,减少系统的维护成本,且一个工厂可以生成多种产品,而不是同一种的产品,比如一个工厂既可以生产鞋子又可以衣服,而不是只能生产鞋子。 二、工厂方法模式 1、实现步骤 第一步: 定义…...

猫抓浏览器插件:网页资源嗅探与下载的终极解决方案

猫抓浏览器插件:网页资源嗅探与下载的终极解决方案 【免费下载链接】cat-catch 猫抓 chrome资源嗅探扩展 项目地址: https://gitcode.com/GitHub_Trending/ca/cat-catch 你是否曾在浏览网页时,看到精彩的视频、音频或图片资源,却苦于无…...

终极LxgwWenKai字体配置指南:如何为VSCode和IDEA打造完美中文编程体验

终极LxgwWenKai字体配置指南:如何为VSCode和IDEA打造完美中文编程体验 【免费下载链接】LxgwWenKai LxgwWenKai: 这是一个开源的中文字体项目,提供了多种版本的字体文件,适用于不同的使用场景,包括屏幕阅读、轻便版、GB规范字形和…...

GLM-OCR场景应用:教育资料数字化、商务文档信息抽取实战

GLM-OCR场景应用:教育资料数字化、商务文档信息抽取实战 1. 引言:文档智能化的时代需求 在信息爆炸的今天,我们每天都要处理大量纸质文档和电子文件。教育机构需要将历年试卷数字化归档,企业财务部门要处理堆积如山的发票和合同…...

Claude Code 用了半年才发现,原来上下文烧没了自己根本不知道!

点击上方卡片关注我设置星标 学习更多AI出海知识用 Claude Code 最怕什么?不是它写错代码,那改改就好。最怕的是写着写着突然质量暴跌,前面说好的逻辑它不认了,该记住的上下文全忘了,然后你反应过来:上下文…...

KMS_VL_ALL_AIO激活工具完全指南:从问题诊断到长效管理

KMS_VL_ALL_AIO激活工具完全指南:从问题诊断到长效管理 【免费下载链接】KMS_VL_ALL_AIO Smart Activation Script 项目地址: https://gitcode.com/gh_mirrors/km/KMS_VL_ALL_AIO 如何诊断Windows/Office激活失败的核心原因? 1.1 激活失败的三大…...

蓝桥杯嵌入式备赛:STM32G431引脚复用功能表,一张图搞定定时器与ADC配置

蓝桥杯嵌入式备赛:STM32G431引脚复用功能实战指南 在蓝桥杯嵌入式赛场上,STM32G431作为官方指定开发平台的核心控制器,其引脚复用功能的灵活配置往往是决定项目成败的关键。许多参赛选手在紧张激烈的比赛中,常常因为引脚配置错误…...

核聚变装置逼近极限时会“漏水“:科学家发现热流平衡决定密度天花板

来源:科学剃刀人类距离可控核聚变又近了一步,但一道隐形天花板始终悬在头顶。当反应堆试图提高燃料密度以获得更多能量时,等离子体总会在某个临界点突然崩溃。这种"密度极限"现象困扰了聚变界四十年。现在,美国麻省理工…...

Windows 11优化终极指南:一键清理预装软件与提升系统性能

Windows 11优化终极指南:一键清理预装软件与提升系统性能 【免费下载链接】Win11Debloat 一个简单的PowerShell脚本,用于从Windows中移除预装的无用软件,禁用遥测,从Windows搜索中移除Bing,以及执行各种其他更改以简化…...

分子构象采样新范式:CREST工具解决药物研发核心挑战

分子构象采样新范式:CREST工具解决药物研发核心挑战 【免费下载链接】crest Conformer-Rotamer Ensemble Sampling Tool based on the xtb Semiempirical Extended Tight-Binding Program Package 项目地址: https://gitcode.com/gh_mirrors/crest/crest 在药…...

别再混淆了!深入对比Vivado中AXI DMA IP核与PS端DMA控制器的角色与分工

深入解析Vivado中AXI DMA与PS端DMA控制器的协同设计 在Zynq/MPSoC平台的软硬件协同开发中,数据搬运效率往往成为系统性能的瓶颈。许多开发者虽然能够熟练使用Vivado中的AXI DMA IP核完成基本数据传输,却对PL端AXI DMA与PS端DMA控制器之间的分工协作机制存…...