Zynq系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTX高速接口,提供8套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本博已有的FPGA图像缩放方案

- 本方案的无缩放应用

- 本方案在Xilinx--Kintex系列FPGA上的应用

- 3、详细设计方案

- 设计原理框图

- SDI 输入设备

- Gv8601a 均衡器

- GTX 解串与串化

- SMPTE SD/HD/3G SDI IP核

- BT1120转RGB

- 自研HLS图像缩放详解

- VDMA图像缓存

- Video Mixer 多路视频拼接详解

- HDMI视频输出架构

- SDI视频输出架构之-->RGB转BT1120

- SDI视频输出架构之-->SMPTE SD/HD/3G SDI + GTX

- SDI视频输出架构之-->Gv8500 驱动器

- SDI视频输出架构之-->SDI转HDMI盒子

- 工程源码架构之-->逻辑设计

- 工程源码架构之-->SDK软件设计

- 4、工程源码1详解-->2路视频缩放拼接,HDMI输出版本

- 5、工程源码2详解-->4路视频缩放拼接,HDMI输出版本

- 6、工程源码3详解-->8路视频缩放拼接,HDMI输出版本

- 7、工程源码4详解-->16路视频缩放拼接,HDMI输出版本

- 8、工程源码5详解-->2路视频缩放拼接,3G-SDI输出版本

- 9、工程源码6详解-->4路视频缩放拼接,3G-SDI输出版本

- 10、工程源码7详解-->8路视频缩放拼接,3G-SDI输出版本

- 11、工程源码8详解-->16路视频缩放拼接,3G-SDI输出版本

- 12、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 13、上板调试验证

- 准备工作

- 2路SDI视频缩放拼接-->输出视频演示

- 4路SDI视频缩放拼接-->输出视频演示

- 8路SDI视频缩放拼接-->输出视频演示

- 16路SDI视频缩放拼接-->输出视频演示

- 14、福利:工程代码的获取

Zynq系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTX高速接口,提供8套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

工程概述

本设计基于Zynq系列的Zynq7100 FPGA开发板实现SDI视频编解码+图像缩放+多路视频拼接,输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机;两路输入SDI视频通过同轴线连接到FPGA开发板的BNC座子,然后同轴视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ的功能;然后差分SDI视频信号进入FPGA内部的GTX高速资源,实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;

本设计的目的是做图像缩放+多路视频拼接后输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了两种输出方式,一种是HDMI输出,另一种是3G-SDI输出,这两种方式都需要对解码BT1120视频进行转RGB和图像缓存操作和图像缩放操作;图像缩放方案采用自研的HLS方案;本设计使用BT1120转RGB模块实现视频格式转换;使用自研的HLS图像缩放模块实现对输入视频的图像缩放操作;使用本Xilinx官方的VDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的PS端DDR3;图像从DDR3读出后,进入Xilinx官方的Video Mixer IP核实现多路视频拼接操作;然后送入HDMI发送模块输出HDMI显示器,这是HDMI输出方式;或者经过RGB转BT1120模块实现视频格式转换,然后视频进入SMPTE SD/HD/3G SDI IP核,进行SDI视频编码操作并输出SDI视频,再经过FPGA内部的GTX高速资源,实现并行数据到高速串行的转换,本博称之为串化,差分高速信号再进入板载的Gv8500芯片实现差分转单端和驱动增强的功能,SDI视频通过FPGA开发板的BNC座子输出,通过同轴线连接到SDI转HDMI盒子连接到HDMI显示器,这是SDI输出方式;本博客提供8套工程源码,具体如下:

现对上述8套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过Xilinx官方的2路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现2路视频拼接操作;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要运行Zynq软核;适用于SDI视频拼接转HDMI场景;

工程源码2

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过Xilinx官方的4路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现4路视频拼接操作;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要运行Zynq软核;适用于SDI视频拼接转HDMI场景;

工程源码3

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制3份得到8路视频,以模拟8路输入(如果你的开发板有8路输入,则无需此操作);再经过8路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为480x540;再经过Xilinx官方的8路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现8路视频拼接操作;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示8路480x540的有效图像,即8分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要运行Zynq软核;适用于SDI视频拼接转HDMI场景;

工程源码4

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制7份得到16路视频,以模拟16路输入(如果你的开发板有16路输入,则无需此操作);再经过16路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为240x540;再经过Xilinx官方的16路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现16路视频拼接操作;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示16路240x540的有效图像,即16分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要运行Zynq软核;适用于SDI视频拼接转HDMI场景;

工程源码5

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过Xilinx官方的2路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现2路视频拼接操作;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTX高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要运行Zynq软核;适用于SDI视频拼接转SDI场景;

工程源码6

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过Xilinx官方的4路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现4路视频拼接操作;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTX高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要运行Zynq软核;适用于SDI视频拼接转SDI场景;

工程源码7

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制3份得到8路视频,以模拟8路输入(如果你的开发板有8路输入,则无需此操作);再经过8路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为480x540;再经过Xilinx官方的8路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现8路视频拼接操作;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTX高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示8路480x540的有效图像,即8分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要运行Zynq软核;适用于SDI视频拼接转SDI场景;

工程源码8

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTX将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制7份得到16路视频,以模拟16路输入(如果你的开发板有16路输入,则无需此操作);再经过16路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为240x540;再经过Xilinx官方的16路VDMA图像缓存方案将视频写入PS侧DDR3做三帧缓存;然后调用Xilinx官方的Video Mixer IP核实现16路视频拼接操作;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTX高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示16路240x540的有效图像,即16分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要运行Zynq软核;适用于SDI视频拼接转SDI场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本博已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

本方案的无缩放应用

本方案有无缩放版本的应用,只做SDI视频编解码,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Kintex系列FPGA上的应用

本方案在Xilinx–Kintex系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

设计原理框图

设计原理框图如下:

注意!!!!

注意!!!!

紫色箭头:3G-SDI输出路径

红色箭头:HDMI输出路径

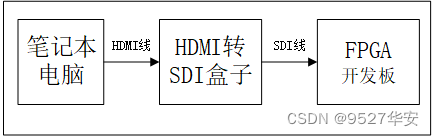

SDI 输入设备

SDI 输入设备有两个,分别接入FPGA开发板的2路SDI视频输入接口;一个是3G-SDI相机,分辨率为1920x1080@60Hz,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

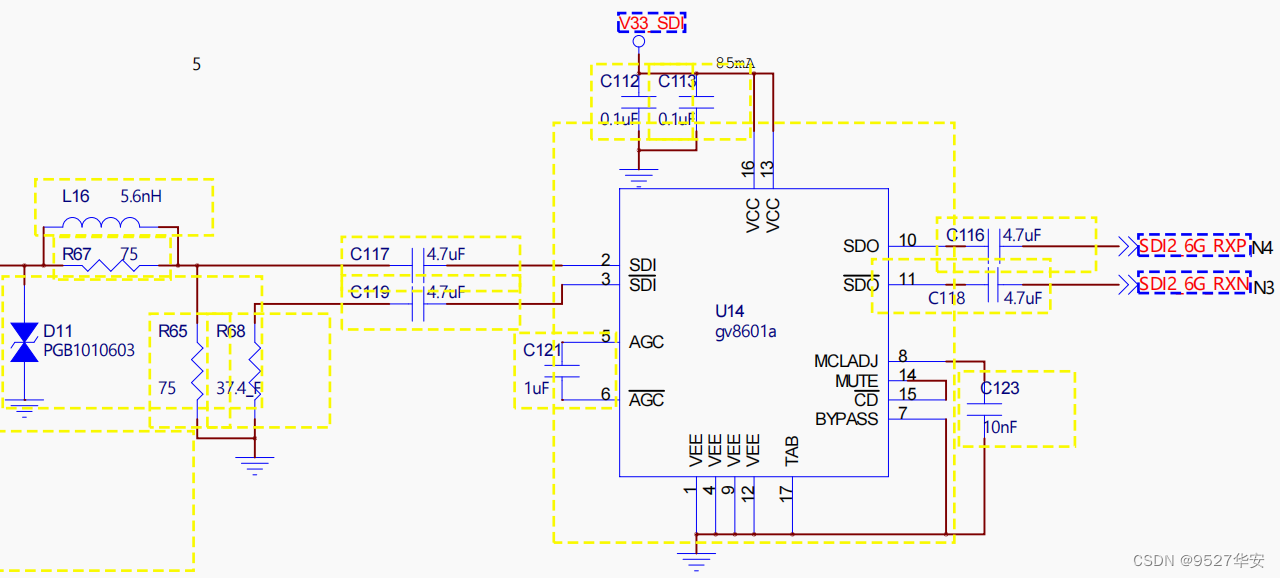

Gv8601a 均衡器

Gv8601a芯片实现单端转差分和均衡EQ的功能,这里选用Gv8601a是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8601a均衡器原理图如下:

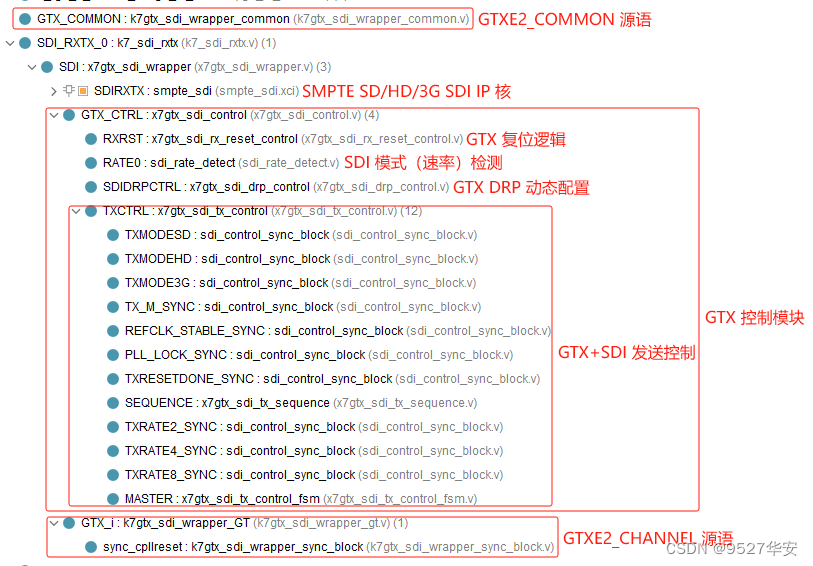

GTX 解串与串化

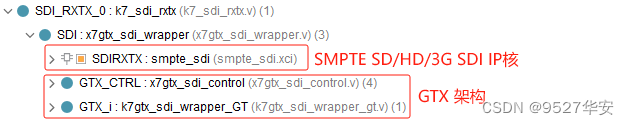

本设计使用Xilinx特有的GTX高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,GTX起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,GTX起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;GTX的使用一般需要例化GTX IP核,通过vivado的UI界面进行配置,但本设计需要对SD-SDI、HD-SDI、3G-SDI视频进行自动识别和自适应处理,所以需要使得GTX具有动态改变线速率的功能,该功能可通过DRP接口配置,也可通过GTX的rate接口配置,所以不能使用vivado的UI界面进行配置,而是直接例化GTX的GTXE2_CHANNEL和GTXE2_COMMON源语直接使用GTX资源;此外,为了动态配置GTX线速率,还需要GTX控制模块,该模块参考了Xilinx的官方设计方案,具有动态监测SDI模式,动态配置DRP等功能;该方案参考了Xilinx官方的设计;GTX 解串与串化模块代码架构如下:

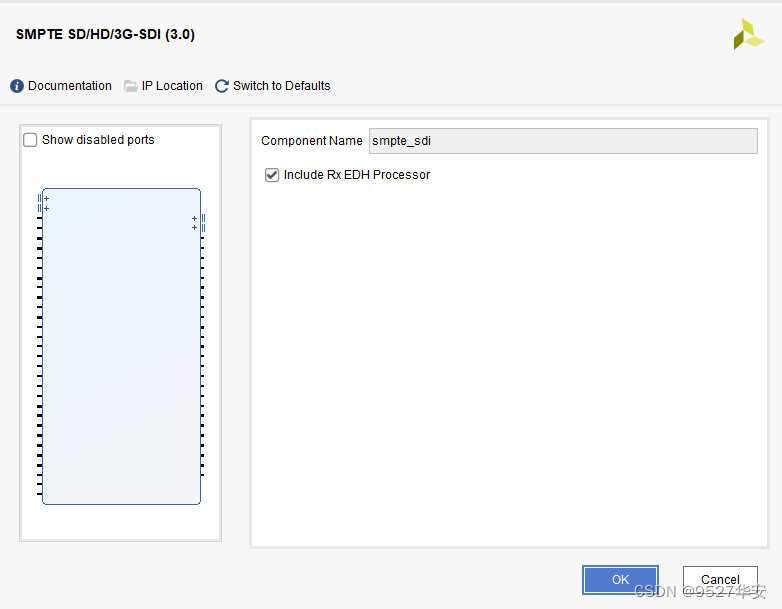

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI视频编解码的IP,该IP配置使用非常简单,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必须与GTX配合才能使用,对于SDI视频接收而言,该IP接收来自于GTX的数据,然后将SDI视频解码为BT1120视频输出,对于SDI视频发送而言,该IP接收来自于用户侧的的BT1120视频数据,然后将BT1120视频编码为SDI视频输出;该方案参考了Xilinx官方的设计;SMPTE SD/HD/3G SDI IP核代码架构如下:

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

BT1120转RGB后调用Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到AXI4-Stream视频流的转换,该IP不需要SDK软件配置;

自研HLS图像缩放详解

本设计的图像缩放采用HLS方案C++代码实现,并综合成RTL后封装为IP,可在vivado中调用该IP,关于这个方案详情,请参考我之前的博客,博客链接如下:

点击直接前往

自研HLS图像缩放优点如下:

1:采用HLS实现,C++代码量很小,核心代码仅3行,并以综合成RTL代码后封装为自定义IP,方便在vivado中调用;

2:采用双线性插值算法,可实现任意比例、任意尺寸缩放,灵活性可谓天花板级别;

3:驱动简单、使用方便,提供SDK驱动程序,在主函数中调用API直接实现缩放操作;

自研HLS图像缩放缺点如下:

1:只适用于Xilinx Zynq系列FPGA,需要其他Xilinx 系列FPGA使用则需要找博主定制,需要修改HLS工程中的FPGA型号,然后重新综合编译封装成IP才能在新的FPGA中使用;

2:只适用于vivado2019.1及其以下版本,从vivado2019.2版本开始,已不能使用其以下版本的HLS IP核,这是Xilinx官方的问题;

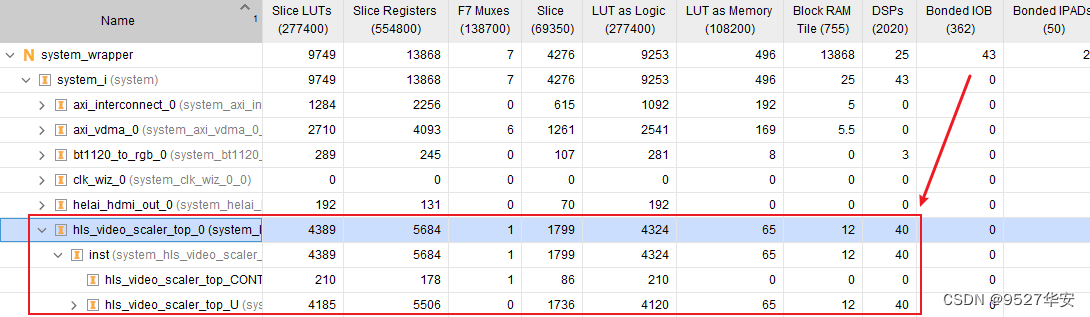

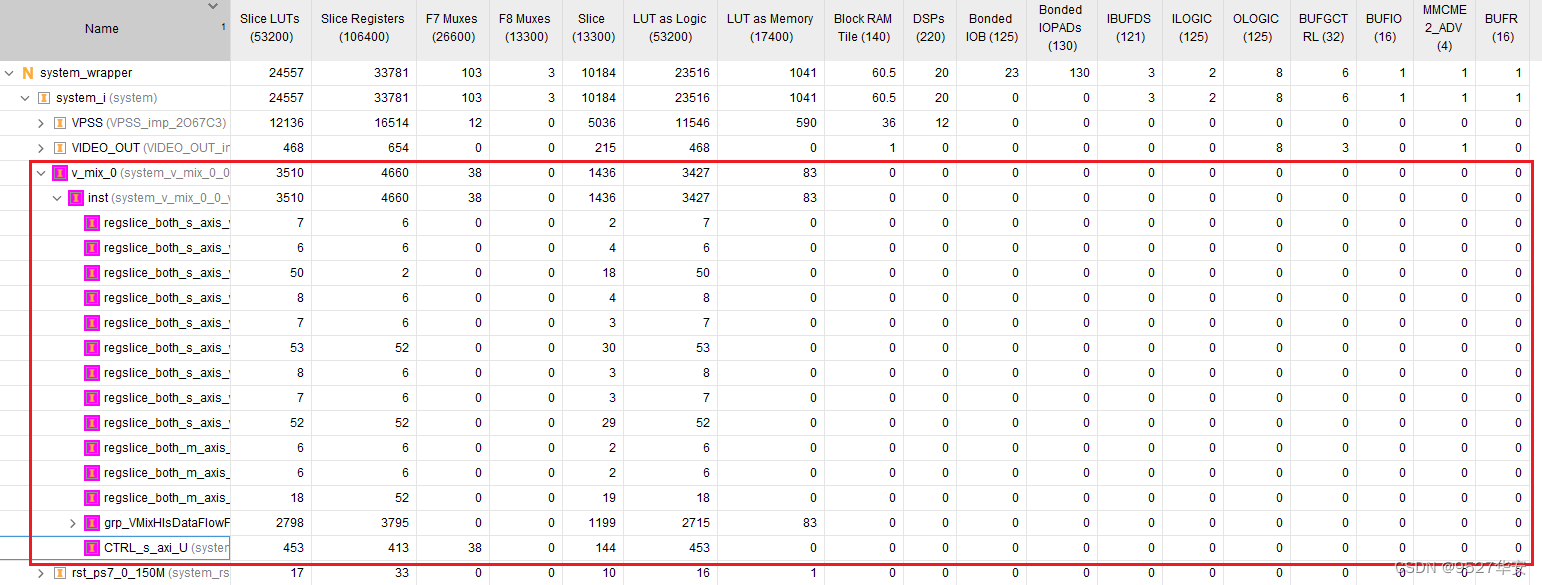

该IP在vivado中的综合资源占用情况如下:

HLS图像缩放需要在SDK中运行驱动和用户程序才能正常工作,我在工程中给出了C语言程序,具体参考工程源码;以工程源码1为例,HLS图像缩放在Block Design设计如下图:

VDMA图像缓存

本设计的视频缓存方案采用Xilinx官方的的VDMA图像缓存架构;缓存介质为PS端DDR3;以工程源码1为例,VDMA使用Xilinx vivado的Block Design设计,如下图:

为了降低延时,VDMA设置为缓存1帧,如下:

Video Mixer 多路视频拼接详解

这里重点介绍一下Xilinx官方的Video Mixer IP;

支持最大分辨率:8K,即可以处理高达8K的视频;

支持最多16层视频拼接叠加,即最多可拼接16路视频;

输入视频格式:AXI4-Stream;

输出视频格式:AXI4-Stream;

需要SDK软件配置,其本质为通过AXI_Lite 做寄存器配置;

提供自定义的配置API,通过调用该库函数即可轻松使用,具体参考SDK代码;

模块占用的FPGA逻辑资源更小,相比于自己写的HLS视频拼接而言,官方的Video Mixer资源占用大约减小30%左右,且更高效:以工程源码1的2路视频拼接为例,Video Mixer逻辑资源如下,请谨慎评估你的FPGA资源情况;

关于这个Video Mixer视频拼接方案详情,请参考我之前的博客,博客链接如下:

点击直接前往

以工程源码1为例,Video Mixer使用Xilinx vivado的Block Design设计,如下图:

HDMI视频输出架构

HDMI视频输出架构如下:

参考Xilinx官方设计,使用VTC+AXI4-Stream To Video Out架构实现输出视频从AXI4-Stream到Native格式的转换;然后使用纯verilog代码实现的RGB888转HDMI模块实现RGB888到HDMI的转换,最后通过显示器显示,RGB888转HDMI模块代码架构如下:

关于RGB888转HDMI模块,请参考我之前的博客,博客地址:点击直接前往

SDI视频输出架构之–>RGB转BT1120

SDI视频输出架构首先要实现VDMA读出的AXI4-Stream到Native格式的转换,得到RGB888视频后再通过RGB转BT1120实现到BT1120视频的转换,其架构如下:

在SDI输出方式下VGA时序模块的像素时钟由SMPTE SD/HD/3G SDI IP核的发送用户时钟提供,在不同的SDI模式下像素时钟不同,比如在3G-SDI模式下像素时钟为148.5M,在HD-SDI的720P@60Hz模式下像素时钟为74.25M;

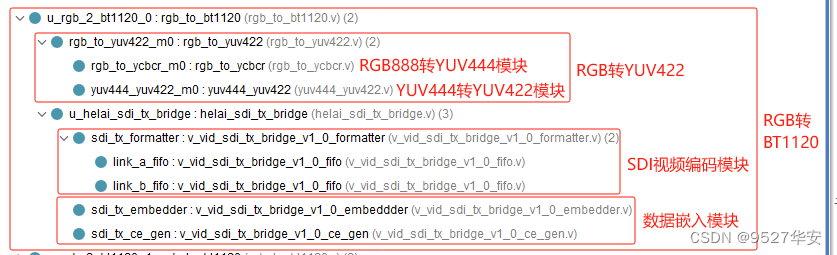

在SDI输出方式下需要使用RGB转BT1120模块;RGB转BT1200模块的作用是将用户侧的RGB视频转换为BT1200视频输出给SMPTE SD/HD/3G SDI IP核;RGB转BT1120模块由RGB888转YUV444模块、YUV444转YUV422模块、SDI视频编码模块、数据嵌入模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

SDI视频输出架构之–>SMPTE SD/HD/3G SDI + GTX

这两部分与接收过程公用相应模块,功能上是接收过程的逆过程,不再赘述;

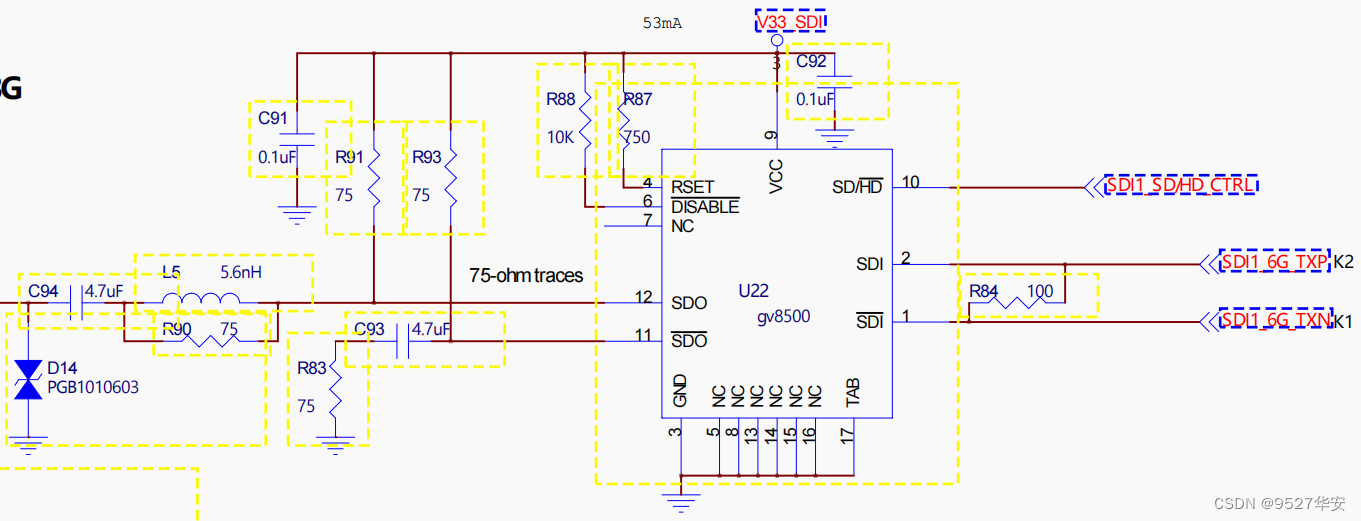

SDI视频输出架构之–>Gv8500 驱动器

Gv8500芯片实现差分转单端和增强驱动的功能,这里选用Gv8500是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8500驱动器原理图如下:

SDI视频输出架构之–>SDI转HDMI盒子

在SDI输出方式下需要使用到SDI转HDMI盒子,因为我手里的显示器没有SDI接口,只有HDMI接口,为了显示SDI视频,只能这么做,当然,如果你的显示器有SDI接口,则可直接连接显示,我的SDI转HDMI盒子在某宝购买,不到100块;

工程源码架构之–>逻辑设计

本博客提供8套工程源码,以工程源码1为例,vivado Block Design设计如下,其他工程与之类似,Block Design设计如下:

以工程源码1为例,工程源码架构如下,其他工程与之类似:

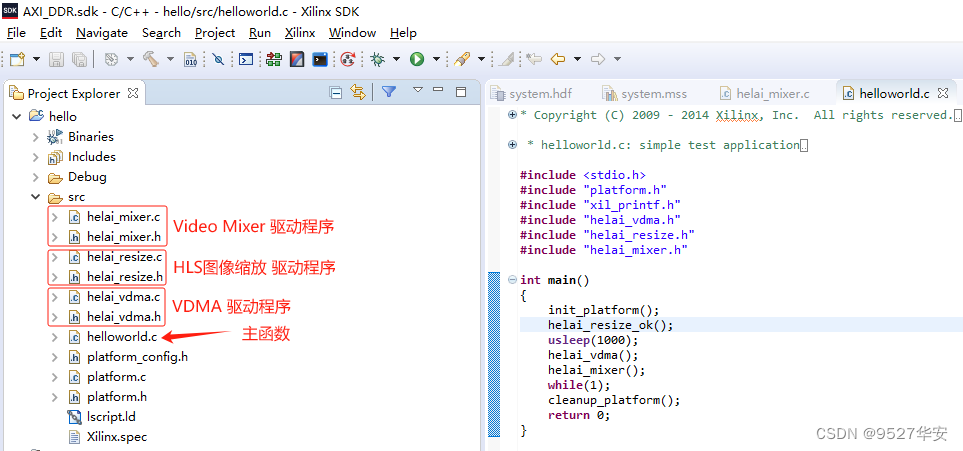

工程源码架构之–>SDK软件设计

本设计工程的PL端时钟由Zynq软核提供,所以需要运行运行SDK以启动Zynq,此外,HLS图像缩放、VDMA、Video Mixer等IP核都需要运行软件驱动才能正常工作,所以,以工程源码1的2路视频拼接为例,SDK软件代码架构如下,其他工程与之类似:

4、工程源码1详解–>2路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:HDMI ,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、工程源码2详解–>4路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制1份,得到2路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制1份,得到2路;

输出:HDMI ,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

6、工程源码3详解–>8路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制3份,得到4路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制3份,得到4路;

输出:HDMI ,1920x1080@60Hz背景下叠加显示8路拼接的480x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到480x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:8路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

7、工程源码4详解–>16路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制7份,得到8路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制7份,得到8路;

输出:HDMI ,1920x1080@60Hz背景下叠加显示16路拼接的240x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到240x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:16路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

8、工程源码5详解–>2路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

9、工程源码6详解–>4路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制1份,得到2路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制1份,得到2路;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

10、工程源码7详解–>8路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制3份,得到4路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制3份,得到4路;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示8路拼接的480x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到480x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:8路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

11、工程源码8详解–>16路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz,然后复制7份,得到8路;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz,然后复制7份,得到8路;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示16路拼接的240x540的有效图像;

图像缩放方案:自研HLS图像缩放;

图像缩放实例:1920x1080缩放到240x540;

图像缓存方案:Xilinx官方VDMA方案;

图像缓存介质:PS端DDR3;

视频拼接方案:Xilinx官方Video Mixer方案;

视频拼接应用:16路视频拼接;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SDI拼接转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

12、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

13、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头和HDMI转SDI盒子;

SDI转HDMI盒子;

HDMI显示器;

我的开发板了连接如下:

2路SDI视频缩放拼接–>输出视频演示

2路SDI视频缩放拼接,输出如下:

Zynq-SDI-2路视频拼接

4路SDI视频缩放拼接–>输出视频演示

4路SDI视频缩放拼接,输出如下:

Zynq-SDI-4路视频拼接

8路SDI视频缩放拼接–>输出视频演示

8路SDI视频缩放拼接,输出如下:

Zynq-SDI-8路视频拼接

16路SDI视频缩放拼接–>输出视频演示

16路SDI视频缩放拼接,输出如下:

Zynq-SDI-16路视频拼接

14、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Zynq系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTX高速接口,提供8套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本博已有的FPGA图像缩放方案本方案的无缩放应用本方案在Xilinx--Kintex系列FPGA上的应用 3、详细设计方案设计原理框图SDI 输入设备Gv8601a 均衡器GTX 解串与串化SMPTE SD/HD/3G SDI IP核BT1120转RGB自研…...

VS2019使用C#写窗体程序技巧(1)

1、打开串口 private void button1_Click(object sender, EventArgs e){myPort cmb1.Text;mybaud Convert.ToInt32(cmb2.Text, 10);databit 8;parity Parity.None;stopBit StopBits.One;textBox9.Text "2";try{sp new SerialPort(myPort, mybaud, parity, dat…...

Python爬虫-requests模块

前戏: 1.你是否在夜深人静的时候,想看一些会让你更睡不着的图片却苦于没有资源... 2.你是否在节假日出行高峰的时候,想快速抢购火车票成功..。 3.你是否在网上购物的时候,想快速且精准的定位到口碑质量最好的商品. …...

适用于PyTorch 2.0.0的Ubuntu 22.04上CUDA v11.8和cuDNN 8.7安装指南

将下面内容保存为install.bash,直接用bash执行一把梭解决 #!/bin/bash### steps #### # verify the system has a cuda-capable gpu # download and install the nvidia cuda toolkit and cudnn # setup environmental variables # verify the installation ######…...

使用conda安装openturns

目录 1. 有效方法2. 整体分析使用pip安装使用conda安装验证安装安装过程中可能遇到的问题 1. 有效方法 conda install -c conda-forge openturns2. 整体分析 OpenTURNS是一个用于概率和统计分析的软件库,主要用于不确定性量化。你可以通过以下步骤在Python环境中安…...

Chameleon:动态UI框架使用详解

文章目录 引言Chameleon框架原理核心概念工作流程 基础使用安装与配置创建基础界面 高级使用自定义组件响应式布局数据流与状态管理 结论 引言 Chameleon,作为一种动态UI框架,旨在通过灵活、高效的方式帮助开发者构建跨平台、响应用户交互的图形用户界面…...

7.10飞书一面面经

问题描述 Redis为什么快? 这个问题我遇到过,但是没有好好总结,导致答得很乱。 答:Redis基于内存操作: 传统的磁盘文件操作相比减少了IO,提高了操作的速度。 Redis高效的数据结构:Redis专门设计…...

[数据结构] 归并排序快速排序 及非递归实现

()标题:[数据结构] 归并排序&&快速排序 及非递归实现 水墨不写bug (图片来源于网络) 目录 (一)快速排序 类比递归谋划非递归 快速排序的非递归实现: (二)归并排序 归…...

面试题 12. 矩阵中的路径

矩阵中的路径 题目描述示例 题解 题目描述 给定一个 m x n 二维字符网格 board 和一个字符串单词 word 。如果 word 存在于网格中,返回 true ;否则,返回 false 。 单词必须按照字母顺序,通过相邻的单元格内的字母构成࿰…...

钉钉扫码登录第三方

钉钉文档 实现登录第三方网站 - 钉钉开放平台 (dingtalk.com) html页面 将html放在 <!DOCTYPE html> <html lang"en"><head><meta charset"UTF-8"><title>登录</title>// jquery<script src"http://code.jqu…...

多GPU系统中的CUDA设备不可用问题

我们在使用多GPU系统时遇到了CUDA设备不可用的问题,详细情况如下: 问题描述: 我们在一台配备有8块NVIDIA GeForce RTX 3090显卡的服务器上运行CUDA程序时,遇到了如下错误: cudaErrorDevicesUnavailable: CUDA-capabl…...

python的列表推导式

文章目录 前言一、解释列表推导式二、在这句代码中的应用三、示例四、使用 for 循环的等价代码总结 前言 看看这一行代码:questions [q.strip() for q in examples["question"]] ,问题是最外层的 中括号是做什么的? 最外层的中括…...

类与对象(2)

我们在了解了类的简单创建后,需要对类的创建与销毁有进一步的了解,也就是对于类的构造函数与析构函数的了解。 目录 注意: 构造函数的特性: 析构函数: 注意: 该部分内容为重难点内容,在正常…...

迂回战术:“另类“全新安装 macOS 15 Sequoia beta2 的极简方法

概述 随着 WWDC 24 的胜利闭幕,Apple 平台上各种 beta 版的系统也都“跃跃欲出”,在 mac 上自然也不例外。 本次全新的 macOS 15 Sequoia(红杉)包含了诸多重磅升级,作为秃头开发者的我们怎么能不先睹为快呢࿱…...

)

如何设计一个秒杀系统,(高并发高可用分布式集群)

设计一个高并发、高可用的分布式秒杀系统是一个非常具有挑战性的任务,需要从架构、数据库、缓存、并发控制、降级限流等多个维度进行考虑。以下是一个典型的秒杀系统设计思路: 1. 系统架构 微服务架构 拆分服务:将系统功能拆分为多个微服务…...

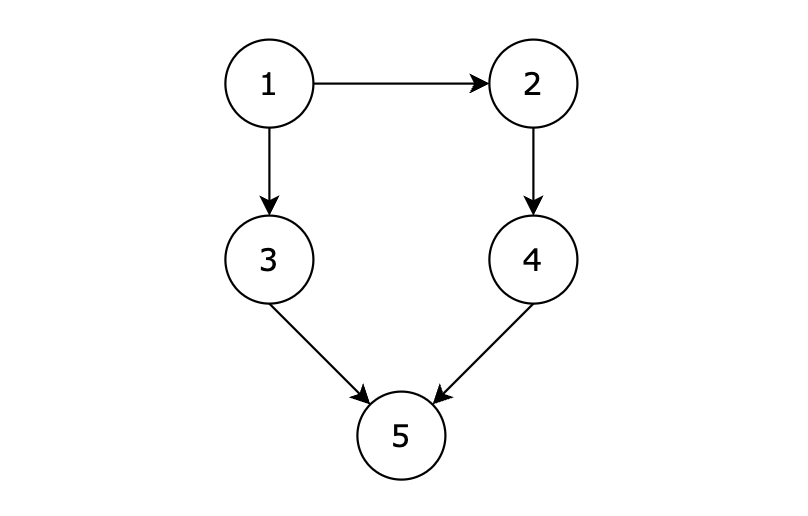

深度优先搜索(所有可达路径)

参考题目:所有可达路径 题目描述 给定一个有 n 个节点的有向无环图,节点编号从 1 到 n。请编写一个函数,找出并返回所有从节点 1 到节点 n 的路径。每条路径应以节点编号的列表形式表示。 输入描述 第一行包含两个整数 N,M&…...

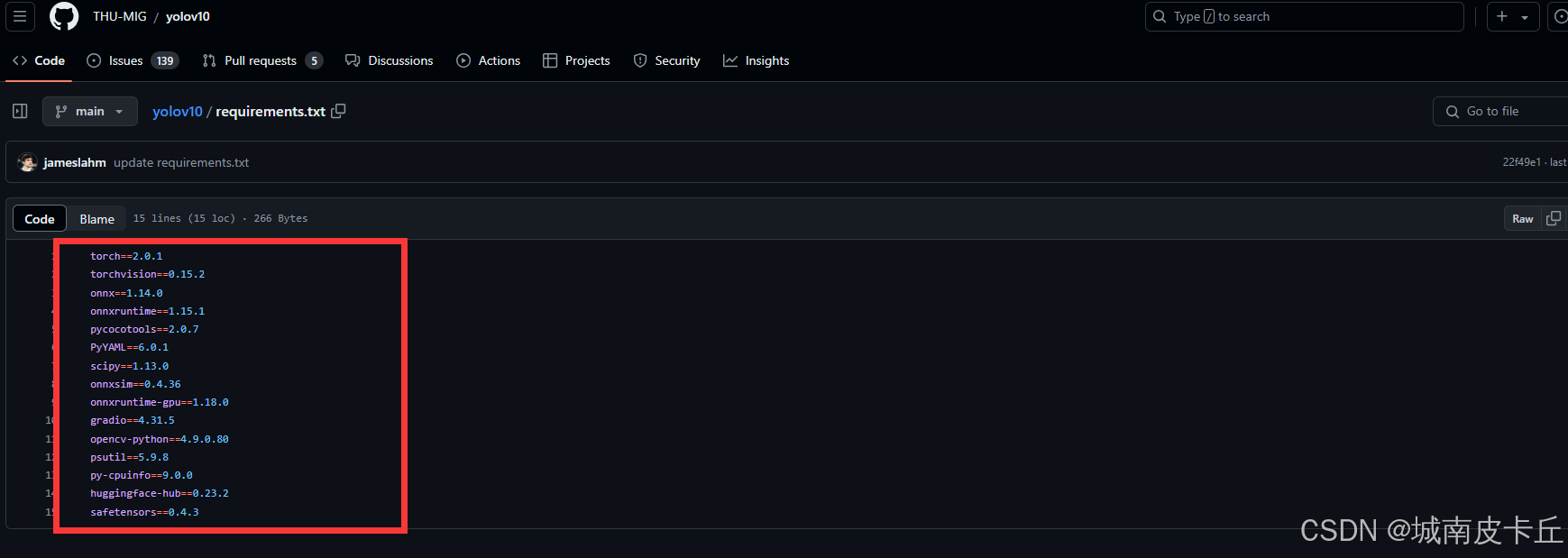

如何配置yolov10环境?

本文介绍如何快速搭建起yolov10环境,用于后续项目推理、模型训练。教程适用win、linux系统 yolo10是基于yolo8(ultralytics)的改进,环境配置跟yolo8几乎一模一样。 目录 第1章节:创建虚拟环境 第2章节:…...

『大模型笔记』GraphRAG:利用复杂信息进行发现的新方法!

GraphRAG:利用复杂信息进行发现的新方法! 文章目录 一. GraphRAG:利用复杂信息进行发现的新方法!1. 将RAG应用于私人数据集2. 整个数据集的推理3. 创建LLM生成的知识图谱4. 结果指标5. 下一步二. 参考文献微软官方推文:https://www.microsoft.com/en-us/research/blog/gra…...

数据结构1:C++实现变长数组

数组作为线性表的一种,具有内存连续这一特点,可以通过下标访问元素,并且下标访问的时间复杂的是O(1),在数组的末尾插入和删除元素的时间复杂度同样是O(1),我们使用C实现一个简单的边长数组。 数据结构定义 class Arr…...

C++入门基础篇(下)

目录 6.引用 6.1 引用的特性 6.2 const引用 7.指针和引用的关系 8.内联函数 9.nullptr 6.引用 引⽤不是新定义⼀个变量,⽽是给已存在变量取了⼀个别名,编译器不会为引⽤变量开辟内存空间, 它和它引⽤的变量共⽤同⼀块内存空间。比如&a…...

CANN/asc-devkit NodeIoNum API文档

NodeIoNum 【免费下载链接】asc-devkit 本项目是CANN 推出的昇腾AI处理器专用的算子程序开发语言,原生支持C和C标准规范,主要由类库和语言扩展层构成,提供多层级API,满足多维场景算子开发诉求。 项目地址: https://gitcode.com/…...

智慧工厂与养殖场的一体化光伏监控系统方案

某企业从事乳制品的生产、销售等全流程业务,新增一套分布式光伏发电系统以平衡能耗支出,主要覆盖乳制品生产加工厂、奶牛养殖场及生态观光牧场等场景,实现“自给自足、余电上网”等综合能源目标。现需要对光伏电站进行联网集中监控࿰…...

5分钟掌握直播间数据抓取:Live Room Watcher终极指南

5分钟掌握直播间数据抓取:Live Room Watcher终极指南 【免费下载链接】live-room-watcher 📺 可抓取直播间 弹幕, 礼物, 点赞, 原始流地址等 项目地址: https://gitcode.com/gh_mirrors/li/live-room-watcher Live Room Watcher是一款基于Java开发…...

3步打造完美macOS菜单栏:Ice菜单栏管理终极指南

3步打造完美macOS菜单栏:Ice菜单栏管理终极指南 【免费下载链接】Ice Powerful menu bar manager for macOS 项目地址: https://gitcode.com/GitHub_Trending/ice/Ice 你是否厌倦了macOS菜单栏上杂乱无章的图标?想要一个整洁、高效且个性化的桌面…...

如何轻松实现Windows风扇智能控制:5个关键技巧打造完美散热系统

如何轻松实现Windows风扇智能控制:5个关键技巧打造完美散热系统 【免费下载链接】FanControl.Releases This is the release repository for Fan Control, a highly customizable fan controlling software for Windows. 项目地址: https://gitcode.com/GitHub_Tr…...

数据采集系统演进:从插卡到嵌入式,技术选型与实战指南

1. 数据采集系统演进史:从插卡到嵌入式的四十年变迁聊起数据采集,很多刚入行的工程师可能觉得这是现代计算机技术催生的产物,无非是传感器、ADC、USB模块和LabVIEW那一套。但如果你翻翻行业的历史,会发现这条技术演进之路远比想象…...

44《实车CAN总线报文ID含义与数据初步解读》

001、CAN总线基础与实车网络拓扑概述 从一次凌晨三点的“丢帧”说起 去年冬天,某主机厂的新能源车型在做冬季标定。凌晨三点,测试工程师打来电话,语气里带着疲惫和焦躁:“VCU发的车速信号,BMS偶尔收不到,但用CANoe监控又一切正常。”我赶到现场,第一件事不是看代码,而…...

ARM架构线程私有内存管理及TPMAX0_EL1寄存器详解

1. ARM架构线程私有内存管理概述在ARMv8/v9架构中,线程私有内存(Thread-Private Memory)是一种重要的内存保护机制。它允许操作系统为每个线程定义专属的内存区域,其他线程无法访问,从而提供硬件级别的内存隔离。这种机…...

大量全新惠普AM4准系统迷你主机涌入咸鱼,支持桌面端5700G处理器,双M2+SATA三盘位,还可选配GTX 1660 Ti 6GB显卡!

众所周知英特尔12代处理器以及AMD锐龙 5000系处理器都是如今极为坚挺的一代平台,两者注定是未来很长一段时间的传家宝平台。而且你敢信,如今依旧还是主流,横跨多年还没有过时和淘汰的迹象,令无数垃圾佬们蠢蠢欲动。其实咸鱼上早就…...

:构造函数与析构函数)

【c++面向对象编程】第3篇:类与对象(二):构造函数与析构函数

目录 一、一个让人头疼的问题 二、构造函数:对象出生时的“第一声啼哭” 1. 最基本的构造函数 2. 带参数的构造函数(重载) 3. 初始化列表:更高效的初始化方式 三、默认构造函数:那个“看不见”的函数 四、析构函…...