Zynq系列FPGA实现SDI编解码转SFP光口传输(光端机),基于GTX高速接口,提供6套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本方案在Xilinx-Kintex7上的应用

- 3、详细设计方案

- 设计原理框图

- 输入Sensor之-->OV5640摄像头

- 输入Sensor之-->HDMI

- VDMA图像缓存

- RGB转BT1120

- GTX 解串与串化

- SMPTE SD/HD/3G SDI IP核

- BT1120转RGB

- HDMI输出

- 工程源码架构之-->逻辑设计

- 工程源码架构之-->SDK软件设计

- 4、工程源码1详解-->OV5640摄像头输入转HD-SDI+SFP光口回环

- 5、工程源码2详解-->OV5640摄像头输入转HD-SDI+SFP光口发送

- 6、工程源码3详解-->SFP光口接收HD-SDI视频转HDMI输出

- 7、工程源码4详解-->HDMI输入转3G-SDI+SFP光口回环

- 8、工程源码5详解-->HDMI输入转3G-SDI+SFP光口发送

- 9、工程源码6详解-->SFP光口接收3G-SDI视频转HDMI输出

- 10、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 11、上板调试验证

- 准备工作

- 输出视频演示

- 12、福利:工程代码的获取

Zynq系列FPGA实现SDI编解码转SFP光口传输(光端机),基于GTX高速接口,提供6套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

工程概述

本设计基于Zynq系列的Zynq7100 FPGA开发板实现SDI视频编解码+SFP光口传输,也就是实现普通Sensor采集转SDI输出,但输出方式不是NBC座子,而是SFP光口,类似于市面上的光端机;理论上输入源可以是多种多样的,取决于你想做的产品,本博主手上只有OV5640摄像头,外加开发板自带了一路HDMI输入接口,所以本设计的Sensor为OV5640摄像头和HDMI,另外,为了照顾收手上没有Sensor或者不是本设计同款Sensor亦或是Sensor方案还未定的情况,本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;

SDI视频转SFP光口发送流程如下:

FPGA采集到Sensor图像后,经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用纯Verilog实现的RGB转BT1120模块实现RGB888视频到BT1120视频流的转换;然后调用Xilinx官方的SMPTE SD/HD/3G SDI IP核实现SDI视频编码操作,本工程有HD-SDI和3G-SDI两种编码;然后调用Xilinx官方的GTX高速资源(直接调用原语),实现并行数据到高速串行的转换,本博称之为串化,差分高速信号再进入板载的SFP光口输出,用光纤连接与其对接的接收设备;

SFP光口接收SDI视频输出流程如下:

FPGA开发板板载SFP光口接收SDI输入视频;差分SDI视频信号进入Xilinx官方的GTX高速资源(直接调用原语),实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,然后调用纯Verilog实现的BT1120转RGB模块实现BT1120视频流到RGB888视频的转换;再经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用本博自研的纯Verilog实现GRB转HDMI模块实现RGB888视频流到HDMI视频转换;最后通过HDMI线连接至显示器显示即可;

本博客提供6套工程源码,具体如下:

现对上述6套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源为OV5640摄像头或动态彩条,分辨率为1280x720@30Hz,可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;FPGA纯verilog实现的i2c配置模块对摄像头进行初始化配置,并采集摄像头数据以RGB888输出,然后调用Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换;然后调用纯Verilog实现的RGB转BT1120模块实现RGB888视频到BT1120视频流的转换;然后调用Xilinx官方的SMPTE SD/HD/3G SDI IP核实现HD-SDI视频编码操作;然后调用Xilinx官方的GTX原语,实现并行数据到高速串行的转换,差分高速信号再进入板载的SFP光口输出,用光纤连接板载的SFP光口的TX和RX接口,形成单板的SFP光口回环;然后FPGA开发板板载SFP光口接收SDI输入视频;差分SDI视频信号进入Xilinx官方的GTX高速资源(直接调用原语),实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,然后调用纯Verilog实现的BT1120转RGB模块实现BT1120视频流到RGB888视频的转换;再经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用本博自研的纯Verilog实现GRB转HDMI模块实现RGB888视频流到HDMI视频转换;最后通过HDMI线连接至显示器显示即可;本工程需要运行Zynq软核;是单板的SFP光口数据回环,即一套工程同时实现了SDI视频转SFP光口发送+SFP光口接收SDI视频输出的完整功能,用于验证该方案的可行性;适用于SDI视频转SFP光口传输场景;

工程源码2

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源为OV5640摄像头或动态彩条,分辨率为1280x720@30Hz,可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;FPGA纯verilog实现的i2c配置模块对摄像头进行初始化配置,并采集摄像头数据以RGB888输出,然后调用Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换;然后调用纯Verilog实现的RGB转BT1120模块实现RGB888视频到BT1120视频流的转换;然后调用Xilinx官方的SMPTE SD/HD/3G SDI IP核实现HD-SDI视频编码操作;然后调用Xilinx官方的GTX原语,实现并行数据到高速串行的转换,差分高速信号再进入板载的SFP光口输出;本工程需要运行Zynq软核;是单板的SFP光口数据发送功能,适用于SDI视频转SFP光口输出场景,比如市面上的光端机;

工程源码3

FPGA开发板板载SFP光口接收SDI输入视频;差分SDI视频信号进入Xilinx官方的GTX高速资源(直接调用原语),实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,然后调用纯Verilog实现的BT1120转RGB模块实现BT1120视频流到RGB888视频的转换;再经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用本博自研的纯Verilog实现GRB转HDMI模块实现RGB888视频流到HDMI视频转换;最后通过HDMI线连接至显示器显示,输出分辨率为1280x720@60Hz;本工程需要运行Zynq软核;是单板的SFP光口数据接收功能,适用于SFP光口接收SDI视频输出场景;

工程源码4

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源为板载的HDMI输入接口或动态彩条,分辨率为1920x1080@60Hz,使用笔记本电脑接入HDMI输入接口,以模拟输入Sensor;可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;FPGA纯verilog实现的i2c配置模块完成HDMI RX的DDC接口配置,EDID配置为1920x1080@60Hz,使用纯VDHL代码实现的HDMI转RGB模块实现输入HDMI视频解码操作,并输出Native的RGB888视频流;然后调用Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换;然后调用纯Verilog实现的RGB转BT1120模块实现RGB888视频到BT1120视频流的转换;然后调用Xilinx官方的SMPTE SD/HD/3G SDI IP核实现3G-SDI视频编码操作;然后调用Xilinx官方的GTX原语,实现并行数据到高速串行的转换,差分高速信号再进入板载的SFP光口输出,用光纤连接板载的SFP光口的TX和RX接口,形成单板的SFP光口回环;然后FPGA开发板板载SFP光口接收SDI输入视频;差分SDI视频信号进入Xilinx官方的GTX高速资源(直接调用原语),实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,然后调用纯Verilog实现的BT1120转RGB模块实现BT1120视频流到RGB888视频的转换;再经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用本博自研的纯Verilog实现GRB转HDMI模块实现RGB888视频流到HDMI视频转换;最后通过HDMI线连接至显示器显示即可;本工程需要运行Zynq软核;是单板的SFP光口数据回环,即一套工程同时实现了SDI视频转SFP光口发送+SFP光口接收SDI视频输出的完整功能,用于验证该方案的可行性;适用于SDI视频转SFP光口传输场景;

工程源码5

开发板FPGA型号为Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;输入源为板载的HDMI输入接口或动态彩条,分辨率为1920x1080@60Hz,使用笔记本电脑接入HDMI输入接口,以模拟输入Sensor;可以通过Sensor模块的顶层参数配置,默认选择Sensor输入;FPGA纯verilog实现的i2c配置模块完成HDMI RX的DDC接口配置,EDID配置为1920x1080@60Hz,使用纯VDHL代码实现的HDMI转RGB模块实现输入HDMI视频解码操作,并输出Native的RGB888视频流;然后调用Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换;然后调用纯Verilog实现的RGB转BT1120模块实现RGB888视频到BT1120视频流的转换;然后调用Xilinx官方的SMPTE SD/HD/3G SDI IP核实现HD-SDI视频编码操作;然后调用Xilinx官方的GTX原语,实现并行数据到高速串行的转换,差分高速信号再进入板载的SFP光口输出;本工程需要运行Zynq软核;是单板的SFP光口数据发送功能,适用于SDI视频转SFP光口输出场景,比如市面上的光端机;

工程源码6

FPGA开发板板载SFP光口接收SDI输入视频;差分SDI视频信号进入Xilinx官方的GTX高速资源(直接调用原语),实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,然后调用纯Verilog实现的BT1120转RGB模块实现BT1120视频流到RGB888视频的转换;再经过Xilinx官方的Video In To AXI4-Stream IP核实现Native视频到 AXI4-Stream视频流的转换,AXI4-Stream视频流是Xilinx推荐的图传数据流形式;然后调用Xilinx官方的VDMA实现图像缓存,缓存介质为PS端DDR3,为了降低延时,VDMA配置为缓存1帧;图像从DDR3中读出后送入ilinx官方的AXI4-Stream To Video Out IP核实现AXI4-Stream视频流到Native视频的转换,即输出带行同步、场同步等同步信号的RGB888视频;然后调用本博自研的纯Verilog实现GRB转HDMI模块实现RGB888视频流到HDMI视频转换;最后通过HDMI线连接至显示器显示,输出分辨率为1920x1080@60Hz;本工程需要运行Zynq软核;是单板的SFP光口数据接收功能,适用于SFP光口接收SDI视频输出场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本方案在Xilinx-Kintex7上的应用

本方案在Xilinx-Kintex7上也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

设计原理框图

设计原理框图如下:

输入Sensor之–>OV5640摄像头

在SDI视频转SFP光口发送工程中,输入Sensor是本工程的输入设备,其一为OV5640摄像头,此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出OV5640摄像头采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

OV5640摄像头需要i2c初始化配置,本设计配置为1280x720@30Hz分辨率,本设计提供纯verilog代码实现的i2c模块实现配置功能;此外,OV5640摄像头还需要图像采集模块实现两个时钟输出一个RGB565的视频转换为一个时钟输出一个RGB888视频,本设计提供纯verilog代码实现的图像采集模块实现配置功能;动态彩条则由FPGA内部逻辑实现,由纯verilog代码编写;将OV5640摄像头配置采集和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

输入Sensor之–>HDMI

在SDI视频转SFP光口发送工程中,输入Sensor是本工程的输入设备,其二为板载的HDMI输入接口,使用笔记本电脑接入HDMI输入接口,以模拟输入Sensor;为了支持1080P@60Hz的输入视频,在硬件设计上需要加上驱动芯片,本设计采用TMDS141RHAR,也可采用其他型号,参考原理图如下:

此外本博主在工程中还设计了动态彩条模块,彩条由FPGA内部逻辑产生,且是动态移动的,完全可模拟Sensor,输入源选择Sensor还是彩条,通过Sensor模块的顶层参数配置,默认选择Sensor输入;Sensor模块如下:

SENSOR_TYPE=0;则输出HDMI接口采集的视频;

SENSOR_TYPE=1;则输出动态彩条的视频;

HDMI输入接口逻辑设计,必须要考虑DDC通信,即通过i2c总线与输入设备协商分辨率,即EDID配置;本设计提供纯verilog代码实现的i2c模块实现EDID配置;此外,TMDS差分视频进入FPGA IO后,需要将其解码为RGB视频,使用纯VDHL代码实现的HDMI转RGB模块实现输入HDMI视频解码操作,并输出Native的RGB888视频流,本博主已将该代码封装为了自定义IP,可在vivado中直接调用,如下:

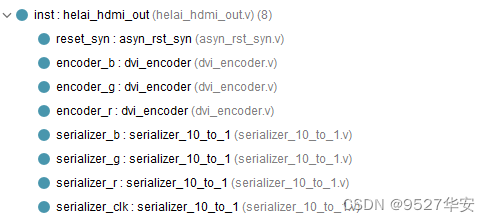

将HDMI转RGB模块和动态彩条进行代码封装,形成helai_OVsensor.v的顶层模块,整个模块代码架构如下:

VDMA图像缓存

本设计的视频缓存方案采用Xilinx官方的的VDMA图像缓存架构;缓存介质为PS端DDR3;VDMA使用Xilinx vivado的Block Design设计,以工程源码1为例,如下图:

为了降低延时,VDMA设置为缓存1帧,如下:

RGB转BT1120

在SDI视频转SFP光口发送工程中,SDI视频输出架构首先要实现VDMA读出的AXI4-Stream到Native格式的转换,得到RGB888视频后再通过RGB转BT1120实现到BT1120视频的转换,其架构如下:

在SDI输出方式下VGA时序模块的像素时钟由SMPTE SD/HD/3G SDI IP核的发送用户时钟提供,在不同的SDI模式下像素时钟不同,比如在3G-SDI模式下像素时钟为148.5M,在HD-SDI的720P@60Hz模式下像素时钟为74.25M;

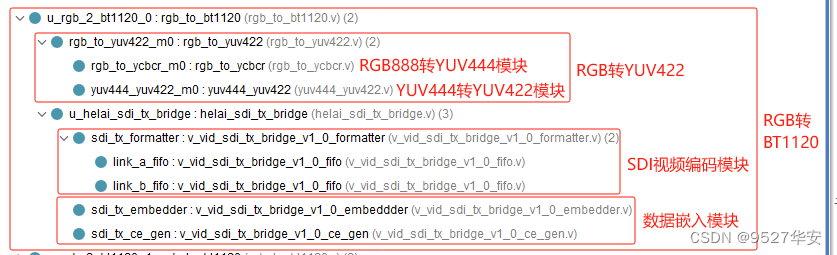

在SDI输出方式下需要使用RGB转BT1120模块;RGB转BT1200模块的作用是将用户侧的RGB视频转换为BT1200视频输出给SMPTE SD/HD/3G SDI IP核;RGB转BT1120模块由RGB888转YUV444模块、YUV444转YUV422模块、SDI视频编码模块、数据嵌入模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

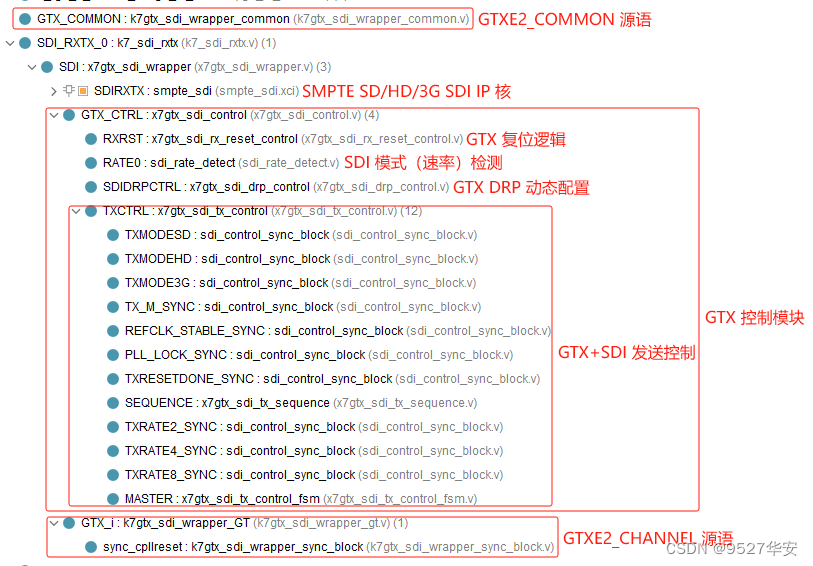

GTX 解串与串化

本设计使用Xilinx特有的GTX高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,GTX起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,GTX起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;GTX的使用一般需要例化GTX IP核,通过vivado的UI界面进行配置,但本设计需要对SD-SDI、HD-SDI、3G-SDI视频进行自动识别和自适应处理,所以需要使得GTX具有动态改变线速率的功能,该功能可通过DRP接口配置,也可通过GTX的rate接口配置,所以不能使用vivado的UI界面进行配置,而是直接例化GTX的GTXE2_CHANNEL和GTXE2_COMMON源语直接使用GTX资源;此外,为了动态配置GTX线速率,还需要GTX控制模块,该模块参考了Xilinx的官方设计方案,具有动态监测SDI模式,动态配置DRP等功能;该方案参考了Xilinx官方的设计;GTX 解串与串化模块代码架构如下:

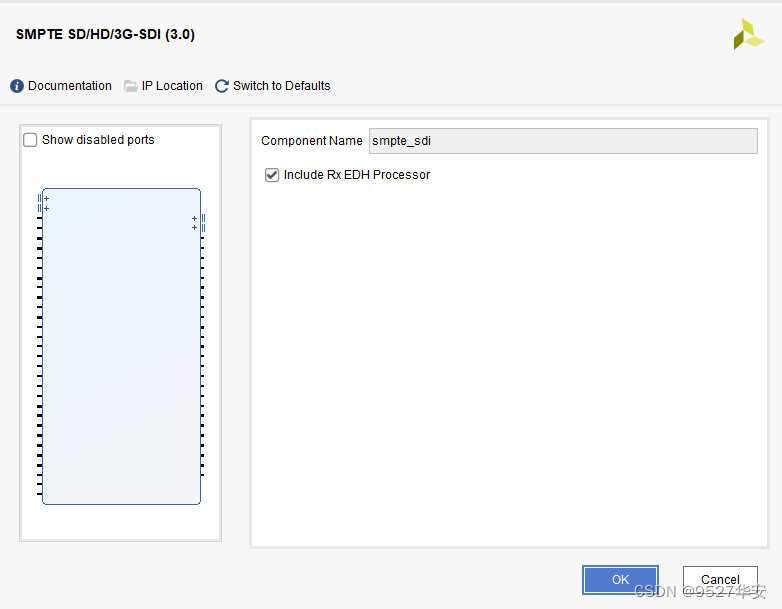

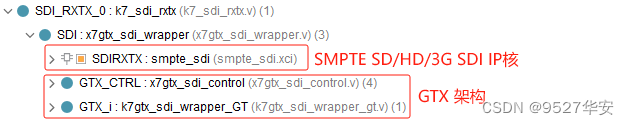

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI视频编解码的IP,该IP配置使用非常简单,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必须与GTX配合才能使用,对于SDI视频接收而言,该IP接收来自于GTX的数据,然后将SDI视频解码为BT1120视频输出,对于SDI视频发送而言,该IP接收来自于用户侧的的BT1120视频数据,然后将BT1120视频编码为SDI视频输出;该方案参考了Xilinx官方的设计;SMPTE SD/HD/3G SDI IP核代码架构如下:

BT1120转RGB

在SFP光口接收SDI视频并输出的工程中,BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

HDMI输出

在SFP光口接收SDI视频并输出的工程中,使用HDMI输出模块将RGB视频编码为HDMI差分信号,HDMI输出模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,代码如下:

关于这个模块,请参考我之前的博客,博客地址:点击直接前往

工程源码架构之–>逻辑设计

本博客提供6套工程源码,以工程源码1为例,该工程同时实现了SDI视频转SFP光口发送+SFP光口接收SDI视频输出的完整功能,vivado Block Design设计如下,其他工程与之类似,Block Design设计为图像缓存架构的部分:

以工程源码1为例,该工程同时实现了SDI视频转SFP光口发送+SFP光口接收SDI视频输出的完整功能,工程源码架构如下,其他工程与之类似:

工程源码架构之–>SDK软件设计

工程源码PL端时钟由Zynq软核提供,所以需要运行运行SDK以启动Zynq,此外,VDMA等IP核都需要运行软件驱动才能正常工作,SDK软件代码架构如下:

4、工程源码1详解–>OV5640摄像头输入转HD-SDI+SFP光口回环

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头或动态彩条,分辨率1280x720@30Hz;

最终视频输出:HDMI,分辨率1280x720@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口TX+RX回环;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现Sensor转SDI+SFP光口传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、工程源码2详解–>OV5640摄像头输入转HD-SDI+SFP光口发送

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:OV5640摄像头或动态彩条,分辨率1280x720@30Hz;

最终视频输出:SFP光口,分辨率1280x720@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口TX发送;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现Sensor转SDI+SFP光口传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

6、工程源码3详解–>SFP光口接收HD-SDI视频转HDMI输出

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:SFP光口,分辨率1280x720@60Hz;

最终视频输出:HDMI,分辨率1280x720@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口RX接收;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SFP光口接收SDI输出的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

7、工程源码4详解–>HDMI输入转3G-SDI+SFP光口回环

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:HDMI(笔记本输入模拟Sensor)或动态彩条,分辨率1920x1080@60Hz;

最终视频输出:HDMI,分辨率1920x1080@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口TX+RX回环;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现Sensor转SDI+SFP光口传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

8、工程源码5详解–>HDMI输入转3G-SDI+SFP光口发送

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:HDMI(笔记本输入模拟Sensor)或动态彩条,分辨率1920x1080@60Hz;

最终视频输出:SFP光口,分辨率1920x1080@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口TX发送;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现Sensor转SDI+SFP光口传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

9、工程源码6详解–>SFP光口接收3G-SDI视频转HDMI输出

开发板FPGA型号:Xilinx-Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:SFP光口,分辨率1920x1080@60Hz;

最终视频输出:HDMI,分辨率1920x1080@60Hz;

缓存方案:Xilinx官方VDMA方案;

缓存介质:PS端DDR3;

SFP光口连接方案:单板SFP光口RX接收;

工程作用:此工程目的是让读者掌握Zynq系列FPGA实现SFP光口接收SDI输出的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

10、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

11、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

笔记本电脑;

OV5640摄像头或者HDMI输入或者动态彩条;

SFP光模块;

光纤;

HDMI显示器;

我的开发板了连接如下:

输出视频演示

以工程源码1为例,输出如下:

Zynq-SDI-SFP-视频收发

12、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Zynq系列FPGA实现SDI编解码转SFP光口传输(光端机),基于GTX高速接口,提供6套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本方案在Xilinx-Kintex7上的应用 3、详细设计方案设计原理框图输入Sensor之-->OV5640摄像头输入Sensor之-->HDMIVDMA图像缓存RGB转BT1120GTX 解串与串化SMPTE SD/HD/3G SDI IP核BT1120转RGBHDMI输…...

SpringBoot实现图形验证码

目录 项目创建 前端代码实现 约定前后端交互接口 需求分析 接口定义 Hutool工具 实现服务器端代码 引入依赖 获取验证码 验证码校验 调整前端代码 随着安全性的要求越来越高,目前许多项目中都使用了验证码,验证码也有各种类型,如 …...

【JVM基础01】——介绍-初识JVM运行流程

目录 1- 引言:初识JVM1-1 JVM是什么?(What)1-1-1 概念1-1-2 优点 1-2 为什么学习JVM?(Why) 2- 核心:JVM工作的原理(How)⭐2-1 JVM 的组成部分及工作流程2-2 学习侧重点 3- 小结(知识点大纲):3-1 JVM 组成3…...

图数据库 - Neo4j简介

深入理解 Neo4j 与 Cypher 语法 什么是 Neo4j Neo4j 是一个基于图的数据库管理系统,它使用图形理论来表示数据关系。这种数据库与传统的关系型数据库不同,它更适合处理高度互联的数据结构。 基本概念 图:在 Neo4j 中,数据以图的…...

C#环境与数据类型

文章目录 C#环境.NET 框架集成开发环境 创建一个C#项目数据类型值类型引用类型对象类型object动态类型dynamic字符串类型string 指针类型 类型转换隐式转换显示转换(强制转换)C#提供的类型转换方法Convert类Parse方法TryParse方法 C#环境 .NET 框架 C#是…...

jenkins系列-06.harbor

https://github.com/goharbor/harbor/releases?page2 https://github.com/goharbor/harbor/releases/download/v2.3.4/harbor-offline-installer-v2.3.4.tgz harbor官网:https://goharbor.io/ 点击 Download now 链接,会自动跳转到上述github页面&am…...

kotlin get set

在 Kotlin 中,如果想实现一个类的属性可以从外部读取但不能修改,可以使用自定义的 getter 和 private setter。以下是一个示例代码: class MyClass {var myProperty: Stringprivate set // 使 setter 私有化,外部无法修改get // …...

Flask包算法服务

常规包算法服务,就是比较简单,直接起一个fastapi就可以了。 import time import asyncio from aidraw import engineer_log as eng from fastapi import FastAPI from pydantic import BaseModel from typing import Optional from aidraw.ardraw import run_aidraw_api# 起…...

中与事件相关的一些核心概念)

Flowable(一个开源的工作流和业务流程管理引擎)中与事件相关的一些核心概念

Flowable(一个开源的工作流和业务流程管理引擎)中与事件相关的一些核心概念 Flowable(一个开源的工作流和业务流程管理引擎)中与事件相关的一些核心概念,包括它们的作用和触发场景。以下是对这些内容的简要说明&#x…...

深度解析:景区客服系统如何助力旅游业可持续发展

一、引言 在全球化与信息化交织的时代背景下,旅游业正以前所未有的速度发展,成为推动经济增长、文化交流与环境保护的重要力量。景区作为旅游业的核心组成部分,其服务质量和管理水平直接影响到游客的满意度和行业的可持续发展。景区客服系统…...

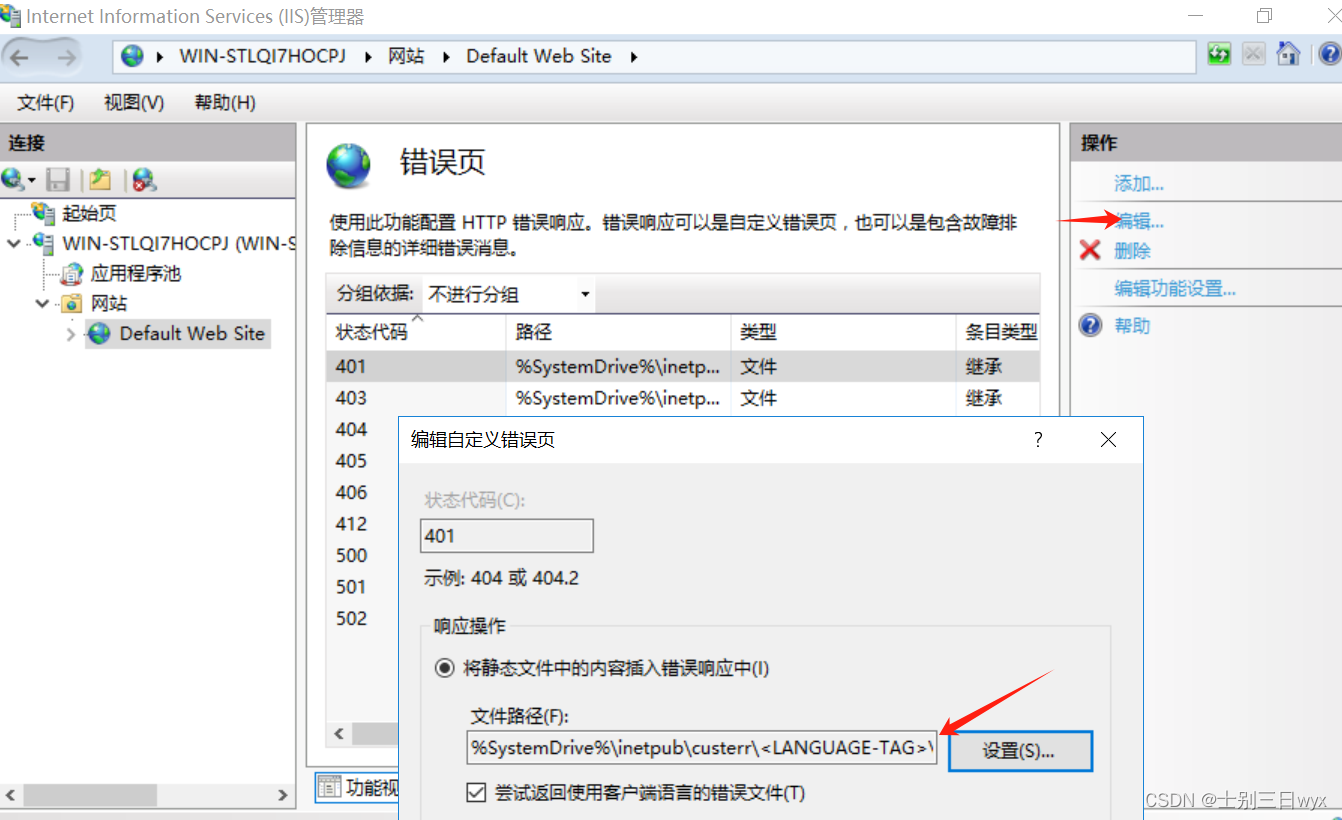

风险评估:IIS的安全配置,IIS安全基线检查加固

「作者简介」:冬奥会网络安全中国代表队,CSDN Top100,就职奇安信多年,以实战工作为基础著作 《网络安全自学教程》,适合基础薄弱的同学系统化的学习网络安全,用最短的时间掌握最核心的技术。 这一章节我们需…...

uniapp 截取两条数据 进行页面翻页滚动

// 轮播信息 <view class"sales_list" ><view class"sales_item" v-for"(item,index) in sellDisplayList" :key"index" click"salesFn(item)"><image :src"item.goodsImg"></image><…...

------1)

python笔记(转存ipynb)------1

list1 ["tom","cat","Lili"] print(list1[0].title())Tom#append()列表方法在列表末尾添加新元素 list1.append(233) print(list1) #可以先创建空列表,再进行追加append(..)以添加[tom, cat, Lili, 233]#insert()列表方法插入元素 l…...

excel系列(二) - 利用 easypoi 快速实现 excel 文件导入导出

一、介绍 在上篇文章中,我们介绍了 apache poi 工具实现 excel 文件的导入导出。 本篇我们继续深入介绍另一款优秀的 excel 工具库:easypoi。 二、easypoi 以前的以前,有个大佬程序员,跳到一家公司之后就和业务人员聊上了&…...

邀请函|2024第八届中国太阳能电池浆料与金属化技术展

2024第八届中国国际太阳能电池浆料与金属化技术展览会 地点:深圳国际会展中心 时间:2025年06-月25日-27日 地点:上海新国际博览中心 时间:2024年12月18日-20日 主办单位:上海氟伦展览有限公司 指导单位:中国新材料技术协会 中国电子学会 耐…...

图像边缘检测:技术原理与算法解析

图像边缘检测是计算机视觉和图像处理中的一个核心任务,它旨在识别图像中亮度变化明显的点,从而识别出图像的边缘。边缘是图像中的重要特征,对于后续的图像分析、物体识别和图像分割等任务具有至关重要的作用。本文将深入探讨图像边缘检测的技…...

【Python星启航】少儿编程精英启蒙之旅 - 大纲

1. 计算机基础与编程环境 计算机的基本构成 编程语言与编程环境介绍 Python语言的特点与优势 安装与配置Python环境 2. 计算机历史与发展 计算机的起源与早期发展 个人电脑的普及与影响 当代计算机技术的前沿动态 计算机在未来教育中的角色 3. 编程基础概念 变量的定义与作…...

MATLAB的mat文件转换成json文件

内参矩阵 (K):相机的内在参数矩阵,通常是一个3x3的矩阵,包含了相机的焦距(fxfx和fyfy)和主点(光学中心)的坐标(cxcx和cycy)。这个矩阵将图像坐标转换为归一化相机…...

STM32第九课:STM32-基于标准库的42步进电机的简单I/O控制(附电机教程,看到即赚到)

一:步进电机简介 步进电机又称为脉冲电机,简而言之,就是一步一步前进的电机。基于最基本的电磁铁原理,它是一种可以自由回转的电磁铁,其动作原理是依靠气隙磁导的变化来产生电磁转矩,步进电机的角位移量与输入的脉冲个数严格成正比…...

文件安全传输系统,如何保障信创环境下数据的安全传输?

文件安全传输系统是一套旨在保护数据在传输过程中的安全性和完整性的技术或解决方案。通常包括以下几个关键组件: 加密:使用强加密算法来确保文件在传输过程中不被未授权访问。 身份验证:确保只有授权用户才能访问或传输文件。 完整性校验…...

基于三菱PLC和MCGS广场喷泉的系统:后发送产品包含梯形图、接线图与原理图等详细资料

基于三菱 plc和MCGS 广场喷泉 我们主要的后发送的产品有,带解释的梯形图接线图原理图图纸,io分配,组态画面最近刚折腾完一个广场喷泉的小项目,用的三菱FX3U PLC加MCGS触摸屏,本来就是冲着练手去的,结果搞…...

)

uniapp实战:ucharts饼图点击事件全解析(附跳转页面实现)

uniapp实战:ucharts饼图点击事件全解析(附跳转页面实现) 在移动端H5开发中,数据可视化图表的交互体验直接影响用户感知。最近接手一个uniapp项目时,发现ucharts的饼图交互存在几个关键痛点:如何区分图例点…...

2026年毕业论文和期刊投稿降AI工具选择对比:不同场景推荐

2026年毕业论文和期刊投稿降AI工具选择对比:不同场景推荐 选降AI工具之前,建议先搞清楚自己的需求。 我整理了几款主流工具的对比,综合来看嘎嘎降AI(www.aigcleaner.com)是性价比最高的。4.8元一篇,达标率…...

M5Unit-DigiClock模块:基于I²C的即插即用数字时钟解决方案

1. 项目概述 M5Unit-DigiClock(SKU: U146)是 M5Stack 推出的一款紧凑型数字时钟单元模块,专为 M5Stack Core 系列主控(如 Core2、CoreS3、Atom Echo)及兼容 ESP32 系列 MCU 的开发板设计。该模块并非通用 RTC 芯片的简…...

UID生成器终极路线图:未来版本将带来的7大突破性功能

UID生成器终极路线图:未来版本将带来的7大突破性功能 【免费下载链接】uid-generator UniqueID generator 项目地址: https://gitcode.com/gh_mirrors/ui/uid-generator UID生成器是分布式系统中确保数据唯一性的核心组件,GitHub加速计划下的ui/u…...

Windows Podman磁盘瘦身实战:WSL vhdx文件压缩与空间回收

1. 为什么你的Windows磁盘总是不够用? 最近在帮同事排查一个诡异的问题:他的开发机C盘明明有200GB空间,装了Podman才两个月就频繁报"磁盘空间不足"。检查后发现,WSL的虚拟磁盘文件ext4.vhdx竟然膨胀到了180GBÿ…...

湖南长沙正规的空调工厂名声

在湖南长沙,寻找一家正规的空调工厂并非易事,但长沙荣幸商贸有限责任公司(以下简称“荣幸商贸”)凭借其卓越的服务和优质的产品,成为了众多消费者的首选。本文将通过具体数据和案例,为您详细介绍荣幸商贸的…...

TongWeb8.0支持JBoss Weld

JBoss Weld 是 CDI(Contexts and Dependency Injection,JSR 299/346/365)的官方参考实现(RI),用于在 Java EE / Jakarta EE 应用中提供依赖注入和上下文管理功能。它不仅内置于 WildFly、GlassFish 等应用…...

ai一键生成node.js环境配置教程,快马平台助你跳过繁琐安装步骤

最近在学习Node.js开发时,发现环境配置这个入门步骤对新手来说确实有点麻烦。不同操作系统下的安装方式差异大,版本选择也让人纠结。好在发现了InsCode(快马)平台的AI辅助开发功能,可以自动生成完整的配置教程,分享下我的使用体验…...

嘉为蓝鲸应用发布中心V6.3发布:流自融合、安全提效,全方位护航企业级应用发布

前言 嘉为蓝鲸应用发布中心鲸舟是企业用于实现一体化应用投产发布的基础设施,能够对应用发布进行统一管理和自动化执行。平台支持单体/微服务应用发布、分布式/容器化发布、应用全生命周期管理,以及蓝绿/金丝雀发布等多种发布场景。发布总览 2026年春季&…...