FPGA开发:Verilog数字设计基础

EDA技术

EDA指Electronic Design Automation,翻译为:电子设计自动化,最早发源于美国的影像技术,主要应用于集成电路设计、FPGA应用、IC设计制造、PCB设计上面。

而EDA技术就是指以计算机为工具,设计者在EDA软件平台上,用硬件描述语言Verilog HDL完成设计文件,然后由计算机自动完成逻辑编译、化简、分割、综合、优化、布局布线、仿真。

EDA涵盖了电子设计、仿真、验证、制造全过程的所有技术,诸如:系统设计与仿真,电路设计与仿真,印制电路板(PCB)设计与校验,集成电路(IC)版图设计、验证和测试,数字逻辑电路设计,模拟电路设计,数模混合设计,嵌入式系统设计,软硬件协同设计,芯片上系统(SoC)设计,可编程逻辑器件(PLD)和可编程系统芯片(SOPC)设计,专用集成电路(ASIC)和专用标准产品(ASSP)设计技术等。

EDA技术的出现极大提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

硬件描述语言HDL

HDL指硬件描述语言,即描述数字电路和系统的语言的统称。

例如,要编写FPGA的代码(即:描述FPGA电路结构)肯定得需要一种语言吧,那C/C++、Java、Python等一众软件语言可以吗?那肯定不行啊,软件语言无法描述出清楚的电路结构,也没有办法约定时钟、走线、端口等。简单一句话,它们没这个实力知道吧😎,所以这时候就需要专用的硬件描述语言HDL了。不过不像软件语言那样枝繁叶茂,经过近三十年的发展,只有Verilog HDL和VHDL二者最终脱颖而出,成为了公认的行业标准,两者逻辑相通。

假如要实现计数器的一个逻辑功能,可以通过编写Verilog语言,对计数器的功能进行描述,完成之后,使用Quarter软件对代码进行分析综合、布局布线等一系列操作,将生成的网表文件下载到FPGA开发板中。

那么在FPGA当中呢,就会实际生成一个硬件电路,其功能就是计数器的功能。

常见的HDL主要有以下4种:

| VHDL |

| Verilog HDL |

| System Verilog |

| System C |

其中VHDL和Verilog HDL在EDA设计中使用最多,也得到几乎所有的主流EDA工具的支持。而Syatem Verilog是Verilog的扩展与延伸。

简要介绍一下Verilog语言的发展历史:

1983年,由由GDA(GateWay Design Automation)公司的Phil Moorby首创,用作Verilog-XL仿真器的内部语言。

1989年,GDA公司被Cadence公司收购,Verilog HDL语言成为Cadence公司的私有财产。

1990年,Cadence公司决定公开Verilog HDL语言,于是成立了OVI(Open Verilog International)组织,负责促进Verilog HDL语言的发展。

2001年,IEEE发布了Verilog HDL 1364-2001标准。在这个标准中,加入了Verilog HDL-A标准,使Verilog有了模拟设计描述的能力。

- Verilog对VHDL的优势

相比于VHDL,Verilog有更广泛的设计群体,成熟的资源也远比VHDL丰富。并且Verilog是一种容易掌握的硬件编程语言(而VHDL需要Ada编程基础)。对于硬件语言学习,首选Verilog。

【注意】无论是Verilog HDL,还是VHDL,不仅包含了结构描述的功能,还包含仿真和验证的功能。对于Verilog HDL,约30%的语句用来实现电路设计,其余语句用于验证和仿真。

IP核简介

IP核,全称知识产权核(Intellectual Property core),在集成电路设计领域中扮演着重要角色。通俗地解释,IP核就是那些已经设计好、验证过,并可以重复使用的电路功能模块或设计模块。它们就像是构建积木一样,可以被设计师们用来快速搭建出复杂的集成电路系统,从而大大缩短设计周期,提高设计效率。

IP核主要分为3类:软IP(Soft IP Core)、固IP(Firm IP Core)和硬IP(Hard IP Core)。

- 软IP

软IP通常是用硬件描述语言(如VHDL或Verilog)编写的功能描述,它只定义了电路的行为和功能,而不涉及具体的电路实现细节(例如实现加法器功能,软核不在乎其内部是晶体管还是MOS管,设计者可自己选择)。这种形式的IP核具有高度的灵活性和可移植性,但需要在后续的设计过程中进行综合和验证。

- 想象一下,你是一位厨师,想要制作一道复杂的菜肴,比如法式炖鸡。在这道菜中,有许多关键的步骤和成分,比如腌制鸡肉、准备蔬菜、炖煮等。现在,我们来用烹饪的步骤来类比软IP核:

- 软IP核就像是一份详细的食谱。这份食谱用文字(就像硬件描述语言)详细描述了制作法式炖鸡的每一个步骤,包括需要哪些食材(就像电路中的元件)、食材的处理方式(就像元件的连接和配置)、以及烹饪的时间、温度等参数(就像电路的时序和性能要求)。但是,这份食谱并没有直接给你提供已经切好的蔬菜、腌制好的鸡肉或者加热好的锅具——它只是告诉你应该怎么做。

- 当你拿到这份食谱时,你需要自己准备食材、工具,并按照食谱上的指示一步步操作。这个过程中,你可能会根据自己的口味和经验对食谱进行一些调整(就像在设计过程中对软IP核进行一定程度的修改和优化)。

- 最终,当你按照食谱完成所有步骤后,你会得到一道美味的法式炖鸡。同样地,在集成电路设计中,当你使用软IP核并按照其描述完成电路设计后,你会得到一个具有特定功能的电路模块。

- 所以,软IP核就像是一份详细的食谱,它提供了实现某个功能所需的所有“配方”和“步骤”,但具体的“食材”和“烹饪过程”还需要设计者自己去准备和实现。这种方式使得设计过程更加灵活,可以根据不同的需求和条件进行调整和优化。

- 固IP

固IP在软IP的基础上,进一步完成了门电路级综合和时序仿真等设计环节,通常以门电路级网表的形式提供给用户。固IP比软IP更接近于物理实现,但仍然保留了一定的灵活性。

- 固IP就像是半成品菜肴。想象一下,你走进一家餐馆的后厨,发现已经有人为你准备好了法式炖鸡的大部分工作:鸡肉已经腌制好,蔬菜也已经切好并部分烹饪过,甚至连炖锅都已经加热到了适宜的温度,并加入了适量的汤底。你只需要将这些半成品组合起来,继续完成最后的炖煮过程,并可能根据个人口味进行微调,比如添加一些香料或调整火候。

- 固IP核在集成电路设计中,就像是部分预制的电路模块。这些模块已经完成了较为关键的设计,比如核心的逻辑功能已经实现,但可能还留有一些接口或参数供用户根据自己的需求进行配置或调整。这样,用户既可以利用已经完成的设计工作,又可以保持一定的设计灵活性和自定义能力。

- 硬IP

硬IP则提供了设计的最终阶段产品——掩膜(Mask),它经过了完全的布局布线,并已经针对特定工艺或购买商进行了优化。硬IP具有极高的可预见性和可靠性,但相对缺乏灵活性。

- 硬IP就像是即食菜肴或者已经做好的成品菜肴。在烹饪的类比中,这就像是走进一家餐馆,直接点了一份法式炖鸡,餐馆的服务员直接把已经烹饪好的、热气腾腾的菜肴端到你的面前。你不需要再去做任何准备或加工,只需要享受这道菜肴的美味即可。

- 在集成电路设计中,硬IP核就是经过完整设计和验证的、可以直接用于生产的电路模块。这些模块通常已经针对特定的工艺或性能要求进行了优化,用户只需要将它们集成到自己的设计中,并按照既定的接口进行连接即可。硬IP核提供了极高的可靠性和可预测性,但相对而言,设计灵活性较低,不太容易进行大规模的修改或定制。

Verilog抽象层级

Verilog的5种模型类型分别代表了电路设计的不同抽象级别,它们分别是系统级(System Level)、算法级(Algorithmic Level)、RTL级(Register Transfer Level)、门级(Gate Level)和开关级(Switch Level)。下面是对这五种模型类型的详细介绍:

- 1. 系统级(System Level)

描述内容:系统级模型使用语言提供的高级结构来实现待设计模块的外部性能。它主要关注系统的整体功能和行为,而不深入到底层的硬件实现细节。

- 系统级模型就像城市规划师制定城市的发展蓝图。他们考虑的是整个城市的布局、交通网络、公共服务设施等宏观层面的设计,而不深入到具体的建筑结构和材料选择。他们关注的是整个系统的功能性和协调性。

- 2. 算法级(Algorithmic Level)

描述内容:算法级模型利用语言提供的高级结构来实现算法的运行。它关注于算法的逻辑和实现方式,而不直接涉及硬件电路的具体实现。

- 算法级模型类似于烹饪食谱。食谱详细说明了制作一道菜所需的步骤和原材料,但它不关注你使用什么样的锅碗瓢盆,也不关心你是用电炉还是煤气灶。它专注于算法的逻辑和流程,即如何达到最终的结果。

- 3. RTL级(Register Transfer Level)

描述内容:RTL级模型描述数据在寄存器之间的流动和如何处理这些数据,以及控制这些数据流动的机制。它是硬件电路设计与行为描述之间的桥梁,与逻辑电路有明确的对应关系。

- RTL级模型就像是组装家具的过程。在这个阶段,你已经有了各个部件(如木板、螺丝、连接件等),并且知道它们是如何通过说明书上的步骤组装在一起的。这类似于在RTL级,你知道了各个寄存器之间的数据流和控制信号,以及如何通过这些寄存器来实现电路的功能。

- 4. 门级(Gate Level)

描述内容:门级模型直接描述逻辑门以及逻辑门之间的连接关系。它关注于电路的基本构建块(如与门、或门、非门等)及其组合方式,与逻辑电路有明确的连接关系。

- 门级模型就像是用积木搭建一个复杂的结构。在这个阶段,你关注的是积木(即逻辑门)之间的连接方式和布局,以构建出你想要的形状和功能。每个积木(逻辑门)都有它特定的功能(如与、或、非等),你需要通过合理的组合来实现你的设计目标。

- 5. 开关级(Switch Level)

描述内容:开关级模型描述器件中三极管和存储节点以及它们之间的连接关系。它深入到电路的物理层面,关注于晶体管级别的电路行为。

- 开关级模型则更像是深入到电子设备内部进行修理。在这个阶段,你需要了解每个元件(如晶体管、电阻、电容等)的物理特性和它们之间的连接方式。你可能需要替换损坏的元件,或者调整电路的连接方式以修复故障。这类似于在开关级,你需要对电路的物理层面有深入的理解,以便进行精确的修复和优化。

HDL综合

HDL综合(Hardware Description Language Synthesis)是电子设计自动化(EDA)中的一个关键步骤,它涉及将硬件描述语言(如Verilog或VHDL)编写的较高层次设计描述(行为级描述)自动转化为较低层次的电路描述或网表(门极形式的模块)。(在这个过程中,综合工具会根据设计约束和优化目标,将抽象的设计转化为可实现的硬件电路。)

通过综合,会产生由与门、或门、非门组成的加法器、比较器、三态门等组合逻辑。

HDL仿真

仿真是对电路模块进行动态的全面测试。

通过观察测试模块的输出信号是否符合要求,可以调试和验证逻辑系统的设计和结构准确与否,并发现问题及时修改。

1. 前(RTL)仿真

假设你正在设计一个简单的计数器模块,使用Verilog HDL编写RTL代码。该计数器模块具有两个输入信号(时钟clk和复位rst_n),一个输出信号(计数值count)。在编写完RTL代码后,你会使用仿真工具(如ModelSim、VCS等)进行前仿真。

仿真过程:

- 1、加载RTL代码到仿真工具中。

- 2、设置输入信号的波形,例如时钟信号clk为周期性信号,复位信号rst_n在开始时为低电平,之后拉高。

- 3、运行仿真,观察输出信号count是否按照预期在每个时钟上升沿递增,并在复位信号为低时重置为0。

- 4、如果发现任何问题(如计数错误、复位不生效等),则回到RTL代码进行调试和修改。

2. 逻辑网表仿真

在RTL代码通过前仿真后,你会将其提交给综合工具(如Design Compiler)进行综合,生成逻辑网表。逻辑网表描述了电路的逻辑连接关系,但尚未进行物理实现。

仿真过程:

- 1、使用综合工具生成逻辑网表。

- 2、将逻辑网表加载到仿真工具中。

- 3、设置与前(RTL)仿真相同的输入信号波形。

- 4、运行仿真,验证综合后的逻辑网表是否仍然满足设计要求。特别注意检查任何由于综合优化而可能引入的问题。

3. 门级仿真

在门级仿真阶段,你可能已经完成了电路的初步布局布线规划,或者至少有了门级网表的详细描述。门级网表包含了具体的门级单元(如与门、或门、触发器等)及其连接关系。

仿真过程:

- 1、加载门级网表到仿真工具中。

- 2、设置输入信号的波形,并考虑门级单元的时序特性。

- 3、运行仿真,观察输出信号的时序特性是否符合设计要求。特别注意检查时钟路径、关键路径等关键部分的时序违例。

- 4、如果发现时序违例或其他问题,则可能需要调整布局布线规划或回到RTL代码进行综合优化。

4. 布线后仿真(后仿真)

在芯片的物理布局布线完成后,你会进行后仿真以验证芯片在实际物理环境下的性能。

仿真过程:

- 1、加载布线后的门级网表到仿真工具中。该网表包含了实际的物理布局和布线信息。

- 2、设置与实际工作环境相似的输入信号波形和条件(如温度、电压等)。

- 3、运行仿真,观察芯片在实际物理环境下的性能表现。特别注意检查时序、功耗、温度等关键参数是否符合设计要求。

- 4、如果发现任何问题(如时序违例、功耗过高、温度过高等),则可能需要调整物理布局布线或重新进行综合优化。

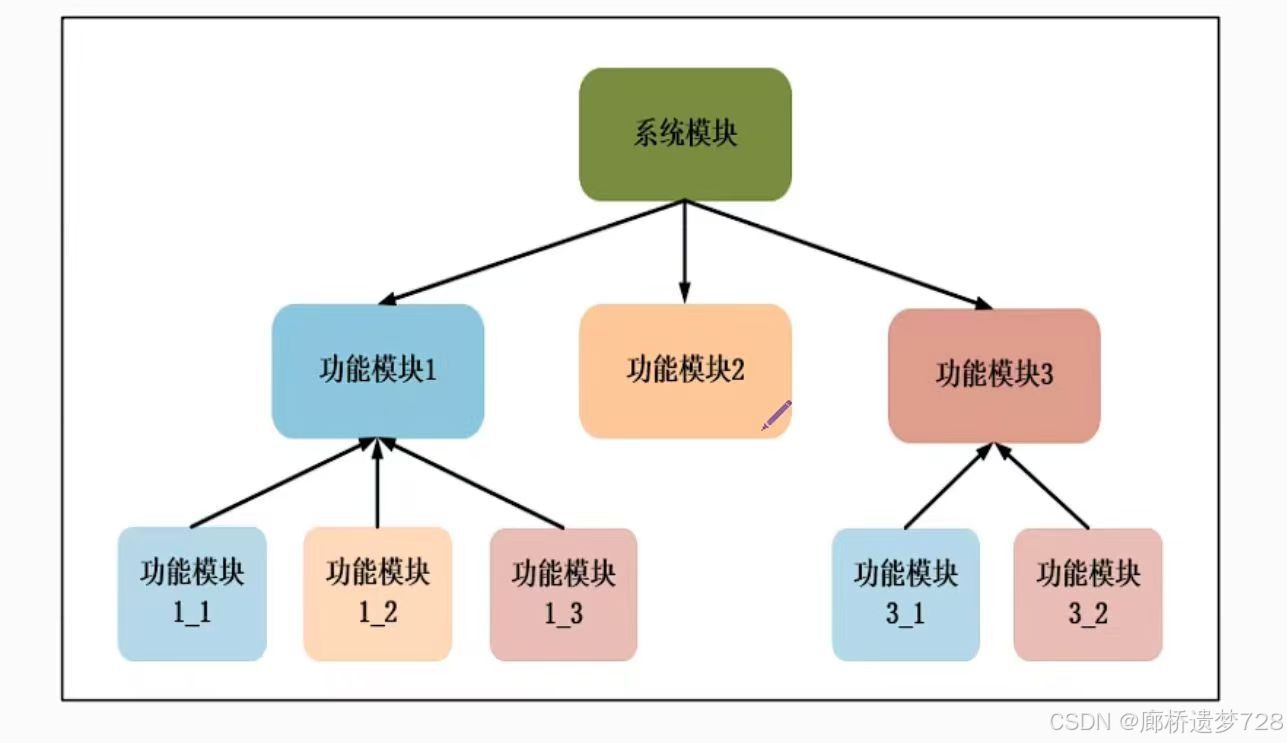

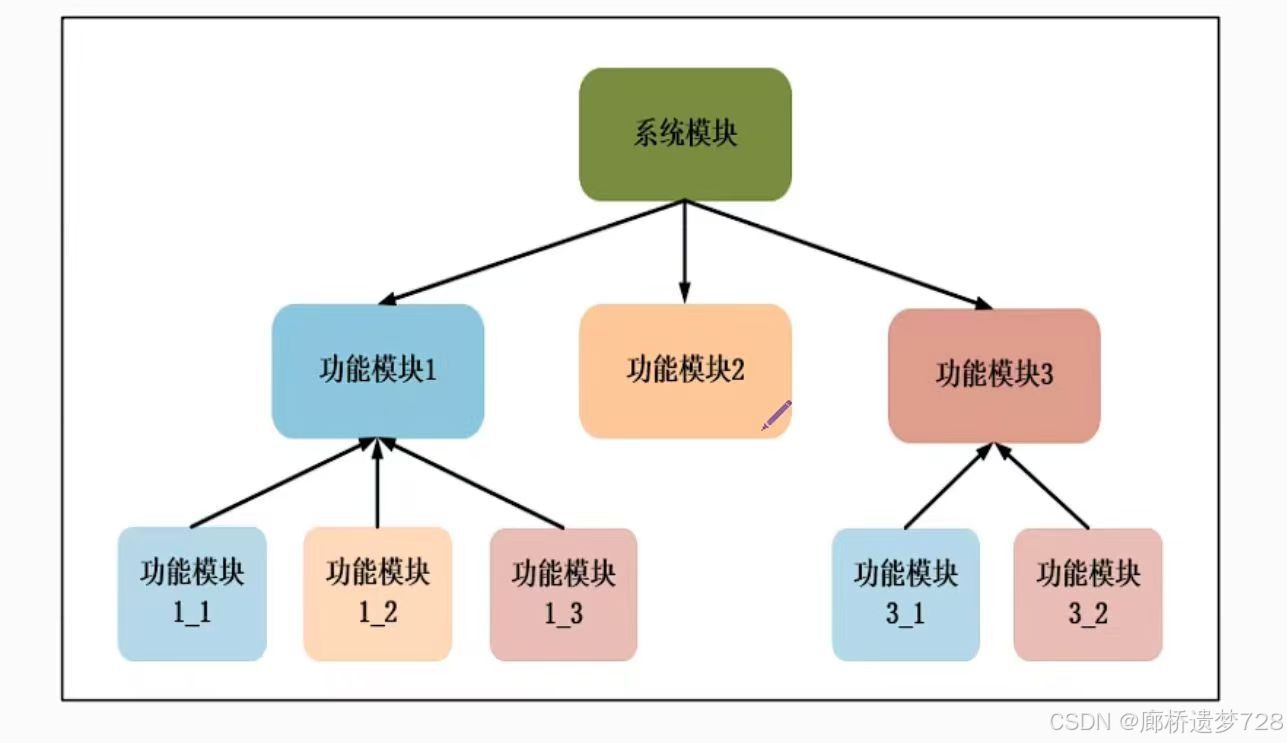

层次化设计

数字电路中根据模块层次不同有两种基本的结构设计方法:自底向上(Bottom-Up)和自顶向下(Top-Down)的设计方法。

- 自底向上

是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的,由基本单元构建高层单元,依次向上,直至构建系统。

- 自顶向下

从系统级开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到直接可以用EDA元件库的元件为止。

- 混合使用

在典型的设计方法中,两种方法是混合使用的。

相关文章:

FPGA开发:Verilog数字设计基础

EDA技术 EDA指Electronic Design Automation,翻译为:电子设计自动化,最早发源于美国的影像技术,主要应用于集成电路设计、FPGA应用、IC设计制造、PCB设计上面。 而EDA技术就是指以计算机为工具,设计者在EDA软件平台上…...

哈希表,算法

一.什么是哈希表 哈希表是一种用于快速数据存取的数据结构。它通过哈希函数将键(key)映射到表中的一个位置,从而实现高效的插入、删除和查找操作。 二.哈希冲突 哈希冲突发生在多个键通过哈希函数映射到哈希表的同一位置时。由于哈希表的大…...

Java数组的定义及遍历

数组的声明 长度不能超过定义的长度。超过则会报错通过下标来访问 数组的遍历 最常用最简单的方法是增强for循环。...

【电路笔记】-反相运算放大器

反相运算放大器 文章目录 反相运算放大器1、概述2、理想反相运算放大器3、实际反相运算放大器3.1 闭环增益3.2 输入阻抗3.3 输出阻抗4、反相运算放大器示例5、总结1、概述 上一篇关于同相运算放大器的文章中已介绍了该运算放大器配置的所有细节,该配置在同相引脚 (+) 上获取输…...

【电子通识】半导体工艺——刻蚀工艺

在文章【电子通识】半导体工艺——光刻工艺中我们讲到人们经常将 Photo Lithography(光刻)缩写成 Photo。光刻工艺是在晶圆上利用光线来照射带有电路图形的光罩,从而绘制电路。光刻工艺类似于洗印黑白照片,将在胶片上形成的图像印…...

vue-router 之如何在模版(template)中获取路由配置信息?

vue-router 之如何在模版(template)中获取路由配置信息? 获取当前路由信息 在vue3 中,route通常使用useRoute()钩子获取的,**代表当前激活的路由信息。**它包含了与当前路由相关的数据,比如路径、参数、查…...

HPL 源码结构分析

文件夹结构: $ cd /home/hipper/ex_hpl_hpcg/ $ pwd $ mkdir ./openmpi $mkdir ./openblas $mkdir ./hpl $ tree 1. 安装openmpi 1.1.1 使用Makefile下载配置编译安装 openmpi Makefile: all:wget https://download.open-mpi.org/release/open-m…...

Java代码审计篇 | ofcms系统审计思路讲解 - 篇3 | 文件上传漏洞审计

文章目录 0. 前言1. 文件上传代码审计【有1处】1.1 可疑点1【无漏洞】1.1.1 直接搜索upload关键字1.1.2 选择第一个,点进去分析一下1.1.3 分析this.getFile()方法1.1.4 分析new MultipartRequest(request, uploadPath)1.1.5 分析isSafeFile()方法1.1.6 分析request.…...

)

【Kubernetes】常见面试题汇总(五)

目录 13.简述 Kubernetes Replica Set 和 Replication Controller 之间有什么区别? 14.简述 kube-proxy 作用? 15.简述 kube-proxy iptables 原理? 16.简述 kube-proxy ipvs 原理? 13.简述 Kubernetes Replica Set 和 Replicat…...

MySQL 解决时区相关问题

在使用 MySQL 的过程中,你可能会遇到时区相关问题,比如说时间显示错误、时区不是东八 区、程序取得的时间和数据库存储的时间不一致等等问题。其实,这些问题都与数据库时区设 置有关。 MySQL Server 中有 2 个环境变量和时区有关,…...

SpringSecurity Context 中 获取 和 更改 当前用户信息的问题

SpringSecurity Context 获取和更改用户信息的问题 SecurityContext 异步线程中获取用户信息 今天在做项目时遇到了一个问题,我需要获取当前用户的 ID。之前,前端并没有存储用户信息,我一直是在后端的 service 中通过 SecurityContext 来获…...

Makefile的四种赋值运算符

Makefile有四种赋值运算符:简单赋值(:)、递归赋值()、条件赋值(?)和追加赋值() 1. 简单赋值(:) 作用:覆盖之前的值。若在多次简单赋…...

framebuffer

framebuffer:帧缓冲、帧缓存 Linux内核为显示提供的一套应用程序接口(驱动内核支持) 分辨率:像素点的总和 像素点: 显示屏:800*600(横向有800个像素点,纵向有600个像素点&#x…...

7.科学计算模块Numpy(4)ndarray数组的常用操作(二)

引言 书接上回,numpy能作为python中最受欢迎的数据处理模块,脱离不了它最核心的部件——ndarray数组。那么,我们今天就来了解一下numpy中对ndarray的常用操作。 通过阅读本篇博客,你可以: 1.掌握ndarray数组的分割 …...

抖音评论区截流脚本软件详细使用教学,抖音私域获客引流的五种方法。

1.先说下什么是抖音截流玩法,截流顾名思义就是在别的博主的视频下面去截流评论潜在流量,然后用评论文案的形式或者其它方式吸引用户加我们的私域~ 玩截流一定不是主动去私信别人,这个就不叫截流了,且一个账号私信多了一定会降权和…...

Linux_kernel移植uboot07

一、移植 根据硬件平台的差异,将代码进行少量的修改,修改过后的代码在目标平台上运行起来 移植还需要考虑硬件环境,驱动只需要考虑内核的环境 二、移植内容 1、移植Uboot uboot属于bootloader的一种,还有其他的bootloader&#x…...

Day-04-QFile打开文件的两种方式

一、UI界面设置两个按键,并直接转到槽函数 二、两种代码展示 #include <QFile> #include <QDebug>//此两种方式中调用函数,应包含的头文件void Widget::on_btnReadFile01_clicked()//第一种打开方式 {//1. 打开文件QFile file;file.setFile…...

第三部分:4---进程地址空间

目录 数组的空间分配解析: 物理地址和虚拟地址: 虚拟地址空间: 进程地址空间的本质: 为什么要有进程地址空间? 页表对进程访问内存的检查: 进程地址空间和页表如何关联起来? 进程的独立…...

【Android】程序开发组件—探究Jetpack

引言 Jetpack是一个开发组件工具集,它的主要目的是帮助我们编写出更加简洁的代码,并简化我们的开发过程,在这么多的组件当中,最需要我们关注的其实还是架构组件,接下来就对Jetpack的主要架构组件进行学习!…...

pytorch torch.norm函数介绍

torch.norm 函数用于计算张量的范数(norm),可以理解为张量的“长度”或“大小”。根据范数的不同类型,它可以衡量不同的张量性质。该函数可以计算 向量 和 矩阵 的多种范数,如 L1范数、L2范数、无穷范数 等。 1. 函数…...

IDEA里Artifact选war还是war exploded?一个设置解决Tomcat热部署难题

IDEA中Artifact选择:war与war exploded深度解析与热部署实战 每次修改完JSP页面后都要重启Tomcat?看着进度条缓慢加载,开发效率被硬生生拖慢。这可能是大多数Java Web开发者都经历过的痛苦。问题的根源往往藏在IDEA那个不起眼的Artifact配置选…...

基于宏观通胀预测模型的利率预期重定价:华尔街降息路径为何出现系统性回撤?CPI成为关键校准变量

摘要:本文通过宏观通胀预测模型,结合利率预期曲线重定价算法与市场情绪迁移分析,对当前美通胀路径、CPI数据影响及华尔街降息预期变化进行系统性建模,分析利率政策预期从宽松交易向数据依赖模式切换的结构性原因。一、市场情绪迁移…...

)

毕设成品 深度学习安全帽佩戴检测(源码+论文)

文章目录 0 前言🔥这两年开始毕业设计和毕业答辩的要求和难度不断提升,传统的毕设题目缺少创新和亮点,往往达不到毕业答辩的要求,这两年不断有学弟学妹告诉学长自己做的项目系统达不到老师的要求。为了大家能够顺利以及最少的精力…...

)

保姆级教程:在Windows 10/11上从源码编译Groops(含Qt环境变量避坑指南)

从零构建Groops编译环境:Windows系统下的完整避坑指南 当你在GNSS数据处理领域深耕时,一款强大的开源工具能让你事半功倍。Groops作为重力场恢复和精密定轨的瑞士军刀,其功能强大但编译过程却可能让新手望而却步。本文将带你一步步穿越编译迷…...

【最新v2.7.1 版本安装包】OpenClaw 新手部署全攻略,无需命令零代码一键安装保姆级

Windows 一键部署 OpenClaw 教程|5 分钟搞定本地 AI 智能体,告别复杂配置 核心亮点 零代码门槛|全程可视化|无需手动配置运行环境|内置全部运行依赖|28 万 Tokens 额度 前言 2026 年开源圈热度居高不下…...

Typora“激活”与“美化”实战指南

1. Typora基础认知与安装准备 Typora作为一款广受好评的Markdown编辑器,其独特之处在于将编辑与预览合二为一。不同于传统Markdown编辑器需要分屏显示源代码和渲染效果,Typora实现了真正的所见即所得——你在编辑区输入的Markdown语法会实时转换为排版效…...

Python3+bypy实战:给你的服务器加个百度网盘自动备份脚本

Python3bypy实战:构建服务器自动化备份系统 在数据为王的时代,服务器上的关键数据如同数字生命线。想象一下凌晨三点收到数据库崩溃的告警,却发现最后一次备份是两周前的手动快照——这种噩梦般的场景正是自动化备份要消灭的敌人。本文将带你…...

CLion集成LVGL与SDL:打造高效嵌入式GUI模拟开发环境

1. 为什么需要CLionLVGLSDL组合? 如果你正在开发嵌入式设备的图形界面,肯定遇到过这样的困境:每次修改UI都要烧录到硬件上测试,一个简单的颜色调整可能要反复折腾十几分钟。我在开发智能手表项目时就深受其害,直到发现…...

Python包安装全攻略:从pip、conda到离线安装,总有一种方法适合你

Python包安装全攻略:从pip、conda到离线安装,总有一种方法适合你 在Python开发中,依赖管理是每个开发者必须掌握的核心技能。无论是数据科学家搭建机器学习环境,还是Web开发者部署Django应用,都离不开Python包的安装与…...

5分钟快速上手:XUnity.AutoTranslator游戏实时翻译插件终极指南

5分钟快速上手:XUnity.AutoTranslator游戏实时翻译插件终极指南 【免费下载链接】XUnity.AutoTranslator 项目地址: https://gitcode.com/gh_mirrors/xu/XUnity.AutoTranslator 还在为语言障碍而无法畅玩海外Unity游戏吗?XUnity.AutoTranslator正…...