FPGA基本结构和简单原理

前言:

FPGA全程为(Field Programmable Gate Array)现场可编程逻辑阵列,以基本的逻辑为主可以实现大多数芯片可以实现的功能,比如说:ASIC芯片等,在半导体领域有着重要的作用。 本文以Xilinx公司生产的XC7K325T和XC7K480T开始介绍,注意这里不对Xilinx的Kintex-7000的功能和特点介绍,主要分别讲解内部结构和简单原理,因此本文主要针对所有通用型FPGA的原理。

本文部分内容参考书籍《Vivado从此开始》和《FPGA原理和结构》,本文基于Vivado仿真结果进行讲解

FPGA基本结构:

在Xilinx的FPGA开发工具在实时综合时可以看到仿真生成的图像,这就是FPGA内部使用资源的情况,下图是打开了芯片布线资源的预览图。

这个芯片就是XC7K480T,这个和芯片的型号关系不大,主要是内部的结构,如果放大了看会看到很多的线以及各种的逻辑门。

上图是FPGA的资源表,可以看到很多的参数,这些参数很大程度上决定了内部逻辑单元的多少,这些参数和FPGA的性能息息相关。

基本逻辑单元(LC):

逻辑单元LC是(Logic Cell)是Xilinx定义的一种标准逻辑单元,作为FPGA的最基本参数,它的多少决定了FPGA的性能有多强大(更准确的说是处理的能力有多强大)。要注意的是这里的逻辑单元是LC,不是CLB(可配置逻辑单元),LC是用于完成用户最小逻辑的单元这两个不一样,在下面统称为基本逻辑单元。

基本逻辑单元主要分为SLICEM和SLICEL两种,这两种内部都含有4个6输入查找表,3个数据选择器(MUX),和1个进位链(Carry Chain),以及8个触发器(Flip-Flop)组成。

上图就是SLICE(包括SLICEM和SLICEL)内部基本结构,虽然它们之间的结构大体相同,但是它们在功能上有一点差别,下面分别对这两种结构分别进行介绍。

SLICEM:

从Vivado中可以看到这个逻辑单元的基本结构,和上面的SLICE结构相似但是所支持的功能有所不同。

SLICEM支持逻辑函数发生器,ROM,分布式RAM以及移位寄存器,这个基本逻辑单元在基础上做了一些添加,参见下图(截取了4个查找表中的两个)。

标准的SLICE上是由4个6输入查找表,在SLICEM上明显多了很多的接口,这些的作用就是扩展基本逻辑单元,可以说SLICEM是SLICE的升级版。

SLICEL:

从Vivado中可以看到这个逻辑单元的基本结构,和上面的SLICE结构相似但是所支持的功能有所不同。

SLICEL支持逻辑函数发生器,ROM,它支持的要比SLICEL要少,是一个比较基础的基本逻辑单元,参见下图(截取了4个查找表中的两个)。

上图可以看出内部是6输入的查找表,它就是基本的逻辑单元。

总结:

下图就是SLICEM和SLICEL两种结构的区别表格。

这个就是参数手册上说明的内部逻辑单元的数量,它可以指的是SLICEM或SLICEL两种型号的多少,比如说:XC7K480T指的是有SLICEM或SLICEL共计有480K个(基本逻辑单元数量)。

可配置逻辑单元(CLB):

可配置逻辑单元(Configurable Logic Block,CLB),这个逻辑单元是配置的就是最小运行模块(基本逻辑单元LC需要驱动模块,才能像可配置逻辑单元那样运行),当然一个FPGA中CLB单元是很丰富的。

在Xilinx中可配置逻辑单元主要分为两种分别是CLBLL和CLBLM这两种,在里面有着两个基本逻辑单元(LC)和驱动控制块,CLBLL的内部由两个SLICEL组成,CLBLM的内部由SLICEL和SLICEM组成。

CLBLL:

CLBLL的内部由两个SLICEL和控制单元组成,下图是两个可配置逻辑单元连接示意图,省略了CLB控制单元,

ViVado综合后预览图由两个SLICEL单元和控制器组成。

在上图可以看出控制器下标注CLBLL控制单元,灰色线从查找表输入端到输出端都连接着控制单元,最后再连接到输出部分。

CLBLM:

CLBLM的内部由SLICEL和SLICEM组成,下图是两个可配置逻辑单元连接示意图,省略了CLB控制单元,

ViVado综合后预览图由SLICE和SLICEM两个单元和控制器组成。

在上图可以看出控制器下标注CLBLM控制单元,灰色线从查找表输入端到输出端都连接着控制单元,最后再连接到输出部分。

FPGA布线资源:

几乎不难发现FPGA内部所有的块都用着线段来进行连接,上文中讲解可配置逻辑单元几乎所有的内容都有布线,在Vivado中可以看到两种布线,第一种是绿色的线条,第二种是灰色的线段,Vivado通过这两种线段来区分线段是否使用,在芯片内部所有的线都是连接好的,只取决于开关块是否使用或开启这一条线。

绿色的线条指示的是使用过的,这经常会在Vivado综合之后出现,显示出布线使用的情况。

灰色的线指的是没有使用过的布线资源,

在FPGA内部通过开关块来控制布线的使用,里面的布线资源很多几乎是全连接模式,它们是通过开关块来进行选择使用的是什么布线。

触发器:

在每个SLICE模块中包含8个存储单元,其中4个只能作为触发器使用另外4个可以配置为触发器或锁存器使用,在FPGA中的触发器可以是D触发器(D Flip-Flop)、T触发器(T Flip-Flop)、JK触发器(JK Flip-Flop)等。这些触发器通常嵌入在FPGA的查找表(LUT)中,或者作为独立的存储单元存在。

触发器在进位链的后面是在基本逻辑单元里面的一个模块,触发器的数量有很多,主要是控制输出的触发等操作,最后传输到CLB控制单元中,虽然简单但可以实现很多的功能,比如说:边沿触发,存储功能,同步触发,异步触发等内容。

上图是在基本逻辑单元中的触发器,最左边两个两个为一组组成FF触发器,最右边两个两个为一组组成一个FF触发器和T触发器的共同体(可以进行两种触发器之间的切换)。

FPGA简单原理:

上文介绍了FPGA基本的结构,当然这样的结构算不上FPGA,只能算的上是PLD(可编程逻辑器件),是FPGA就少不了RAM,触发器,DSP单元等内容。

通过介绍FPGA常用块来介绍基本原理,和各部分使用情况,在这里要知道在Xilinx的FPGA中一个芯片被化为了很多的区域,这些不同的区域除了有可配置逻辑单元,开关块,有着不同的功能,以XC7K480T为列,参见下图:

可以看到FPGA内部主要单元块是由竖向排列的,蓝色的线是可配置逻辑单元和开关块,上面的看起来是红色的小点点是放大后会看到是BRAM(片上内存),上面的看起来是绿色的小点点是放大后会看到是DSP(数字信号处理器),这个的数量在FPGA中是很多的。

FPGA开关块:

上面介绍了最基本的可配置逻辑单元,在FPGA中还少不了开关块这样的控制逻辑的单元,说真的开关块的关系和可配置逻辑单元(CLB)的关系很微妙,有的可配置逻辑单元有着两个快关块(这样的配置是相对来说较少的),有的可配置逻辑单元有着一个开关块,在连接到外围电路时列如DSP,BRAM是才是两个开关块。

开关块的布局很有规律,几乎是每一个可配置逻辑单元都有一个,但是仍有许多的可配置逻辑资源有两个开关块,把开关块这一章节放到FPGA简单原理中是因为它涉及到了基本原理。

单开关块结构,这样的结构是很标准的每一个可配置逻辑单元都有一个开关块,控制着可配置逻辑单元打开和关闭情况。

他们主要是一个可配置逻辑单元+开关块进行连接然后在FPGA中一列的形式排序相连,多个这样的结构组成一列组,这样的结构在FPGA中随处可见。

双开关块结构,这样的结构在FPGA中少于单开关块,他们不是单纯的可配置逻辑单元+开关块的结构,主要是出现在一个列组的边缘,在下图的最左面(下图像没有照到)通常连接的是BRAM或是DSP等元件。

开关块的布线使用,下图就是开关块使用时候的情况可以看到块内部的基本布线很乱,连接到外部布线很整齐,包括了可配置逻辑单元控制器(这里单指CLB控制器)也是很乱。

为什么布线会很乱,这其实是Vivado生成的简化显示,真实的开关块内部结构很复杂,这就要谈论开关块内部的基本原理。

开关块的基本原理:

开关块主要分为几种结构:第一种是基于闪存的可编程开关(非易失存储),第二种是静态存储器,最后一种是反熔丝式(几乎已经不常用了)。

先来说明第一种,如果对单片机的寄存器结构有一定的研究就很好理解,它们的结构和存储存芯片的结构相似,主要是浮栅晶体管和场效应管的共同作用。

它的原理就是一个存储器每次可存储一个字节,就是这一个字节就可以控制开关块的打开和关闭的状态。

当然了光有浮栅晶体管可不行还要有FPGA信号的传输才行,于是就出现了基于闪存的可编程开关。

在注释中可以知道两个开关共用浮栅和控制栅极。左边的小开关用于编程,右边的大开关用于连接FPGA信号。把栅极共用当浮栅晶体管最左边的通过编程后存储了开关信号(布尔信号,只有0和1),到了右边FPGA用户信号就是连接到开关块的外部信号。

这也就是说FPGA的开关块里面有多少个输出或输入端子就说明内部有多少个基于闪存的可编程开关。

第二种是基于静态存储器原理,这个是比较常用的,不用保存的连接数据,更符合FPGA的JTAG调试状态,这个存储器断电后数据丢失,开关块的连接线路也会重新定义。

静态存储器由两个CMOS反相器(等效为非门电路)构成的触发器和两个传输晶体管组成,输出的Q信号再连接MOS管控制着开关块单个单元的开启和关闭,同时静态存储器利用触发器的双稳态记录数据,而数据通过PT进行。

FPGA片上RAM:

下面主要拿XC7K480T芯片的X1Y1模块组讲解RAM部分,由于FPGA是时序逻辑电路所以片上的RAM是不可获取的一部分,已知的FPGA片上RAM有两种分别是:BRAM(FPGA中定制的RAM资源,属于是片上),DRAM(是由片上逻辑单元拼凑出来的主要是用到了触发器),下图就是BRAM片上RAM资源。

片上RAM的结构类似于内存芯片(DDR结构),或者类似于D触发器的结构,上面的图中是简单的构造, 在图中可以可以得知一个BRAM主存储的附近有很多的辅助的模块。

其中在里面有BRAM_CASC_MUX_R(或L)这个模块主要的作用是控制模块多个BRAM相连接,他们的连接关系是通过控制模块来进行相连接的并不是直接相连,再通过模块和模块之间相连接就类似于总线控制器。

可以看到一个BRAM存储器连接着有着5个单独的开关块(是所有的结构都是这样的)和可配置逻辑单元+开关块的结构,在外边有着辅助接口控制器组成,当然这些放大后都是可以看到具体的端口号。

DSP单元:

下面主要拿XC7K480T芯片的X1Y1模块组讲解DSP部分,DSP数字信号处理器,在FPGA中主要作用是对一些开关块的信号和数字信号进行处理,可以实现很多的功能,这里的DSP是DSP48在这里可以实现48个核心功能比如说:乘法,加法,累加等基本运算。

DSP单元的外围辅助模块要比BRAM的要少,因为DSP之间的连接主过DSP辅助模块相连接的,上图的下面的那个模块就是DSP连接控制单元,DSP的内部结构主要是由Xilinx公司官方定制的,只知道主要用途,至于内部的结构还是不得而知了。

但是基于DSP48的基本结构还是有的。

在内部有预加法器,乘法器,后加法器和逻辑单元等内容,实现各种信号处理的功能。

在直接连接到DSP单元的是开关块控制其它内容(所有结构都是这样的),这样的连接主要是为了方便对可配置逻辑单元的控制。

FPGA-I/O块:

下面主要拿XC7K480T芯片的X0Y0模块组讲解I/O块部分,说真的FPGA内部由几百K个逻辑单元和数百万调连接线,以及几十K个开关块,这样多的逻辑资源却要映射到几百个I/O端口上,可想而知这样的I/O接口块是很复杂的。

下图就是基本的I/O接口块,内部的东西很多但是没有BRAM单元,没有DSP单元,没有可配置逻辑单元,只有开关块,I/O总线块,电平信号转换模块以及输出接口模式设定块。

开关块的作用和在可配置逻辑单元中的作用相似,只不过是没有可配置逻辑单元,并且两个开关块相连接进行输出前的基本信号控制。

上图就是I/O接口输出模块前端,这主要实现对信号数据的汇总和输出信号的输出驱动,接口驱动芯片部分和开关块相似里面对信号的基本处理。

针对图中橘色的块有两个作用:一个是辅助I/O块逻辑的(上图中没有连接到外部I/O接口的部分),另一个作用就是并行数据转串行数据的作用。

上图就是逻辑块用作数据类型转换的作用,绿色的部分就是I/O输出接口模块。

仔细观察就会发现这里面有上下拉电阻,以及输出电平转换(因为芯片内部逻辑电压很低大约有1V),和各种接口类型的支持的电路,这就包括上下拉电阻(三态,高电平,低电平,高阻),输出驱动管(场效应管等)虽然要比单片机的模式少很多,但是针对FPGA来说是足够使用了。

结尾:

本文主要讲解FPGA的基本结构和简单原理,通过上面的基本的模块和单元就能组成简单的FPGA当然了这只是针对纯逻辑的FPGA的介绍,如果是ZYNQ系列(内部嵌入了ARM内核),还是要单独来介绍的,如果是Xilinx公司的Ultra Scale+系列的内部结构还是不一样的。

本文共计5700字,如果你细心看完一定会有收获,了解了很多关于FPGA内部结构和原理,如果善于研究会发现为什么内部时钟会有延时,Vivado的仿真就是针对内部布线资源的信号延迟进行验证,基本原理是什么,手册上的一些重要的参数指的又是什么,或许你应该会知道怎样使用FPGA内部资源才能做到尽量的节省,有更多的关于FPGA的知识和内容都要从学习中才能知道。

————————【完】———————

相关文章:

FPGA基本结构和简单原理

前言: FPGA全程为(Field Programmable Gate Array)现场可编程逻辑阵列,以基本的逻辑为主可以实现大多数芯片可以实现的功能,比如说:ASIC芯片等,在半导体领域有着重要的作用。 本文…...

【machine learning-七-线性回归之成本函数】

监督学习之cost function 成本函数权重、偏置如何实现拟合数据成本函数是如何寻找出来w和b,使成本函数值最小化? 在线性回归中,我们说到评估模型训练中好坏的一个方法,是用成本函数来衡量,下面来详细介绍一下 成本函数…...

Stable Diffusion Fooocus批量绘图脚本

当当当挡~,流动传热数值计算之余发布点AIGC相关文章,希望大家能喜欢~ 1 Stable Diffusion各种UI分析对比 提示:此部分主要是对SD各种界面的简要介绍和对比,只关注Fooocus批量绘图的读者可直接跳到第二部分。 Stable Diffusion …...

Web 安全基础教程:从零基础入门到精通

一、Web 安全概述 (一)Web 安全的定义与重要性 1.定义 Web 安全是指保护 Web 应用程序免受各种网络威胁,确保 Web 服务的保密性、完整性和可用性。在当今数字化时代,Web 应用广泛存在于各个领域,从电子商务到社交媒…...

ubuntu 20.04 ‘Wired Unmanaged‘ 网络无法配置解决方法

问题描述 系统:ubuntu20.04连上网线后右上角没有有线网络连接的图标,在网络配置界面也只有VPN和无线网络的配置;实际上此时电脑已经连接网络,通过DHCP获得IP地址可以正常访问网络。 解决办法 ubuntu有有两套网络管理软件:serve…...

前端实战:使用JS和Canvas实现运算图形验证码(uniapp、微信小程序同样可用)

图形验证码是网站安全防护的重要组成部分,能有效防止自动化脚本进行恶意操作,如何实现一个简单的运算图形验证码?本文封装了一个简单的js类,可以用于生成简单但安全的图形验证码。它支持自定义验证码样式,包括字体大小…...

SQL Server 语句日期格式查找方法

1. SQL Server中,处理日期格式和查找特定日期格式方法示例 在SQL Server中,处理日期格式和查找特定日期格式的记录是一个常见的需求。SQL Server提供了多种函数和格式选项来处理和比较日期。以下是一个详细的示例,展示了如何根据特定日期格式…...

【Python报错已解决】python setup.py bdist_wheel did not run successfully.

🎬 鸽芷咕:个人主页 🔥 个人专栏: 《C干货基地》《粉丝福利》 ⛺️生活的理想,就是为了理想的生活! 专栏介绍 在软件开发和日常使用中,BUG是不可避免的。本专栏致力于为广大开发者和技术爱好者提供一个关于BUG解决的经…...

查询结果是1条记录,但执行更新却是2条记录原因查找

1、问题 在 sqlserver2008 数据库 select * from userinfo WHERE username SP4267ED2409011; 查询结果是1条记录,但执行更新 UPDATE userinfo SET qt qt 2.0 WHERE username SP4267ED2409011; 结果是这样的 Affected rows: 1 Affected rows: 1 返回了2个&#x…...

校园网站的管理与建设心得体会

随着时代发展的需要,学校网站建设如雨后春笋般的涌现出来。在这股大潮的带动下我校校园网网站建设也逐步开展深入。通过数年的发展,我校的校园网建设取得了长足发展,架构了数字化交流平台,整理了专题学习网站资源,开设…...

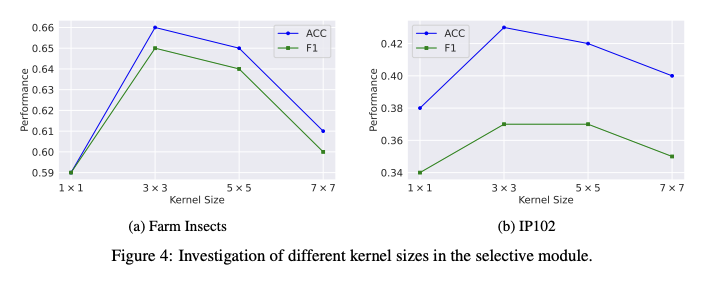

智慧农业——InsectMamba利用状态空间模型对害虫进行分类

介绍 论文地址:https://arxiv.org/abs/2404.03611 害虫分类是农业中的一个重要问题。准确识别有害害虫可减少对作物的损害,确保粮食安全和环境的可持续发展。然而,害虫及其自然环境的高度拟态性和物种多样性使得视觉特征的提取极具挑战性。…...

基于机器学习的癌症数据分析与预测系统实现,有三种算法,bootstrap前端+flask

研究背景 癌症作为全球范围内最主要的死亡原因之一,已成为当代医学研究和公共健康的重大挑战。据世界卫生组织(WHO)的统计,癌症每年导致全球数百万人的死亡。随着人口老龄化、环境污染和生活方式的改变,癌症的发病率逐…...

docker|Oracle数据库|docker快速部署Oracle11g和数据库的持久化(可用于生产环境)

一、 容器数据持久化的概念 docker做为容器化的领先技术,现在广泛应用于各个平台中,但不知道什么时候有一个说法是docker并不适用容器化数据库,说容器化的数据库性能不稳定,其实,这个说法主要是因为对docker的数据持…...

uni-app 聊天界面滚动到消息底部

目录 问题 组件 页面 使用的API 总结 问题 当你发一个消息,但是消息却需要你自己向下滑你才能看见,否则一直呗输入框挡住。 组件 scroll-view组件:一般使用scroll-view组件的都采取使用其scroll-into-view或者scroll-to属性。 scroll-…...

学习风格的类型

学习风格是指个体在学习过程中偏好的方式和方法。不同的学习风格反映了人们在接收、处理和记忆信息方面的不同偏好。了解自己的学习风格可以帮助提高学习效率和效果。以下是几种常见的学习风格类型: 1. 视觉型(Visual Learner) 特点&#x…...

GCP容器镜像仓库使用

GCP容器镜像仓库产品为:Artifact Registry。 1)用户账号认证 GCP需要前置在控制台登陆对应环境账号。然后执行以下命令操作: $ gcloud auth login 2)登陆镜像仓库 $ gcloud auth configure-docker us-west1-docker.pkg.dev …...

【C++ Primer Plus习题】16.10

大家好,这里是国中之林! ❥前些天发现了一个巨牛的人工智能学习网站,通俗易懂,风趣幽默,忍不住分享一下给大家。点击跳转到网站。有兴趣的可以点点进去看看← 问题: 解答: #include <iostream> #include <string> #include <…...

Django框架全面指南

Django是一个高级的Python Web框架,它鼓励快速开发和清晰、实用的设计。本指南将全面介绍Django的核心概念和使用方法。 1. Django简介 Django遵循"batteries included"哲学,提供了Web开发所需的几乎所有功能。它的主要特点包括: ORM(对象关系映射)URL路由模板…...

git 更新LingDongGui问题解决

今天重新更新灵动gui的代码,以便使用最新的arm-2d,本来以为是比较简单的一件事情(因为以前已经更新过一次),却搞了大半天,折腾不易啊,简单记录下来,有同样遇到问题的同学参考&#x…...

Thymeleaf模版引擎

Thymeleaf是面向Web和独立环境的现代服务器端Java模版引擎,能够处理HTML、XML、JavaScript、CSS甚至纯文本。Thymeleaf旨在提供一个优雅的、高度可维护的创建模版的方式。为了实现这一目标,Thymeleaf建立在自然模版的概念上,将其逻辑注入到模…...

暗黑破坏神2存档编辑器:3分钟学会可视化存档修改

暗黑破坏神2存档编辑器:3分钟学会可视化存档修改 【免费下载链接】d2s-editor 项目地址: https://gitcode.com/gh_mirrors/d2/d2s-editor 还在为复杂的十六进制编辑而烦恼吗?d2s-editor 是一款专为《暗黑破坏神2》玩家设计的 Web 存档编辑器&…...

【无线通信】多载波无线通信系统设计Matlab仿真

✅作者简介:热爱科研的Matlab仿真开发者,擅长毕业设计辅导、数学建模、数据处理、建模仿真、程序设计、完整代码获取、论文复现及科研仿真。 👇 关注我领取海量matlab电子书和数学建模资料 🍊个人信条:格物致知,完整…...

旧Mac焕新:使用OpenCore Legacy Patcher让2008-2017年设备支持最新macOS系统

旧Mac焕新:使用OpenCore Legacy Patcher让2008-2017年设备支持最新macOS系统 【免费下载链接】OpenCore-Legacy-Patcher Experience macOS just like before 项目地址: https://gitcode.com/GitHub_Trending/op/OpenCore-Legacy-Patcher 老旧设备升级正成为越…...

用 DeepWiki 线索看 OpenClaw:它到底用到了哪些 AI 技术?

用 DeepWiki 线索看 OpenClaw:它到底用到了哪些 AI 技术? OpenClaw 近来在个人 AI 助手、Agent 框架和本地优先智能体领域里讨论度很高。很多人第一次看到它,会把它简单理解为“一个能接聊天渠道的大模型壳子”。但如果顺着 GitHub 文档以及项…...

)

WinForms界面美化:用SunnyUI的UILight控件做个状态指示灯(附完整代码)

WinForms界面美化实战:用SunnyUI的UILight控件打造专业状态指示灯 在桌面应用开发中,状态指示是用户界面不可或缺的元素。传统的WinForms控件往往显得单调乏味,而SunnyUI的UILight控件为我们提供了一种简单高效的解决方案。这个圆形指示灯控…...

GLM-4.1V-9B-Base快速部署:Docker镜像体积优化与启动时间实测对比

GLM-4.1V-9B-Base快速部署:Docker镜像体积优化与启动时间实测对比 1. 模型概述 GLM-4.1V-9B-Base是智谱开源的一款视觉多模态理解模型,专注于图像内容识别与分析任务。该模型具备9B参数规模,在中文视觉理解领域表现出色,能够完成…...

网站的页面加载速度和SEO有什么关系

网站的页面加载速度和SEO有什么关系 在当今互联网时代,网站的页面加载速度和SEO(搜索引擎优化)之间的关系是一个不可忽视的重要问题。在用户体验和搜索引擎排名方面,页面加载速度起着至关重要的作用。本文将从问题分析、原因说明…...

人脸分析系统快速上手教程:一键部署智能人脸检测工具

人脸分析系统快速上手教程:一键部署智能人脸检测工具 1. 系统介绍与核心功能 1.1 什么是人脸分析系统 人脸分析系统(Face Analysis WebUI)是一个基于InsightFace框架的智能人脸检测与分析工具。它能够自动识别图片中的人脸,并提…...

Ostrakon-VL终端教程:终端日志记录与扫描任务审计追踪

Ostrakon-VL终端教程:终端日志记录与扫描任务审计追踪 1. 像素特工终端简介 Ostrakon-VL终端是一款专为零售与餐饮行业设计的智能扫描工具,它将复杂的图像识别任务转化为直观有趣的"数据扫描任务"。与传统工业级UI不同,这款终端采…...

STM32duino GNSS库深度解析:Teseo LIV3F驱动与NMEA协议实现

1. 项目概述STM32duino X-NUCLEO-GNSS1A1 是一款面向 STM32 平台的 Arduino 兼容库,专为意法半导体(STMicroelectronics)推出的 X-NUCLEO-GNSS1A1 GNSS 扩展板设计。该扩展板基于意法半导体自研的 Teseo LIV3F 单芯片 GNSS 接收器,…...