详解Xilinx JESD204B PHY层端口信号含义及动态切换线速率(JESD204B五)

点击进入高速收发器系列文章导航界面

Xilinx官方提供了两个用于开发JESD204B的IP,其中一个完成PHY层设计,另一个完成传输层的逻辑,两个IP必须一起使用才能正常工作。

7系列FPGA只能使用最多12通道的JESD204B协议,线速率为1.0至12.5 Gb/s;而UltraScale和UltraScale+系列FPGA还可以使用最多8通道的JESD204C协议,线速率为1.0至32 Gb/s。

PHY层的IP是在GTX/H的基础上封装得到的,因此GTX/H的很多原理在该IP中依旧可以使用,包含共享逻辑的内核框图如下所示。

下图是该IP的一个使用场景,包含三路JESD204B的收发通道,此处使用了三个PHY IP,其实可以只使用一个三通道的PHY,通过AXI接口调节各个通道的线速率。

1、端口信号

手册对该IP的讲解比较简单,没有其内部详细的框图,因此从端口信号出发,分析其功能。图1是包含三个收发器通道的端口信号框图,端口信号的含义如下表所示:

| 信号 | I/O | 含义 |

|---|---|---|

| txoutclk | O | 收发器的输出时钟,该时钟来自TX主通道,一般不会使用。 |

| rxoutclk | O | 收发器的输出时钟,该时钟来自RX主通道,一般不会使用。 |

| tx_core_clk | I | 用于驱动收发器txusrclk2的内核时钟,频率为发送通道线速率/40。 |

| rx_core_clk | I | 用于驱动收发器rxusrclk2的内核时钟,频率为接收通道线速率/40。 |

| drp_clk | I | 动态重新配置端口(DRP)时钟。 |

| cpll_refclk | I | 收发器通道PLL的参考时钟。 |

| qpll_refclk | I | 7系列四通道QPLL的参考时钟。 |

| tx_reset_gt | I | TX通道复位信号。 |

| rx_reset_gt | I | RX通道复位信号。 |

| tx_reset_done | O | TX通道复位完成指示信号。 |

| rx_reset_done | O | RX通道复位完成指示信号。 |

| tx_sys_reset | I | TX通道收发器及PLL复位信号。 |

| rx_sys_reset | I | RX通道收发器及PLL复位信号。 |

| gtN_txdata[31:0] | I | 发送通道的用户数据接口,N取值范围[0,lane-1]。 |

| gtN_txcharisk[3:0] | I | 发送通道的K码指示信号,N取值范围[0,lane-1]。 |

| gt_prbssel[2:0] | I | 设置发送通道的PRBS模式。 |

| gtN_rxdata[31:0] | O | 接收通道的用户数据接口,N取值范围[0,lane-1]。 |

| gtN_rxcharisk[3:0] | O | 接收通道的K码指示信号,N取值范围[0,lane-1]。 |

| rxencommalign | I | 逗号对齐指示信号,高电平有效。 |

| txp_out[N:0] | O | 正差分串行数据输出, N取值范围[0,lane-1]。 |

| txn_out[N:0] | O | 负差分串行数据输出, N取值范围[0,lane-1]。 |

| rxp_in[N:0] | I | 正差分串行数据输入, N取值范围[0,lane-1]。 |

| rxn_in[N:0] | I | 负差分串行数据输入, N取值范围[0,lane-1]。 |

我在网上发现很多人对tx_core_clk的频率为什么是线速率除以40不理解,一些博主给出的答案是手册上这么写的,手册确实是这么写的,没有什么毛病。

但是前面我们已经详细分析了GTX的时钟架构,要知道这个原因还不是易如反掌吗?

首先JESD204B的PHY是在GTX/H的基础上封装得到的,并且tx_core_clk就是GTX/H的txusrclk2,那只需要知道txusrclk2的频率计算方式即可。

JESD204B采用8B10B编码,则如下图可知,输入数据为32位,编码后的数据位宽为40,则txusrclk2的频率为线速率除以40。不管PCS内部并行数据位宽是20位还是40位,都不会影响txusrclk2的频率,这个参数只会影响txusrclk的频率。

7系列FPGA该IP的复位框图如下所示,sys_reset和reset_gt两个复位的范围不一样,reset_gt只对GTX/H进行复位,而sys_reset会同时复位QPLL、CPLL以及内部的逻辑部分,范围更大。

其余端口信号都比较简单,是GTX的8B10B编码方式的简化端口信号,不再赘述其含义。该IP还可以通过一组axi_lite端口去配置其内部的寄存器,这部分信号上表并没有列出。还可以把调试接口引出,调试接口相关信号也与GTX的信号基本一致,所以不再赘述。

2、寄存器

该IP内部提供了很多寄存器,用户可以通过axi_lite总线进行配置,如下图所示,很多只读寄存器,通过这些寄存器可以获取IP的一些配置参数。

内部还有很多配置GTX/H的寄存器,比如回环模式、预加重、去加重、均衡器等等,如下图所示。

上述这些寄存器要么在GTX/H中经常出现,要么就是一些只读的状态寄存器,用户一般会使用到的其实是更改线速率的相关寄存器,其实就是更改QPLL/CPLL的分频系数。

2.1、更改QPLL参数配置线速率

QPLL内部框图如下所示,首先外部时钟信号从5处输入,经过M倍分频后到达4处,4和3一起输入鉴相器,然后经过环路滤波器,当3和4的相位频率相同时,QPLL输出锁定。

GTX的压控振荡器VCO可以输出两种频率范围,Lower Band的范围是5.93~8GHz,Upper Band的范围是9.8~12.5GHz。而GTH QPLL的VCO频率范围是8~13.1GHz。

上图2处是输出时钟信号,1处是VCO输出信号,3处是VCO输出信号经过N分频后的反馈信号。

因为QPLL锁定的条件是鉴相器输入信号频率相位保持一致,因此会有如下公式fPLLClkin / M = fPLLClkout * 2 / N,最终计算得到fPLLClkout = (fPLLClkin * N) / (2 * M)。

如下图所示,QPLL或者CPLL的输出时钟经过数据选择器作为CDR的参考时钟信号,CDR调整该时钟和接收数据的相位后,经过D分频后作为串并转换(SIPO)的串行时钟信号。

在前文分析GTX内部时钟架构的时候推测出SIPO和ISPO模块是双沿传输数据的,因此可以计算得到线速率为f(LineRate)=f(pllClkOut)*2/D。

因此可以通过设置M、N、D和VCO的输出频段等几个参数达到更改线速率的效果,比如参数M与QPLL_REFCLK_DIV寄存器的值对应。

上图中M和N参数对应的寄存器地址和设置如下所示,QPLL需要注意VCO的频段设置,超出范围则无法得到正确的输出时钟频率。

由于参数D是位于PMA内部,与QPLL和CPLL没有关系,因此不管使用QPLL还是CPLL,分频系数D的寄存器均如下所示,因为两个通道均有该结构,因此都需要设置该参数。

2.2、更改CPLL参数配置线速率

CPLL比QPLL会简单一点,GTX的VCO输出频率范围1.63.3GHz,GTH的VCO输出频率范围1.65.16GHz。

CPLL锁定条件为鉴相器的两个输入频率和相位保持一致,最终得到如下公式:

QPLL和CPLL的输出时钟与线速率关系是一样的,因此不再赘述;最终也只需要配置N1、N2、M、D这几个参数,就可以改变线速率。CPLL这几个参数对应的寄存器名和取值范围如下图所示。

参数D的配置与图11一致,一般情况下不需要去修改这些参数,在配置IP时vivado会自动计算出这些寄存器的数值。但是如果在系统运行时,想要去更改某路收发器的线速率,就必须了解这些寄存器的配置原理。

配置这些参数时,首先要考虑VCO的频率范围,如果存在多组参数能够满足要求的情况,则选中数值较小的分频参数那一组。

上述通过axi_lite配置高速收发器内部的参数,因为该IP可以包含多个高速收发器通道。因此在配置具体的高速收发器之前,需要通过地址为0x24的寄存器写入后续需要配置的高速收发器通道。否则将会对默认的高速收发器通道进行配置,导致其余收发器的参数没有配置。

该IP其实比较简单,只是对GTX/H进行了简单封装,接收端连对齐都没有实现,必须配合JESD204B的发送或接收模块一起使用才行。后面先单独仿真一下该模块,在与上层IP一起使用。

该手册可以在公众号后台回复“xilinx手册”(不包括引号),在其的JESD204B文件夹中获取。

相关文章:

详解Xilinx JESD204B PHY层端口信号含义及动态切换线速率(JESD204B五)

点击进入高速收发器系列文章导航界面 Xilinx官方提供了两个用于开发JESD204B的IP,其中一个完成PHY层设计,另一个完成传输层的逻辑,两个IP必须一起使用才能正常工作。 7系列FPGA只能使用最多12通道的JESD204B协议,线速率为1.0至12.…...

Java面试——场景题

1.如何分批处理数据? 1.使用LIMIT和OFFSET子句: 这是最常用的分批查询方法。例如,你可以使用以下SQL语句来分批查询数据: SELECT * FROM your_table LIMIT 1000 OFFSET 0; 分批查询到的数据在后端进行处理,达到分批…...

xss-labs靶场第一关测试报告

目录 一、测试环境 1、系统环境 2、使用工具/软件 二、测试目的 三、操作过程 1、注入点寻找 2、使用hackbar进行payload测试 3、绕过结果 四、源代码分析 五、结论 一、测试环境 1、系统环境 渗透机:本机(127.0.0.1) 靶 机:本机(127.0.0.…...

微软PowerBI认证!数据分析师入门级证书备考攻略来啦

#微软PowerBI认证!数据分析师入门级证书! 😃Power BI是一种强大的数据可视化和分析工具,学习Power BI,能提高数据的分析能力,将数据转化为有意义的见解,并支持数据驱动的决策制定。 ㅤ ✨微软P…...

上海AI Lab视频生成大模型书生.筑梦环境搭建推理测试

引子 最近视频生成大模型层出不穷,上海AI Lab推出新一代视频生成大模型 “书生・筑梦 2.0”(Vchitect 2.0)。根据官方介绍,书生・筑梦 2.0 是集文生视频、图生视频、插帧超分、训练系统一体化的视频生成大模型。OK,那就让我们开始吧。 一、模…...

3D看车如何实现?有哪些功能特点和优势?

3D看车是一种创新的汽车展示方式,它利用三维建模和虚拟现实技术,将汽车以更真实、更立体的形式呈现在消费者面前。 一、3D看车的实现方式 1、三维建模: 通过三维建模技术,按照1:1的比例还原汽车外观,包括车身线条、细…...

Pytorch中不会自动传播梯度的操作有哪些?

在 PyTorch 中,某些生成张量的操作本身不会创建与计算图相关联的梯度信息。这些操作通常用于初始化张量,并且默认情况下不需要进行梯度计算。以下是一些常见的不会自动传播梯度的张量生成操作: 数值初始化操作: torch.linspace():…...

【设计模式】软件设计原则——开闭原则里氏替换单一职责

开闭原则内容引出 开闭原则 定义:一个软件实体,类,函数,模块;对扩展开放,对修改关闭。用抽象构建框架,用实现扩展细节。可以提高软件的可复用性和可维护性。 开发新功能时,尽量不修…...

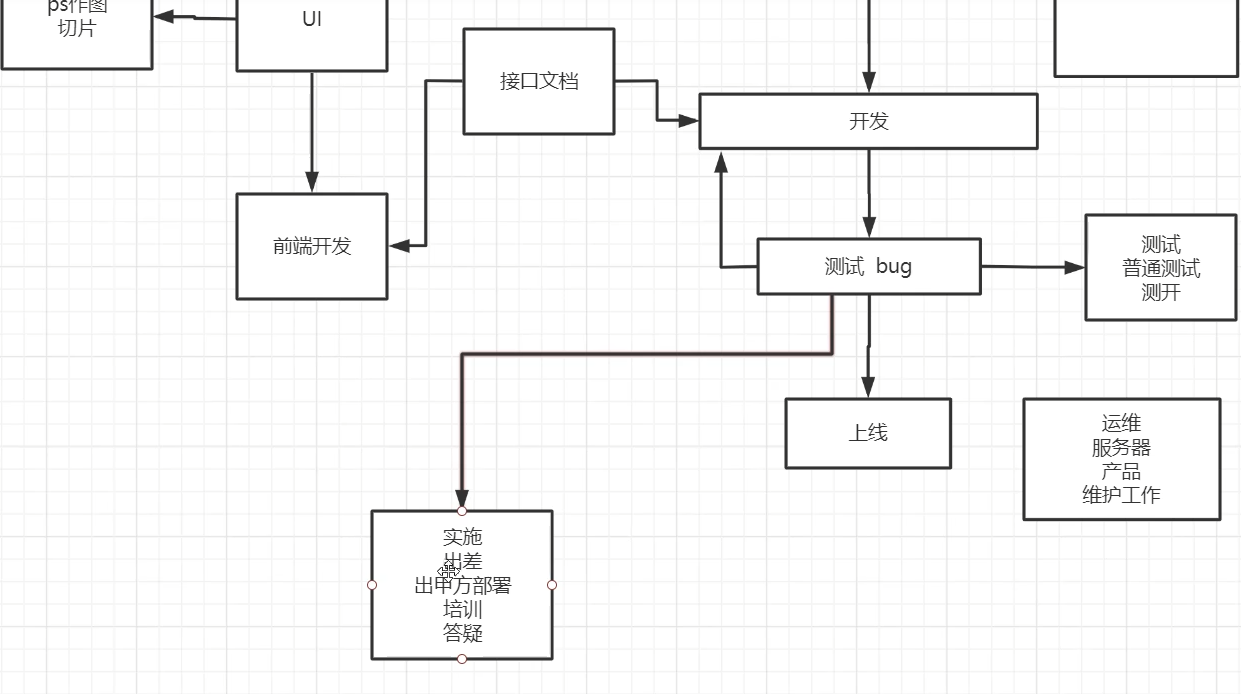

项目完整开发的流程

流程 1.设计产品 2.写需求文档 2.1需求分析,后端设计数据库,建表,客户沟通,说完签字,留证据,防止后面扯皮,和防止后续变需求重新写业务 3.画原型图,也就是草图,初始的…...

性能测试学习6:jmeter安装与基本配置/元件/线程组介绍

一.JDK安装 官网:https://www.oracle.com/ 二.Jmeter安装 官网:http://jmeter.apache.org/download_jmeter.cgi 下载zip包,zip后缀那个才是Windows系统的jmeter 三.Jmeter工作目录介绍 四.Jmeter功能 1)修改默认配置-汉化 2&am…...

大数据ETL数据提取转换和加载处理

什么是 ETL? 提取转换加载(英语:Extract, transform, load,简称ETL),用来描述将资料从来源端经过抽取、转置、加载至目的端的过程。ETL一词较常用在数据仓库,但其对象并不限于数据仓库。 ETL&…...

物理与环境安全技术

目录 物理安全 环境安全 物理安全 物理安全是指通过实施一系列的防护措施,以保护人员、设备、设施和信息资源免受物理上的威胁、损坏或非法入侵。 访问控制:限制对数据中心、机房等关键设施的物理访问。通常采用的措施有门禁系统(使用门禁…...

手把手教你如何配置好VS Code的WEB基础开发环境(保姆级)

1. VS Code介绍 微软旗下的多场景开发环境软件,支持JAVA、C、C#、C、WEB、VUE、CSS、HTML、Python等等等 如果你刚刚开始编程或者准备学习WEB,那么我强烈建议你使用这款软件 缺点:(针对初学者) 需要安装各种各样的插…...

高性能、编译器编写语言、编程语言的高低贵贱

高性能 高性能是一个通用名词,可在服务器、客户端甚至浏览器实现高性能。对于大型网站、服务器后端、游戏后端,高性能是一个不可绕过的槛。 高性能技术 池机制 静态分配:就像编译型语言对代码的预处理,不像解释型语言动态解析。可…...

Python安装库时使用国内源pip install -i

普通 安装方式会从国外站点下载, 首先是慢,再有可能会下载失败 所以一般指定国内源 示例 正常情况下,安装pandas这个模块 pip install pandas指定源命令如下: pip install -i https://pypi.tuna.tsinghua.edu.cn/simple/ pan…...

Linux 再入门整理:详解 /etc/fstab 文件

目录 1. 什么是 /etc/fstab2. /etc/fstab 文件的格式2.1 设备文件 (Device)2.2 挂载点 (Mount Point)2.3 文件系统类型 (File System Type)2.4 挂载选项 (Mount Options)2.5 Backup Operation(dump 参数)2.6 Pass Order (fsck 参数)2.6.1 参数设置2.6.2 …...

2.8 双绞线、同轴电缆、光纤与无线传输介质

传输介质及分类 传输介质也称为传输媒体,它是发送设备和接收设备之间的物理通路。 传输介质可分为导向传输介质和非导向传输介质。在导向传输介质中,电磁波被导向沿着固体媒介(铜线或光纤)传播,而非导向传输介质可以…...

OBOO鸥柏:布局于为无人机展厅行产业提供LCD液晶显示终端

新华网快讯,于10月9日消息,有投资者在互动平台向OBOO鸥柏公司提问:您好!目前有哪些工业/商用显示产品应用于无人机展厅展馆场景?能否着重介绍下贵司屏幕主要应用哪些品牌无人机数字化展厅展馆做保障? 鸥柏…...

win10状态栏中 “音量” 符号丢失,而在“打开或关闭系统图标”中音量开关无法调节的解决方法

最近在使用电脑需要调节音量时,突然发现电脑右下角的音量图标不见了,在网上搜索了,测试了许多种方法,都没有解决这个问题。 后面想想,使用其他途径,或许可以解决了我的这个问题,终于功夫不负有心…...

Mysql 学习——项目实战

MySQL 学习——项目实战 项目出处 博主:Asmywishi Linux-Ubuntu启动Mysql sudo mysqlData preparation Create Database and Table Create database : create database mysql_example1;Start database : use mysql_example1;Create Student table : # 学生表…...

智在记录 AI 语音转文字效果全景展示

在日常的工作和生活中,我们常常面临这样的困境:一场长达两小时的头脑风暴会议结束后,整理纪要却要花掉半天时间;课堂上老师语速飞快,笔记记得手忙脚乱,回头复习时却发现关键逻辑断档;或是医生叮…...

HNU 计算机系统 bomblab:从GDB断点到链表重构的逆向实战

1. 逆向工程实战:从零开始拆解二进制炸弹 第一次接触bomblab时,我盯着终端里那个名为"bomb"的可执行文件发呆了十分钟。这个看似普通的Linux程序就像个黑盒子,里面藏着六个需要密码才能解除的"炸弹"。作为计算机系统课程…...

的预配置策略与实战价值)

当台风来袭时,电网如何“未雨绸缪”?聊聊应急移动电源(MPS)的预配置策略与实战价值

当台风来袭时,电网如何“未雨绸缪”?应急移动电源(MPS)的预配置策略与实战价值 台风过境时,医院ICU的呼吸机突然断电、通信基站的备用电池耗尽、交通信号灯集体瘫痪——这些场景并非虚构,而是真实发生在201…...

UCCL:GPU网络传输的性能优化与创新

1. UCCL:GPU网络传输的革命性创新在分布式机器学习训练场景中,GPU集群间的通信效率往往成为制约系统整体性能的关键瓶颈。传统基于TCP/IP的传输协议由于内核协议栈处理和多次数据拷贝等问题,难以满足现代AI训练任务对低延迟和高带宽的严苛要求…...

小米路由器4A千兆版刷机翻车实录:从Breed救砖到完美刷入Padavan固件全记录

小米路由器4A千兆版救砖实战:从硬件识别到Padavan固件完美适配 深夜的台灯下,我盯着桌面上那台已经变砖的小米路由器4A千兆版,USB转TTL模块的指示灯微弱地闪烁着。这已经是本周第三次尝试救砖了——前两次要么是夹子接触不良导致校验失败&…...

同步、异步与互斥:从通用OS到RTOS的全面解析

一、基础概念:进程与线程1.1 什么是进程?进程是操作系统进行资源分配和调度的基本单位,是一个正在运行的程序实例。1.2 什么是线程?线程是操作系统进行CPU调度的基本单位,是进程内部的一条执行路径(轻量级进…...

Qt新手也能搞定的GPU加速图片渲染:用QOpenGLWidget和QImage实现高性能显示

Qt新手也能搞定的GPU加速图片渲染:用QOpenGLWidget和QImage实现高性能显示 在Qt应用开发中,处理高分辨率图片或序列帧(如医学影像、地图切片)时,传统的QLabel显示方式常会遇到性能瓶颈。当图片尺寸超过1080P或需要快速…...

CVAT管理员必看:用户权限、任务分割与Datumaro数据导入导出全流程详解

CVAT管理员实战指南:权限配置、任务优化与数据流转全解析 1. 权限管理的艺术:从基础配置到高级控制 在CVAT平台中,权限管理是确保数据安全与协作效率的核心机制。不同于普通标注员视角,管理员需要掌握三个关键权限层级:…...

RK3588 LGA核心板:高性能嵌入式开发的模块化解决方案

1. 项目概述:当旗舰SoC遇见极致封装最近在嵌入式圈子里,一个“小而强”的组合引起了我的注意:瑞芯微的旗舰级SoC RK3588,被塞进了一个极其紧凑的LGA封装里,做成了名为SOM-3588-LGA的核心板,并且已经现货发售…...

可视化STM32引脚波形)

告别盲调!用Keil自带的逻辑分析仪(Debug Simulator)可视化STM32引脚波形

告别盲调!用Keil自带的逻辑分析仪(Debug Simulator)可视化STM32引脚波形 在嵌入式开发中,调试环节往往占据整个开发周期的40%以上时间。对于STM32开发者而言,传统的调试方式主要依赖LED闪烁观察或串口打印输出,这种方式不仅效率低…...