Formality:官方Tutorial(一)

相关阅读

Formality![]() https://blog.csdn.net/weixin_45791458/category_12841971.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12841971.html?spm=1001.2014.3001.5482

本文是对Synopsys Formality User Guide Tutorial中第一个实验的翻译(有删改),Lab文件可以从以下链接获取。

Formality官方Tutorial![]() https://download.csdn.net/download/weixin_45791458/90220600?spm=1001.2014.3001.5501

https://download.csdn.net/download/weixin_45791458/90220600?spm=1001.2014.3001.5501

本教程首先解释如何为运行Formality做好准备,然后通过三个使用该工具的实验进行讲解。

在开始之前

在开始本教程之前,请确保系统上已正确安装Formality。Shell配置文件(如果使用Bash,指的是.bashr文件;如果使用Zsh,指的是~/.zshrc;如果使用Csh,指的是~/.cshrc)应正确设置路径,已包含Formality安装的bin目录。例如,如果安装目录是/opt/Synopsys/Formality2018/fm/O-2018.06-SP1,请在配置文件中添加如下的设置路径语句(假设使用Bash):

export PATH=$PATH:/opt/Synopsys/Formality2018/fm/O-2018.06-SP1/bin不需要为每个平台(64-bit/32-bit)单独设置可执行路径,Formality启动脚本会自动确定使用的平台并调用正确的二进制文件。但是,为了使工具能够执行此操作,必须确保所有需要的平台都已安装在同一个Formality树中。请将Formality安装在其独立的目录树中,与其他Synopsys工具(如Design Compiler)分开。

创建教程目录

安装Formality后,设计示例所需的文件位于fm_install_path/doc/fm/tutorial目录中。要在用户家目录创建一个包含所有子目录的教程目录,请执行以下操作:

1、切换到主目录

% cd $HOME2、使用以下命令复制教程数据,其中fm_install_path是Formality的安装目录

% cp -r fm_install_path/doc/fm/tutorial $HOME3、切换到新的教程目录

% cd tutorial教程目录的内容

教程目录包含以下子目录:

- GATE:Verilog门级网表。

- GATE_WITH_JTAG:带有扫描和联合测试行动组(JTAG)插入的Verilog门级网表。

- GATE_WITH_SCAN:带有扫描插入的Verilog门级网表。

- LIB:门级网表所需的逻辑库。

- RTL:RTL源代码。

启动Formality Shell

% fm_shell

...

fm_shell (setup)>fm_shell命令启动了Formality的Shell环境和命令行界面,在命令行界面可以通过以下命令启动GUI:

fm_shell (setup)> start_gui 提示符中的(setup)表示当前使用命令时所在的模式。可用的模式有:guide、setup、preverify、match和verify,有关于模式的更详细讨论,可见下文,当启动Formality时,默认进入setup模式。Formality:等价性检查的流程与模式(Guide、Setup、Preverify、Match与Verify)文章浏览阅读1.3k次,点赞41次,收藏20次。Formality:等价性检查的流程与模式(Guide、Setup、Preverify、Match与Verify)_formality检查https://chenzhang.blog.csdn.net/article/details/144174638

实验一、Verifying fifo.vg Against fifo.v

在本教程的这一部分,将验证一个综合后的名为fifo.vg的纯Verilog门级网表与名为fifo.v的RTL参考设计之间的等价性。

在任何时候都可以通过执行以下命令退出并保存当前的Formality会话:

fm_shell> save_session session_file_name要重新调用该会话,请执行:

fm_shell> restore_session session_file_name加载SVF文件

在指定参考设计和实现设计之前,可以选择性地将自动设置文件(.svf)加载到Formality中。SVF文件帮助Formality处理由设计流程中的其他工具引起的设计变更。Formality使用该文件来协助比较点匹配和验证过程,这些信息有助于对正在验证的设计中的比较点进行对齐。对于每个加载的SVF文件,Formality会在恰当时机处理其内容,以便在基于名称的比较点匹配期间使用。

有关SVF文件的详细介绍,可见下文。

Formality:set_svf命令文章浏览阅读1.3k次,点赞40次,收藏31次。Formalitysvf文件的全称是Setup Verification for Formality,即Design Compiler提供给Formality的设置验证文件,它的作用是为Formality的指导模式(Guidance)和设置模式(Setup)提供信息,以帮助其更好地理解和处理设计流程中因使用Design Compiler而引起的设计变更的一种机制。svf文件的详细介绍和生成命令在下面的博客中已经讨论,本文主要讨论Formality中的set_svf命令。_formality把svf转成txt命令https://chenzhang.blog.csdn.net/article/details/144404635 有关比较点匹配的详细介绍,可见下文。

Formality:匹配(match)是如何进行的?文章浏览阅读906次,点赞33次,收藏18次。匹配指的是Formality工具尝试将参考设计中的每个匹配点与实现设计中的相应匹配点进行配对,这里的匹配点包括对比点(Compare Points)以及普通的匹配点(Points)。 在介绍匹配点前首先需要了解逻辑锥(Logic Cones)的概念,逻辑锥是指从特定的设计对象出发,并向后延伸至某些设计对象的组合逻辑结构,之所以被称为锥,是因为其就像椎体一样(一般)拥有一个顶点和多个底点,如图1所示。https://chenzhang.blog.csdn.net/article/details/144404964 要加载SVF文件,请执行以下操作:

fm_shell> set_svf svf_file_name.svf 注意:如果希望将Design Compiler中的附加约束和非约束信息传递给Formality,请在读取SVF文件之前设置自动化设置模式,有关自动化设置模式可见下文。Formality:设置Automated Setup Mode模式文章浏览阅读1.1k次,点赞28次,收藏36次。Formality要使用自动设置模式,在加载/执行svf文件之前,需要将synopsys_auto_setup变量(布尔值)设置为true或者在GUI界面中选择Use Auto Setup,如图1所示。当自动设置模式设置后,一组Formality变量会被设置,一些设置命令会执行,以与Synopsys综合工具例如Design Compiler兼容,从而通过使用svf指导文件提高整体工具的设置性能。_automa ic modehttps://chenzhang.blog.csdn.net/article/details/144113957 注意:本教程不使用SVF文件,因此本节信息仅供参考。

指定参考设计

指定参考设计包括读取设计文件、可选地读取工艺库,并设置顶层设计。参考设计是与转换后的实现设计进行比较的设计。在本实验中,参考设计是名为fifo.v的RTL源文件。

需要显式指定DesignWare根目录,因为fifo.v包含一个DesignWare中的RAM实例,可按如下所示设置hdlin_dwroot变量:

| fm_shell | GUI |

| 使用set_app_var hdlin_dwroot path_to_DesignCompiler_install命令 | 1、选择Edit > Formality Tcl Variables,将会显示Formality Tcl Variables对话框。 2、在Reading Designs部分,选择hdlin_dwroot变量。 3、输入或选择路径path_to_DesignCompiler_install并回车确定。 |

现在加载所有参考Verilog文件:

| fm_shell | GUI |

| 使用read_verilog -r {./RTL/fifo.v ./RTL/gray2bin.v ./RTL/gray_counter.v ./RTL/pop_ctrl.v ./RTL/push_ctrl.v ./RTL/rs_flop.v}命令 | 1、点击Ref.。 2、点击Verilog,导航到GATE子目录选择文件并点击Open。 3、点击加载文件按钮 |

最后定义参考设计的顶层设计,设置顶层设计将启动所有文件的链接和展开过程,并报告是否缺少任何文件,Formality会自动搜索DesignWare库以寻找RAM的实现:

| fm_shell | GUI |

| 使用set_top fifo命令 | 1、点击Set Top Design。 2、选择WORK库和fifo设计,并点击Set Top。 |

指定实现设计

指定实现设计的过程与指定参考设计的过程类似,首先加载所有实现Verilog文件:

| fm_shell | GUI |

| 使用read_verilog -i ./GATE/fifo.vg命令 | 1、点击Impl.。 2、点击Verilog,导航到GATE子目录选择文件并点击Open。 3、点击加载文件按钮 |

但于参考设计不同的是,此时需要加载工艺库:

| fm_shell | GUI |

| 使用read_verilog -i LIB/lsi_10k.db命令 | 1、点击Read DB Libraries。 2、点击DB,导航到LIB子目录选择lsi_10k.db文件并点击Open。 3、 点击加载文件按钮 |

最后定义实现设计的顶层设计:

| fm_shell | GUI |

| 使用set_top fifo命令 | 1、点击Set Top Design。 2、选择WORK库和fifo设计,并点击Set Top。 |

执行设置

通常需要指定额外的设置信息,以考虑设计网表中未包含的信息或为了实现最佳性能。这一步骤涉及向Formality提供信息。例如,如果设计经过了如扫描或JTAG插入等转换,可能需要设置常量。在这种情况下,只有fifo.vg被综合,因此可以继续进行到下一个步骤:Match。

进行匹配

匹配是Formality将参考设计和实现设计分割成逻辑单元的过程,这些逻辑单元称为逻辑锥(logic cones)。每个逻辑锥都有一个比较点作为顶点,且实现设计中的每个比较点必须与参考设计中的每个比较点匹配,否则验证将失败。匹配阶段需要确保没有不匹配的逻辑锥,并验证实现设计的功能性。

要进行匹配,请执行以下操作:

| fm_shell | GUI |

| 使用match命令 | 1、点击Match。 2、点击Run Matching。 |

匹配结果显示619个点全部匹配成功。

验证设计

要验证设计,请执行以下操作:

| fm_shell | GUI |

| 使用verify命令 | 1、点击Verify。 2、点击Verify。 |

在此案例中,验证将失败并显示有17个比较点验证失败,因为fifo.vg中故意包含了一个设计错误,以展示Formality的调试功能。

调试

对于大多数用户来说,调试失败的验证是一个挑战,也就是说必须找到设计中功能差异的确切位置,然后进行修复。使用GUI进行调试更加直观,如果你之前使用的是fm_shell,以下命令可以启动GUI:

fm_shell> start_gui在本实验继续调试之前,下一部分将简要介绍GUI的一些基础知识。

GUI的简单介绍

主GUI会话窗口如图1所示,包含了表1所示的区域。

图1 主GUI会话窗口

表1 窗口区域

| 窗口区域 | 描述 |

| 设计栏 (Design bar) | 显示参考设计和实现设计的WORK库路径。 |

| 菜单栏 (Menu bar) | GUI命令,其中一些在工具栏和右键菜单中也有重复。 |

| 工具栏 (Toolbar) | GUI命令。工具栏根据显示在上下文窗格中的视图发生变化。可以重新排列工具栏上的图标,并将工具栏移动到窗口的任意边缘。右键单击工具栏并选择或取消选择以查看所需的工具栏菜单。 |

| 基于流程的工具栏 (Flow-based toolbar) | 显示执行正式验证所需采用的正确流程的选项。选项会高亮显示,指示当前所在的流程步骤。每个选项都会在上下文窗格中显示一个新视图。默认情况下,GUI从第一个步骤(指导)开始打开,并显示指导工作区。使用fm_shell执行步骤并调用GUI时,GUI将高亮显示当前所在的流程步骤。当继续一个之前保存的Formality会话时,也会发生这种情况。 |

| 上下文窗格 (Context pane) | 主要的工作区域。在这里执行执行验证所需的操作,也可以在此查看报告。可以调整大小并分离上下文或报告窗格,以查看更大的报告。 |

| 命令控制台 (Command console) | 显示根据Formality提示符下使用的命令记录和其他信息。可以调整大小并分离命令控制台,以查看较大的命令记录。 |

| Formality提示符 (Formality prompt) | 一个文本框,可以在其中输入通过GUI界面无法访问的Formality命令和变量。 |

| 状态栏 (Status bar) | 显示工具的当前状态。 |

使用GUI调试

1、在基于流程的工具栏上,点击Debug,如果它尚未被选中。上下文窗格会显示失败点报告,其中可能会出现多个名称相似的失败点,如图2所示。例如,可能会看到*_reg[0]、*_reg[1]、*_reg[2]和*_reg[3],通常一组失败点是由一个单一的错误引起的。

图2 失败点报告

2、要对失败点进行诊断,请在失败点报告中右键并点击Diagnosis或者在菜单栏Run的下拉栏点击Diagnosis,如图3所示。 在诊断过程中,Formality会分析比较点并找到错误候选项。错误候选项窗口Analyses会出现,显示在实现设计中发现的错误候选项。

图3 执行诊断

注意:在调试过程中,如果出现错误提示,指出诊断失败是因为错误过多(且知道错误不是由设置问题引起的),请选择某个有相似名称的失败点,右键并点击Diagnose Selected Points或在菜单栏Run的下拉栏点击Diagnose Selected Points。这可能有助于将诊断定向到设计的特定部分。

3、在错误候选项窗口中,右键点击U81并选择Show Logic Cones。窗口会显示该错误相关的失败点列表,可以从中选择一个点(例如使用push_logic/pop_count_svd_reg[0]),双击或点击OK以查看逻辑锥,如图4所示。

图4 选择一个失败比较点以查看逻辑锥

Failing ConeSchematics窗口会出现,显示参考设计(上屏)和实现设计(下屏)的逻辑锥示意图。实现设计的示意图会突出显示并放大实现设计的逻辑锥中的错误候选项U81反相器,而参考设计的示意图会高亮显示与实现设计中的错误候选项对应的匹配区域,如图5所示。

图5 参考设计和实现设计的逻辑锥

实现设计中的错误候选项用橙色高亮显示,而参考设计中对应的匹配区域用黄色高亮显示。要单独查看错误区域,可以用一以下任意方式实现:

- 右键并选择Prune/Restore > Isolate Error Candidates

- 选择Edit > Prune/Restore > Isolate Error Candidates

这样会将不相关的子逻辑锥(子逻辑锥并不是真正意义上的逻辑锥,因为没有比较点,它只是逻辑锥的一部分)修建,仅显示错误反相器,如图6所示。

图6 修剪不相关的子逻辑锥

可以在Pattern窗口中查看已修剪后的逻辑锥输入(需要勾选Filter),如图7所示。

图7 修剪后的逻辑锥输入Pattern

4、选择Pattern1并观察触发器的CLK引脚的标注:参考设计显示逻辑0,而实现设计显示逻辑1。 注意到驱动实现设计中触发器的CLK引脚的逻辑中包括一个反相器。在综合过程中,可能会插入一个反相器以修复保持时间问题,你可以:

- 通过点击工具栏上的Zoom In图标,或者点击示意图,进行放大查看。

- 复制/粘贴逻辑锥示意图中的选定对象,点击Edit > Copy,并选择以下之一:Instance Name、Library Name或Design Name,接着通过Ctrl+V或右键并选择Paste,将这些名称粘贴到Formality提示符或任何其他可编辑文本框中。

5、通过编辑网表或重新综合设计,生成一个新的、无时钟树操作错误的网表。为了节约时间,在GATE目录包含了修正后的网表fifo_mod.vg。可以在shell中执行以下命令,查看两个网表差异:

% diff ./GATE/fifo.v ./GATE/fifo.mod.vg

将看到修改后的网表去除了反相器。

6、最后重新按照本实验的步骤验证fifo.mod.vg和fifo.v之间的等价性(略)。

原文链接Formality各版本User Guide![]() https://download.csdn.net/download/weixin_45791458/90184000?spm=1001.2014.3001.5503

https://download.csdn.net/download/weixin_45791458/90184000?spm=1001.2014.3001.5503

相关文章:

Formality:官方Tutorial(一)

相关阅读 Formalityhttps://blog.csdn.net/weixin_45791458/category_12841971.html?spm1001.2014.3001.5482 本文是对Synopsys Formality User Guide Tutorial中第一个实验的翻译(有删改),Lab文件可以从以下链接获取。 Formality官方Tu…...

力扣28找出字符串中第一个匹配项的下标

class Solution:def strStr(self, haystack: str, needle: str) -> int:# 特殊情况处理if not needle:return 0# 获取 haystack 和 needle 的长度a len(needle)b len(haystack)# 遍历 haystack,检查每个子字符串是否与 needle 匹配for i in range(b - a 1):if…...

【JAVA】java中将一个list进行拆解重新组装

一、使用场景 1、当需要对一个list中的元素属性进行重新赋值,比如一个list中存储了订单数据,我们需要改变list中每个订单的id,然后再重新输出订单list if(CollectionUtils.isNotEmpty(orderList)){ orderList.forEach(p->{ …...

在 Windows 上使用 SSH 密钥访问 Linux 服务器

本章目录: 前言1. 准备工作2. 生成 SSH 密钥对步骤 1:打开命令行步骤 2:运行 ssh-keygen 命令步骤 3:选择密钥保存位置步骤 4:设置密钥密码(可选)步骤 5:生成密钥对 3. 查看生成的密钥文件4. 将…...

小白0基础centos8安装docker

总述:博主作为0基础小白将详细记录第一次从centos8的下载到安装docker的过程,包括中间出现的问题和解决方案 1Centos8下载 参见博文CentOS 8 的安装(官方安装、清华大学开源软件镜像站、阿里云镜像、网易镜像下的安装步骤)_cent…...

机器学习之逻辑回归算法、数据标准化处理及数据预测和数据的分类结果报告

逻辑回归算法、数据标准化处理及数据预测和数据的分类结果报告 目录 逻辑回归算法、数据标准化处理及数据预测和数据的分类结果报告1 逻辑回归算法1.1 概念理解1.2 算法导入1.3 算法优缺点 2 LogisticRegression理解2.1查看参数定义2.2 参数理解2.3 方法2.4基本格式 3 数据标准…...

openGauss连接是报org.opengauss.util.PSQLException: 尝试连线已失败

安装好高斯数据库后然后用java连接时报如下错误: 解决方法: 在openGauss数据库的安装路径下/opt/opengauss/data/single_node(这个路径根据自己实际情况变化)有个pg_hba.conf文件,修改里面host内容如下,我这里设置的是所有ip都能…...

详细的一条SQL语句的执行流程

SQL 语句的执行流程会因数据库管理系统的不同而略有差异,但一般来说,主要包括以下几个阶段: 查询解析 词法分析:数据库系统首先将输入的 SQL 语句按字符流进行扫描,依据词法规则把它分割成一个个的单词,如…...

适用于小白的程序报错提问 AI 模板

#工作记录 程序报错提问 AI 模板 1、你现在将扮演python专家,请保持连续对话,请基于你的专业知识修改代码并回答! 2、可以向我询问任何有利于你分析问题的信息。 3、你修改的程序代码,运行后报错,报错信息我放在最后…...

web实操9——session

概念 数据保存在服务器HttpSession对象里。 session也是域对象,有setAttribute和getAttribute方法 快速入门 代码 获取session和塞入数据: 获取session获取数据: 请求存储: 请求获取: 数据正常打印:…...

OFDM学习-(二)长短序列和PPDU整体数据处理流程

OFDM学习 (二)长短序列和PPDU整体数据处理流程 OFDM学习前言一、短序列短序列的作用 二、长序列三、PLCP/SIGNAL/DATA数据处理流程三、fpga实现STS模块LTS模块训练序列模块仿真波形 总结 前言 根据框图可以知道发射机这部分信号在DA转换之前,…...

.NET周刊【12月第4期 2024-12-22】

国内文章 dotnet 简单使用 ICU 库进行分词和分行 https://www.cnblogs.com/lindexi/p/18622917 本文将和大家介绍如何使用 ICU 库进行文本的分词和分行。 dotnet 简单聊聊 Skia 里的 SKFontMetrics 的各项属性作用 https://www.cnblogs.com/lindexi/p/18621674 本文将和大…...

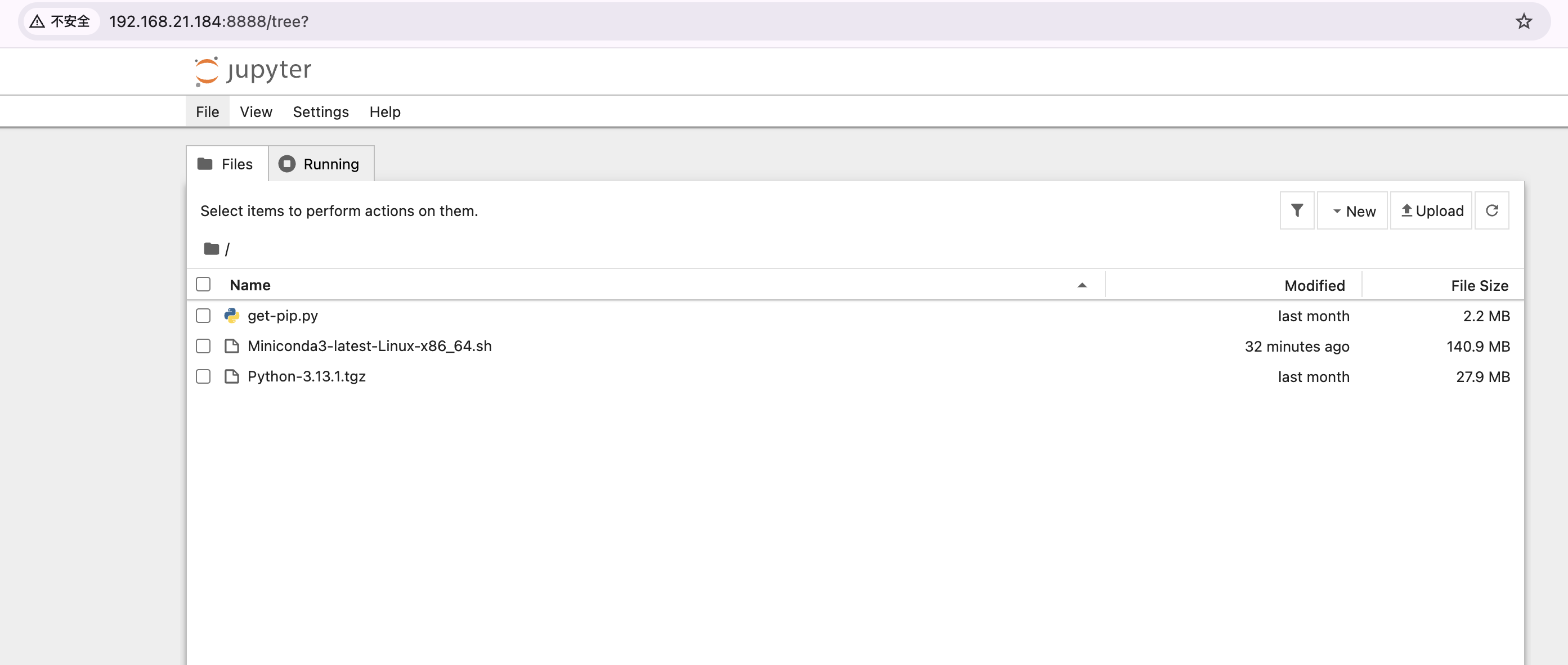

Conda 安装 Jupyter Notebook

文章目录 1. 安装 Conda下载与安装步骤: 2. 创建虚拟环境3. 安装 Jupyter Notebook4. 启动 Jupyter Notebook5. 安装扩展功能(可选)6. 更新与维护7. 总结 Jupyter Notebook 是一款非常流行的交互式开发工具,尤其适合数据科学、机器…...

鸿蒙开发:实现键值数据库存储

前言 鸿蒙当中数据持久化存储,为我们提供了多种的实现方式,比如用户首选项方式,关系型数据库方式,键值型数据库方式,文件存储方式等等,对于数据量比较的小的,我们直接选择轻量级的用户首选项方式…...

WebGL 实践(一)开发环境搭建

WebGL 是一种基于 JavaScript 的 API,用于在浏览器中渲染 2D和3D 图形,很多场景都能用,例如游戏开发、数据可视化、在线教育和虚拟现实等应用领域。 零、基础知识 相关基础知识很重要,如果会html、JavaScript等技术掌握起来会更…...

在线机考|2024华为实习秋招春招编程题(最新)——第3题_PCB印刷电路板布线_300分(八)

题目内容 在PCB印刷电路板设计中,器件之间的连线需要避免线路的阻抗值增大、而且赛件之间还有别的器件和别的干扰源,在布线时我们希望受到的干扰尽量小。现将电路板简化成一个MN的矩阵,每个位置(单元格)的值表示其源干扰度。 如果单元格的值为0,表示此位置没有干扰源;如果单…...

)

Spring源码分析之事件机制——观察者模式(三)

目录 自定义事件 事件监听器 事件发布者(服务层) 使用示例controller层 Spring源码分析之事件机制——观察者模式(一)-CSDN博客 Spring源码分析之事件机制——观察者模式(二)-CSDN博客 这两篇文章是这…...

C#实现画图,及实现图像运动,C#中GDI+图形图像技术(Graphics类、Pen类、Brush类)C#之快速入门GDI+绘图 C#实现快速画图功能

下载源码 <-------- 在C#的世界里,GDI如同一位多才多艺的艺术家,以其强大的绘图能力,让开发者能够轻松地在应用程序中挥洒创意,绘制出丰富多彩的图形世界。GDI不仅支持基本的几何图形绘制,还能处理复杂的图像处理任…...

【51单片机零基础-chapter6:LCD1602调试工具】

实验0-用显示屏LCD验证自己的猜想 如同c的cout,前端的console.log() #include <REGX52.H> #include <INTRINS.H> #include "LCD1602.h" int var0; void main() {LCD_Init();LCD_ShowNum(1,1,var211,5);while(1){;} }实验1-编写LCD1602液晶显示屏驱动函…...

算法题(24):只出现一次的数字(二)

审题: 数组中除了答案元素只出现一次外,其他元素都会出现三次,我们需要找到并返回答案元素 思路: 由于现在会出现三次,所以利用异或运算符的方法就会失效。而所有数据都在32位二进制范围内,所以我们采用依次…...

腾讯开源翻译大模型HY-MT1.5-7B镜像使用教程:新手快速入门

腾讯开源翻译大模型HY-MT1.5-7B镜像使用教程:新手快速入门 你是否曾为寻找一个既强大又好用的翻译工具而烦恼?无论是阅读外文资料、处理多语言客服,还是开发一个需要实时翻译的应用,找到一个靠谱的翻译引擎总是关键一步。今天&am…...

高效考证解决方案:一次通关的行动蓝图)

信息系统项目管理师(高项)高效考证解决方案:一次通关的行动蓝图

一、 认知破局:理解考试本质与核心挑战信息系统项目管理师(俗称“高项”)是国家软考高级资格,它不仅是职称证书,更是项目投标的硬性门槛(集成/软件企业申报资质、投标时项目经理资格必备)。其核…...

二、空间碎片聚类-轨道计算与J2000坐标系实现

1. 整体思路 在空间碎片监测、卫星对地观测等任务中,需要精确知道卫星和空间目标在某一时刻的位置。通常我们使用开普勒轨道六要素(半长轴、偏心率、倾角、升交点赤经、近地点幅角、真近点角)来描述轨道,并通过轨道动力学外推得到任意时刻的位置。本文实现了一套基于J2000…...

如何实现格式保留翻译?Hunyuan MT1.5结构化文本处理实战解析

如何实现格式保留翻译?Hunyuan MT1.5结构化文本处理实战解析 1. 引言:当翻译遇到格式难题 你有没有遇到过这样的尴尬场景?好不容易找到一款翻译工具,把英文网页翻译成了中文,结果发现所有链接都失效了,排…...

如何彻底解决ComfyUI-Manager安装难题:终极完整指南

如何彻底解决ComfyUI-Manager安装难题:终极完整指南 【免费下载链接】ComfyUI-Manager ComfyUI-Manager is an extension designed to enhance the usability of ComfyUI. It offers management functions to install, remove, disable, and enable various custom …...

PyTorch 2.8镜像实际效果:torch.compile+FlashAttention-2双优化下的吞吐量提升对比

PyTorch 2.8镜像实际效果:torch.compileFlashAttention-2双优化下的吞吐量提升对比 1. 镜像环境与技术亮点 PyTorch 2.8深度学习镜像为开发者提供了一个开箱即用的高性能计算环境。基于RTX 4090D 24GB显卡和CUDA 12.4的深度优化组合,这个镜像特别适合需…...

Word文档自动更新日期技巧

设置Word文档自动显示当天日期打开Word文档后,可以通过插入日期字段实现每次打开时自动更新为当天日期。方法1:使用日期字段在Word文档中定位光标到需要显示日期的位置。点击菜单栏"插入"→"文本"→"日期和时间"。在弹出的…...

李慕婉-仙逆-造相Z-Turbo AI核心原理科普:如何用Transformer理解并生成人类语言

李慕婉-仙逆-造相Z-Turbo AI核心原理科普:如何用Transformer理解并生成人类语言 你有没有想过,当你和“李慕婉-仙逆-造相Z-Turbo”这样的AI模型对话时,它到底是怎么“听懂”你的话,又“想”出那些回答的?它不像我们人…...

DevOps工具链集成:GitLab CI、Jenkins与Argo CD如何选?

DevOps工具链集成:GitLab CI、Jenkins与Argo CD如何选? 在DevOps实践中,工具链的选型直接影响交付效率与系统稳定性。GitLab CI、Jenkins和Argo CD作为主流工具,分别覆盖持续集成(CI)、持续交付࿰…...

Qwen3.5-2B图文理解教程:GIF动图逐帧理解+动态内容总结生成方法

Qwen3.5-2B图文理解教程:GIF动图逐帧理解动态内容总结生成方法 1. 引言 Qwen3.5-2B是一款轻量化多模态基础模型,属于Qwen3.5系列的小参数版本(20亿参数)。这款模型主打低功耗、低门槛部署,特别适配端侧和边缘设备&am…...