翻译:How do I reset my FPGA?

文章目录

- 背景

- 翻译:How do I reset my FPGA?

- 1、Understanding the flip-flop reset behavior

- 2、Reset methodology

- 3、Use appropriate resets to maximize utilization

- 4、Many options

- 5、About the author

背景

在写博客《复位信号的同步与释放(同步复位、异步复位、异步复位同步释放)》时,

笔者遇到了一篇文章《How do I reset my FPGA?》,相逢是缘,决定将它阅读一下。

基于此,考虑到这篇文章是英文写的,就进行简单翻译下,供诸位道友参考,记作此文。

基于此,考虑到这篇文章是英文写的,就进行简单翻译下,供诸位道友参考,记作此文。

说明1:翻译水平有限,如果文章有误,欢迎大家指出、讨论,笔者也会积极改正,希望大家一起进步!

参考文献:《How do I reset my FPGA?》

翻译:How do I reset my FPGA?

在FPGA设计中,复位信号充当一种同步信号,用于将所有存储元件设置到已知状态。在数字设计中,设计者通常会实现一个全局复位信号作为外部引脚,以便在上电时对设计进行初始化。全局复位引脚与其他输入引脚类似,通常被异步地应用于FPGA。然后,设计者可以选择在FPGA内部使用这个信号来异步或同步地对他们的设计进行复位。

在FPGA设计中,复位信号充当一种同步信号,用于将所有存储元件设置到已知状态。在数字设计中,设计者通常会实现一个全局复位信号作为外部引脚,以便在上电时对设计进行初始化。全局复位引脚与其他输入引脚类似,通常被异步地应用于FPGA。然后,设计者可以选择在FPGA内部使用这个信号来异步或同步地对他们的设计进行复位。

但是,在一些提示和技巧的帮助下,设计者将找到可以用来选择更合适的复位结构的方法。一个优化的复位结构可以提升FPGA中的器件利用率、时序性能和功耗表现。

但是,在一些提示和技巧的帮助下,设计者将找到可以用来选择更合适的复位结构的方法。一个优化的复位结构可以提升FPGA中的器件利用率、时序性能和功耗表现。

1、Understanding the flip-flop reset behavior

在深入探讨复位技术之前,理解FPGA中slice内的触发器的行为至关重要。在Xilinx的7系列架构中,每台设备中的每个slice结构中包含八个寄存器,而且这些寄存器均为D型触发器。这些触发器公用一个共同的控制集。

在深入探讨复位技术之前,理解FPGA中slice内的触发器的行为至关重要。在Xilinx的7系列架构中,每台设备中的每个slice结构中包含八个寄存器,而且这些寄存器均为D型触发器。这些触发器公用一个共同的控制集。

触发器的控制集包括时钟输入(CLK)、高电平有效的芯片使能(CE)和高电平有效的SR端口。触发器中的SR端口可以作为 同步置位/复位端口 或 异步预置/清零端口 (见图1)。

触发器的控制集包括时钟输入(CLK)、高电平有效的芯片使能(CE)和高电平有效的SR端口。触发器中的SR端口可以作为 同步置位/复位端口 或 异步预置/清零端口 (见图1)。

可以编译出触发器的RTL代码也会编译出触发器将使用的复位类型。如图2a所示,当复位信号出现在RTL进程的敏感列表中时,代码会编译出一个异步复位。综合工具会编译出一个触发器,其SR端口配置为预置或清零端口,由FDCE或FDPE触发器原语表示。当SR端口被断言时,触发器的输出会立即被强制为触发器的SRVAL属性值。

可以编译出触发器的RTL代码也会编译出触发器将使用的复位类型。如图2a所示,当复位信号出现在RTL进程的敏感列表中时,代码会编译出一个异步复位。综合工具会编译出一个触发器,其SR端口配置为预置或清零端口,由FDCE或FDPE触发器原语表示。当SR端口被断言时,触发器的输出会立即被强制为触发器的SRVAL属性值。

在同步复位的情况下,综合工具会编译出一个触发器,其SR端口被配置为置位或复位端口,由FDSE或FDRE触发器原语表示。当SR端口被断言时,触发器的输出会在时钟的下一个上升沿被强制为触发器的SRVAL属性值。

在同步复位的情况下,综合工具会编译出一个触发器,其SR端口被配置为置位或复位端口,由FDSE或FDRE触发器原语表示。当SR端口被断言时,触发器的输出会在时钟的下一个上升沿被强制为触发器的SRVAL属性值。

此外,你还可以将触发器的输出初始化为INIT属性指定的值。INIT值在配置期间以及在全局置位/复位(GSR)信号被断言时加载到触发器中。

此外,你还可以将触发器的输出初始化为INIT属性指定的值。INIT值在配置期间以及在全局置位/复位(GSR)信号被断言时加载到触发器中。

Xilinx FPGA中的触发器可以支持 异步/同步 复位/置位 控制。然而,底层的触发器一次只能实现一个自带的 置位/复位/预置/清零 功能。如果在RTL代码中编写多个 置位/复位/预置/清零 条件,将会导致其中一个条件使用触发器的SR端口来实现,而其他的条件则通过FPGA的逻辑资源来实现,从而占用更多的FPGA资源。

Xilinx FPGA中的触发器可以支持 异步/同步 复位/置位 控制。然而,底层的触发器一次只能实现一个自带的 置位/复位/预置/清零 功能。如果在RTL代码中编写多个 置位/复位/预置/清零 条件,将会导致其中一个条件使用触发器的SR端口来实现,而其他的条件则通过FPGA的逻辑资源来实现,从而占用更多的FPGA资源。

如果其中一个条件是同步的,另一个是异步的,那么异步条件将由触发器的SR端口实现,而同步条件将通过逻辑资源来实现。一般来说,最好避免使用多个 置位/复位/预置/清零 条件。此外,每个slice中每四个触发器一组,其SR端口是同步还是异步,仅由一个(控制集的)属性决定。

如果其中一个条件是同步的,另一个是异步的,那么异步条件将由触发器的SR端口实现,而同步条件将通过逻辑资源来实现。一般来说,最好避免使用多个 置位/复位/预置/清零 条件。此外,每个slice中每四个触发器一组,其SR端口是同步还是异步,仅由一个(控制集的)属性决定。

2、Reset methodology

无论使用哪种复位类型(同步或异步),通常都需要将复位信号与时钟同步。只要全局复位脉冲的持续时间足够长,设备中的所有触发器都将进入复位状态。然而,复位信号的撤销必须满足触发器的时序要求,以确保触发器能够干净地从复位状态转换到正常状态。如果未能满足这一要求,可能会导致触发器进入亚稳态。

无论使用哪种复位类型(同步或异步),通常都需要将复位信号与时钟同步。只要全局复位脉冲的持续时间足够长,设备中的所有触发器都将进入复位状态。然而,复位信号的撤销必须满足触发器的时序要求,以确保触发器能够干净地从复位状态转换到正常状态。如果未能满足这一要求,可能会导致触发器进入亚稳态。

此外,为了确保某些子系统的正确运行(如状态机和计数器),所有触发器必须在同一时钟沿撤销复位。如果同一状态机的不同位在不同的时钟沿撤销复位,状态机可能会进入非法状态。这进一步强调了撤销复位信号与系统时钟同步的必要性。

此外,为了确保某些子系统的正确运行(如状态机和计数器),所有触发器必须在同一时钟沿撤销复位。如果同一状态机的不同位在不同的时钟沿撤销复位,状态机可能会进入非法状态。这进一步强调了撤销复位信号与系统时钟同步的必要性。

对于在给定时钟域中使用同步复位方法的设计而言,仅需使用标准的亚稳态解决电路(两个背靠背的触发器)将全局复位引脚同步到特定的时钟域即可。然后,这个被同步后的复位信号可以通过触发器上的同步SR端口初始化该时钟域中的所有存储元件。由于同步器和需要被复位的触发器都在同一个时钟域,时钟的标准PERIOD约束涵盖了它们之间路径的时序。设备中的每个时钟域都需要使用一个单独的同步器来为该时钟域生成一个全局复位的同步版本。

对于在给定时钟域中使用同步复位方法的设计而言,仅需使用标准的亚稳态解决电路(两个背靠背的触发器)将全局复位引脚同步到特定的时钟域即可。然后,这个被同步后的复位信号可以通过触发器上的同步SR端口初始化该时钟域中的所有存储元件。由于同步器和需要被复位的触发器都在同一个时钟域,时钟的标准PERIOD约束涵盖了它们之间路径的时序。设备中的每个时钟域都需要使用一个单独的同步器来为该时钟域生成一个全局复位的同步版本。

现在让我们直奔主题。这里有一些具体的技巧和建议,可以帮助你为产品设计找到最佳的复位策略。

现在让我们直奔主题。这里有一些具体的技巧和建议,可以帮助你为产品设计找到最佳的复位策略。

- 建议1:当对触发器的同步SR端口进行驱动时,每个时钟域都需要其自身的全局复位信号的本地化版本,并且该版本信号需与该时钟域同步。

有时,无法保证设计的一部分拥有有效的时钟。这可能发生在使用恢复时钟或由热插拔模块提供时钟的系统中。在这种情况下,可能需要通过触发器上的异步SR端口对设计中的存储元件异步复位进行初始化。即使存储元件使用异步SR端口,但复位信号的撤销边缘仍必须与时钟同步。这一要求由触发器的复位恢复时序弧线(reset-recovery timing arc)所定义,类似于异步SR的撤销边缘到时钟上升沿的建立时间要求。如果不能满足这一时序弧线,可能会导致触发器进入亚稳态、同步子系统进入非期望的状态。

有时,无法保证设计的一部分拥有有效的时钟。这可能发生在使用恢复时钟或由热插拔模块提供时钟的系统中。在这种情况下,可能需要通过触发器上的异步SR端口对设计中的存储元件异步复位进行初始化。即使存储元件使用异步SR端口,但复位信号的撤销边缘仍必须与时钟同步。这一要求由触发器的复位恢复时序弧线(reset-recovery timing arc)所定义,类似于异步SR的撤销边缘到时钟上升沿的建立时间要求。如果不能满足这一时序弧线,可能会导致触发器进入亚稳态、同步子系统进入非期望的状态。

如下图3所示,复位桥接电路提供了一种机制,可以异步地断言复位(即使在缺乏有效时钟的情况下,也会因此生效。),且同步地撤销复位。在这个电路中,有假设两个触发器的SR端口具有异步预置功能(SRVAL=1)。

如下图3所示,复位桥接电路提供了一种机制,可以异步地断言复位(即使在缺乏有效时钟的情况下,也会因此生效。),且同步地撤销复位。在这个电路中,有假设两个触发器的SR端口具有异步预置功能(SRVAL=1)。

你可以使用这种复位桥接电路的输出来驱动给定时钟域的异步复位。这个同步复位可以通过触发器上的异步SR端口初始化该时钟域中的所有存储元件。同样,设备中的每个时钟域都需要一个单独的、由单独的复位桥接电路生成的全局复位的同步版本。

你可以使用这种复位桥接电路的输出来驱动给定时钟域的异步复位。这个同步复位可以通过触发器上的异步SR端口初始化该时钟域中的所有存储元件。同样,设备中的每个时钟域都需要一个单独的、由单独的复位桥接电路生成的全局复位的同步版本。

- 建议2:复位桥接电路提供了一种安全的机制,用于同步地撤销异步复位。每个时钟域都需要使用复位桥接电路来生成其自身的全局复位的本地化版本。

图3,假设电路中用于时钟复位桥接及其相关逻辑的时钟(clk_a)是稳定且无误的。在FPGA中,时钟可以直接来自片外时钟源(理想情况下,通过支持时钟的引脚),或者用过多模时钟管理器(MMCM)或锁相环(PLL)在内部生成。任何被用来生成时钟的MMCM或PLL在复位后都需要校准。因此,你可能需要在全局复位路径中插入额外的逻辑来稳定该时钟。

图3,假设电路中用于时钟复位桥接及其相关逻辑的时钟(clk_a)是稳定且无误的。在FPGA中,时钟可以直接来自片外时钟源(理想情况下,通过支持时钟的引脚),或者用过多模时钟管理器(MMCM)或锁相环(PLL)在内部生成。任何被用来生成时钟的MMCM或PLL在复位后都需要校准。因此,你可能需要在全局复位路径中插入额外的逻辑来稳定该时钟。

- 建议3:在撤销对FPGA的全局复位之前,确保MMCM或PLL生成的时钟稳定且已锁定。

图4,展示了一个FPGA中典型的复位实现。Xilinx寄存器上的SR控制端口是高电平有效的。如果RTL代码描述了低电平有效的置位/复位/预置/清零功能,综合工具会在直接驱动寄存器的控制端口之前编译出一个反相器。而且必须通过查找表来完成这种反相,从而占用一个LUT输入。低电平控制信号编译出的额外逻辑可能导致运行时间更长、器件利用率降低,还会影响时序和功耗。

图4,展示了一个FPGA中典型的复位实现。Xilinx寄存器上的SR控制端口是高电平有效的。如果RTL代码描述了低电平有效的置位/复位/预置/清零功能,综合工具会在直接驱动寄存器的控制端口之前编译出一个反相器。而且必须通过查找表来完成这种反相,从而占用一个LUT输入。低电平控制信号编译出的额外逻辑可能导致运行时间更长、器件利用率降低,还会影响时序和功耗。

总结?尽可能在HDL代码或实例化组件中使用高电平有效的控制信号。当无法在设计中对控制信号的极性进行控制时,需要在代码的顶层层次结构中对信号进行反相。以这种方式(进行RTL)描述时,编译出的反相器可以被吸收进I/O逻辑中,而无需使用任何额外的FPGA逻辑或布线。

总结?尽可能在HDL代码或实例化组件中使用高电平有效的控制信号。当无法在设计中对控制信号的极性进行控制时,需要在代码的顶层层次结构中对信号进行反相。以这种方式(进行RTL)描述时,编译出的反相器可以被吸收进I/O逻辑中,而无需使用任何额外的FPGA逻辑或布线。

- 建议4:高电平有效的复位能够提高器件利用率、提升性能。

需要注意的是,FPGA并不一定需要一个全局复位。全局复位会与设计中的其它网络竞争相同的布线资源。由于需要传播到设计中的每一个触发器,全局复位通常具有很高的扇出,这可能会占用大量的布线资源,并对器件利用率和时序性能产生负面影响。因此,去探索不依赖于完整的全局复位的其它复位机制是非常值得的。

需要注意的是,FPGA并不一定需要一个全局复位。全局复位会与设计中的其它网络竞争相同的布线资源。由于需要传播到设计中的每一个触发器,全局复位通常具有很高的扇出,这可能会占用大量的布线资源,并对器件利用率和时序性能产生负面影响。因此,去探索不依赖于完整的全局复位的其它复位机制是非常值得的。

如图5所示,当Xilinx的FPGA被配置或重新配置时,每个单元(包括触发器和Block RAMs)都会被初始化。因此,FPGA配置与全局复位具有相同的效果,因为它会将FPGA中每个存储元件的初始状态设置为已知状态。

如图5所示,当Xilinx的FPGA被配置或重新配置时,每个单元(包括触发器和Block RAMs)都会被初始化。因此,FPGA配置与全局复位具有相同的效果,因为它会将FPGA中每个存储元件的初始状态设置为已知状态。

可以从RTL代码中推断触发器的初始化值。图6所示的示例,展示了如何在RTL中用代码对寄存器进行初始化。FPGA工具确实可以综合信号的初始化,尽管人们普遍误解认为这是不可能的。底层VHDL信号或Verilog寄存器的初始化值将成为编译出的触发器的INIT值,该值在配置期间会被加载到触发器中。

可以从RTL代码中推断触发器的初始化值。图6所示的示例,展示了如何在RTL中用代码对寄存器进行初始化。FPGA工具确实可以综合信号的初始化,尽管人们普遍误解认为这是不可能的。底层VHDL信号或Verilog寄存器的初始化值将成为编译出的触发器的INIT值,该值在配置期间会被加载到触发器中。

与寄存器类似,你也可以在配置期间初始化BRAM(Block RAMs)。随着基于处理器的系统中嵌入式RAM的增加,BRAM初始化已成为一项有用的功能。这是因为预定义的RAM便于更简单的仿真设置,并消除了嵌入式设计中需要启动序列来清除内存的要求。

与寄存器类似,你也可以在配置期间初始化BRAM(Block RAMs)。随着基于处理器的系统中嵌入式RAM的增加,BRAM初始化已成为一项有用的功能。这是因为预定义的RAM便于更简单的仿真设置,并消除了嵌入式设计中需要启动序列来清除内存的要求。

全局置位/复位(GSR)信号是一种特殊的预布线复位信号,它在FPGA配置过程中将设计保持在初始状态。配置完成后,GSR信号被释放,此时所有的触发器和其他资源都具备了它们的INIT值。除了在配置过程中使用它之外,用户设计可以通过实例化STARTUPE2模块并连接到GSR端口来使用GSR网络。通过使用这个端口,设计可以重新断言GSR网络,这将使FPGA中的所有存储元件返回到由它们的INIT属性指定的状态。

全局置位/复位(GSR)信号是一种特殊的预布线复位信号,它在FPGA配置过程中将设计保持在初始状态。配置完成后,GSR信号被释放,此时所有的触发器和其他资源都具备了它们的INIT值。除了在配置过程中使用它之外,用户设计可以通过实例化STARTUPE2模块并连接到GSR端口来使用GSR网络。通过使用这个端口,设计可以重新断言GSR网络,这将使FPGA中的所有存储元件返回到由它们的INIT属性指定的状态。

GSR的撤销是异步的,并且可能需要几个时钟周期才能影响设计中的所有触发器。状态机、计数器或其它任何可以自动改变状态的逻辑都需要一个明确的复位信号,该复位信号的撤销与用户时钟同步。因此,仅使用GSR作为唯一的复位机制可能会导致系统不可靠。因此,采用混合方法来有效管理启动过程会更好。

GSR的撤销是异步的,并且可能需要几个时钟周期才能影响设计中的所有触发器。状态机、计数器或其它任何可以自动改变状态的逻辑都需要一个明确的复位信号,该复位信号的撤销与用户时钟同步。因此,仅使用GSR作为唯一的复位机制可能会导致系统不可靠。因此,采用混合方法来有效管理启动过程会更好。

- 建议5:采用一种混合方法,依赖GSR提供的内置初始化功能,同时为设计中可以自主启动的部分提供明确的复位信号,可以带来更好的利用率和性能。

在使用GSR设置整个设计的初始状态之后,对于需要同步复位的逻辑元件(如状态机),使用明确的复位信号。可以通过标准的亚稳态解决电路或复位桥接电路来生成明确复位信号的同步版本。

在使用GSR设置整个设计的初始状态之后,对于需要同步复位的逻辑元件(如状态机),使用明确的复位信号。可以通过标准的亚稳态解决电路或复位桥接电路来生成明确复位信号的同步版本。

3、Use appropriate resets to maximize utilization

工具会把设计映射到底层FPGA资源,而在RTL代码中使用的复位风格会对工具的这种能力产生显著影响。在编写RTL代码时,设计者需要调整其子设计的复位风格,以便工具能够将设计映射到这些资源上,这是很重要的。

工具会把设计映射到底层FPGA资源,而在RTL代码中使用的复位风格会对工具的这种能力产生显著影响。在编写RTL代码时,设计者需要调整其子设计的复位风格,以便工具能够将设计映射到这些资源上,这是很重要的。

除了使用GSR机制进行初始化外,你无法使用明确的复位信号来复位SRLs(移位寄存器锁存器)、LUTRAMs(查找表RAM)和块RAM(Block RAMs)的内容。因此,在编写那些会被映射到这些资源的代码时,重要的是,要专门编写不带复位的代码。例如,如果RTL代码描述了一个32位移位寄存器,并为移位寄存器中的32个阶段提供了明确的复位,综合工具将无法直接将此RTL代码映射到SRL32E,因为它无法使用这种资源来满足编码复位的要求。反而,它可能会编译出32个触发器,也可能会围绕SRL32E编译出一些额外的电路,来实现所需的复位功能。相比于编写不带复位的RTL代码,这两种解决方案都将需要消耗更多的资源。

除了使用GSR机制进行初始化外,你无法使用明确的复位信号来复位SRLs(移位寄存器锁存器)、LUTRAMs(查找表RAM)和块RAM(Block RAMs)的内容。因此,在编写那些会被映射到这些资源的代码时,重要的是,要专门编写不带复位的代码。例如,如果RTL代码描述了一个32位移位寄存器,并为移位寄存器中的32个阶段提供了明确的复位,综合工具将无法直接将此RTL代码映射到SRL32E,因为它无法使用这种资源来满足编码复位的要求。反而,它可能会编译出32个触发器,也可能会围绕SRL32E编译出一些额外的电路,来实现所需的复位功能。相比于编写不带复位的RTL代码,这两种解决方案都将需要消耗更多的资源。

- 建议6:在映射到SRLs(移位寄存器锁存器)、LUTRAMs(查找表RAM)或块RAM(Block RAMs)时,不要为SRL或RAM矩阵编写复位代码。

在7系列器件中,无法将具有不同控制信号下的触发器打包到同一个slice中。对于低扇出复位,这可能会对整体slice利用率产生负面影响。如图7所示,对于同步复位,综合工具可以使用查找表(LUT)来实现复位功能,而不是使用触发器的控制端口,从而将复位作为控制端口进行移除。这意味着,你可以把得到的 LUT/触发器对 与其它未使用其SR端口的触发器打包在一起,这可能会带来更高的LUT利用率,但也会提高切片利用率。

在7系列器件中,无法将具有不同控制信号下的触发器打包到同一个slice中。对于低扇出复位,这可能会对整体slice利用率产生负面影响。如图7所示,对于同步复位,综合工具可以使用查找表(LUT)来实现复位功能,而不是使用触发器的控制端口,从而将复位作为控制端口进行移除。这意味着,你可以把得到的 LUT/触发器对 与其它未使用其SR端口的触发器打包在一起,这可能会带来更高的LUT利用率,但也会提高切片利用率。

- 建议7:同步复位能够提升FPGA的利用率。在设计中使用同步复位,而不是异步复位

一些较大的专用资源(即,Block RAMs和DSP48E1 cells)包含寄存器,是作为专用资源功能的一部分被编译出来的寄存器。Block RAMs具有可选的输出寄存器,可以通过使用它们来增加一个时钟周期的延迟,从而提高时钟频率。DSP48E1 cells有许多寄存器,你可以将它们用于流水线处理以提高最大时钟速度,也可以用于周期延迟(Z-1)。然而,这些寄存器仅具有 同步置位/复位 功能。

一些较大的专用资源(即,Block RAMs和DSP48E1 cells)包含寄存器,是作为专用资源功能的一部分被编译出来的寄存器。Block RAMs具有可选的输出寄存器,可以通过使用它们来增加一个时钟周期的延迟,从而提高时钟频率。DSP48E1 cells有许多寄存器,你可以将它们用于流水线处理以提高最大时钟速度,也可以用于周期延迟(Z-1)。然而,这些寄存器仅具有 同步置位/复位 功能。

- 建议8:使用同步复位允许综合工具使用DSP48E1 slices或block RAMs等内部专用资源的寄存器。这可以提高设计这部分中的整体器件的利用率和性能,并且还能降低整体功耗。

如果RTL代码描述了 异步置位/复位 ,那么综合工具将无法使用这些内部寄存器。相反,它将使用slice中的触发器,因为它们可以实现所需的 异步置位/复位 功能。这不仅会导致器件利用率低下,还会对性能和功耗产生负面影响。

如果RTL代码描述了 异步置位/复位 ,那么综合工具将无法使用这些内部寄存器。相反,它将使用slice中的触发器,因为它们可以实现所需的 异步置位/复位 功能。这不仅会导致器件利用率低下,还会对性能和功耗产生负面影响。

4、Many options

FPGA有多种复位选项可供选择,每种都有其自身的优势和劣势。这里概述的建议将帮助设计者为他们的设计选择一个合适的复位结构。一个优化的复位结构将提升FPGA的器件利用率、时序性能和功耗表现。

FPGA有多种复位选项可供选择,每种都有其自身的优势和劣势。这里概述的建议将帮助设计者为他们的设计选择一个合适的复位结构。一个优化的复位结构将提升FPGA的器件利用率、时序性能和功耗表现。

5、About the author

相关文章:

翻译:How do I reset my FPGA?

文章目录 背景翻译:How do I reset my FPGA?1、Understanding the flip-flop reset behavior2、Reset methodology3、Use appropriate resets to maximize utilization4、Many options5、About the author 背景 在写博客《复位信号的同步与释放(同步复…...

Linux 进程环境变量:深入理解与实践指南

🌟 快来参与讨论💬,点赞👍、收藏⭐、分享📤,共创活力社区。🌟 🚩用通俗易懂且不失专业性的文字,讲解计算机领域那些看似枯燥的知识点🚩 在 Linux 系统里…...

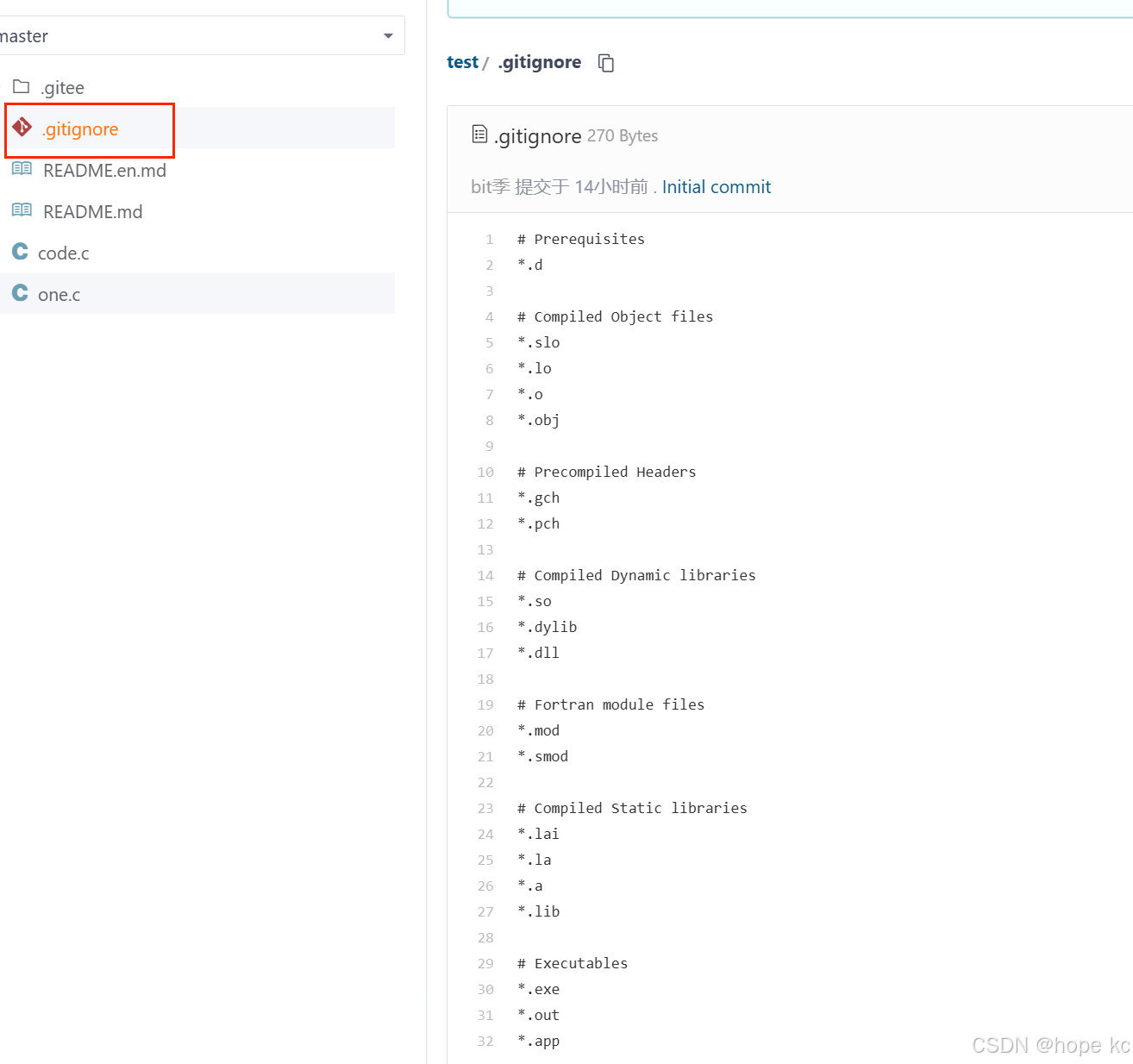

Linux探秘坊-------5.git

1.git介绍 1.版本控制器 为了能够更⽅便我们管理这些不同版本的⽂件,便有了版本控制器。所谓的版本控制器,就是能让你了解到⼀个⽂件的历史,以及它的发展过程的系统。通俗的讲就是⼀个可以记录⼯程的每⼀次改动和版本迭代的⼀个管理系统&am…...

Linux中的几个基本指令(二)

文章目录 1、cp指令例一:例二:例三:例四:例五: 2、mv 指令例一:例二: 3、cat指令例一: 4、tac指令5、which指令6、date指令时间戳:7、zip指令 今天我们继续学习Linux下的…...

)

Java入门笔记(1)

引言 在计算机编程的广袤宇宙中,Java无疑是一颗格外耀眼的恒星。那么,Java究竟是什么呢? Java是美国Sun公司(Stanford University Network)在1995年推出的一门计算机高级编程语言。曾经辉煌的Sun公司在2009年被Oracle&…...

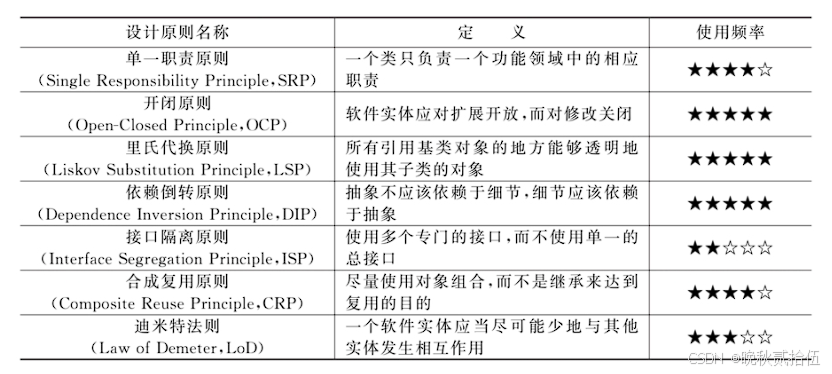

设计模式的艺术-开闭原则

原则使用频率图(仅供参考) 1.如何理解开闭原则 简单来说,开闭原则指的是 “对扩展开放,对修改关闭”。 当软件系统需要增加新的功能时,应该通过扩展现有代码的方式来实现,而不是去修改已有的代码。 例如我…...

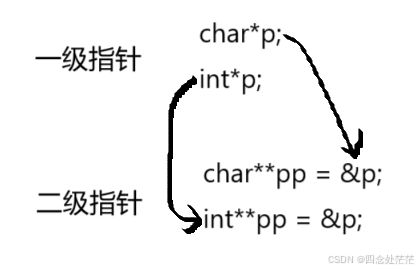

【C语言系列】深入理解指针(3)

深入理解指针(3) 一、字符指针变量二、数组指针变量2.1数组指针变量是什么?2.2数组指针变量怎么初始化? 三、二维数组传参的本质四、函数指针变量4.1函数指针变量的创建4.2函数指针变量的使用4.3两段有趣的代码4.4 typedef关键字 …...

three.js+WebGL踩坑经验合集:写在前面的话

笔者从2023年初开始参与一个基于three.js引擎的web项目的开发工作。本打算2024年春节就把期间踩过的坑写到博客上分享给大家,然而哪怕本专栏的各种构思和内容已经在笔者的脑海里翻滚了一年,得了严重拖延症患者的我还是一直拖到了现在,实在惭愧…...

利用Linux的工作队列(Workqueue)实现中断下半部的处理

本文代码在哪个基础上修改而成? 本文是在博文 https://blog.csdn.net/wenhao_ir/article/details/145228617 的代码基础上修改而成。 关于工作队列(Workqueue)的概念 工作队列(Workqueue)可以用于实现Linux的中断下半部的,之前在博文 https://blog.cs…...

LabVIEW处理复杂系统和数据处理

LabVIEW 是一个图形化编程平台,广泛应用于自动化控制、数据采集、信号处理、仪器控制等复杂系统的开发。它的图形化界面使得开发人员能够直观地设计系统和算法,尤其适合处理需要实时数据分析、高精度控制和复杂硬件集成的应用场景。LabVIEW 提供丰富的库…...

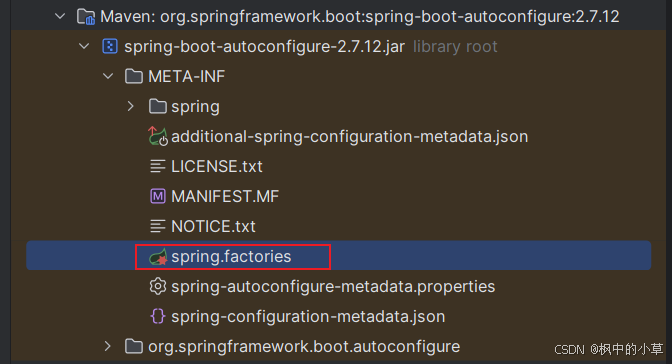

spring-springboot -springcloud

目录 spring: 动态代理: spring的生命周期(bean的生命周期): SpringMvc的生命周期: SpringBoot: 自动装配: 自动装配流程: Spring中常用的注解: Spring Boot中常用的注解: SpringCloud: 1. 注册中心: 2. gateway(网关): 3. Ribbon(负载均…...

DRG/DIP 2.0时代下基于PostgreSQL的成本管理实践与探索(下)

五、数据处理与 ETL 流程编程实现 5.1 数据抽取与转换(ETL) 在 DRG/DIP 2.0 时代的医院成本管理中,数据抽取与转换(ETL)是将医院各个业务系统中的原始数据转化为可供成本管理分析使用的关键环节。这一过程涉及从医院 HIS 系统中抽取患者诊疗数据,并对其进行格式转换、字…...

打造本地音乐库

文章目录 存储介质硬盘(NAS)媒体播放器(可视MP3、MP4)实体介质(CD光盘、黑胶片)注意事项为什么不使用在线音乐(App)和网盘打造一套HiFi系统的成本非常高 获取音乐正版音乐途径免费音…...

【2024 - 年终总结】叶子增长,期待花开

写在前面:本博客仅作记录学习之用,部分图片来自网络,如需引用请注明出处,同时如有侵犯您的权益,请联系删除! 文章目录 前言论博客创作保持2024的记录清单博客科研开源工作生活 总结与展望互动致谢参考 前言…...

python 统计相同像素值个数

目录 python 统计相同像素值个数 最大值附近的值 python 统计相同像素值个数 import cv2 import numpy as np import time from collections import Counter# 读取图像 image cv2.imread(mask16.jpg)# 将图像转换为灰度图像 gray_image cv2.cvtColor(image, cv2.COLOR_BGR2…...

蓝卓“1+2+N”智慧工厂架构,让工业智能更简单

面对复杂的工业环境、海量的数据以及多样化的业务需求,如何实现智能化转型,让工业智能触手可及,成为了众多企业面临的难题。蓝卓以创新精神为引领,推出了“12N”智慧工厂架构,旨在简化工业智能的实现路径,让…...

12、MySQL锁相关知识

目录 1、全局锁和表锁使用场景 2、行锁的意义 3、为什么说间隙锁解决了快照的幻读? 4、RR隔离级别产生幻读的场景 5、详解元数据锁(MDL)作用以及如何减少元数据锁 6、出现死锁场景 7、查看MySQL锁情况 8、自增锁 1、全局锁和表锁使用场景 全局锁 备份数据库:当需要…...

某大厂一面:HashMap 的put方法具体做了哪些操作

HashMap 的 put 方法是一个常用的操作,它将一个键值对插入到哈希表中。下面是 put 方法执行的详细流程,包括各个步骤的解释,并附上相应的代码片段。 1. 检查键是否为 null 如果传入的键为 null,HashMap 会特别处理这种情况&…...

WPF基础 | 深入 WPF 事件机制:路由事件与自定义事件处理

WPF基础 | 深入 WPF 事件机制:路由事件与自定义事件处理 一、前言二、WPF 事件基础概念2.1 事件的定义与本质2.2 常见的 WPF 事件类型 三、路由事件3.1 路由事件的概念与原理3.2 路由事件的三个阶段3.3 路由事件的标识与注册3.4 常见的路由事件示例 四、自定义事件处…...

精选100+套HTML可视化大屏模板源码素材

大屏数据可视化以大屏为主要展示载体的数据可视化设计。 “大面积、炫酷动效、丰富色彩”,大屏易在观感上给人留下震撼印象,便于营造某些独特氛围、打造仪式感。 原本看不见的数据可视化后,便能调动人的情绪、引发人的共鸣。 使用方法&…...

Verilog自动化测试进阶:用VSCode插件5分钟生成带时序图的Testbench模板

Verilog自动化测试进阶:用VSCode插件5分钟生成带时序图的Testbench模板 在数字电路设计领域,Testbench的编写往往占据了工程师大量时间。传统手动编写方式不仅效率低下,还容易遗漏关键测试场景。本文将带你探索如何利用VSCode生态中的Verilog…...

)

TLK2711芯片的8B/10B编码与Comma发送详解:从原理到FPGA代码实现(附Verilog示例)

TLK2711芯片的8B/10B编码与Comma发送全解析:从原理到FPGA实现 高速串行通信领域,TLK2711作为TI的明星产品,其稳定性和性能一直备受工程师关注。但真正让这颗芯片发挥极致性能的关键,往往隐藏在那些看似简单的协议细节中——比如8B…...

2026届毕业生推荐的六大AI辅助论文方案解析与推荐

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 人工智能技术已然极为深入广泛地融入到了高等教育的场景之中,于毕业论文写作的整…...

Kettle连接MySQL实战:从JDBC到JNDI的两种配置详解

1. Kettle连接MySQL的两种方式:JDBC与JNDI Kettle(现称为Pentaho Data Integration)作为一款强大的ETL工具,与MySQL数据库的连接是数据工程师日常工作中的高频操作。在实际项目中,我们通常会遇到两种连接方式ÿ…...

3分钟上手:B站视频数据分析工具快速指南

3分钟上手:B站视频数据分析工具快速指南 【免费下载链接】Bilivideoinfo Bilibili视频数据爬虫 精确爬取完整的b站视频数据,包括标题、up主、up主id、精确播放数、历史累计弹幕数、点赞数、投硬币枚数、收藏人数、转发人数、发布时间、视频时长、视频简介…...

从数据遗忘到数字记忆:WeChatMsg如何重塑你的微信聊天价值体系

从数据遗忘到数字记忆:WeChatMsg如何重塑你的微信聊天价值体系 【免费下载链接】WeChatMsg 提取微信聊天记录,将其导出成HTML、Word、CSV文档永久保存,对聊天记录进行分析生成年度聊天报告 项目地址: https://gitcode.com/GitHub_Trending/…...

5步快速搞定ComfyUI-Impact-Pack中SAM模型加载失败的终极指南

5步快速搞定ComfyUI-Impact-Pack中SAM模型加载失败的终极指南 【免费下载链接】ComfyUI-Impact-Pack Custom nodes pack for ComfyUI This custom node helps to conveniently enhance images through Detector, Detailer, Upscaler, Pipe, and more. 项目地址: https://gitc…...

3分钟掌握Windows三指拖拽:让触控板操作效率翻倍

3分钟掌握Windows三指拖拽:让触控板操作效率翻倍 【免费下载链接】ThreeFingersDragOnWindows Enables macOS-style three-finger dragging functionality on Windows Precision touchpads. 项目地址: https://gitcode.com/gh_mirrors/th/ThreeFingersDragOnWindo…...

)

Mac用户别慌!手把手教你在M1/M2芯片Mac上查看GPU性能日志(nvvp文件)

M1/M2芯片Mac用户实战指南:跨平台分析CUDA性能日志的完整方案 当你在Linux服务器上跑完耗时三天的深度学习训练,生成了宝贵的.nvvp性能分析文件,却发现手边的M2 MacBook Pro根本无法直接打开——这种技术栈割裂的痛,只有经历过的人…...

)

别再只盯着EDID了!一文搞懂DisplayPort的DPCD配置与链路协商(附实战解析)

DisplayPort链路协商深度解析:从DPCD寄存器到实战调试 在显示技术领域,工程师们常常将注意力集中在EDID(Extended Display Identification Data)上,却忽视了DisplayPort接口中更为关键的动态协商机制——DPCDÿ…...