FPGA实现SDI视频缩放转UltraScale GTH光口传输,基于GS2971+Aurora 8b/10b编解码架构,提供2套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 我这里已有的 GT 高速接口解决方案

- 本博已有的 SDI 编解码方案

- 我这里已有的FPGA图像缩放方案

- 3、工程详细设计方案

- 工程设计原理框图

- SDI 输入设备

- GS2971芯片

- BT1120转RGB

- 纯Verilog图像缩放模块详解

- 纯Verilog图像缩放模块使用(重点阅读)

- 视频数据组包

- 基于UltraScale GTH高速接口的视频传输架构

- UltraScale GTH IP 简介

- UltraScale GTH 基本结构

- UltraScale GTH 的参考时钟

- UltraScale GTH 发送和接收处理流程

- UltraScale GTH 发送接口

- UltraScale GTH 接收接口

- UltraScale GTH IP核调用和使用

- 接收数据对齐模块

- 视频数据解包

- FDMA图像缓存

- HDMI视频输出

- 工程源码架构

- 4、vivado工程源码1详解-->KU060版本

- 5、vivado工程源码2详解-->Zynq UltraScale ZU4EV版本

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证

- 准备工作

- UltraScale GTH光口SDI视频传输效果演示

- 8、工程代码的获取

FPGA实现SDI视频缩放转UltraScale GTH光口传输,基于GS2971+Aurora 8b/10b编解码架构,提供2套工程源码和技术支持

1、前言

FPGA实现SDI视频编解码现状;

一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。本设计使用GS2971接收器方案;

FPGA实现SFP光口视频编解码现状;

目前基于Xilinx系列FPGA的SFP光口视频编解码主要有以下几种,Artix7系列的GTP、Kintex7系列的GTX、更高端FPGA器件的GTH、GTY、GTV、GTM等,线速率越来越高,应用场景也越来越高端;编码方式也是多种多样,有8b/10b编解码、64b/66b编解码、HDMI编解码、SDI编解码等等;本设计采用UltraScale系列的UltraScale GTH作为高速接口、8b/10b编解码的方式实现SFP光口视频编解码;

工程概述

本设计使用Xilinx UltraScale系列FPGA为平台,实现UltraScale GTH 8b/10b编解码视频传输;输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用SD-SDI或者HD-SDI相机,因为本设计是三种SDI视频自适应的,同轴的SDI视频通过同轴线连接到GS2971转接板,GS2971解码芯片将同轴串行的SDI视频解码为并行的BT1120格式视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;然后使用纯verilog实现的BT1120转RGB模块实现视频格式转换后输出RGB888视频;然后使用自研的、纯verilog实现的、支持任意比例缩放的图像缩放模块实现对输入视频的图像缩放操作;然后缩放视频送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用Xilinx官方的UltraScale GTH IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入Xilinx官方的UltraScale GTH IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后使用本博主常用的FDMA图像缓存架构对采集视频做图像3帧缓存,缓存介质为板载DDR4;然后Native视频时序控制FDMA从DDR4中读取视频并同步输出RGB888视频流;然后使用RGB转HDMI模块或专用芯片实现RGB视频流转HDMI差分视频信号;最后用显示器显示视频即可;针对市场主流需求,本博客设计并提供2套工程源码,具体如下:

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–Kintex UltraScale–xcku060-ffva1156-2-i;输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用SD-SDI或者HD-SDI相机,因为本设计是三种SDI视频自适应的,同轴的SDI视频通过同轴线连接到GS2971转接板,GS2971解码芯片将同轴串行的SDI视频解码为并行的BT1120格式视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;然后使用纯verilog实现的BT1120转RGB模块实现视频格式转换后输出RGB888视频;然后使用自研、纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为1280x720;然后缩放视频送入送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用Xilinx官方的UltraScale GTH IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入Xilinx官方的UltraScale GTH IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后使用本博主常用的FDMA图像缓存架构对采集视频做图像3帧缓存,缓存介质为板载DDR4;然后Native视频时序控制FDMA从DDR4中读取视频并同步输出RGB888视频流;然后经过纯verilog显示的RGB转HDMI模块输出HDMI差分视频,输出分辨率为1280x720@60Hz;由此形成Sensor+高速接口+光编码+HDMI的高端架构;该工程适用于SFP光口的视频采集卡(光端机)应用;

工程源码2

开发板FPGA型号为Xilinx–>Zynq UltraScale–xczu4ev-sfvc784-1-i;输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用SD-SDI或者HD-SDI相机,因为本设计是三种SDI视频自适应的,同轴的SDI视频通过同轴线连接到GS2971转接板,GS2971解码芯片将同轴串行的SDI视频解码为并行的BT1120格式视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;然后使用纯verilog实现的BT1120转RGB模块实现视频格式转换后输出RGB888视频;然后使用自研、纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为1280x720;然后缩放视频送入送入视频组包模块,将视频的每一行打上包头包尾标记以包的形式输出,以便接收方进行有效识别;让后调用Xilinx官方的UltraScale GTH IP核实现视频8b/10b编码和数据串化,将并行数据串化为高速串行差分信号,线速率设置为5Gbps,编码后的视频通过板载的SFP光口的光纤输出;然后用板载的SFP光口的光纤接收视频,然后送入Xilinx官方的UltraScale GTH IP核实现视频8b/10b解码和数据解串,将差分高速串行信号解为并行数据;然后数据送入数据对齐模块,实现错位数据对齐;然后数据送入视频解包模块,实现每一行的视频包头包尾拆解,并生成对应的场同步信号和数据有效信号输出;然后使用本博主常用的FDMA图像缓存架构对采集视频做图像3帧缓存,缓存介质为PS端DDR4;然后Native视频时序控制FDMA从DDR4中读取视频并同步输出RGB888视频流;然后经过ADV7511输出HDMI差分视频,输出分辨率为1280x720@60Hz;由此形成Sensor+高速接口+光编码+HDMI的高端架构;该工程适用于SFP光口的视频采集卡(光端机)应用;

本博客详细描述了FPGA基于Aurora 8b/10b编解码架构实现UltraScale GTH光口视频传输的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

我这里已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

3、工程详细设计方案

工程设计原理框图

工程设计原理框图如下:

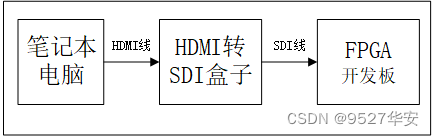

SDI 输入设备

SDI 输入设备可以是SDI相机,代码兼容HD/SD/3G-SDI三种模式;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

GS2971芯片

本设计采用GS2971芯片解码SDI,GS2971不需要软件配置,硬件电阻上下拉即可完成配置,本设计配置为输出BT1120格式视频,当然,你在设计电路时也可以配置为输出CEA861格式视频;GS2971硬件架构如下,提供PDF格式原理图:

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

BT1120转RGB模块顶层接口如下:

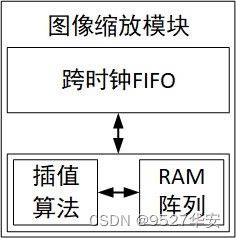

纯Verilog图像缩放模块详解

本设计的图像缩放模块使用纯Verilog方案,功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

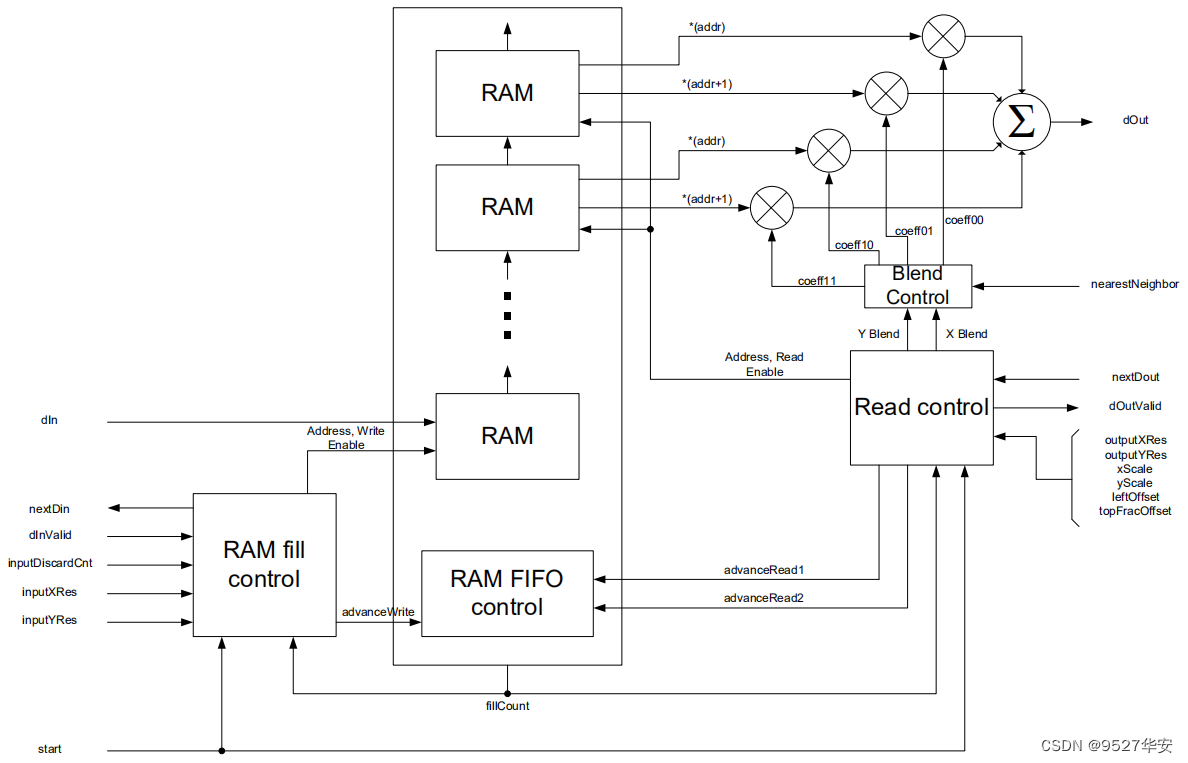

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

依据上图,图像缩放模块内部核心是例化了4个双口RAM,作用是缓存4行图像,以得到4个临近的像素,以此为基础做线性插值;如果是做图像放大操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中插入更多的像素点来扩大分辨率;如果是做图像缩小操作,就以这4个临近的像素为基准,以线性插值为算法,在原图像中删除更多的像素点来缩小分辨率;此外,前面描述的工作是实时的、整幅图像全部扫描式的进行,所以需要对RAM的读写操作进行精准控制;

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

代码里的配置如下:

纯Verilog图像缩放模块使用(重点阅读)

图像缩放模块使用非常简单,顶层代码里设置了四个参数,举例如下:

上图是将输入视频分辨率从1280x720缩放为1920x1080;

如果你想将输入视频分辨率从1280x720缩放为640x480;

则只需修改为如下:

再比如你想将输入视频分辨率从1280x720缩放为960x540;

则只需修改为如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

在本博主这里,想要实现图像缩放,操作就是这么无脑简单,就该两个参数就能搞定貌似高大上的双线性插值图像缩放,这种设计、这种操作、这种工程源码,你还喜欢吗?

视频数据组包

由于视频需要在UltraScale GTH 中通过aurora 8b/10b协议收发,所以数据必须进行组包,以适应aurora 8b/10b协议标准;视频数据组包模块代码位置如下:

首先,我们将16bit的视频存入FIFO中,存满一行时就从FIFO读出送入UltraScale GTH发送;在此之前,需要对一帧视频进行编号,也叫作指令,UltraScale GTH组包时根据固定的指令进行数据发送,UltraScale GTH解包时根据固定的指令恢复视频的场同步信号和视频有效信号;当一帧视频的场同步信号上升沿到来时,发送一帧视频开始指令 0,当一帧视频的场同步信号下降沿到来时,发送一帧视频开始指令 1,视频消隐期间发送无效数据 0 和无效数据 1,当视频有效信号到来时将每一行视频进行编号,先发送一行视频开始指令,在发送当前的视频行号,当一行视频发送完成后再发送一行视频结束指令,一帧视频发送完成后,先发送一帧视频结束指令 0,再发送一帧视频结束指令 1;至此,一帧视频则发送完成,这个模块不太好理解,所以我在代码里进行了详细的中文注释,需要注意的是,为了防止中文注释的乱序显示,请用notepad++编辑器打开代码;指令定义如下:

注意!!!指令可以任意更改,但最低字节必须为bc;

基于UltraScale GTH高速接口的视频传输架构

本设计使用UltraScale GTH高速接口传输视频,使用8b/10b编解码协议,搭建基于UltraScale GTH高速接口的视频传输架构,包括视频数据组包模块、UltraScale GTH IP核配置调用、接收数据对齐模块、视频数据解包模块等部分,总体代码架构如下:

基于UltraScale GTH高速接口的视频传输架构顶层接口核参数配置如下:

本设计共例化了2路UltraScale GTH,所以2路UltraScale GTH的收发回环方式也做了灵活的参数化配置,如果你只需要1路GT,则可删除另一路,如果你想例化更多路GT,则可根据上述设计方法扩展,十分方便;

UltraScale GTH IP 简介

关于UltraScale GTH 介绍最详细的肯定是Xilinx官方的《ug576-ultrascale-gth-transceivers》,我们以此来解读:《ug576-ultrascale-gth-transceivers》的PDF文档我已放在了资料包里;我用到的开发板FPGA型号为Kirtex7-UltraScale-xcku060-ffva1156-2-i;带有28路UltraScale GTX资源,其中2路连接到了板载2个SFP光口,每通道的收发速度为 500 Mb/s 到 16.375 Gb/s 之间。GTH 收发器支持不同的串行传输接口或协议,比如8b/10b编解码、PCIE /2.0/3.0 接口、万兆网 XUAI 接口、OC-48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、数字分量串行接口(SDI)等等;

UltraScale GTH 基本结构

UltraScale GTH 基本结构如下:

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道),下图为UltraScale GTH 收发器在Kintex7 UltraScale FPGA 芯片中的示意图:《ug576-ultrascale-gth-transceivers》第19页;

在 Ultrascale/Ultrascale+架构系列的 FPGA 中,GTH 高速收发器通常使用 Quad 来划分,一个 Quad 由四个GTHE3/4_CHANNEL 原语和一个 GTHE3/4_COMMON 原语组成。每个GTHE3/4_COMMON 中包含两个 LC-tank pll(QPLL0 和 QPLL1)。只有在应用程序中使用 QPLL 时,才需要实例化 GTHE3/4_COMMON。每个 GTHE3/4_CHANNEL 由一个 channel PLL(CPLL)、一个 transmitter,和一个 receiver 组成。一个参考时钟可以直接连接到一个 GTHE3/4_CHANNEL 原语,而不需要实例化 GTHE3/4_COMMON;

Ultrascale GTH 收发器的发送端和接收端功能是相互独立,都是由 Physical Media Attachment(物理媒介适配层 PMA)和Physical Coding Sublayer(物理编码子层 PCS)组成。PMA 内部集成了串并转换(PISO)、预加重、接收均衡、时钟发生器和时钟恢复等;PCS 内部集成了 8b/10b 编解码、弹性缓冲区、通道绑定和时钟修正等,每个 GTHE3/4_CHANNEL源语的逻辑电路见《ug576-ultrascale-gth-transceivers》第20页;

UltraScale GTH 的参考时钟

UltraScale 器件中的 GTH 收发器提供了不同的参考时钟输入选项。参考时钟选择架构支持 QPLL0、QLPLL1 和CPLL。从架构上讲,每个 Quad 包含四个 GTHE3/4_CHANNEL 原语,一个 GTHE3/4_COMMON 原语,两个专用的外部参考时钟引脚对,以及专用的参考时钟路由。如果使用到了高性能 QPLL,则必须实例化 GTHE3/4_COMMON,如下面 GTHE3/4_COMMON 时钟多路复用器结构的详细视图所示,(《ug576-ultrascale-gth-transceivers》第33页)在一个 Quad 中有 6 个参考时钟引脚对,两个本地参考时钟引脚对:GTREFCLK0或GTREFCLK1,两个参考时钟引脚对来自上面的两个Quads:GTSOUTHREFCLK0或 GTSOUTHREFCLK1,两个参考时钟引脚对来自下面的两个 Quads: GTNORTHREFCLK0 或GTNORTHREFCLK1。

UltraScale GTH 发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

UltraScale GTH 发送接口

《ug576-ultrascale-gth-transceivers》的第104到179页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲UltraScale GTH例化时留给用户的发送部分需要用到的接口;用户只需要关心发送接口的时钟和数据即可,以例化2路UltraScale GTH 为例,经本博主优化,用户只需要关心如下UltraScale GTH 发送接口即可快速使用UltraScale GTH ;

UltraScale GTH 接收接口

《ug576-ultrascale-gth-transceivers》的第181到314页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲UltraScale GTH 例化时留给用户的发送部分需要用到的接口;用户只需要关心接收接口的时钟和数据即可,以例化2路UltraScale GTH 为例,经本博主优化,用户只需要关心如下UltraScale GTH 接收接口即可快速使用UltraScale GTH ;

UltraScale GTH IP核调用和使用

UltraScale GTH IP核配置调用在工程种位置如下:

UltraScale GTH IP核调用和使用很简单,通过vivado的UI界面即可完成,如下:

UltraScale GTH基本配置如下:板载差分晶振125M,线速率配置为5G,协议类型被指为aurora 8b/10b;如下:

相较于Xilinx 7系列FPGA的GT高速接口,UltraScale系列FPGA在物理约束页也有较大改进,已不需要用户再去查看官方数据手册找到原理图所在的FPGA内部位置,而是直接给出了详细PIN脚,只要在这里选对了位置,GT高速接口的时钟和数据引脚在XDC中已不再需要约束,如下:

此外,有别于Xilinx 7系列FPGA的GT高速接口;UltraScale 系列FPGA的GT高速接口在控制引脚方面更加细节,用户可以选择具体哪些控制引脚被使用,当然,这需要开发人员对SERDES技术有较高的认知,在此基础上,可使我们的设计更加便捷,对于8B/10编解码协议而言,开发者可能只需关注并使用极性反转控制,如果需要动态变速,可能还需要使用DRP接口,其余功能性接口其实不必太过关注;如下:

接收数据对齐模块

由于GT资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;数据对齐模块顶层接口如下:

视频数据解包

数据解包是数据组包的逆过程,代码位置如下:

UltraScale GTH解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;由于数据解包是数据组包的逆过程,所以这里不再过多赘述,视频数据解包模块顶层接口如下:

FDMA图像缓存

FDMA图像缓存架构实现的功能是将输入视频缓存到板载DDR中再读出送后续模块,目的是实现视频同步输出,实现输入视频到输出视频的跨时钟域问题,更好的呈现显示效果;由于调用了Xilinx官方的MIG作为DDR控制器,所以FDMA图像缓存架构就是实现用户数据到MIG的桥接作用;架构如下:

FDMA图像缓存架构由FDMA控制器+FDMA组成;FDMA实际上就是一个AXI4-FULL总线主设备,与MIG对接,MIG配置为AXI4-FULL接口;FDMA控制器实际上就是一个视频读写逻辑,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;FDMA控制器每次写入一行视频数据,即每次向DDR中写入M个像素,写N次即可完成1帧图像的缓存,读视频与之一样;同时调用两个FIFO实现输入输出视频的跨时钟域处理,使得用户可以AXI4内部代码,以简单地像使用FIFO那样操作AXI总线,从而达到读写DDR的目的,进而实现视频缓存;本设计图像缓存方式为3帧缓存;图像缓存模块代码架构如下:

基于FDMA的图像缓存架构在Block Design设计中如下:

HDMI视频输出

缓存图像从DDR4读出后经过Native时序生成模块输出标准的VGA时序视频,然后经过纯verilog显示的RGB转HDMI模块输出HDMI差分视频;最后送显示器显示即可;需要注意的是,UltraScale系列FPGA不支持oserdese2原语,所以只能用oserdese3原语实现10 bit串化,基于此,本博主提供的RGB转HDMI模块可支持7系列、ULTRASCALE系列FPGA、ULTRASCALE_PLUS系 FPGA,顶层代码如下:

代码例化如下:

此外,有的FPGA开发板采用专用芯片实现RGB转HDMI功能,这种情况下只需配置芯片即可,本设计中有的工程就是使用了ADV7511芯片,其i2c配置代码如下:

工程源码架构

提供2套工程源码,以工程源码1为例,工程Block Design设计如下:

提供2套工程源码,以工程源码1为例,综合后的工程源码架构如下:

工程源码2使用了Zynq;PL端时钟由Zynq软核提供,所以需要运行运行SDK以启动Zynq,所以需要在SDK里运行一个简单的hello world程序,SDK软件代码架构如下:

4、vivado工程源码1详解–>KU060版本

开发板FPGA型号:Xilinx–Kintex UltraScale–xcku060-ffva1156-2-i;

FPGA开发环境:Vivado2019.1;

输入:3G-SDI相机或HDMI转SDI盒子,分辨率1920x1080@60Hz;

输出:HDMI,RTL逻辑编码方案,分辨率1280x720@60Hz;

SDI视频解码方案:GS2971芯片方案;

图像缩放方案:纯verilog代码实现、任意比例缩放的图像缩放模块;

图像缩放用例:1920x1080缩放到1280x720;

回环光口类型:SFP光口;

高速接口类型:UltraScale GTH,线速率5Gbps;

高速接口编解码协议:8b/10b编解码;

图像缓存方案:FDMA图像缓存+DDR4颗粒+3帧缓存;

实现功能:FPGA实现UltraScale GTH光口视频传输;

工程作用:此工程目的是让读者掌握FPGA实现UltraScale GTH光口视频传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、vivado工程源码2详解–>Zynq UltraScale ZU4EV版本

开发板FPGA型号:Xilinx–>Zynq UltraScale–xczu4ev-sfvc784-1-i;

FPGA开发环境:Vivado2019.1;

输入:3G-SDI相机或HDMI转SDI盒子,分辨率1920x1080@60Hz;

输出:HDMI,ADV7511编码方案,分辨率1280x720@60Hz;

SDI视频解码方案:GS2971芯片方案;

图像缩放方案:纯verilog代码实现、任意比例缩放的图像缩放模块;

图像缩放用例:1920x1080缩放到1280x720;

回环光口类型:SFP光口;

高速接口类型:UltraScale GTH,线速率5Gbps;

高速接口编解码协议:8b/10b编解码;

图像缓存方案:FDMA图像缓存+PS端DDR4颗粒+3帧缓存;

实现功能:FPGA实现UltraScale GTH光口视频传输;

工程作用:此工程目的是让读者掌握FPGA实现UltraScale GTH光口视频传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

6、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证

准备工作

需要准备的器材如下:

SDI摄像头、GS2971转接板;

FPGA开发板,没有开发板可以找本博提供;

SFP光模块和光纤;

我的开发板了连接如下:

UltraScale GTH光口SDI视频传输效果演示

UltraScale GTH光口SDI视频传输效果演示如下:

SDI-GTP

8、工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

FPGA实现SDI视频缩放转UltraScale GTH光口传输,基于GS2971+Aurora 8b/10b编解码架构,提供2套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目我这里已有的 GT 高速接口解决方案本博已有的 SDI 编解码方案我这里已有的FPGA图像缩放方案 3、工程详细设计方案工程设计原理框图SDI 输入设备GS2971芯片BT1120转RGB…...

二级C语言题解:矩阵主、反对角线元素之和,二分法求方程根,处理字符串中 * 号

目录 一、程序填空📝 --- 矩阵主、反对角线元素之和 题目📃 分析🧐 二、程序修改🛠️ --- 二分法求方程根 题目📃 分析🧐 三、程序设计💻 --- 处理字符串中 * 号 题目…...

利用 Python 爬虫获取按关键字搜索淘宝商品的完整指南

在电商数据分析和市场研究中,获取商品的详细信息是至关重要的一步。淘宝作为中国最大的电商平台之一,提供了丰富的商品数据。通过 Python 爬虫技术,我们可以高效地获取按关键字搜索的淘宝商品信息。本文将详细介绍如何利用 Python 爬虫技术获…...

什么是幂等性

幂等性(Idempotence)是一个在数学、计算机科学等多个领域都有重要应用的概念,下面从不同领域为你详细介绍其含义。 数学领域 在数学中,幂等性是指一个操作或函数进行多次相同的运算,其结果始终与进行一次运算的结果相…...

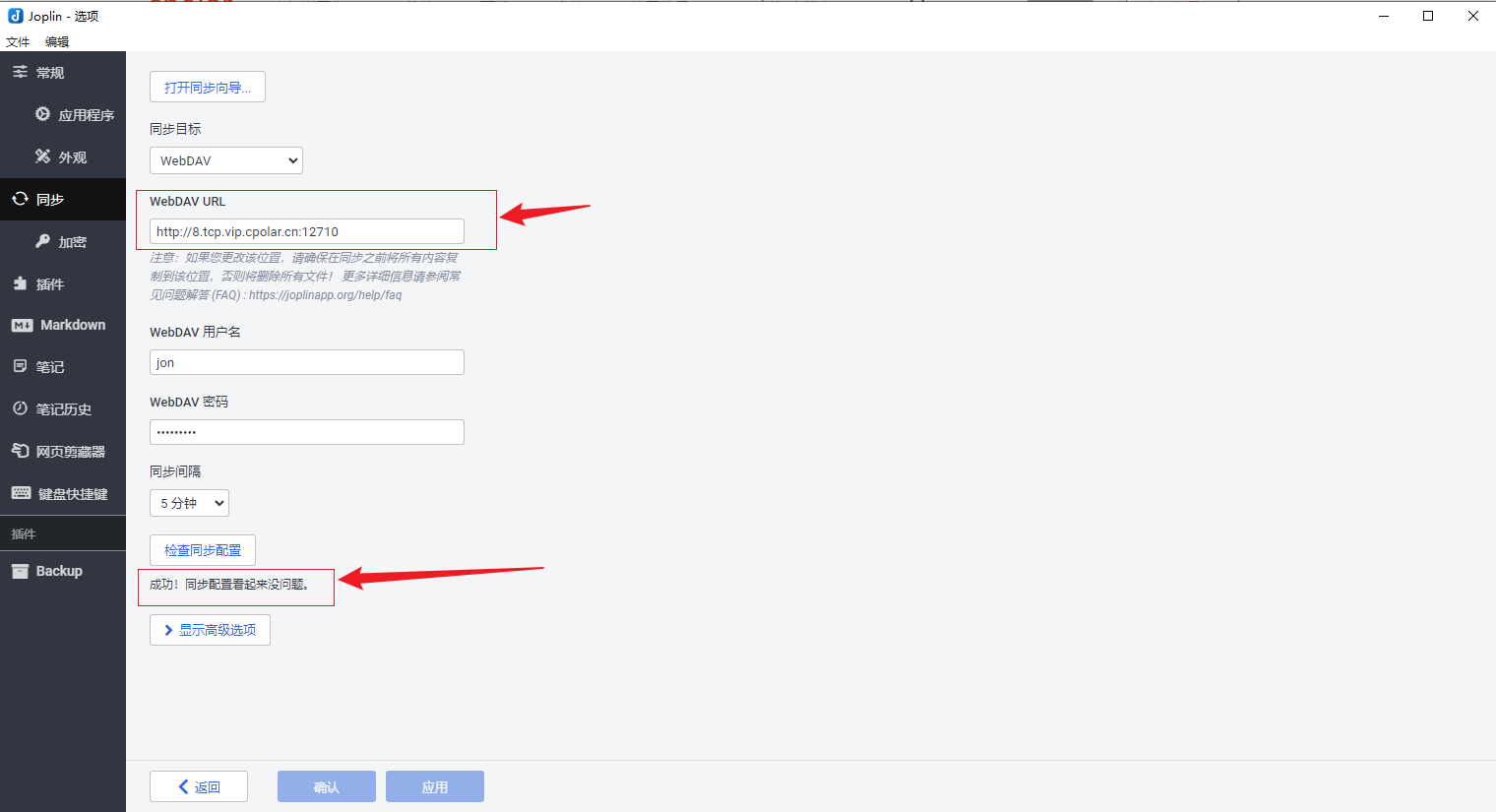

群晖NAS如何通过WebDAV和内网穿透实现Joplin笔记远程同步

文章目录 前言1. 检查群晖Webdav 服务2. 本地局域网IP同步测试3. 群晖安装Cpolar工具4. 创建Webdav公网地址5. Joplin连接WebDav6. 固定Webdav公网地址7. 公网环境连接测试 前言 在数字化浪潮的推动下,笔记应用已成为我们记录生活、整理思绪的重要工具。Joplin&…...

示例:JAVA调用deepseek

近日,国产AI DeepSeek在中国、美国的科技圈受到广泛关注,甚至被认为是大模型行业的最大“黑马”。在外网,DeepSeek被不少人称为“神秘的东方力量”。1月27日,DeepSeek应用登顶苹果美国地区应用商店免费APP下载排行榜,在…...

【提示工程】:如何有效与大语言模型互动

随着人工智能技术的快速发展,大语言模型(LLM)如 GPT 系列在各类任务中的应用越来越广泛。从文本生成到代码编写,从数据分析到内容创作,这些模型展现出了强大的能力。然而,要充分发挥大语言模型的潜力,关键在于如何设计高质量的提示词(Prompts)。这门技术被称为提示工程…...

操作系统—经典同步问题

补充 互斥信号量mutex初值均为1 同步信号量根据问题实际描述自己设计 生产者-消费者问题 问题描述:一组生产者进程和一组消费者进程 共享一个初始为空、大小为n的缓冲区。(缓冲区:临界资源) 只有缓冲区没满时,生产者…...

profinet工业通信协议网关:提升钢铁冶炼智能制造效率的利器

工业通信协议网关profinet转ethercat(稳联技术WL-PN-ECATM)在钢铁冶炼生产线中的智能应用实践 在现代钢铁冶炼生产中,复杂的设备互联和数据传输对生产效率和质量控制至关重要。本案例详细阐述了某大型钢铁集团通过工业通信协议网关实现生产线…...

)

Vue基础:计算属性(描述依赖响应式状态的复杂逻辑)

文章目录 引言computed() 方法期望接收一个 getter 函数可写计算属性:计算属性的 Setter计算属性的缓存机制调试 Computed引言 推荐使用计算属性来描述依赖响应式状态的复杂逻辑 computed 函数:它接受 getter 函数并为 getter 返回的值返回一个不可变的响应式 ref 对象。 c…...

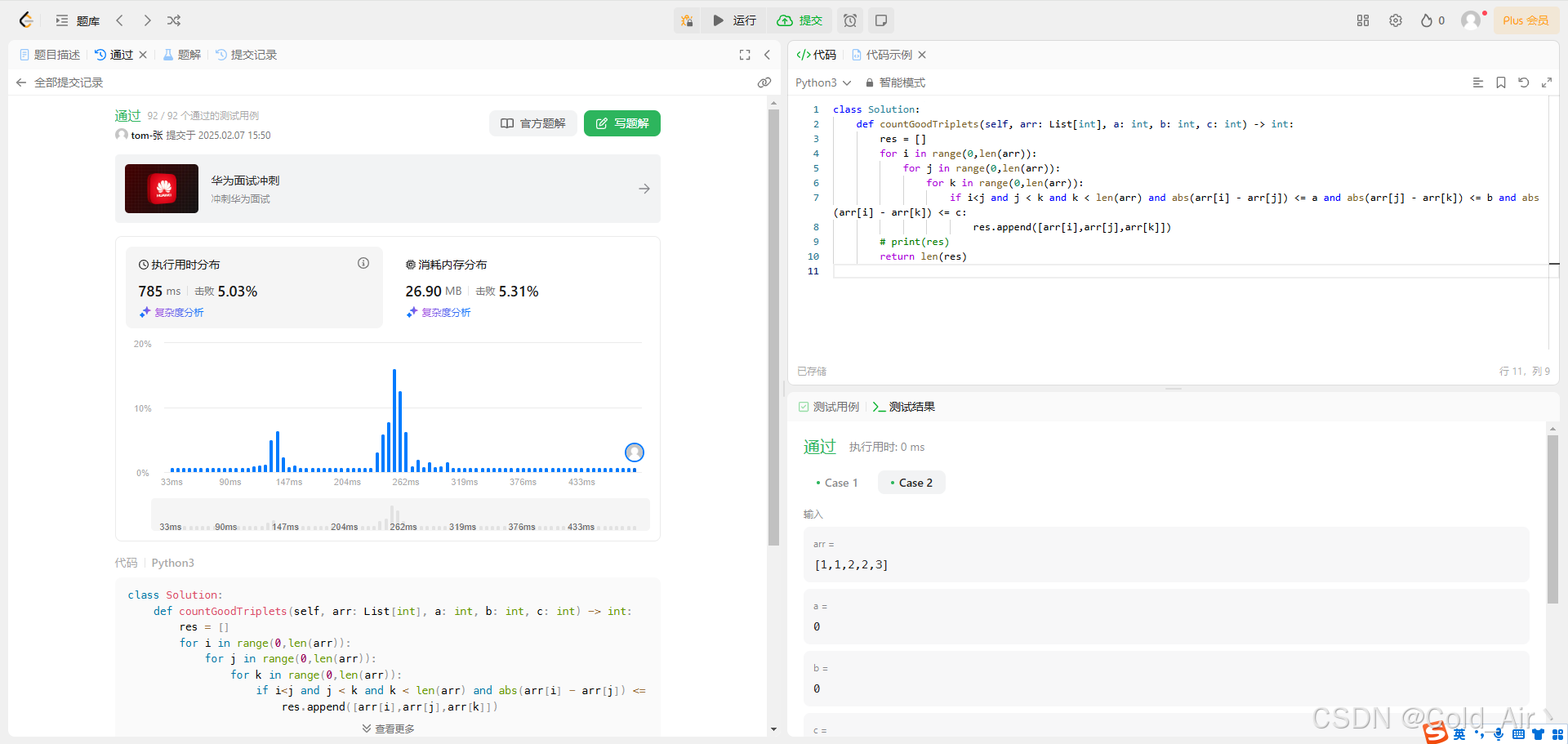

leetcode:1534. 统计好三元组(python3解法)

难度:简单 给你一个整数数组 arr ,以及 a、b 、c 三个整数。请你统计其中好三元组的数量。 如果三元组 (arr[i], arr[j], arr[k]) 满足下列全部条件,则认为它是一个 好三元组 。 0 < i < j < k < arr.length|arr[i] - arr[j]| &l…...

BUU27 [SUCTF 2019]CheckIn1

题目是上传文件 直接上传muma.jpg还不成功: 好吧,那做一个图片马上去,换马以后发现还是不行,呃啊啊啊啊 干啥啥不行,搜wp第一名,哎 新面孔:exif_imagetype 函数在 PHP 中用于检测一个文件是否为…...

unity学习30:Audio Source, Audio clip 音效和音乐

目录 1 音乐相关必须要有 Audio listener 和Source 2 Scene里必须要有 Audio listener 3 Audio Source 3.1 Audio Source 就是音源,可播放的音乐clip 分类 3.2 创建Audio Source 3.3 各种属性 3.4 3D sound Settings 4 使用脚本来播放声音 4.1 声明AudioC…...

【Qt 常用控件】输入类控件1(QLineEdit和QTextEdit 输入框)

目录 1.QLineEdit 单行输入框 例:输入个人信息,通过按钮提交 例:为输入框设置验证器,检查输入的电话 例:验证两次输入的密码是否一致 例:是否显示密码按钮,toggled信号。 2.QTextEdit多行输入框 、QPl…...

openEuler22.03LTS系统升级docker至26.1.4以支持启用ip6tables功能

本文记录了openEuler22.03LTS将docker升级由18.09.0升级至26.1.4的过程(当前docker最新版本为27.5.1,生产环境为保障稳定性,选择升级到上一个大版本26的最新小版本)。 一、现有环境 1、系统版本 [rootlocalhost opt]# cat /etc…...

深入解析:如何利用 Java 爬虫按关键字搜索淘宝商品

在电商领域,通过关键字搜索商品是常见的需求。无论是商家分析竞争对手,还是消费者寻找心仪的商品,获取搜索结果中的商品信息都至关重要。本文将详细介绍如何利用 Java 爬虫按关键字搜索淘宝商品,并提供完整的代码示例。 一、Java…...

STM32上部署AI的两个实用软件——Nanoedge AI Studio和STM32Cube AI

1 引言 STM32 微控制器在嵌入式领域应用广泛,因为它性能不错、功耗低,还有丰富的外设,像工业控制、智能家居、物联网这些场景都能看到它的身影。与此同时,人工智能技术发展迅速,也逐渐融入各个行业。 把 AI 部署到 STM…...

C++ Primer 成员访问运算符

欢迎阅读我的 【CPrimer】专栏 专栏简介:本专栏主要面向C初学者,解释C的一些基本概念和基础语言特性,涉及C标准库的用法,面向对象特性,泛型特性高级用法。通过使用标准库中定义的抽象设施,使你更加适应高级…...

芯科科技的BG22L和BG24L带来应用优化的超低功耗蓝牙®连接

全新的BG22L为常见蓝牙设备提供强大的安全性和处理能力,而BG24L支持先进的AI/ML加速和信道探测功能 2025年2月6日 – 致力于以安全、智能无线连接技术,建立更互联世界的全球领导厂商Silicon Labs(亦称“芯科科技”,NASDAQ&#x…...

java后端开发面试常问

面试常问问题 1 spring相关 (1)Transactional失效的场景 <1> Transactional注解默认只会回滚运行时异常(RuntimeException),如果方法中抛出了其他异常,则事务不会回滚(数据库数据仍然插…...

终极免费音频编辑神器:告别昂贵软件,开启专业音频创作之旅

终极免费音频编辑神器:告别昂贵软件,开启专业音频创作之旅 【免费下载链接】audacity Audio Editor 项目地址: https://gitcode.com/GitHub_Trending/au/audacity 你是否曾因音频编辑软件的复杂界面而望而却步?是否在寻找一款既能满足…...

Scroll Reverser深度解析:macOS事件拦截与独立滚动控制的高效实现

Scroll Reverser深度解析:macOS事件拦截与独立滚动控制的高效实现 【免费下载链接】Scroll-Reverser Per-device scrolling prefs on macOS. 项目地址: https://gitcode.com/gh_mirrors/sc/Scroll-Reverser Scroll Reverser是一款专为macOS设计的开源工具&am…...

基于smartcat的智能文件自动分类与归档系统实践

1. 项目概述:一个智能化的文件分类与归档工具最近在整理个人电脑和服务器上的文件时,我又一次陷入了混乱。下载文件夹里混杂着PDF、图片、代码压缩包、安装程序;项目文档和历史备份散落在各处。手动分类不仅耗时,而且容易出错。我…...

基于RAG与本地LLM的智能代码库管理工具部署与优化指南

1. 项目概述:一个为开发者打造的智能代码库管理工具最近在整理自己过去几年的项目代码时,我遇到了一个几乎所有开发者都会头疼的问题:代码库越来越多,但想快速找到某个特定功能的实现、或者想复用一段之前写过的优质代码时&#x…...

别再手动改路由了!用Ant Design Vue的Menu组件动态生成“顶一左多”级导航菜单

基于Ant Design Vue的声明式导航菜单架构设计 在复杂后台管理系统开发中,导航菜单的动态生成与权限控制一直是架构设计的难点。传统方案往往需要在多个组件中硬编码菜单结构,导致维护成本高、权限同步困难。本文将介绍如何利用Ant Design Vue的Menu组件与…...

自动驾驶系统商业化策略:硬件与软件协同设计解析

1. 自动驾驶系统的商业策略框架解析自动驾驶系统(Autonomous Driving System, ADS)作为智能交通领域的核心技术,其商业化落地需要硬件(SSH)与软件策略的协同设计。从技术架构来看,ADS由感知层、决策层和执行…...

10个UTF8-CPP最佳实践:让你的C++ Unicode处理更高效

10个UTF8-CPP最佳实践:让你的C Unicode处理更高效 【免费下载链接】utfcpp UTF-8 with C in a Portable Way 项目地址: https://gitcode.com/gh_mirrors/ut/utfcpp UTF8-CPP是一个轻量级的C库,提供了便捷的UTF-8编码和解码功能,帮助开…...

cliclick 开发者指南:从源码编译到自定义Action开发

cliclick 开发者指南:从源码编译到自定义Action开发 【免费下载链接】cliclick macOS CLI tool for emulating mouse and keyboard events 项目地址: https://gitcode.com/gh_mirrors/cl/cliclick cliclick 是一款强大的 macOS 命令行工具,用于模…...

)

紧急通知:地质项目交付周期压缩迫在眉睫——用NotebookLM替代传统笔记整理,单项目节省22.6工时(附审计级日志)

更多请点击: https://intelliparadigm.com 第一章:NotebookLM地质学研究辅助的范式变革 NotebookLM 作为 Google 推出的基于用户上传文档进行语义理解与推理的 AI 工具,正悄然重塑地质学研究的知识处理流程。传统地质工作依赖大量野外笔记、…...

告别“模板感”:打造高转化企业官网的全流程指南

在互联网流量红利见顶的今天,企业官网早已不再是简单的“网络名片”。面对同质化严重的模板网站,用户早已审美疲劳。一个真正有价值的网站,不仅要颜值在线,更要有清晰的定位和严密的逻辑支撑。它既是品牌形象的门面,更…...